NRL LIBRARY DOROTHY STONE M/S 2185

Sys 7 LIB

PROGRAMMER'S GUIDE TO THE CENTRAL PROCESSOR

## TEXAS INSTRUMENTS

INCORPORATED

# TEXAS INSTRUMENTS

930039 **-** 2 MAY 1976

## C Texas Instruments Incorporated 1976 All Rights Reserved

The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein and patents which might be granted thereon disclosing or employing the materials, methods, techniques or apparatus described herein are the exclusive property of Texas Instruments Incorporated.

No disclosure of the information or drawings shall be made to any other person or organization without the prior consent of Texas Instruments Incorporated.

## LIST OF EFFECTIVE PAGES

INSERT LATEST CHANGED PAGES DESTROY SUPERSEDED PAGES

Note: The portion of the text affected by the changes is indicated by a vertical bar in the outer margins of the page.

Programmer's Guide to the Central Processor

Original . . . . . . . . . . . . . . . . . May 1973 Revised and Reissued . . . . . . . . . . . May 1976

Total number of pages in this publication is 427 consisting of the following:

| PAGE<br>NO.       | CHANGE<br>NO. | PAGE<br>NO. | CHANGE<br>NO. | PAGE<br>NO. | CHANGE<br>NO. |

|-------------------|---------------|-------------|---------------|-------------|---------------|

| Title             | 0             |             |               |             |               |

| Effec. Pages.     | 0             |             |               |             |               |

| i - xvi           | 0             |             |               |             |               |

| 1-1 - 1-4         | 0             |             |               |             |               |

| 2-1 - 2-20        | 0             |             |               |             |               |

| 3-1 - 3-5         | 0             |             |               |             |               |

| 4-1 - 4-25        | 0             |             |               |             |               |

| 5-1 - 5-7         | 0             |             |               |             |               |

| 6-1 - 6-54        | 0             |             |               |             |               |

| 7-1 - 7-176       | 0             |             |               |             | ·             |

| 8-1 - 8-65/8-6    | 6.0           |             |               |             |               |

| A-1 - A-10        | 0             |             |               |             |               |

| B-1 - B-10        | 0             |             |               |             |               |

| C-1 - C-10        | 0             |             |               |             |               |

| D-1 - D-4         | 0             |             |               |             |               |

| E-1 - E-4         | 0             |             |               |             |               |

| $F-1 - F-4 \dots$ | 0             |             |               |             |               |

| G-1 - G-5         | 0             |             |               |             |               |

| H-1 - H-2         | 0             |             |               |             |               |

| User's Resp .     | 0             |             |               |             |               |

| Bus. Reply        | 0             |             |               |             |               |

|                   |               |             |               |             |               |

## TEXAS INSTRUMENTS

INCORPORATED EQUIPMENT GROUP AUSTIN, TEXAS

## **Application For Automatic Update**

|        | REF NO.          | NAME<br>9 12          | LAST , INITIAL 41 56      |

|--------|------------------|-----------------------|---------------------------|

| CARD 1 |                  | NAME                  |                           |

| CARD 2 |                  | PART NUMBER           | 736657                    |

| CARD 3 |                  | MAIL STATION          | ENTER & USM IF US MAIL    |

| CARD 4 |                  | QUANTITY              | ENTER QUANTITY OF MANUALS |

|        | COMPLETE ONLY IF | US MAIL ADDRESS       | RIGHT JUSTIFIED  NAME     |

|        |                  | ADDI                  | 41 LAST, INITIAL 60       |

|        |                  | Alpholi               | ADDRESS                   |

|        | СТТТТ            | Molola                | ADDRESS                   |

|        |                  | ADD2                  |                           |

|        | ППП              | ADD3 OF LINES         |                           |

|        |                  | REQUIRED FOR COMPLETE |                           |

|        | ППП              | ADD4 ADDRESS          |                           |

|        |                  |                       |                           |

|        |                  | ADD5                  |                           |

|        |                  |                       |                           |

|        |                  | ADD6                  |                           |

|        |                  | •                     |                           |

FOLD AND STAPLE THIS SHEET. RETURN ADDRESS IS ON REVERSE SIDE.

I AM PRESENTLY ON DISTRIBUTION FOR OTHER DOCUMENTS YES NO

EQUIPMENT GROUP

P.O. BOX 2909

AUSTIN, TEXAS 78767

ATTENTION

TECHNICAL DATA BRANCH

MAIL STATION 2146

## TABLE OF CONTENTS

| Section |                   |                                                     | Page  |  |  |  |

|---------|-------------------|-----------------------------------------------------|-------|--|--|--|

| I       | GENE              | RAL DESCRIPTION                                     |       |  |  |  |

|         | 1-1               | The Central Processor                               | 1-1   |  |  |  |

|         | 1-2               | Central Processor-Peripheral Processor Relationship | 1 - 1 |  |  |  |

|         | 1-3               | Central Processor Resources                         | 1-1   |  |  |  |

|         | 1-8               | The Assembler                                       | 1-2   |  |  |  |

|         | 1-9               | Coding Media                                        | 1-3   |  |  |  |

|         | 1-10              | Punched Card                                        | 1-10  |  |  |  |

|         | 1-11              | Coding Form                                         | 1-11  |  |  |  |

| II      | LANGUAGE ELEMENTS |                                                     |       |  |  |  |

|         | 2-1               | Character Set for the ASC                           | 2-1   |  |  |  |

|         | 2-2               | Printable Characters                                | 2-1   |  |  |  |

|         | 2-3               | Special Characters                                  | 2-1   |  |  |  |

|         | 2-4               | Items                                               | 2-1   |  |  |  |

|         | 2-5               | Symbol                                              | 2-3   |  |  |  |

|         | 2-6               | Character String                                    | 2-3   |  |  |  |

|         | 2-7               | Decimal Integer                                     | 2-3   |  |  |  |

|         | 2-8               | Hexadecimal Integer                                 | 2-4   |  |  |  |

|         | 2-9               | Floating Point Item                                 | 2-4   |  |  |  |

|         | 2-10              | Fixed Point Decimal Item                            | 2-5   |  |  |  |

|         | 2-11              | Location Counter                                    | 2-6   |  |  |  |

|         | 2-12              | Literal                                             | 2-6   |  |  |  |

|         | 2-13              | Intrinsic Function                                  | 2-6   |  |  |  |

| Section |      |                                                | Page |

|---------|------|------------------------------------------------|------|

|         | 2-14 | Operators                                      | 2-7  |

|         | 2-15 | Operator Types                                 | 2-7  |

|         | 2-16 | Expressions                                    | 2-7  |

|         | 2-17 | Subexpressions                                 | 2-10 |

|         | 2-18 | Assumed Parentheses                            | 2-11 |

|         | 2-19 | Literals                                       | 2-12 |

|         | 2-20 | Lists                                          | 2-13 |

|         | 2-21 | Intrinsic Functions                            | 2-14 |

|         | 2-22 | Global Attribute Functions                     | 2-14 |

|         | 2-26 | Location Intrinsic Functions                   | 2-16 |

|         | 2-27 | Program Sections                               | 2-16 |

|         | 2-28 | Relocation                                     | 2-17 |

|         | 2-29 | Constants                                      | 2-17 |

|         | 2-32 | Location Counter                               | 2-17 |

|         | 2-33 | Relocatability of Symbols                      | 2-18 |

|         | 2-34 | Relocatability of Expressions                  | 2-18 |

| III     | LANG | UAGE STRUCTURE                                 |      |

|         | 3-1  | Statement Format                               | 3-1  |

|         | 3-2  | Conventions for Describing Language Statements | 3-2  |

|         | 3-3  | Continuation Lines                             | 3-2  |

|         | 3-4  | Label Field                                    | 3-3  |

|         | 3-6  | Command Field                                  | 3-3  |

|         | 3-7  | Operand Field                                  |      |

|         | 3-8  | Remark Field                                   |      |

| Section |       |                                      | Page         |

|---------|-------|--------------------------------------|--------------|

|         | 3-9   | Comment Lines                        | 3 <b>-</b> 5 |

|         | 3-10  | Blank Lines                          | 3 - 5        |

| IV      | DIREC | CTIVES                               |              |

|         | 4-1   | Introduction                         | 4-1          |

|         | 4-2   | Definition Directives                | 4-1          |

|         | 4-3   | Equate Directive (EQU)               | 4-1          |

|         | 4-4   | Set Directive (SEŢ)                  | 4-2          |

|         | 4-5   | External Name Directive (EXTRN)      | 4-3          |

|         | 4-6   | Entry Name Directive (ENTRY)         | 4-4          |

|         | 4-7   | Data Directive (DATA)                | 4-5          |

|         | 4-8   | Format Directive (FORM)              | 4-6          |

|         | 4-9   | Using Directive (USING)              | 4-7          |

|         | 4-10  | Drop Directive (DROP)                | 4-8          |

|         | 4-11  | Origin Directive (ORG)               | 4-8          |

|         | 4-12  | Control Directives                   | 4-9          |

|         | 4-13  | Literal Origin Directive (LITORG)    | 4-9          |

|         | 4-14  | End Assembly Directive (END)         | 4-10         |

|         | 4-15  | Section Directive (SEC)              | 4-11         |

|         | 4-16  | Common Module Directive (COM)        | 4-12         |

|         | 4-17  | Dummy Section Directive (DUM)        | 4-13         |

|         | 4-18  | Dummy Common Module Directive (COMD) | 4-14         |

|         | 4-19  | Copy Directive (COPY)                | 4-15         |

|         | 4-20  | Reserve Directive (RES)              | 4-16         |

|         | 4-21  | Align Directive (ALIGN)              | 4-16         |

|         | 4-22  | Do Directive (DO)                    | 4-17         |

|         | 4-23  | Pseudo Directives                    | 4-21         |

| Section |              |                                           | Page  |

|---------|--------------|-------------------------------------------|-------|

|         | 4-24         | Indirect Address Constant Directive (IND) | 4-21  |

|         | 4-25         | Branch Address Constant Directive (BCON)  |       |

|         | 4-26         | Data Halfword Directive (DATAH)           | 4-22  |

|         | 4-27         | Listing Directives                        | 4-22  |

|         | 4-28         | Skip Directive (SKIP)                     | 4-23  |

|         | 4-29         | List Directive (LIST)                     | 4-24  |

|         | 4-30         | Nolist Directive (NOLIST)                 | 4-25  |

| v       | ASSEN        | MBLER OUTPUT                              |       |

|         | 5-1          | Assembler Output                          | 5-1   |

|         | 5-2          | Source Program Listing                    | 5 - 1 |

|         | 5-3          | Messages                                  | 5-3   |

|         | 5 <b>-</b> 5 | Cross-Reference Listing                   | 5-5   |

| VI      | ASSEN        | MBLER-CENTRAL PROCESSOR INTERFACE         |       |

|         | 6-1          | Introduction                              | 6-1   |

|         | 6-2          | Instruction Formats                       | 6-1   |

|         | 6-3          | Label                                     | 6-3   |

|         | 6-4          | Command                                   | 6-3   |

|         | 6-5          | Operands                                  | 6-3   |

|         | 6-6          | R, N, X Operand List                      | 6-3   |

|         | 6-10         | R, R, N Operand List                      | 6-7   |

|         | 6-11         | Register Addressing                       | 6-8   |

|         | 6-12         | Register Operand-R Field Addresses        | 6-8   |

|         | 6-13         | Address Operand Register Addresses        | 6-11  |

|         | 6-14         | Address Development                       | 6-12  |

| Section |       |                                              | Page          |

|---------|-------|----------------------------------------------|---------------|

|         | 6-15  | Assembler Translation                        | 6-12          |

|         | 6-18  | Machine Translation                          | 6-15          |

|         | 6-29  | Immediate Operands                           | 6-31          |

|         | 6-30  | Assembler Translation                        | 6-31          |

|         | 6-33  | Machine Translation                          | 6-32          |

|         | 6-40  | Branch Address Development                   | 6-36          |

|         | 6-41  | Assembler Translation                        | 6-37          |

|         | 6-47  | Machine Translation                          | 6-39          |

|         | 6-51  | Data Formats                                 | 6-43          |

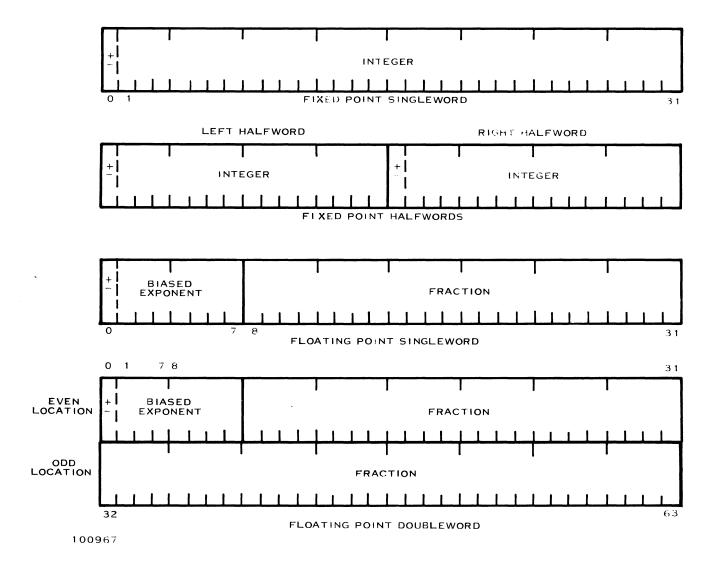

|         | 6-52  | Fixed Point Data                             | 6-44          |

|         | 6-53  | Floating Point Data                          | 6-44          |

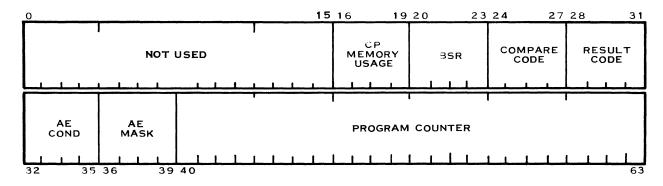

|         | 6-56  | Program Status Doubleword                    | 6-49          |

|         | 6-57  | Branch or Skip Register                      | 6-50          |

|         | 6-58  | Compare Code                                 | 6-50          |

|         | 6-59  | Result Code                                  | 6-51          |

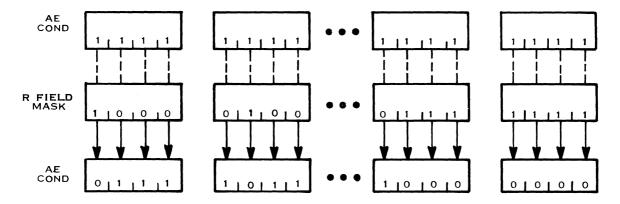

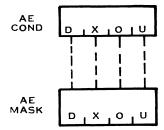

|         | 6-60  | Arithmetic Exception Condition Code          | 6-51          |

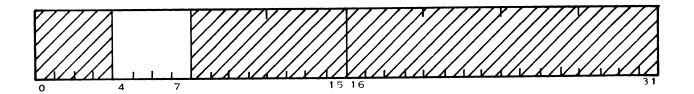

|         | 6-62  | Arithmetic Exception Mask                    | 6-53          |

|         | 6-64  | Program Counter                              | 6-54          |

| VII     | THE S | CALAR INSTRUCTIONS FOR THE CENTRAL PROCESSOR |               |

|         | 7-1   | Introduction                                 | 7-1           |

|         | 7-2   | Load Register Instructions                   | 7-2           |

|         | 7-3   | Load, Word (L)                               | 7-3           |

|         | 7-4   | Load, Left Half From Left (LLL)              | 7-4           |

|         | 7-5   | Load, Right Halfword From Right (LRR)        | <b>7-</b> 5   |

|         | 7-5.1 | Load, Right Halfword From Left (LRL)         | 7 <b>-</b> 5A |

|         | 7-6   | Load, Left Halfword From Right (LLR)         | 7-6           |

| Section |          |                                                            | Page  |

|---------|----------|------------------------------------------------------------|-------|

|         | 7-7      | Load, Doubleword (LD)                                      | 7-7   |

|         | 7-8      | Load Immediate, Word (LI)                                  | 7-8   |

|         | 7-9      | Load Immediate, Halfword (LIH)                             | 7-9   |

|         | 7-10     | Load Negative, Fixed Point Word (LN)                       | 7-10  |

|         | 7-11     | Load Negative, Fixed Point Halfword (LNH)                  | 7-11  |

|         | 7-12     | Load Negative, Floating Point Word (LNF)                   | 7-12  |

|         | 7-13     | Load Negative, Floating Point Doubleword (LND)             | 7-13  |

|         | 7-14     | Load Magnitude, Fixed Point Word (LM)                      | 7-14  |

|         | 7-15     | Load Magnitude, Fixed Point Halfword (LMH)                 | 7-15  |

|         | 7-16     | Load Magnitude, Floating Point Word (LMF)                  | 7-16  |

|         | 7-17     | Load Magnitude, Floating Point Doubleword (LMD) .          | 7-17  |

|         | 7-18     | Load Negative Magnitude, Fixed Point Word (LNM).           | 7-18  |

|         | 7-19     | Load Negative Magnitude, Fixed Point Halfword (LNMH)       | 7-19  |

|         | 7-20     | Load Negative Magnitude, Floating Point Word (LNMF)        | 7-20  |

|         | 7-21     | Load Negative Magnitude, Floating Point Double-word (LNMD) | 7-21  |

|         | 7-22     | Load One's Complement, Word (LD)                           | 7-22  |

|         | 7-23     | Load Register File (LF)                                    | 7-23  |

|         | 7-24     | Load Register Files, Multiple (LFM)                        | 7-24  |

|         | 7-25 Sto | re Instructions                                            | 7-25  |

|         | 7-26     | Store Word (ST)                                            | 7-26  |

|         | 7-27     | Store Halfword (STLL)                                      | 7-27  |

|         | 7-28     | Store Right Halfword Into Right (STRR)                     | 7-28  |

|         | 7-28.1   | Store Right Halfword Into Left (STRL)                      | 7-28A |

|         | 7-29     | Store Left Halfword Into Right (STLR)                      | 7-29  |

|         | 7-30     | Store Doubleword (STD)                                     | 7-30  |

|         | 7-31     | Store Zero, Word (STZ)                                     | 7-31  |

|                 |                                                                                                      | Page                          |

|-----------------|------------------------------------------------------------------------------------------------------|-------------------------------|

| -32             | Store Zero, Halfword (STZH)                                                                          | 7-32                          |

| <b>-</b> 33     | Store Zero, Doubleword (STZD)                                                                        | 7-33                          |

| <b>-</b> 34     | Store Negative, Fixed Point Word (STN)                                                               | 7-34                          |

| <del>-</del> 35 | Store Negative, Fixed Point Halfword (STNH)                                                          | 7-35                          |

| <b>-</b> 36     | Store Negative, Floating Point Word (STNF)                                                           | 7-36                          |

| <b>-</b> 37     | Store Negative, Floating Point Doubleword (STND)                                                     | 7-37                          |

| <b>-</b> 38     | Store One's Complement, Word (STO)                                                                   | 7-38                          |

| <b>-</b> 39     | Store One's Complement, Halfword (STDH)                                                              | 7-39                          |

| <b>-</b> 40     | Store Register File (STF)                                                                            | 7-40                          |

| <b>-</b> 41     | Store Register Files, Multiple (STFM)                                                                | 7-41                          |

| -42 Arit        | hmetic Instructions                                                                                  | 7-42                          |

| <b>-</b> 43     | Add, Fixed Point Word (A)                                                                            | 7-43                          |

| <b>-</b> 44     | Add, Fixed Point Halfword (AH)                                                                       | 7-44                          |

| <del>-</del> 45 | Add, Floating Point Word (AF)                                                                        | 7-45                          |

| <b>-</b> 46     | Add, Floating Point Doubleword (AFD)                                                                 | 7-46                          |

| <b>-</b> 47     | Add Immediate, Fixed Point Word (AI)                                                                 | 7-47                          |

| <b>-</b> 48     | Add Immediate, Fixed Point Halfword (AIH)                                                            | 7-48                          |

| <b>-</b> 49     | Add Magnitude, Fixed Point Word (AM)                                                                 | 7-49                          |

| <b>-</b> 50     | Add Magnitude, Fixed Point Halfword (AMH)                                                            | 7-50                          |

| <b>-</b> 51     | Add Magnitude, Floating Point Word (AMF)                                                             | 7-51                          |

| -52             | Add Magnitude, Floating Point Doubleword (AMFD)                                                      | 7-52                          |

| <b>-</b> 53     |                                                                                                      | 7-53                          |

| -54             | Subtract, Fixed Point Halfword (SH)                                                                  | 7-54                          |

| -55             | Subtract, Floating Point Word (SF)                                                                   | 7 <b>-</b> 55                 |

| <b>-</b> 56     | Subtract, Floating Point Doubleword (SFD)                                                            | <b>7-</b> 56                  |

| <b>-</b> 57     | Subtract Immediate, Fixed Point Word (SI)                                                            | 7 <b>-</b> 57                 |

| <b>-</b> 58     | Subtract Immediate, Fixed Point Halfword (SIH)                                                       | 7 <b>-</b> 58                 |

|                 | -33 -34 -35 -36 -37 -38 -39 -40 -41 -42 Arit -43 -44 -45 -46 -47 -48 -49 -50 -51 -52 -53 -54 -55 -56 | Store Zero, Doubleword (STZD) |

| Section |               |                                                      | Page         |

|---------|---------------|------------------------------------------------------|--------------|

|         | 7-59          | Subtract Magnitude, Fixed Point Word (SM)            | 7-59         |

|         | 7-60          | Subtract Magnitude, Fixed Point Halfword (SMH)       | 7-60         |

|         | 7-61          | Subtract Magnitude, Floating Point Word (SMF)        | 7-61         |

|         | 7-62          | Subtract Magnitude, Floating Point Doubleword (SMFD) | 7-62         |

|         | 7-63          | Multiply, Fixed Point Word (M)                       | 7-63         |

|         | 7-64          | Multiply, Fixed Point Halfword (MH)                  | 7-64         |

|         | 7-65          | Multiply, Floating Point Word (MF)                   | 7-65         |

|         | 7-66          | Multiply, Floating Point Doubleword (MFD)            | 7-66         |

|         | 7-67          | Multiply Immediate, Fixed Point Word (MI)            | 7-67         |

|         | 7-68          | Multiply Immediate, Fixed Point Halfword (MIH)       | 7-68         |

|         | 7-69          | Divide, Fixed Point Word (D)                         | 7-69         |

|         | 7-70          | Divide, Fixed Point Halfword (DH)                    | 7-70         |

|         | 7-71          | Divide, Floating Point Word (DF)                     | 7-71         |

|         | 7-72          | Divide, Floating Point Doubleword (DFD)              | 7-72         |

|         | 7-73          | Divide Immediate, Fixed Point Word (DI)              | 7-73         |

|         | 7-74          | Divide Immediate, Fixed Point Halfword (DIH)         | 7-74         |

|         | 7-75 Lo       | gical Instructions                                   | <b>7-7</b> 5 |

|         | 7 <b>-</b> 76 | AND, Word (AND)                                      | 7-76         |

|         | 7-77          | AND, Doubleword (ANDD)                               | 7-77         |

|         | 7 <b>-</b> 78 | AND Immediate, Word (ANDI)                           | 7-78         |

|         | 7-79          | OR, Word (OR)                                        | 7-79         |

|         | 7-80          | OR, Doubleword (ORD)                                 | 7-80         |

|         | 7-81          | OR Immediate, Word (ORI)                             | 7-81         |

|         | 7-82          | Exclusive OR, Word (XOR)                             | 7-82         |

|         | 7-83          | Exclusive OR, Doubleword (XORD)                      | 7-83         |

|         | 7-84          | Exclusive OR Immediate, Word (XORI)                  | 7-84         |

|         | 7-85          | Equivalence, Word (EQC)                              | 7-85         |

| Section |               |                                               | Page          |

|---------|---------------|-----------------------------------------------|---------------|

|         | 7-86          | Equivalence, Doubleword (EQCD)                | 7-86          |

|         | 7-87          | Equivalence Immediate, Word (EQCI)            | 7-87          |

|         | 7 <b>-</b> 88 | Shift Instructions                            | 7-88          |

|         | 7 <b>-</b> 89 | Arithmetic Shifts                             | 7-89          |

|         | 7-90          | Logical Shifts                                | 7-89          |

|         | 7-91          | Circular Shifts                               | 7-90          |

|         | 7-92          | Algorithm for Bit Reversal                    | 7-91          |

|         | 7-93          | Arithmetic Shift, Word (SA)                   | 7-92          |

|         | 7-94          | Arithmetic Shift, Halfword (SAH)              | 7-93          |

|         | 7-95          | Arithmetic Shift, Doubleword (SAD)            | 7-94          |

|         | 7-96          | Logical Shift, Word (SL)                      | 7-95          |

|         | 7-97          | Logical Shift, Halfword (SLH)                 | 7-96          |

|         | 7 <b>-</b> 98 | Logical Shift, Doubleword (SLD)               | 7-97          |

|         | 7-99          | Circular Shift, Word (SC)                     | 7-98          |

|         | 7-100         | Circular Shift, Halfword (SCH)                | 7-99          |

|         | 7-101         | Circular Shift, Doubleword (SCD)              | 7-100         |

|         | 7-102         | Bit Reversal, Word (RVS)                      | 7-101         |

|         | 7-103         | Compare Instructions                          | 7-102         |

|         | 7-104         | Compare, Fixed Point Word (C)                 | 7-103         |

|         | 7-105         | Compare, Fixed Point Halfword (CH)            | 7-104         |

|         | 7-106         | Compare, Floating Point Word (CF)             | <b>7-</b> 105 |

|         | 7-107         | Compare, Floating Point Doubleword (CFD)      | 7-106         |

|         | 7-108         | Compare Immediate, Fixed Point Word (CI)      | 7-107         |

|         | 7-109         | Compare Immediate, Fixed Point Halfword (CIH) | 7-108         |

|         | 7-110         | Compare Logical AND, Word (CAND)              | 7-109         |

|         | 7-111         | Compare Logical AND, Doubleword (CANDD)       | 7-110         |

|         | 7-112         | Compare Logical AND Immediate, Word (CANDI)   | 7-111         |

| Section |       |                                                      | Page   |

|---------|-------|------------------------------------------------------|--------|

|         | 7-113 | Compare Logical OR, Word (COR)                       | 7-112  |

|         | 7-114 | Compare Logical OR, Doubleword (CORD)                | 7-113  |

|         | 7-115 | Compare Logical OR Immediate, Word (CORI)            | 7-114  |

|         | 7-116 | Increment or Decrement, Test and Skip Instructions   | 7-115  |

|         | 7-117 | Increment, Test and Skip on Equal (ISE)              | 7-116  |

|         | 7-118 | Increment, Test and Skip on Not Equal (ISNE)         | 7-117  |

|         | 7-119 | Decrement, Test and Skip on Equal (DSE)              | 7-118  |

|         | 7-120 | Decrement, Test and Skip on Not Equal (DSNE)         | 7-119  |

|         | 7-121 | Increment or Decrement, Test and Branch Instructions | 7-120  |

|         | 7-122 | Increment, Test and Branch on Zero (IBZ)             | 7-121  |

|         | 7-123 | Increment, Test and Branch on Not Zero (IBNZ)        | 7-122  |

|         | 7-124 | Decrement, Test and Branch on Zero (DBZ)             | 7-123  |

|         | 7-125 | Decrement, Test and Branch on Not Zero (DBNZ)        | 7-124  |

|         | 7-126 | Index, Test and Branch Instructions                  | 7-125  |

|         | 7-127 | Algorithm for Index Test and Branch                  | 7-126  |

|         | 7-128 | Branch on Less Than or Equal (BCLE)                  | 7-127  |

|         | 7-129 | Branch on Greater Than (BCG)                         | 7-128  |

|         | 7-130 | Conditional Branch Instructions                      | 7-129  |

|         | 7-131 | Condition Algorithms for Conditional Branches        | 7-132  |

|         | 7-132 | Branch on Comparison Code True (BCC)                 | 7-133  |

|         | 7-133 | Branch on Result Code True (BRC)                     | 7-135  |

|         | 7-134 | Branch on Arithmetic Exception (BAE)                 | 7-137  |

|         | 7-135 | Branch on Execute Branch Condition True (BXEC)       | 7-140  |

|         | 7-136 | Unconditional Branch Instructions                    | 7-141  |

|         | 7-137 | Branch and Load Base Register With Program Counter   | 7 1/12 |

| Section |       |                                                                     | Page           |

|---------|-------|---------------------------------------------------------------------|----------------|

|         | 7-138 | Branch and Load Index or Vector Register With Program Counter (BLX) | 7-143          |

|         | 7-139 | Stack Instructions                                                  | 7-144          |

|         | 7-140 | Stack Instruction Definition                                        | 7-145          |

|         | 7-141 | Push Word Into Last-In-First-Out Stack (PSH)                        | 7-146          |

|         | 7-142 | Pull Word From Last-In-First-Out Stack (PUL)                        | 7-147          |

|         | 7-143 | Modify Stack Parameter Doubleword (MOD)                             | 7-148          |

|         | 7-144 | Conversion and Normalization Instructions                           | 7-150          |

|         | 7-145 | Algorithm for Floating Point to Fixed Point Conversions             | 7-151          |

|         | 7-146 | Algorithm for Fixed Point to Floating Point Conversions             | 7-152          |

|         | 7-147 | Fixed Point Normalization                                           | 7-154          |

|         | 7-148 | Convert Floating Point Word to Fixed Point Word (FLFX)              | 7 <b>-</b> 155 |

|         | 7-149 | Convert Floating Point Word to Fixed Point Half-word (FLFH)         | 7-156          |

|         | 7-150 | Convert Floating Point Doubleword to Fixed Point Word (FDFX)        | 7-157          |

|         | 7-151 | Convert Fixed Point Word to Floating Point Word (FXFL)              | 7-158          |

|         | 7-152 | Convert Fixed Point Halfword to Floating Point Word (FHFL)          | <b>7-</b> 159  |

|         | 7-153 | Convert Fixed Point Word to Floating Point Doubleword (FXFD)        | 7-160          |

|         | 7-154 | Convert Fixed Point Halfword to Floating Point Doubleword (FHFD)    | 7-160          |

|         | 7-155 | Normalize Fixed Point Word (NFX)                                    | 7-162          |

|         | 7-156 | Normalize Fixed Point Halfword (NFH)                                | 7-163          |

|         | 7-157 | Miscellaneous Instructions                                          | 7 164          |

| Section |                                                   |                                                           | Page                    |  |  |  |  |

|---------|---------------------------------------------------|-----------------------------------------------------------|-------------------------|--|--|--|--|

|         | 7-158                                             | Exchange Words (XCH)                                      | 7-165                   |  |  |  |  |

|         | 7-159                                             | Load Look Ahead (LLA)                                     | 7-166                   |  |  |  |  |

|         | 7-159.1                                           | Prepare to Branch (PB)                                    | 7 <b>-</b> 167 <i>A</i> |  |  |  |  |

|         | 7-160                                             | Load Effective Address (LEA)                              | 7-168                   |  |  |  |  |

|         | 7-161                                             | Execute (XEC)                                             | 7-169                   |  |  |  |  |

|         | 7-162                                             | Interpret (INT)                                           | 7-170                   |  |  |  |  |

|         | 7-162.1                                           | Fork (FORK)                                               | 7-170 <i>A</i>          |  |  |  |  |

|         | 7-162.2                                           | Join (JOIN)                                               | 7-170                   |  |  |  |  |

|         | 7-163                                             | Monitor Call and Proceed (MCP)                            | 7-171                   |  |  |  |  |

|         | 7-164                                             | Monitor Call and Wait (MCW)                               | 7-172                   |  |  |  |  |

|         | 7-165 P                                           | rogram Status Instructions                                | 7-173                   |  |  |  |  |

|         | 7-166                                             | Load Arithmetic Exception Mask (LAM)                      | 7-174                   |  |  |  |  |

|         | 7-167                                             | Load Arithmetic Exception Condition (LAC)                 | 7-175                   |  |  |  |  |

|         | 7-167.1                                           | Load Arithmetic Exception Mask and Condition (LEM) .      | 7 <b>-</b> 175 <i>A</i> |  |  |  |  |

|         | 7-168                                             | Store Program Status Word (SPS)                           | 7-176                   |  |  |  |  |

| VIII    | THE VECTOR INSTRUCTIONS FOR THE CENTRAL PROCESSOR |                                                           |                         |  |  |  |  |

|         | 8 <b>-</b> 1 In                                   | troduction                                                | 8-1                     |  |  |  |  |

|         | 8-2 D                                             | efinition                                                 | 8-1                     |  |  |  |  |

|         | 8-3 E                                             | xecute Vector Parameter File Instructions                 | 8-4                     |  |  |  |  |

|         | 8-4                                               | Vector Load and Execute (VECTL)                           | 8-4                     |  |  |  |  |

|         | 8-5                                               | Vector Execute (VECT)                                     | 8-5                     |  |  |  |  |

|         | 8-6 T                                             | he Vector Parameter File                                  | 8-6                     |  |  |  |  |

|         | 8-7                                               | Vector Operation Specification                            | 8-6                     |  |  |  |  |

|         | 8-8                                               | Arithmetic and Logical Comparison Condition Specification | 8-6                     |  |  |  |  |

|         | 8-9                                               | Vector Length (Self Loop Count) Specification             | 8-8                     |  |  |  |  |

| Section |      |                                                  | Page |

|---------|------|--------------------------------------------------|------|

|         | 8-10 | Single-Valued Vector and Word Size Specification | 8-8  |

|         | 8-11 | Single-Valued Vectors                            | 8-8  |

|         | 8-12 | Immediate Vectors                                | 8-11 |

|         | 8-13 | Vector Address Development                       | 8-14 |

|         | 8-14 | Directly Addressed Vectors                       | 8-14 |

|         | 8-13 | Vector Address Development                       | 8-14 |

|         | 8-15 | Halfword Index Start Specification               | 8-15 |

|         | 8-16 | Self Loop Increment Direction                    | 8-16 |

|         | 8-17 | Inner Loop Specification                         | 8-18 |

|         | 8-20 | Outer Loop Specification                         | 8-19 |

|         | 8-23 | Program Interrupts                               | 8-19 |

|         | 8-24 | Vector Hazard                                    | 8-20 |

|         | 8-25 | Vector Arithmetic Instructions                   | 8-20 |

|         | 8-26 | Vector Add Instructions                          | 8-21 |

|         | 8-27 | Vector Add Magnitude Instructions                | 8-22 |

|         | 8-28 | Vector Subtract Instructions                     | 8-23 |

|         | 8-29 | Vector Subtract Magnitude Instructions           | 8-24 |

|         | 8-30 | Vector Multiply Instructions                     | 8-25 |

|         | 8-31 | Vector Dot Product Instructions                  | 8-26 |

|         | 8-32 | Vector Divide Instructions                       | 8-28 |

|         | 8-33 | Vector Logical Instructions                      | 8-30 |

|         | 8-34 | Vector Shift Instructions                        | 8-31 |

|         | 8-35 | Vector Merge Instructions                        | 8-33 |

|         | 8-36 | Vector Order Instructions                        | 8-34 |

|         | 8-37 | Vector Compare Instructions                      | 8-36 |

| Section |      |                                                         | Page |

|---------|------|---------------------------------------------------------|------|

|         | 8-38 | Vector Compare Arithmetic Instructions                  | 8-38 |

|         | 8-39 | Vector Compare Logical Instructions                     | 8-38 |

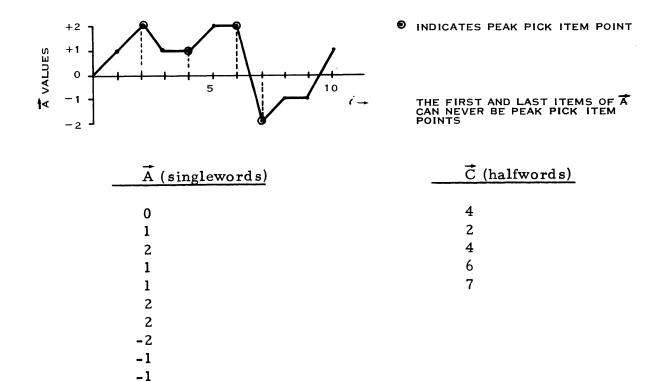

|         | 8-40 | Vector Peak Picking Instructions                        | 8-39 |

|         | 8-41 | Vector Search Instructions                              | 8-40 |

|         | 8-42 | Vector Search for Largest Element Instructions          | 8-41 |

|         | 8-43 | Vector Search for Largest Magnitude Instructions        | 8-42 |

|         | 8-44 | Vector Search for Smallest Element Instructions         |      |

|         | 8-45 | Vector Search for Smallest Magnitude Instructions       | 8-44 |

|         | 8-46 | Vector Conversion Instructions                          | 8-45 |

|         | 8-47 | Convert Floating Point Elements to Fixed Point Elements | 8-45 |

|         | 8-48 | Convert Fixed Point Elements to Floating Point Elements | 8-46 |

|         | 8-49 | Vector Normalize Instructions                           | 8-47 |

|         | 8-50 | Vector Map Instructions                                 | 8-49 |

|         | 8-51 | Vector Select Boolean Instructions                      | 8-52 |

|         | 8-52 | Vector Replace Boolean Instructions.,                   | 8-54 |

|         | 8-53 | Vector Map Boolean Instructions                         | 8-56 |

|         | 8-54 | Vector Maximum/Minimum Instructions                     | 8-58 |

|         | 8-55 | Vector Compare Boolean Instructions                     | 8-60 |

|         | 8-56 | Vector Compare and/or Boolean Instructions              | 8-61 |

|         | 8-57 | Vector Select                                           | 8-62 |

|         | 8-58 | Vector Replace                                          | 8_63 |

#### APPENDIXES

| Append       | ix                                                          |      |

|--------------|-------------------------------------------------------------|------|

| Α            | SCALAR INSTRUCTIONS BY LOGICAL GROUPING                     | A-1  |

| В            | SCALAR INSTRUCTIONS IN ALPHABETICAL ORDER BY ASSEMBLER CODE | B-1  |

| С            | SCALAR INSTRUCTIONS IN NUMERIC ORDER BY MACHINE CODE        | C-1  |

| D            | VECTOR INSTRUCTIONS BY LOGICAL GROUPING                     | D-1  |

| E            | VECTOR INSTRUCTIONS IN ALPHABETICAL ORDER BY ASSEMBLER CODE | E-1  |

| F            | VECTOR INSTRUCTIONS IN NUMERIC ORDER BY MACHINE CODE        | F- 1 |

| G            | SCALAR INSTRUCTION TIME REQUIREMENTS                        | G-1  |

|              | G-1 Scalar Instruction Timing Groups                        | G-1  |

| Н            | VECTOR INSTRUCTION TIME REQUIREMENTS                        | H- 1 |

|              | H-1 Time Requirements for Complete Vector Operation         | H- 1 |

| ·            | LIST OF ILLUSTRATIONS                                       |      |

| Figure       | Title                                                       | Page |

| 1-1          | Coding Form                                                 | 1-4  |

| 5-1          | Sample Source Program Listing                               | 5-2  |

| 5-2          | Cross-Reference Listing Example                             | 5-6  |

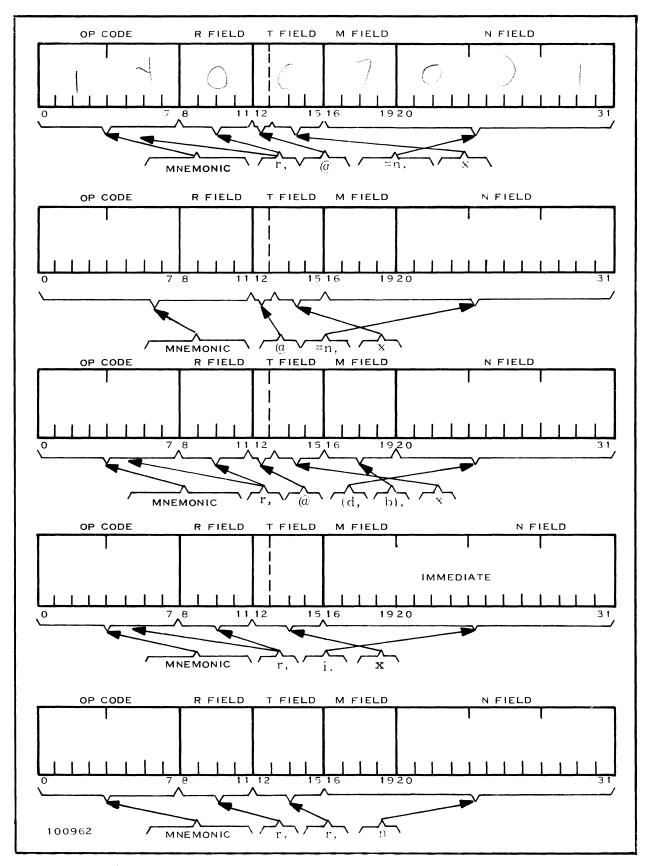

| 6 <b>-</b> 1 | Assembler Statement Translations into Machine Code          | 6-2  |

| 6-2          | Register File Specifications                                | 6-9  |

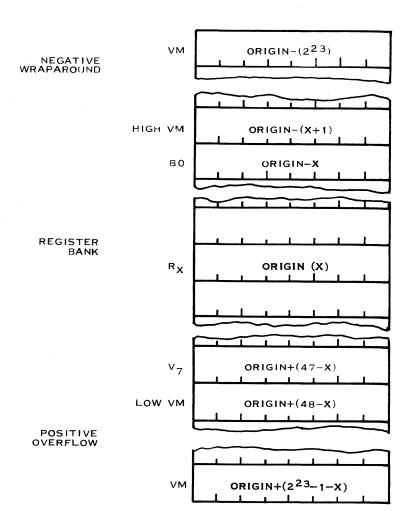

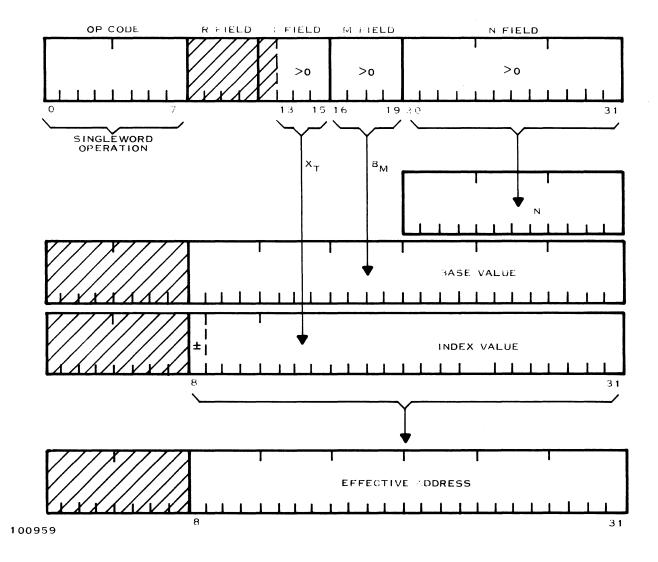

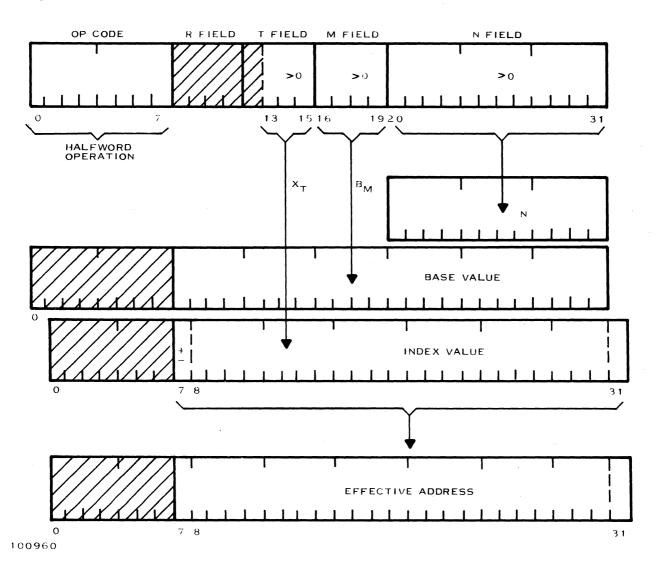

| 6-3          | Development of Singleword Effective Addresses               | 6-17 |

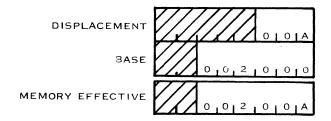

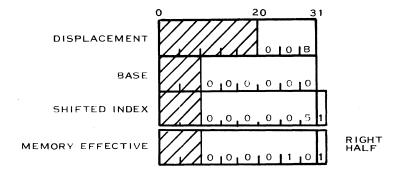

| 6-4          | Development of Halfword Effective Addresses                 | 6-20 |

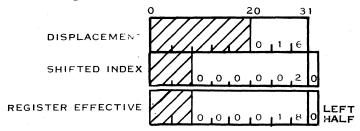

| 6 <b>-</b> 5 | Development of Doubleword Effective Addresses               | 6-23 |

| 6 <b>-</b> 6 | Indirect Address Cell Format                                | 6-28 |

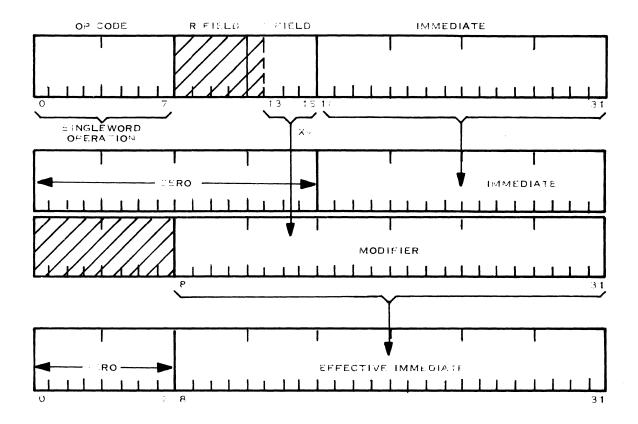

| 6 <b>-</b> 7 | Development of Singleword Effective Immediate Operands      | 6-33 |

| 6 <b>-</b> 8 | Development of Halfword Effective Immediate Operands        | 6-34 |

| 6-9          | Development of Singleword Logical Immediate Operands        | 6-36 |

## LIST OF ILLUSTRATIONS (Continued)

| Figure | Title                                                                  | Page         |

|--------|------------------------------------------------------------------------|--------------|

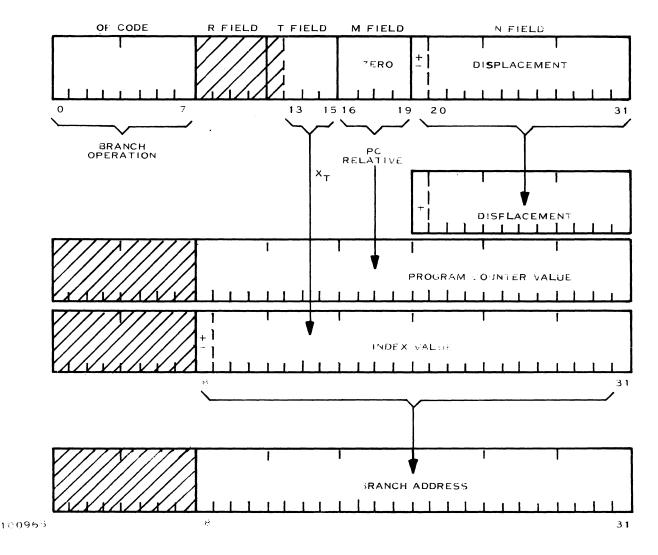

| 6-10   | Program Counter Relative Branch Address Development                    | 6-40         |

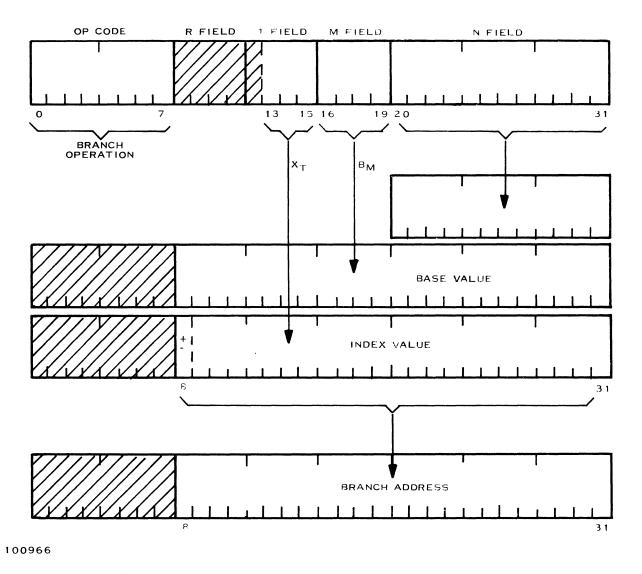

| 6-11   | Development of Base Relative Branch Addresses                          | 6-42         |

| 6-12   | Algebraic Data Formats                                                 | 6-43         |

| 8-1    | The Vector Parameter File                                              | 8-3          |

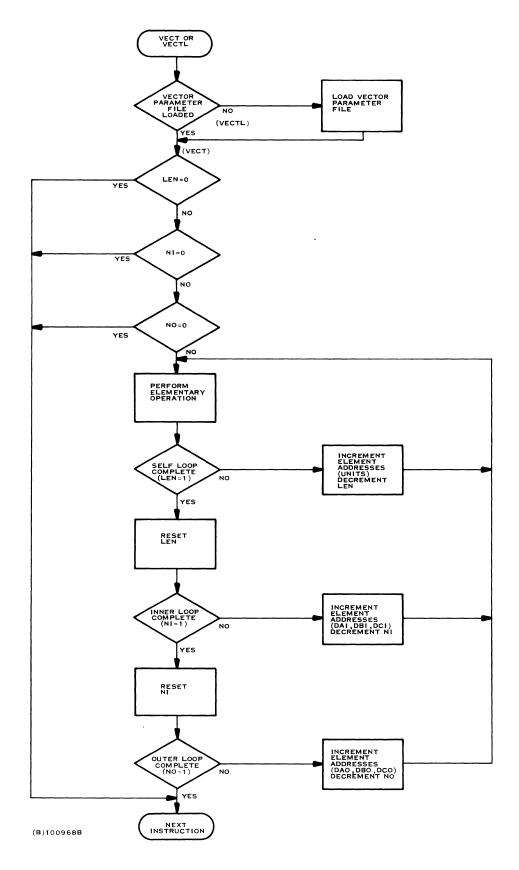

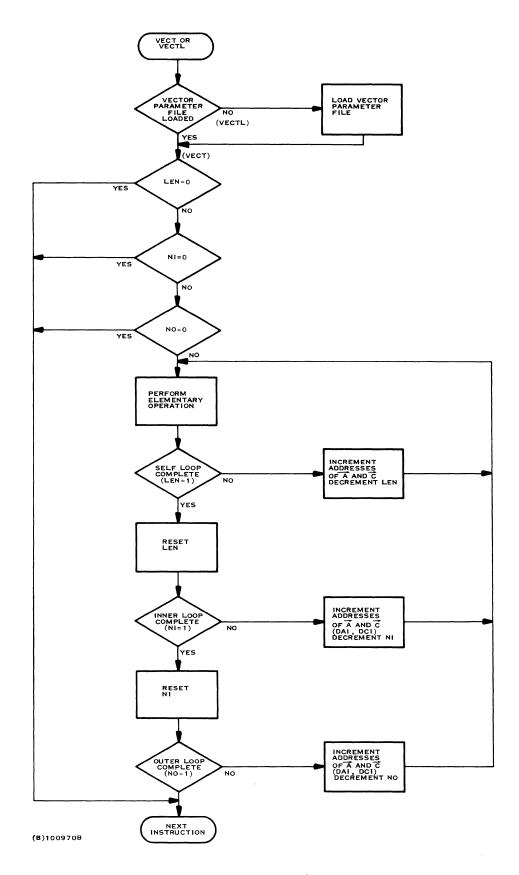

| 8-2    | Flow of Execution of a Vector Parameter File                           | 8-7          |

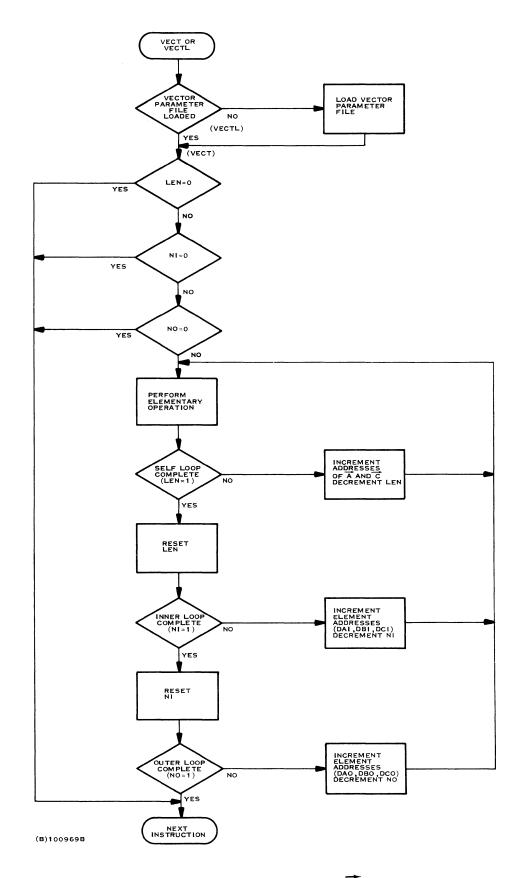

| 8-3    | Flow of Execution with B Single-valved                                 | 8-10         |

| 8-4    | Flow of Execution with B Single-valved                                 | 8-13         |

|        | LIST OF TABLES                                                         |              |

| Table  | Title                                                                  | Page         |

| 2-1    | Printable Characters                                                   | 2-2          |

| 2-2    | Special Characters                                                     | 2-2          |

| 2-3    | Operator Hierarchies and Descriptions                                  | 2-8          |

| 2-4    | Use of Operators                                                       | 2-9          |

| 2-5    | Results of Operations on Absolute and Relocatable Items in Expressions | 2-19         |

| 5-1    | Assembler Generated Messages                                           | 5-4          |

| 5-2    | Procedure Processing Message Symbols                                   | 5 <b>-</b> 5 |

| 6-1    | General Forms and Variations of the Operand Lists                      | 6-4          |

| 6-2    | Register Addressing Symbols                                            | 6-10         |

| 6-3    | Development of Singleword Addresses (Direct)                           | 6-18         |

| 6-4    | Development of Branch Addresses (Direct)                               | 6-41         |

| 6-5    | Value Ranges of Fixed Point Data                                       | 6-44         |

| 6-6    | Specifications for Arithmetic Exception Mask Data Constants            | 6-54         |

| 8-1    | Specifications of the SV Field                                         | 8-9          |

| 8-2    | Specifications of the HS Field Valves                                  | 8-17         |

| 8-3    | Specifications of the VI Field Valves                                  | 8-17         |

| 8-4    | Specifications of the VI, HS, and ALCT Fields                          | 8-37         |

| 8-5    | Specifications of the ALCT Valves                                      | 8-37         |

| H-1    | Vector Execution Rates in Clocks/Element                               | H-1          |

## SECTION I

#### GENERAL DESCRIPTION

#### 1-1. THE CENTRAL PROCESSOR

The Central Processor is that unit of the ASC dedicated to processing the user's raw data. It is particularly oriented toward the processing of numerical data that is typical of scientific data processing.

#### 1-2. CENTRAL PROCESSOR-PERIPHERAL PROCESSOR RELATIONSHIP

The Central Processor operates under control of the Peripheral Processor in which the operating system resides. The resources of the Central Processor are time-shared among users through this system which can cause a current program's status to be saved, the program to be removed from the Central Processor, and another program to be given control of the Central Processor.

All communication, either to or from the Central Processor, takes place through the Peripheral Processor.

#### 1-3. CENTRAL PROCESSOR RESOURCES

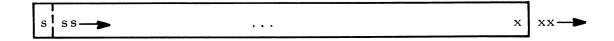

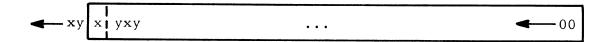

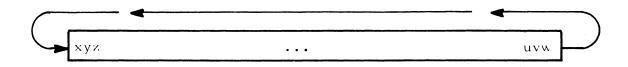

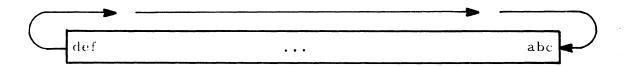

Once a program is given control of the Central Processor, both program and data are streamed directly from central memory to the Central Processor and results streamed back. Streaming is accomplished by double buffering of both program and data.

#### 1-4. Pipeline Instruction Processing

The instructions fetched from memory are decoded in a pipeline made of four levels. This method permits four instructions to be in the process of decoding at any given time, and, unless a branch instruction requires the discard of some of the instructions, each instruction is ready for execution in the arithmetic unit as soon as its resources are available.

#### 1-5. Vector Operations

The Central Processor performs operations on ordered sets of data without requiring additional instruction decoding. Once a vector operation has been initiated, the data upon which it operates is streamed directly to the arithmetic unit from central memory, and the results streamed back to central memory.

#### 1-6. Instruction Set

The Central Processor has 177 scalar instructions and 70 vector instructions that provide a large range of programming ploys.

#### 1-7. Data Formats

The Central Processor performs operations on fixed point, floating point, or binary logical data.

Fixed point data may be either 32-bit singlewords or 16-bit halfwords, and in either case the values are represented with any negative numbers in two's complement notation.

Floating point data may be either 32-bit singlewords or 64-bit doublewords. In either case, the biased hexadecimal exponent method of representation is used.

#### 1-8. THE ASSEMBLER

The assembler as implemented for the Central Processor provides for symbolic coding of programs to be executed in the Central Processor.

There are directives which are commands to the assembler itself. These directives are used to inform the assembler of conditions to be expected at assembly time, of conditions to be expected at object program execution time, and of the nature of the symbols used by the programmer.

The assembler mnemonics for actual machine codes are the names of procedures built into the assembler. These procedures translate the mnemonics and the operands associated with them into object code that the machine can execute.

There are also procedures built into the assembler which translate data that is in a form more convenient to the programmer into the object data forms usable by the machine.

#### 1-9. CODING MEDIA

A source program is a sequence of source statements that are punched into cards and entered into the computer by a card reader.

#### 1-10. PUNCHED CARD

The card format is a standard 80-column punched card.

#### 1-11. CODING FORM

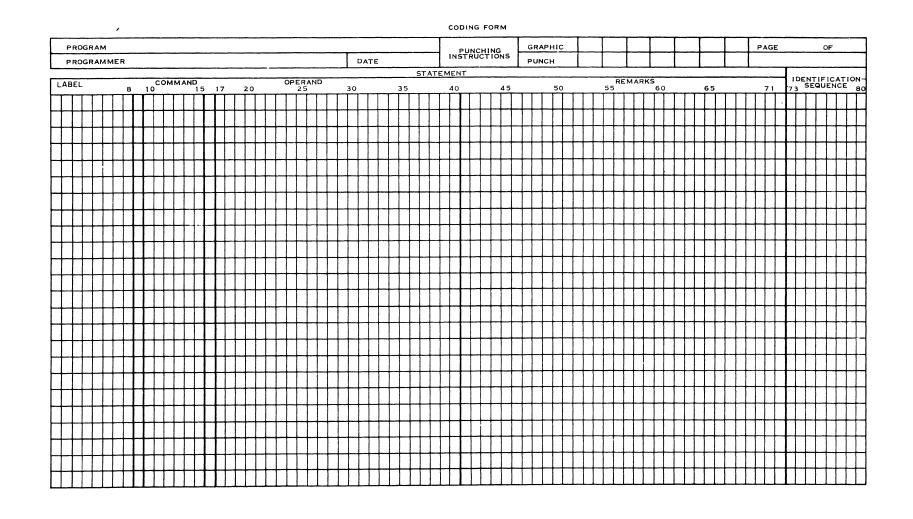

Assembler source statements may be written on the standard coding form, shown in Figure 1-1. One line of code on the form is punched into one card; vertical columns on the form correspond to card columns.

Space is provided for program identification and for instructions to keypunch operators. The body of the coding form consists of the statement field, columns 1 through 72, and the identification sequence field, columns 73 through 80.

Figure 1-1. Coding Form

## SECTION II LANGUAGE ELEMENTS

#### 2-1. CHARACTER SET FOR THE ASC

The ASC Assembler recognizes the EBCDIC character set as standard notation. That is, characters are interpreted as punched on the IBM 029 keypunch.

References in this manual are made to alphabetic characters (A through Z), numeric characters (0 through 9), and special characters (all the rest).

All characters except the double quotation mark ('') and the semicolon (;) may be used in character strings, and these also may be used freely in the remark field and in comments. The period (or decimal point), dollar sign (\$), and question mark (?) may be used in symbols along with alphabetic and numeric characters. Most of the special characters have unique meanings to the assembler.

The double quotation mark ('') inside a character string will terminate the string. The semicolon (;) when used inside character strings will terminate the card image, and the string will be continued on the next line beginning with the first non-blank character.

#### 2-2. PRINTABLE CHARACTERS

Table 2-1 contains a list of the non-alphanumeric printable characters and their names without regard to their special meanings to the assembler.

#### 2-3. SPECIAL CHARACTERS

Table 2-2 lists the special characters which have unique meaning to the ASC Assembler.

#### 2-4. ITEMS

Any item consists of a combination of one or more characters. An item may be a symbol, decimal integer, character string, hexadecimal integer, location counter, floating point item, fixed point item, literal, or intrinsic function.

Table 2-1. Printable Characters

| CHAR-<br>ACTER | NAME                 | CARD<br>CODE | CHAR-<br>ACTER | NAME                     | CARD<br>CODE |

|----------------|----------------------|--------------|----------------|--------------------------|--------------|

|                | blank                | blank        | -              | hyphen, or<br>minus sign | 11           |

| ¢              | cent sign            | 12-8-2       | /              | slash (virgule)          | 0 - 1        |

|                | period               | 12-8-3       | ,              | comma                    | 0-8-3        |

| <              | less than            | 12-8-4       | %              | percent sign             | 0-8-4        |

| (              | left<br>parenthesis  | 12-8-5       | _              | horizontal<br>bar        | 0-8-5        |

| +              | plus sign            | 12-8-6       | >              | greater than             | 0-8-6        |

|                | vertical bar         | 12-8-7       | ?              | question mark            | 0-8-7        |

| &              | ampersand            | 12           | <b>†</b>       | vertical arrow           | 8-1          |

| !              | exclamation          | 11-8-2       | :              | colon                    | 8-2          |

|                | point                |              | #              | number                   | 8-3          |

| \$             | dollar sign          | 11-8-3       | @              | at                       | 8-4          |

| *              | asterisk             | 11-8-4       | 1              | apostrophe               | 8-5          |

| )              | right<br>parenthesis | 11-8-5       | =              | equals                   | 8-6          |

| ;              | semicolon            | 11-8-6       | 11             | quotation<br>marks       | 8-7          |

|                | not sign             | 11-8-7       |                |                          |              |

Table 2-2. Special Characters

| CHARACTER MEANING |                         | CHARACTER | MEANING                 |

|-------------------|-------------------------|-----------|-------------------------|

| # _               | hexadecimal             | )         | right parenthesis       |

| @                 | indirect addressing     | ¢         | augment indicator       |

| ,                 | separator               | >         | greater than            |

| \$                | location counter        | ;         | continuation            |

| *                 | multiply and comments   | $\neg$    | not                     |

|                   | period or decimal point | 11        | EBCDIC string indicator |

| <                 | less than               | =         | equals or literal       |

| - subtract        |                         |           | indicator               |

| /                 | divide                  | (         | left parenthesis        |

| +                 | add                     | blank     | separator or space      |

2-5. SYMBOL

A symbol is represented as a string of from one to eight EBCDIC characters, the first of which must be alphabetic. The remaining characters may be alphabetic, numeric, . , \$ , # , or any other special characters not used by the Assembler for unique purposes. (See Table 2-2 for characters having unique meaning to the Assembler.)

<u>VALUE</u>: The value of a symbol is the value of the item to which the symbol is assigned.

Examples: AABBCCDD

Q. J\$P?

2-6. CHARACTER STRING

A character string is any string of characters surrounded by double quotation marks (not to be confused with two single quotation marks). Semicolons (;) or double quotation marks ('') cannot be parts of a character string because they operate on the string. Character strings which are assigned to symbols as values cannot exceed 8 characters in length. Other character strings are restricted to 256 characters.

<u>VALUE</u>: The value of a character string is the EBCDIC representation of the characters found between the quotation marks. Each character string is converted into an even multiple of 4 characters (32 bits). Strings which do not contain a multiple of 4 characters are filled to the right with blanks.

Example: ''AB\*C''

2-7. DECIMAL INTEGER

A decimal integer is a string of unsigned decimal digits (0 through 9).

<u>VALUE</u>: The value of a decimal integer is the 32-bit (binary representation) base 10 value of the string of digits.

Examples: 19

5440

LANGUAGE ELEMENTS

#### 2-8. HEXADECIMAL INTEGER

A hexadecimal integer is a string of unsigned hexadecimal digits (0 through F) preceded by a #. The maximum number of characters after the # is 16.

<u>VALUE</u>: The value of a hexadecimal integer is the 32 or 64-bit (binary representation) base 16 value of the string of digits.

Example: #3B8FE5

#### 2-9. FLOATING POINT ITEM

A floating point item is a string of decimal digits with a decimal point and optionally followed by a decimal exponent. The exponent is written as the letter E or the letter D followed by an integer constant. The item may be positive, zero, or negative. If either the initial string of decimal digits or the integral exponent are unsigned, the assembler assumes the respective part to be positive. If a decimal exponent is given, the decimal point is not required in the initial string of digits. The item may assume one of three forms:

- 1. A string of decimal digits with a decimal point, and without an exponent.

This form is assumed by the assembler, to be single precision representation.

- 2. A string of decimal digits, optionally with a decimal point, followed by the letter E and an integral decimal exponent. The E specifies single precision representation.

- 3. A string of decimal digits, optionally with a decimal point, followed by the letter D and an integral decimal exponent. The D specifies double precision representation.

For both single and double precision representation, the value of the exponent, n, has the range:  $-64 \le n \le +63$ . The range of values M, a floating point item, may have is: (1) in single precision (32-bit representation),  $16^{-65} \le M \le (1 - 16^{-6}) \times 16^{63}$  and true zero; and (2) in double precision (64-bit representation),  $16^{-65} \le M \le (1 - 16^{-14}) \times 16^{63}$  and true zero; or, approximately,  $5.4 \times 10^{-79} \le M \le 7.2 \times 10^{75}$ . The number of bits used in the representation of the fractional part of a

floating point item does not significantly affect its range of values, but affects the precision of the values that may be represented.

If the maximum exponent value is exceeded, a syntax error is returned; but, if the significance is exceeded, truncation of the least significant bits occurs and no error message is returned.

<u>VALUE</u>: The value of a floating point item is the 32 or 64-bit binary representation of the string of digits with 8 bits reserved for the exponent and with the remaining 24 or 56 bits left for the fraction. The exponent is represented in excess 64 notation. The fraction is normalized in its area.

Examples:

5.321E+6

6D-26

5.3

-5.2E6

2.718

#### 2-10. FIXED POINT DECIMAL ITEM

A fixed point decimal item is a string of decimal digits, which may have a decimal point, followed by (1) a B or a BB, and by (2) a binary scale factor. The item may be positive, zero, or negative. If either the initial string of decimal digits or the binary scale factor is unsigned, the assembler assumes the respective part to be positive. A positive binary scale factor shifts the binary representation of the quantity to the left by the specified number of binary units, and a negative binary scale factor shifts the binary representation of the quantity to the right by the specified number of binary units. Any part of the decimal numeral which would result in a binary fraction, when converted to binary and scaled, will be truncated. A single B specifies single precision, and a double B (i.e., BB) specifies double precision.

The range of values of a fixed point item, F, is restricted to: -2, 147, 483,  $648 \le F \le +2$ , 147, 483, 647 (i.e.,  $-2^{31} \le F \le 2^{31}$  - 1).

VALUE: The value of a fixed point decimal item is the 32 or 64-bit binary representation of the string of digits with the representation determined by converting integer and fraction portions of the string separately and placing the result in either 32 or 64 bits as determined by the precision designator, B or BB, respectively.

Examples:

3.21B + 5

3.21BB+5

6B2

6BB2

#### 2-11. LOCATION COUNTER

The coding symbol for the value of the location counter is \$...

VALUE: The value of \$ is the 32-bit current value at assembly time of the location counter.

Example:

\$+6

#### 2-12. LITERAL

A literal is a constant which is the relative location of the start of one or more words of data. A literal is expressed in the form of an equals sign followed by the data to be contained in the relative location (see Topic 2-19).

VALUE: The value of a literal is the location of a constant.

Examples:

=A

=6

=A+6

#### 2-13. INTRINSIC FUNCTION

An intrinsic function is an item used to produce substitution of another item, expression, or list in its place. See Topic 2-21.

VALUE: The value of an intrinsic function is the identity of the particular parameter operated on by the function, or is the value assigned to the condition of the parameter operated on by the function.

Example: T(RHO)

#### 2-14. OPERATORS

Items may be combined using the special character operators defined in Table 2-3. The table also gives hierarchy numbers for determining the sequence in which the value of an expression is computed. Operations with higher hierarchies are performed before operations having lower hierarchies. Operations with the same hierarchy are performed from left to right.

#### 2-15. OPERATOR TYPES

Each operator falls under two type classifications: every operator is either a unary operator or a binary operator, and every operator is one of the following: an arithmetic operator, a relational operator, or a logical operator. See Tables 2-3 and 2-4 for the operator symbols and their uses.

UNARY OPERATION: A unary operation is one that involves only one operand.

BINARY OPERATION: A binary operation is one that involves two operands.

ARITHMETIC OPERATION: An arithmetic operation is one that yields algebraic quantities.

RELATIONAL OPERATION: A relational operation is one that yields a "TRUE" or "FALSE" quantity; i.e., 1 or 0, respectively.

LOGICAL OPERATION: A logical operation is one that yields a Boolean quantity.

#### 2-16. EXPRESSIONS

An expression is an item, or it is a series of items, connected by operators. The sequence of operations performed in evaluating an expression is determined by the hierarchy of the operators in the expression. The hierarchy of operators is shown in Table 2-3. Operations with higher hierarchy numbers are performed first; operations with the same hierarchy are performed from left to right.

Table 2-3. Operator Hierarchies and Descriptions

| HIER-<br>ARCHY | SYMBOL       | TYPE              | DESCRIPTION                       |

|----------------|--------------|-------------------|-----------------------------------|

| 7              | +            | Unary Arithmetic  | Plus                              |

| 7              | -            | Unary Arithmetic  | Minus (two's complement)          |

| 7              | -            | Unary Arithmetic  | Not (one's complement)            |

| 6              | //           | Binary Logical    | Logical Binary Operator           |

| 5              | *            | Binary Arithmetic | Arithmetic Product                |

| 5              | /            | Binary Arithmetic | Arithmetic Quotient               |

| 4              | +            | Binary Arithmetic | Arithmetic Sum                    |

| 4              | -            | Binary Arithmetic | Arithmetic Difference             |

| 3              | <            | Binary Relational | Arithmetic Less Than              |

| 3              | 一<           | Binary Relational | Not Less Than                     |

| 3              | =            | Binary Relational | Arithmetic Equals                 |

| 3              | <b>-</b> ¬ = | Binary Relational | Not Equals                        |

| 3              | <=           | Binary Relational | Less Than or Equal                |

| 3              | >            | Binary Relational | Arithmetic Greater Than           |

| 3              | 一>           | Binary Relational | Not Greater Than                  |

| 3              | >=           | Binary Relational | Greater Than or Equal             |

| 2              | <b>米米</b>    | Binary Logical    | Logical Product (AND)             |

| 1              | ++ .         | Binary Logical    | Logical Sum (OR)                  |

| 1 .            |              | Binary Logical    | Logical Difference (Exclusive OR) |

| 1              | ==           | Binary Logical    | Logical Equivalence               |

The length of an expression is limited by the number of continuation lines over which the statement may extend. The value of an arithmetic expression, E, is restricted to the range: -2,147,483,648  $\leq$  E  $\leq$  +2,147,483,647 (-2<sup>31</sup>  $\leq$  E  $\leq$  2<sup>31</sup> - 1). The value of an expression, E, containing an external symbol or symbols is restricted to the range: -8,388,608  $\leq$  E  $\leq$  +8,388,617, (-2<sup>23</sup>  $\leq$  E  $\leq$  2<sup>3</sup> - 1).

Floating point numbers are not valid in expressions which contain more than one item. That is, floating point arithmetic will not be performed at assembly

Table 2-4. Use of Operators

| SYMBOL     | GENERAL<br>FORM                                                                                   | WHERE                                                                                    | RESULTS                                                                                               |

|------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| +          | +a                                                                                                | a is an algebraic expression                                                             | a                                                                                                     |

| -          | -a                                                                                                | a is an algebraic expression                                                             | two's complement of a                                                                                 |

| 一          | ¬a                                                                                                | a is an algebraic or logical expression                                                  | one's complement of a                                                                                 |

| //         | a//i                                                                                              | a is a logical expression; i is an integer expression                                    | shift a left i binary digits if i<br>is positive; shift a right i bi-<br>nary digits if i is negative |

| 714        | a*b                                                                                               | a and b are algebraic expressions                                                        | the product of a and b                                                                                |

| /          | a/b                                                                                               | the numerator a is an algebraic expression; the denominator b is an algebraic expression | the quotient of a divided by b                                                                        |

| +          | a+b                                                                                               | a and b are algebraic expressions                                                        | the sum of a and b                                                                                    |

| -          | a-b                                                                                               | a and b are algebraic expressions                                                        | the difference of a and b                                                                             |

| <          | a <b< td=""><td>a and b are algebraic expressions</td><td>true if a is less than b</td></b<>      | a and b are algebraic expressions                                                        | true if a is less than b                                                                              |

| ¬<         | a¬ <b< td=""><td>a and b are algebraic expressions</td><td>true if a is not less than b</td></b<> | a and b are algebraic expressions                                                        | true if a is not less than b                                                                          |

| =          | a=b                                                                                               | a and b are algebraic expressions                                                        | true if a is equal to b                                                                               |

| <b>¬</b> = | a                                                                                                 | a and b are algebraic expressions                                                        | true if a is not equal to b                                                                           |

| <=         | a <=b                                                                                             | a and b are algebraic expressions                                                        | true if a is less than or equal to b                                                                  |

| >          | a >.b                                                                                             | a and b are algebraic expressions                                                        | true if a is greater than b                                                                           |

| □ >        | a¬>b                                                                                              | a and b are algebraic expressions                                                        | true if a is not greater than b                                                                       |

| >=         | a>=b                                                                                              | a and b are algebraic expressions                                                        | true if a is greater than or equal to b                                                               |

| गंद गंद    | a**b                                                                                              | a and b are logical expressions                                                          | logical product of a and b (AND)                                                                      |

| ++         | a++b                                                                                              | a and b are logical expressions                                                          | logical sum of a and b (OR)                                                                           |

|            | ab                                                                                                | a and b are logical expressions                                                          | logical difference of a and b (exclusive OR)                                                          |

| ==         | a==b                                                                                              | a and b are logical expressions                                                          | logical equivalence of a and b                                                                        |

time. The assembler will denote as an error any attempts to do arithmetic operations on double length floating point numbers in expressions, or on character strings longer than four characters.

Certain logical operations (\*\*, ++, --, and ==) and all relational operations may be performed on values that require more than four characters (32 bits) to represent them.

#### 2-17. SUBEXPRESSIONS

An expression may contain subexpressions, and subexpressions may contain other subexpressions. A subexpression is an expression enclosed in parentheses, and it may appear wherever an item is valid. Subexpressions are evaluated before other items in an expression, and the innermost subexpression is evaluated first.

The value of an item or expression is right-justified in its generated result field, and unspecified leading bit positions will contain zeros; character strings are left-justified with blanks filled to the right in the last word for unjustified characters.

Note: Character strings used in immediate operands (see Topic 6-32) are not left-justified in a fullword, but justified in the 16-bit N field. Thus, a character string immediate operand has a maximum of two characteriers, and the rightmost byte is blank filled if there is only one character in the string.

The value of the part of the expression or subexpression containing and affected by a relational operator (e.g., >, <, or =) is equated to one if the relation is true and equated to zero if the relation is false. For example, if E is an expression of the form:

X > Y

then, E is evaluated as a one (1) if the relation is true, or zero (0) if the relation is false. Also, if the assigned section of expression X is not the same as the assigned section of expression Y, then the expression E cannot be completed and is evaluated as false (zero).

## Examples:

1. The following expression is evaluated as zero if R is a relocatable item:

R - 4 > 37

2. The following expression is evaluated as zero if the subexpression (X > Y) is false and equal to A if the subexpression (X > Y) is true:

A\*(X>Y)

## 2-18. ASSUMED PARENTHESES

The following examples denote how parentheses are assumed, the results being governed by the hierarchies in Table 2-3.

Expression: -A//-I\*2

Method: 1. Two's complement A

2. Two's complement I

3. Shift two's complement of A by value of two's complement of I

4. Multiply result by two

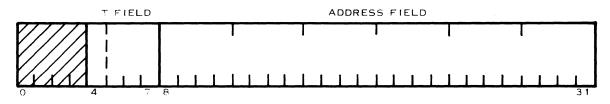

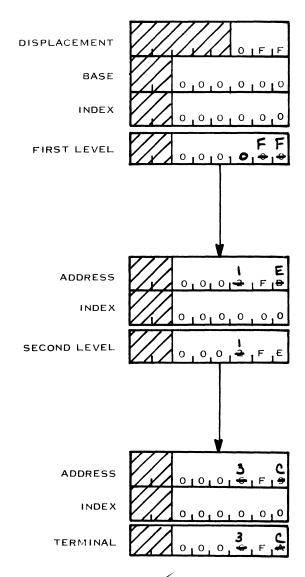

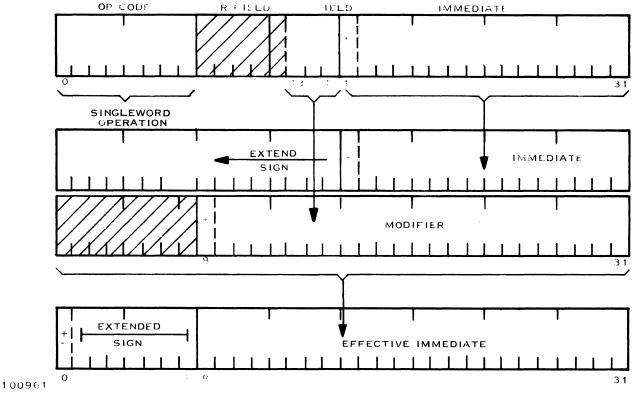

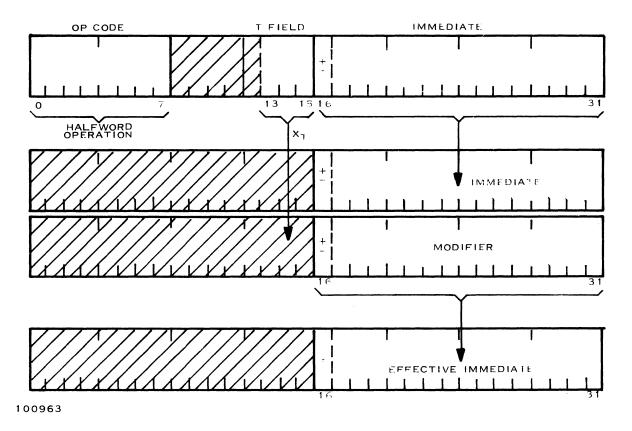

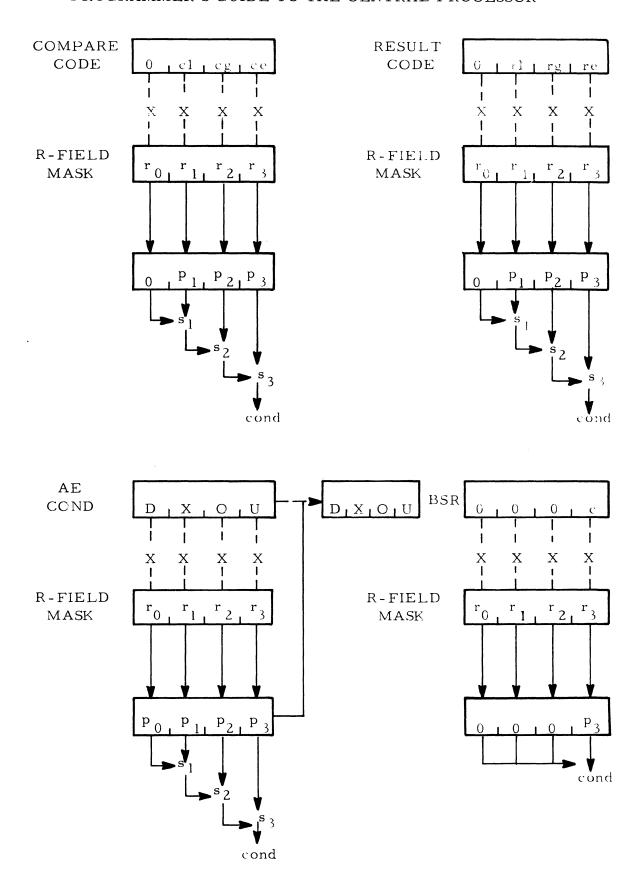

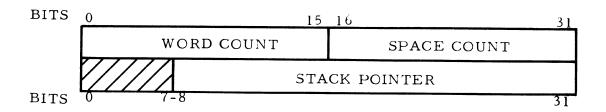

Assumes: ((-A)//(-I))\*2