# **MANUAL REVISION STATUS**

# PRODUCT: 4114 Computer Display Terminal

This manual supports the following versions of this product: Serial Numbers B010100 and up

| REV. | DATE     | DESCRIPTION    |

|------|----------|----------------|

| @    | JUN 1981 | Original Issue |

|      |          |                |

|      |          |                |

|      |          |                |

|      |          |                |

|      |          |                |

|      |          |                |

|      |          |                |

|      |          |                |

| 1    |          |                |

|      |          |                |

|      |          |                |

|      |          |                |

|      |          |                |

|      |          |                |

|      |          |                |

|      |          |                |

|      |          |                |

|      |          |                |

|      |          |                |

| 1    |          |                |

|      |          |                |

## CONTENTS

| Section | 1 | INTRODUCTION Related Documents General Description Physical Description Options Accessories                                                                                                                                                          | 1-1<br>1-3<br>1-5                                        |

|---------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Section | 2 | CHARACTERISTICS  General Information Introduction to the Display Module Description of the Display Module Hardware Display Features Introduction to the Pedestal Description of the Pedestal Specifications                                          | 2-1<br>2-2<br>2-2<br>2-3<br>2-4<br>2-4                   |

| Section | 3 | OPERATING INFORMATION Operating Controls Getting Started Turning on the 4114 Getting the Terminal Ready Setup Mode The Dialog Area 4010 Compatibility. Programming Keys Creating a Graphics Segment. Manipulating a Graphics Segment. Graphics Input | 3-5<br>3-6<br>3-7<br>3-8<br>3-12<br>3-12<br>3-17<br>3-22 |

| Section | 4 | INTRODUCTION TO THEORY OF OPERATION Introduction                                                                                                                                                                                                     | 4-2                                                      |

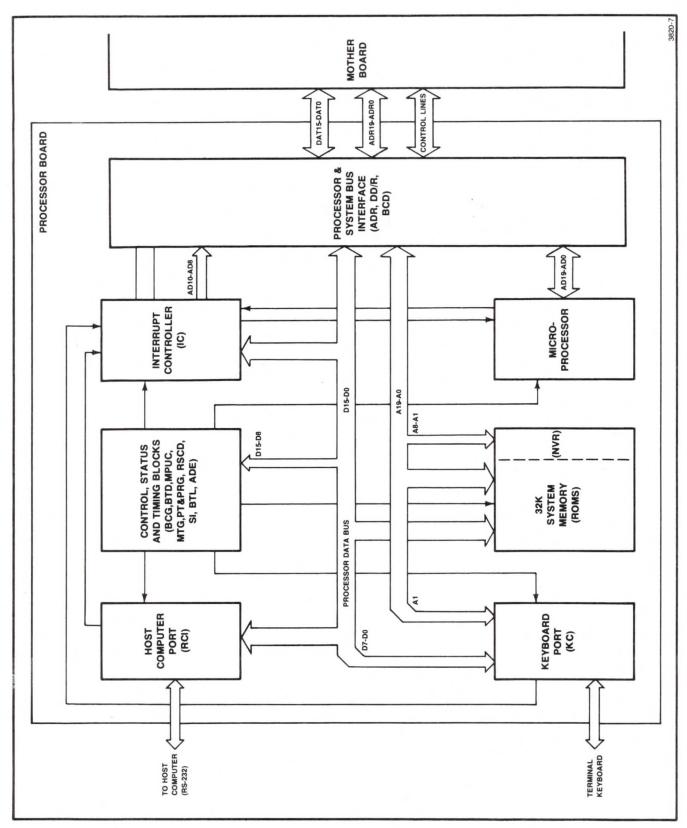

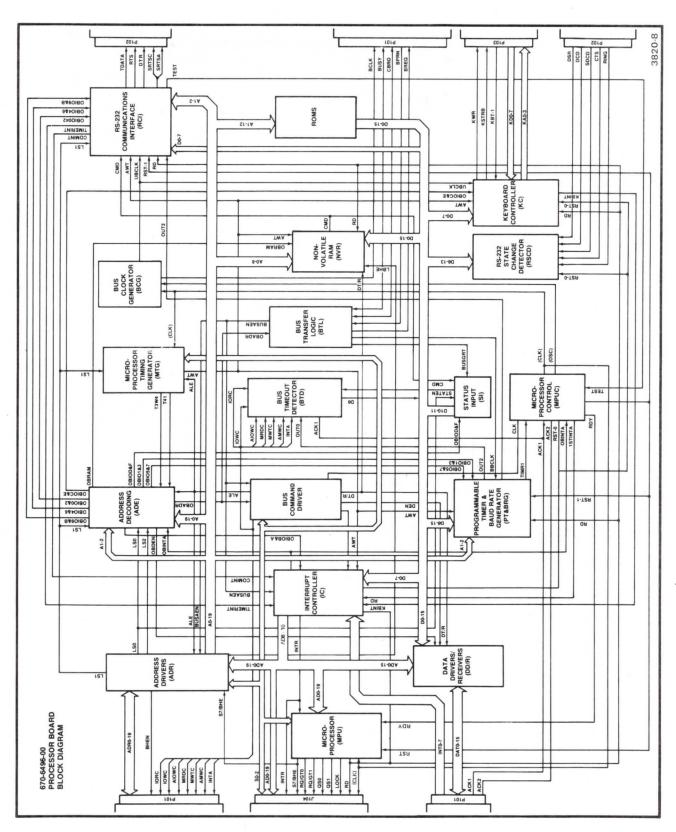

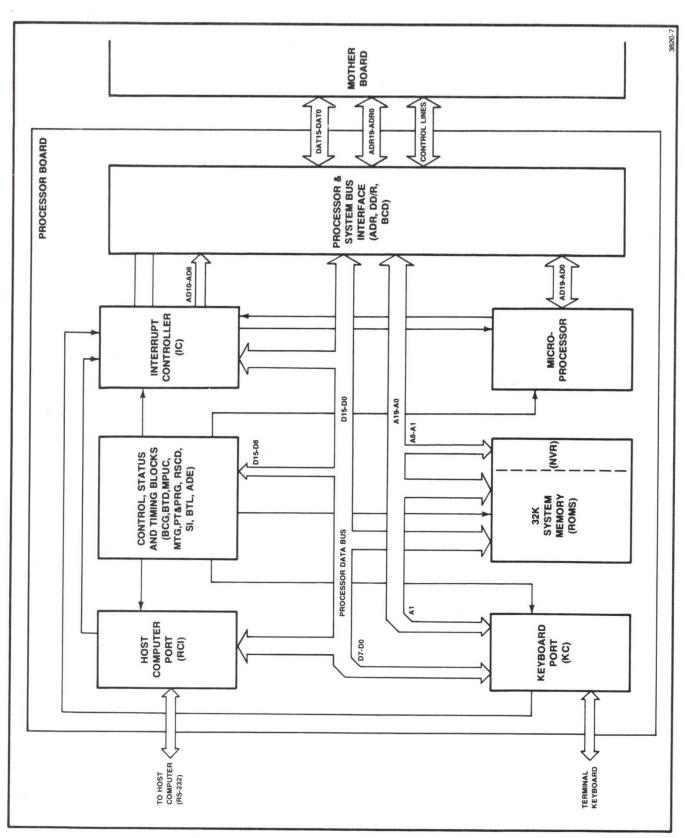

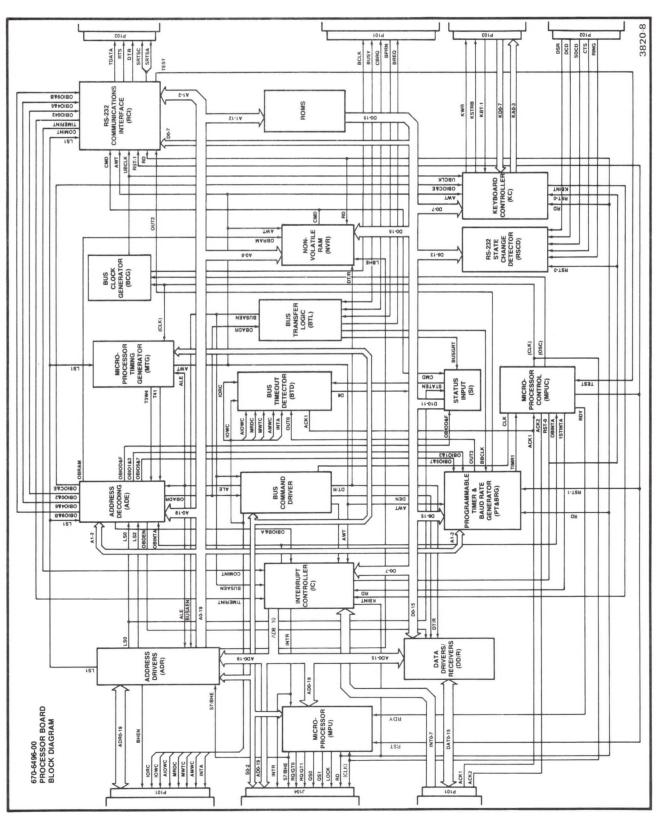

| Section | 5 | PROCESSOR KEYBOARD CIRCUIT THEORY Introduction to the Processor Board Microprocessor                                                                                                                                                                 | 5-2<br>5-3<br>5-3<br>5-3                                 |

| Section 5 | Host Computer Port<br>Keyboard Port                                                                                                                                                                                                               |         | <b>age</b><br>-5<br>-5                                            |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------------------------------------|

|           | Detailed Processor Board Circ Descriptions                                                                                                                                                                                                        | uit     | -5<br>-1235268260235<br>-2235268260235<br>-3460235<br>-5565177901 |

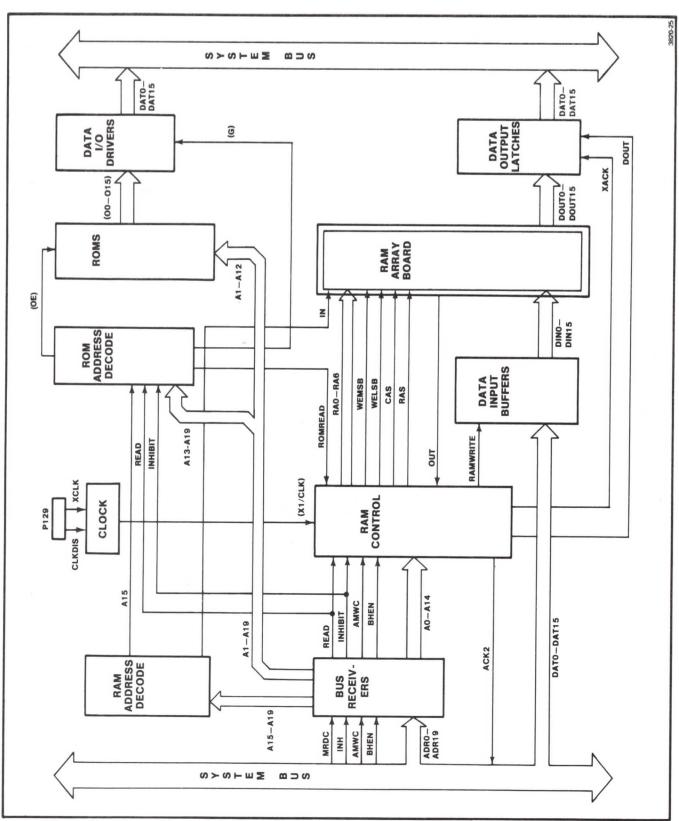

| Section 6 | THEORY OF OPERATION OF RAM/RO Introduction to RAM/ROM Board General Description General Operation Bus Receivers RAM Control Data Input Buffers RAM Array Board Data Cutput Latches RAM Address Decode ROM Address Decode ROMs Data Output Drivers | M BOARD | -1<br>-1<br>-4<br>-6<br>-12<br>-13<br>-15<br>-17<br>-18<br>-20    |

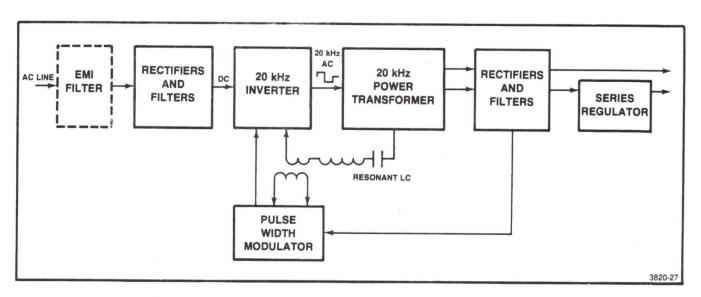

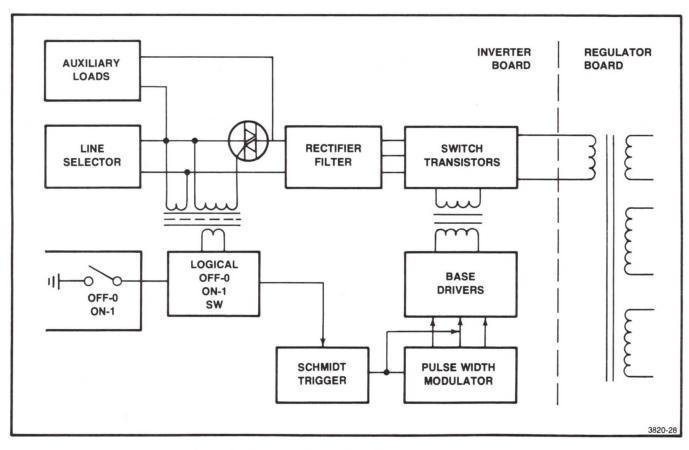

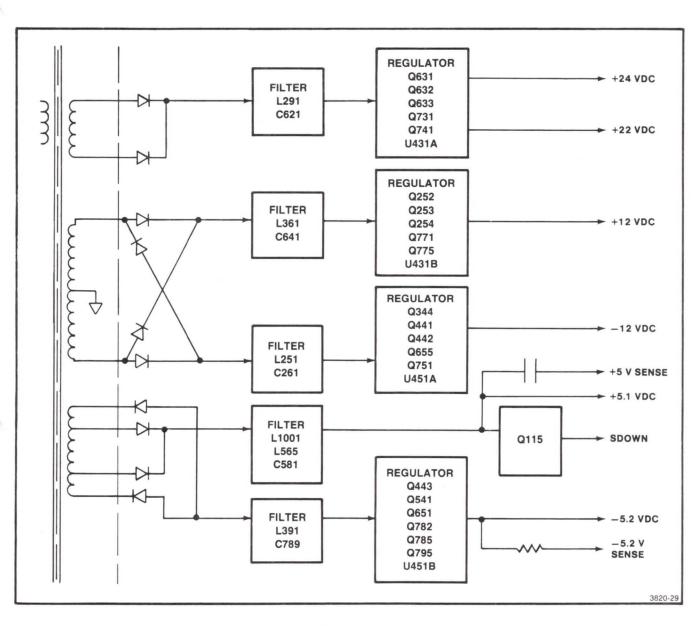

| Section 7 | THEORY OF OPERATION OF POWER SUPPLY Inverter Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .7-3<br>.7-4<br>.7-4<br>.7-5                                                                                          |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

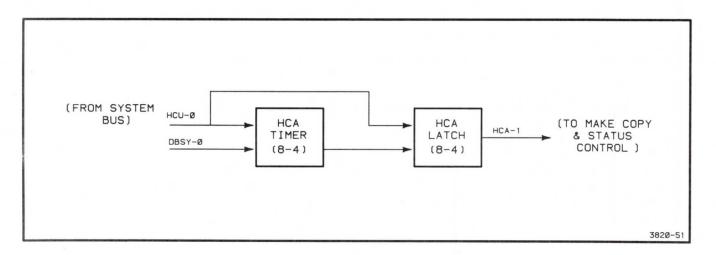

| Section 8 | THEORY OF OPERATION OF DISPLAY ELECTRONICS Introduction Display Controller Address Decode Status Control Test Status Driver Command Latch Initiate Command Command Decode DMA Control Jump Address Latches Jump Address Multiplexer Address Controllers Scaling Control Address Drivers Vector Control Pipeline Register Vector Timing Dot-Dash Generator HCU Availability Make Copy Erase Ready for Vector Vector Generator Vector Generator Vector Generator Vector Timing Vector Timing X Data Handler Data Multiplexer Shift Register Latch Rate Multiplier Counter Scissoring Extend DAC Processing | . 8 - 2 4 7 7 7 7 7 8 2 4 5 8 - 2 4 7 7 7 7 7 8 2 4 5 8 - 2 6 7 8 8 - 2 8 8 - 2 8 6 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 |

|           | X DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .8-50                                                                                                                 |

| Section 8  | Cont)       Page         Offset Current       8-50         X Slew Rate Amplifier       8-50         X Integrator       8-51         TC Power       8-51         X Current Switch       8-51         X Decoder       8-52         1.3 Volt Power       8-53         Absolute Position Level Translator       8-53         Z Axis Controller       8-53 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 9  | THEORY OF OPERATION OF DVST DISPLAY MODULE Introduction                                                                                                                                                                                                                                                                                               |

| Section 10 | ADJUSTMENT PROCEDURES Introduction                                                                                                                                                                                                                                                                                                                    |

| Section 11 | MAINTENANCE Page                            |

|------------|---------------------------------------------|

|            | Introduction11-1                            |

|            | Self Test Diagnostic Program11-1            |

|            | Routine Maintenance11-2                     |

|            | Cleaning                                    |

|            | Visual Inspection                           |

|            | Troubleshooting Information11-5             |

|            | Controls and Operation11-5                  |

|            | Characteristics11-6                         |

|            | Self Test1-6                                |

|            | Block Diagrams and Circuit Diagrams11-6     |

|            | Component Layout Illustrations11-7          |

|            | Recommended Troubleshooting Equipment11-7   |

|            | Parts Replacement11-7                       |

|            | Connectors11-8                              |

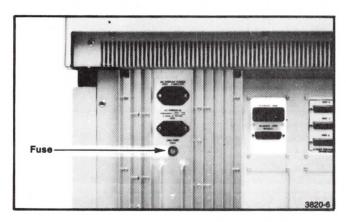

|            | Fuses11-9                                   |

|            | Semiconductors11-10                         |

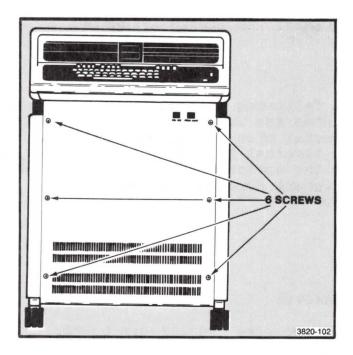

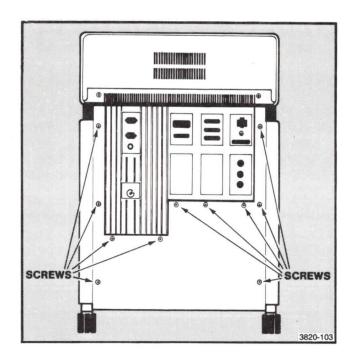

|            | Removal/Replacement ProceduresDisplay       |

|            | Module                                      |

|            | Cabinet                                     |

|            | Circuit Module11-16                         |

|            | Crt Module11-19                             |

|            | Reconfiguring the CRT Module11-32           |

|            | Selecting X and Y Axis Inputs11-37          |

|            | Removal/Replacement ProcedurePedestal.11-39 |

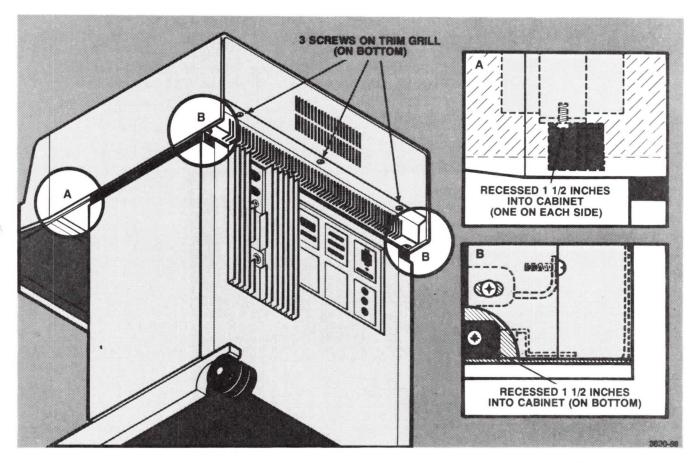

|            | Cabinet11-39                                |

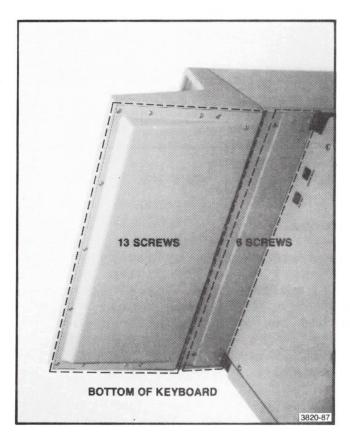

|            | Keyboard Removal11-44                       |

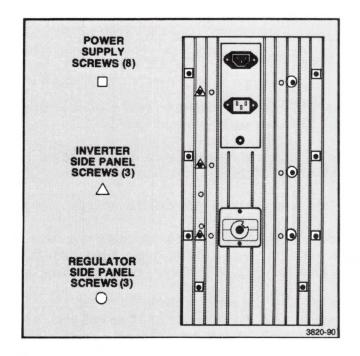

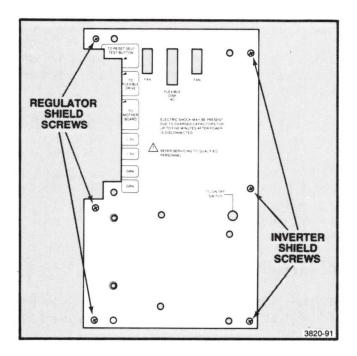

|            | Power Supply Module11-45                    |

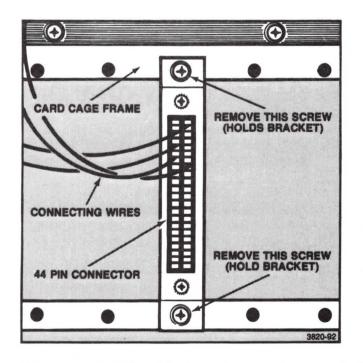

|            | Card Cage11-51                              |

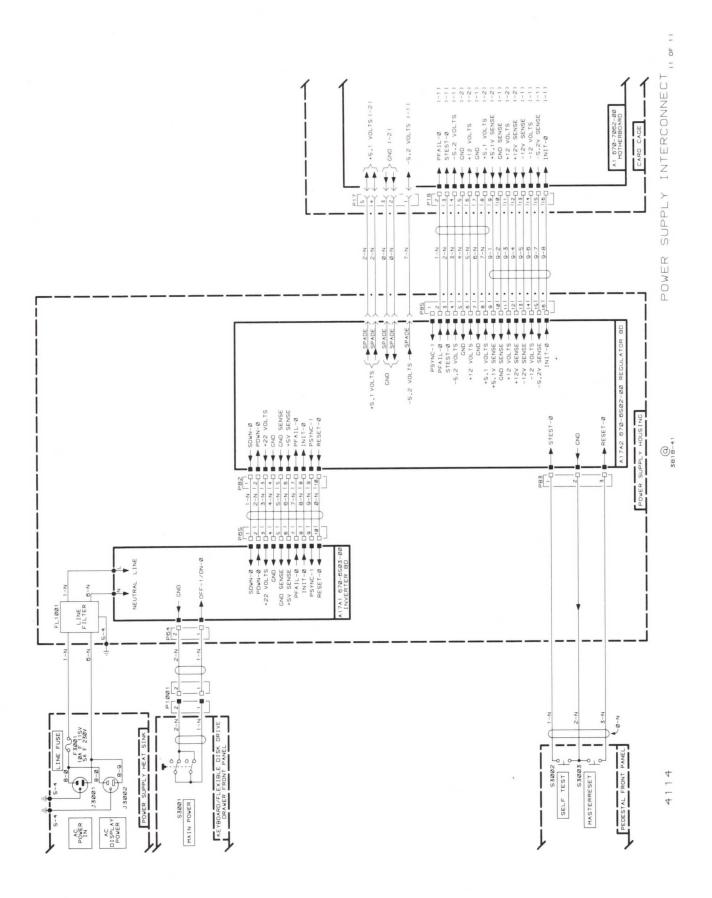

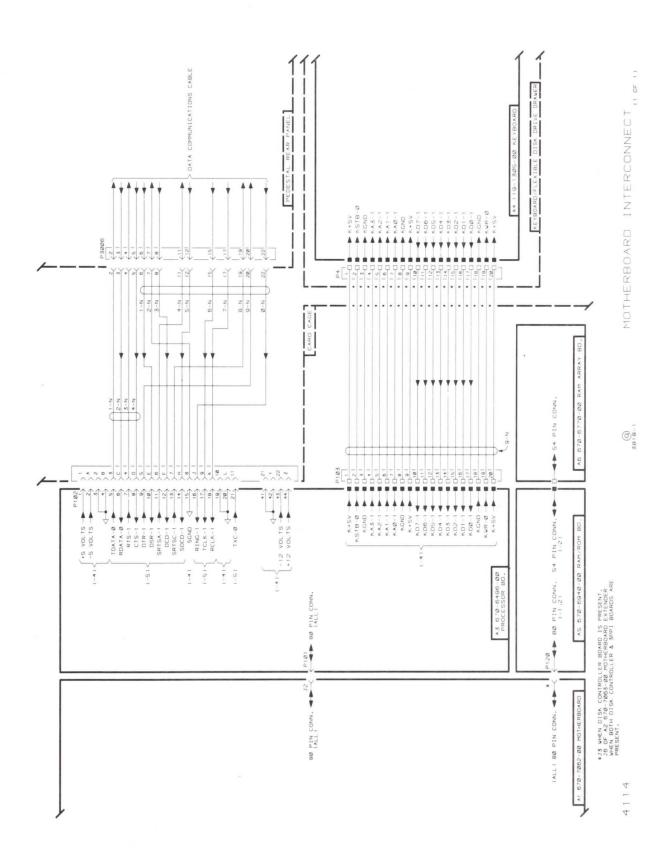

| Section 12 | INTERCONNECT AND BLOCK DIAGRAMS             |

| Appendix A | SIGNAL LIST                                 |

| Appendix B | OPTIONS                                     |

| Appendix C | BOARD STRAPS                                |

| Appendix D | ASCII CODE CHARTS                           |

| Appendix E | SELF TEST                                   |

| Appendix F | DISPLAY LIST COMMANDS                       |

# TABLES

| Table                                                                                                                                                                                | Description                                                                                                                                                                                                                                                                                     | Page                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-1<br>2-2-3<br>2-3<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-1<br>2-2<br>2-7<br>2-1<br>2-3<br>2-1<br>2-3<br>2-1<br>2-3<br>2-3<br>2-3<br>2-3<br>2-3<br>2-3<br>2-3<br>2-3<br>2-3<br>2-3 | Environmental Specifications                                                                                                                                                                                                                                                                    | 2-7<br>2-8<br>2-10<br>2-13<br>2-14<br>2-15<br>2-19<br>3-16<br>3-23<br>3-25<br>5-38-5<br>5-38-6<br>5-3487<br>8-6<br>8-18<br>9-725<br>10-2<br>11-10<br>0-1 |

| D-4<br>D-5<br>D-6<br>E-1<br>E-2<br>E-3<br>E-4<br>E-5                                                                                                                                 | Characters Used in <int-report> Parameters Characters Used in <xy> Parameters Characters Used in <xy-report> Parameters Self Test Errors Directory Keyboard/Processor Board Errors Processor Board Errors RAM/Bus and Host Port Errors Hex-to-Decimal Equivalents</xy-report></xy></int-report> | D-5<br>D-6<br>E-4<br>E-7<br>E-9<br>E-11                                                                                                                  |

| Table | Description                                     | Page |

|-------|-------------------------------------------------|------|

| E-6   | System/Option ROMs Errors                       | E-16 |

| E-7   | ROM Test Errors                                 |      |

| E-8   | CMOS Memory Errors                              | E-20 |

| E-9   | Display Controller, Vector Generator, and Displ |      |

|       | Module Errors                                   |      |

| E-10  | Self Test/Power Up Tests Sequence               | E-26 |

| E-11  | 3PPI Errors                                     | E-28 |

| E-12  | Disk Option Errors                              | E-31 |

| E-13  | Tablet Errors                                   | E-38 |

| F-1   | Display List Command Bit Patterns               | F-2  |

# ILLUSTRATIONS

| Figure                                 | Description                                                                    | Page                            |

|----------------------------------------|--------------------------------------------------------------------------------|---------------------------------|

| 2-1<br>3-1<br>3-2<br>3-3<br>5-1<br>5-2 | 4114 Dimensions                                                                | 3-3<br>3-3<br>3-4<br>5-2<br>5-7 |

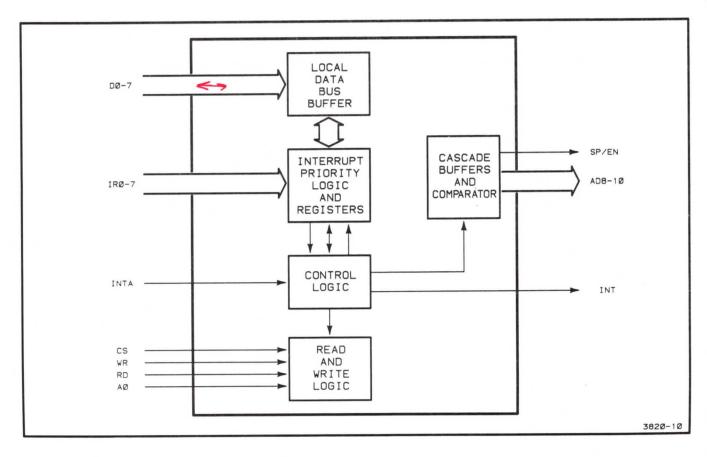

| 5-3<br>5-4                             | Programmable Interrupt Controller Block Diagram                                |                                 |

| 5-5                                    | Programmable Interrupt Controller Pin Descriptions                             | 5-17                            |

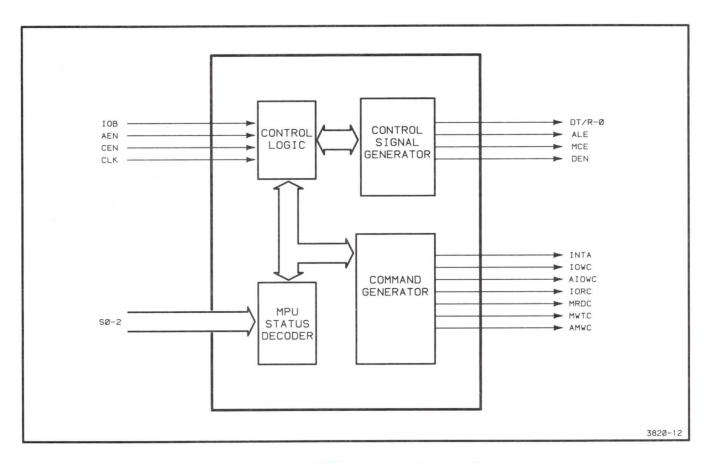

| 5-6<br>5-7<br>5-8                      | Bus Controller Block Diagram                                                   | 5-28                            |

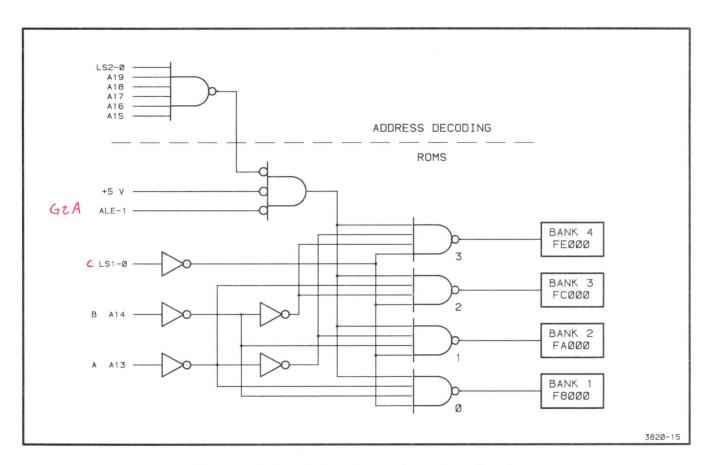

| 5 <b>-</b> 9<br>5 <b>-</b> 10          | ROMs Bank Decoder Logic                                                        | 5 <b>-</b> 35                   |

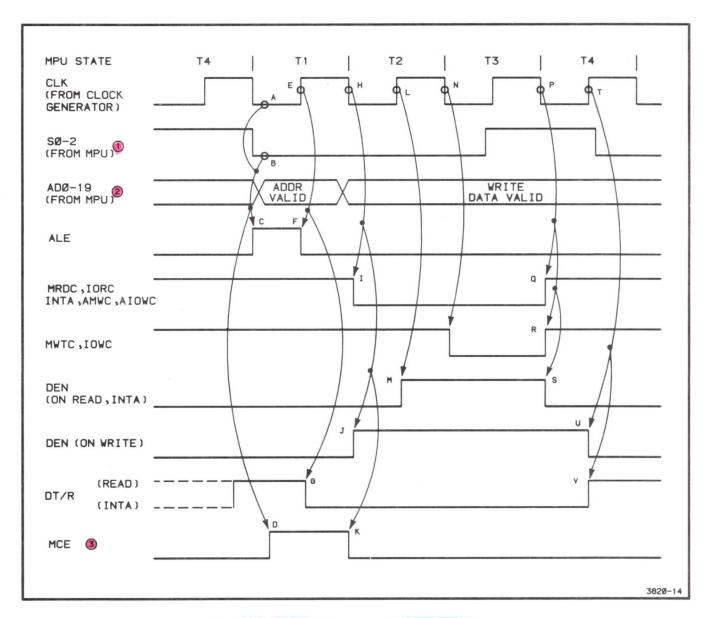

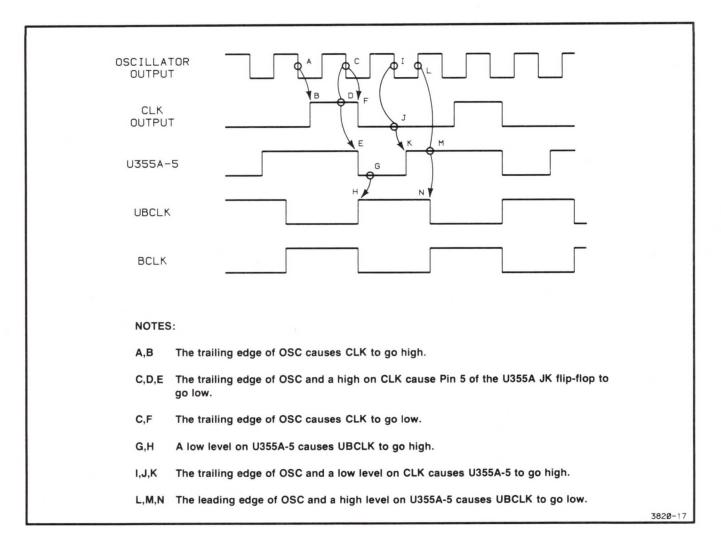

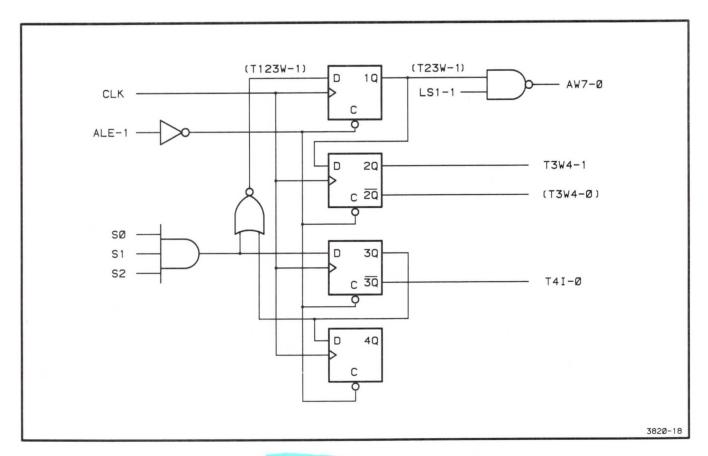

| 5-11<br>5-12<br>5-13                   | Bus Clock Generator Timing                                                     | 5-56                            |

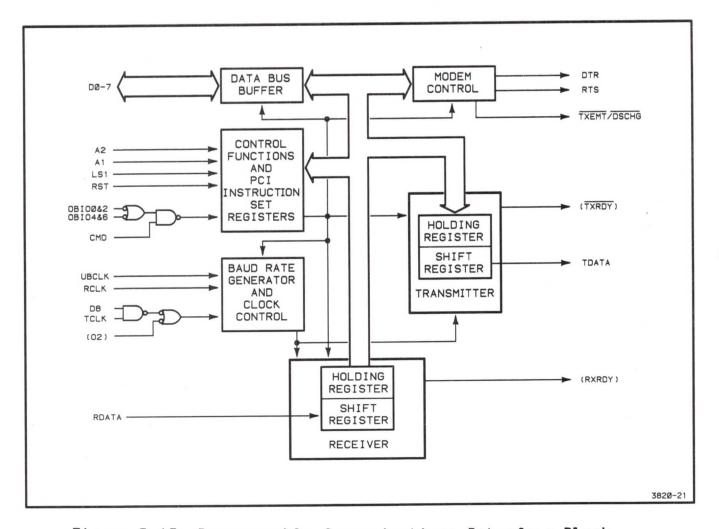

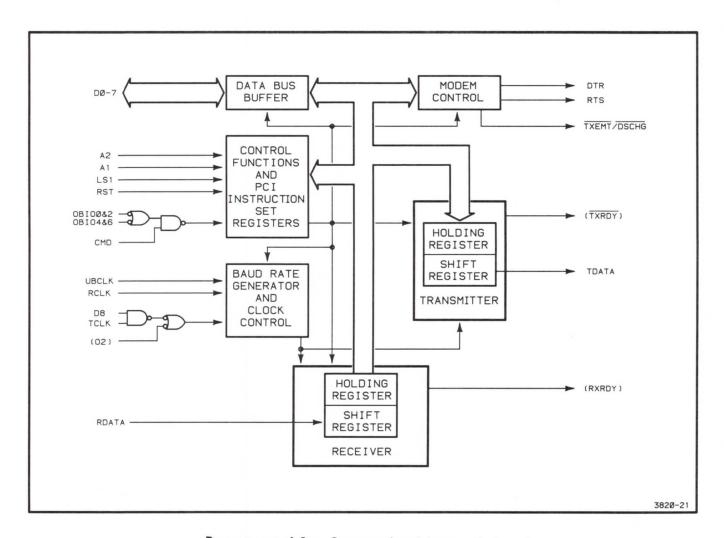

| 5-14                                   | Programmable Communications Interface Pin Descriptions                         |                                 |

| 5-15                                   | Programmable Communications Interface Block Diagram                            | 5-68                            |

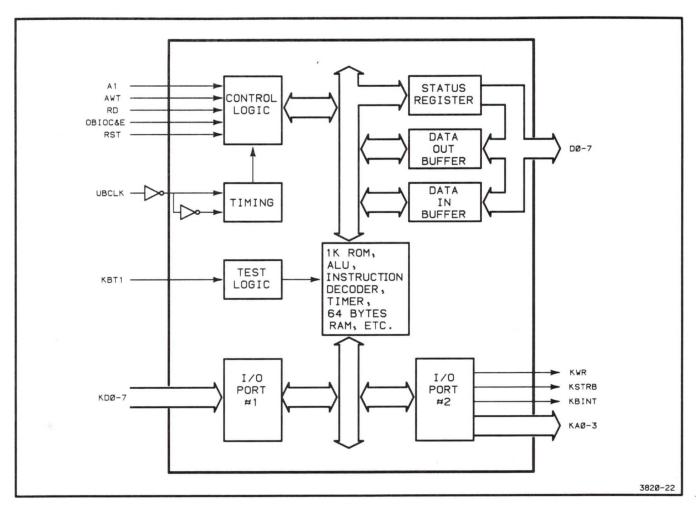

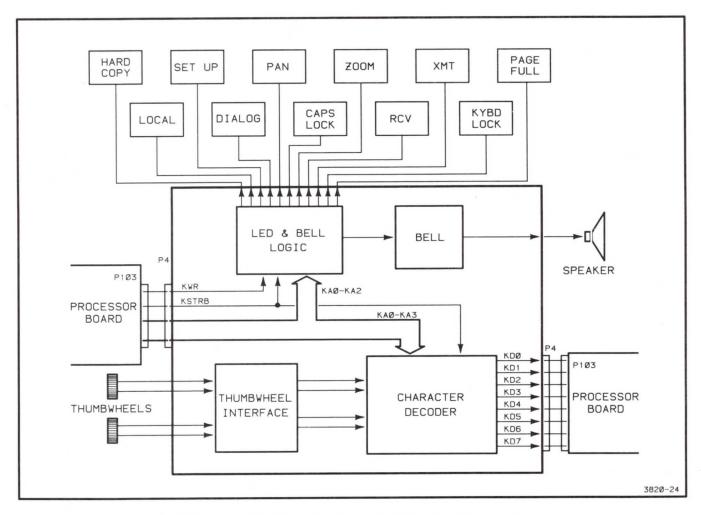

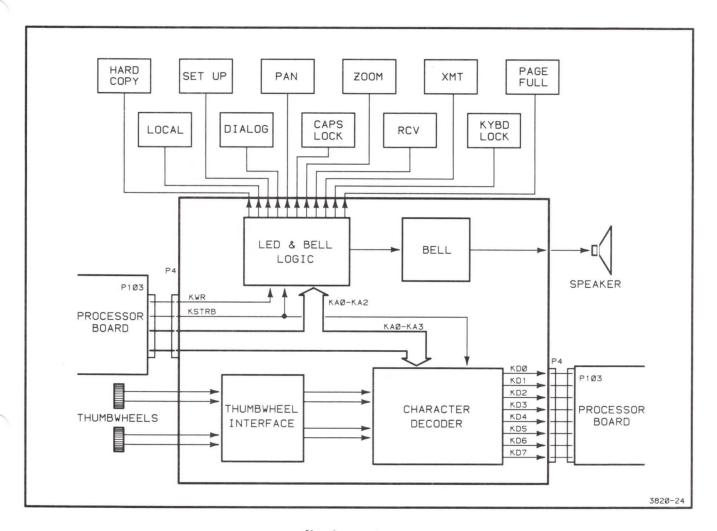

| 5 <b>-</b> 16                          | Keyboard Controller Microprocessor Block Diagram                               | 5-73                            |

| 5-18                                   | Descriptions                                                                   | 5-74<br>5-78                    |

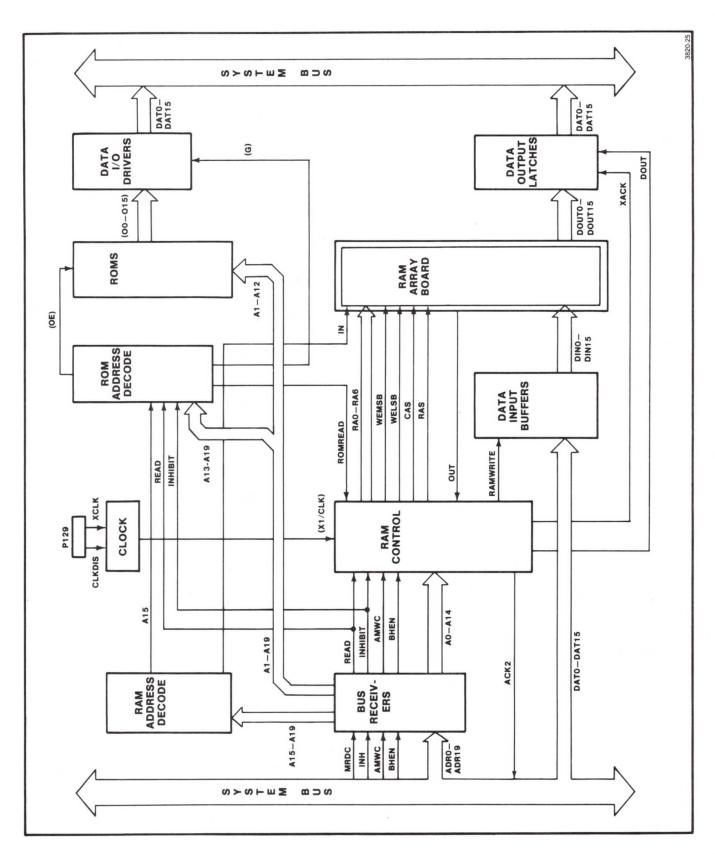

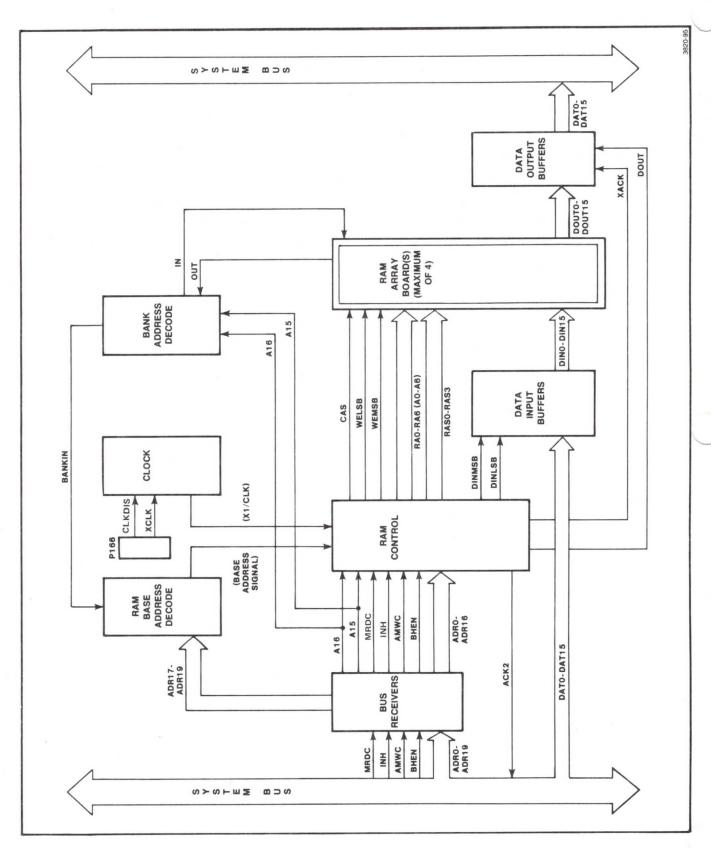

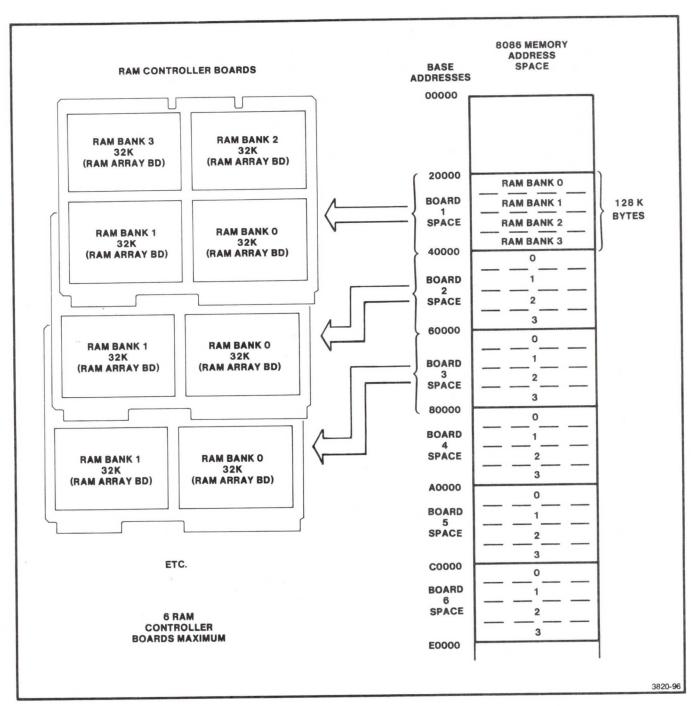

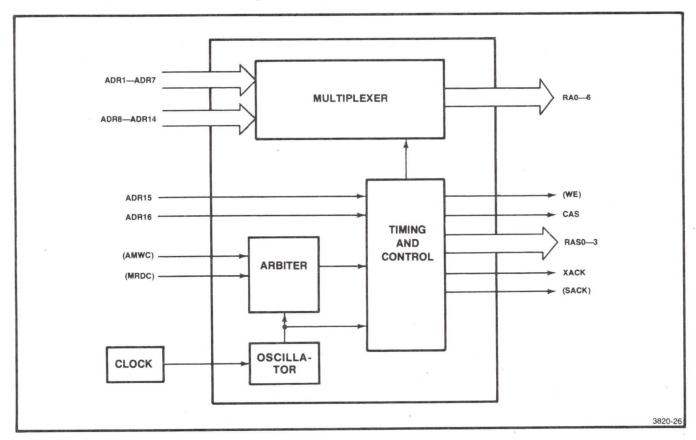

| 6-1<br>6-2                             | RAM/ROM Block Diagram                                                          | 6-2                             |

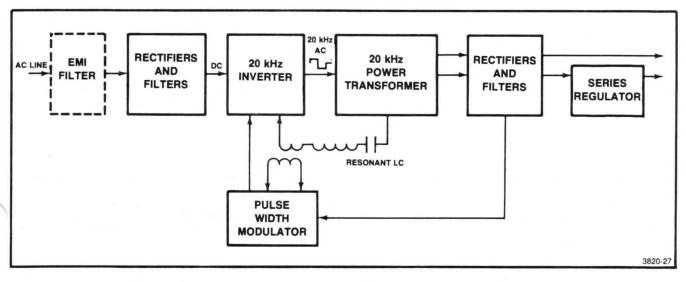

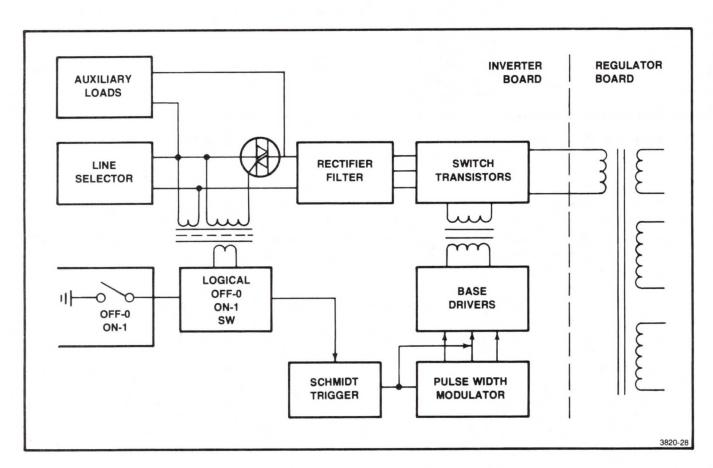

| 7-1                                    | Simplified Block Diagram of a High Efficiency Power Supply                     | 7-1                             |

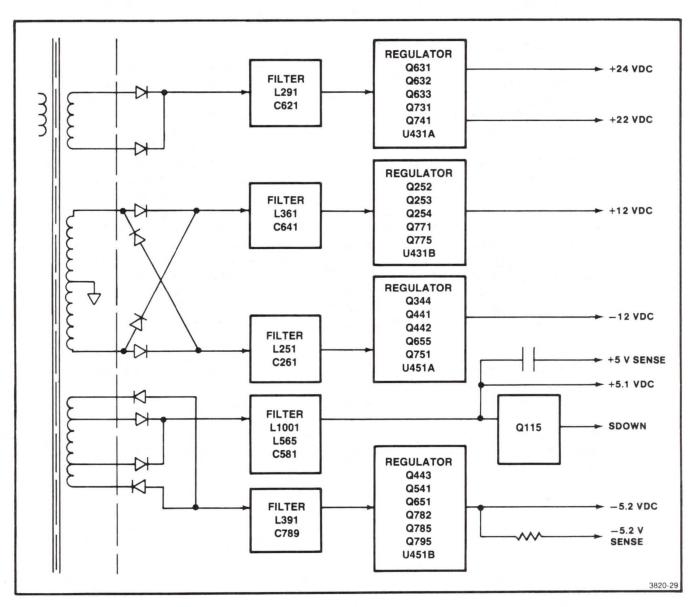

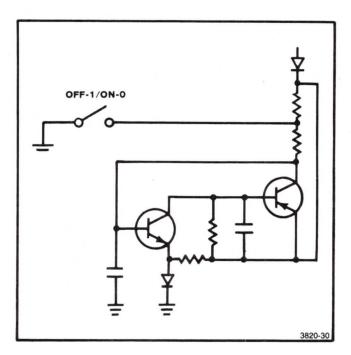

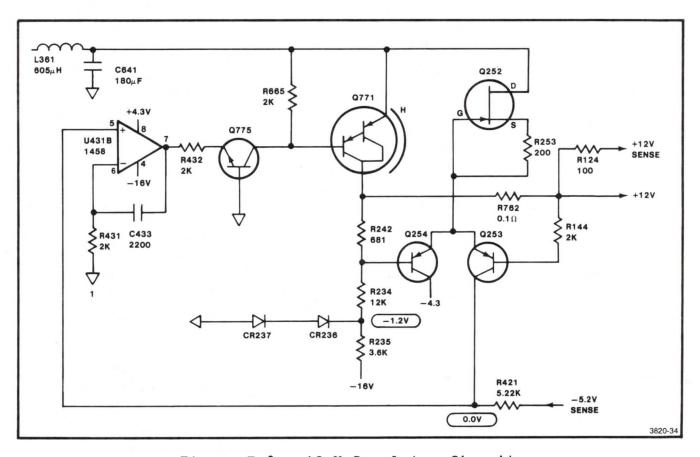

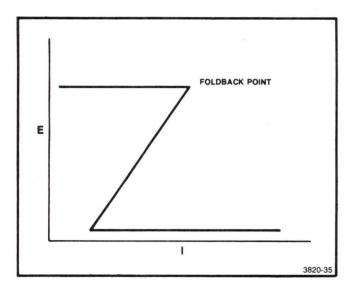

| 7-2<br>7-3<br>7-4                      | Functional Block Diagram of Regulator Board  Logical OFF-1/ON-0 Switch         | 7-3                             |

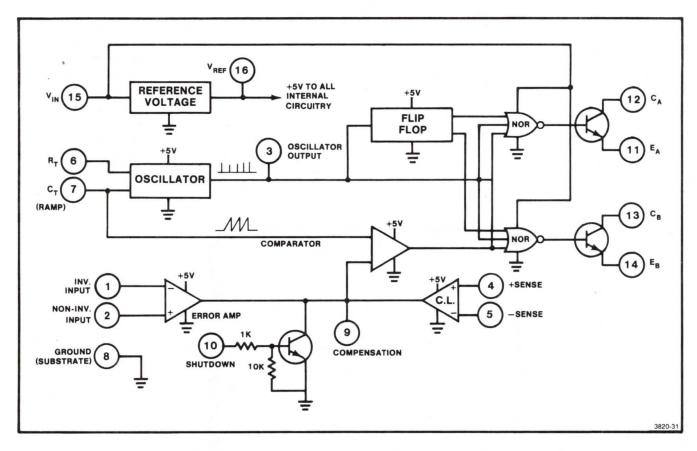

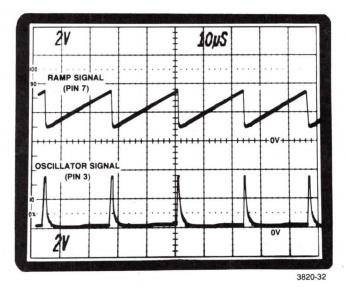

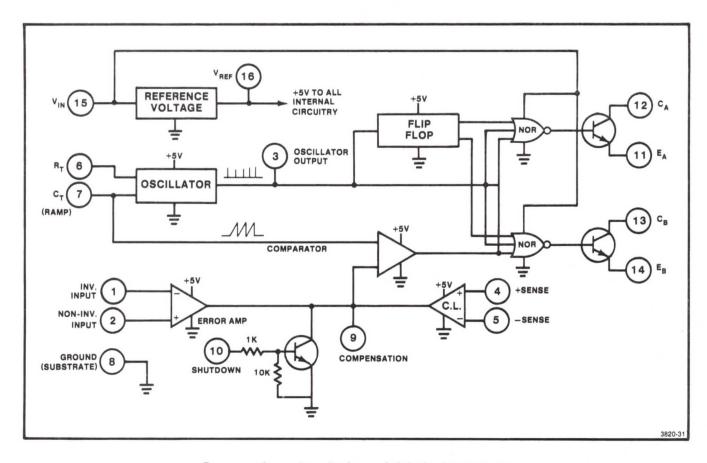

| 7-5<br>7-6                             | Pulse Width Modulator Block Diagram PWM Comparator Input and Oscillator Output | 7-7                             |

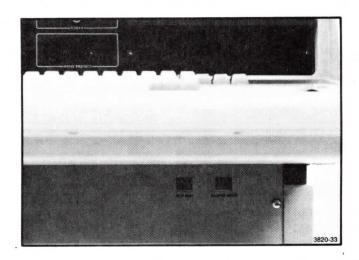

| 7-7<br>7-8<br>7-9                      | SELF-TEST and RESET Buttons                                                    | 7-11                            |

| Figure                                                      | Description                                                                                                                                                                                                                                                                                                                                 | Page                                     |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

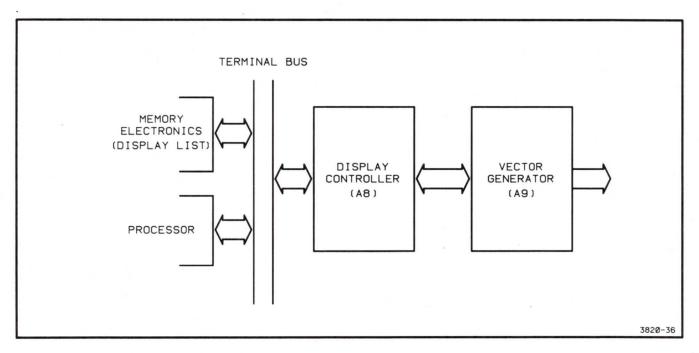

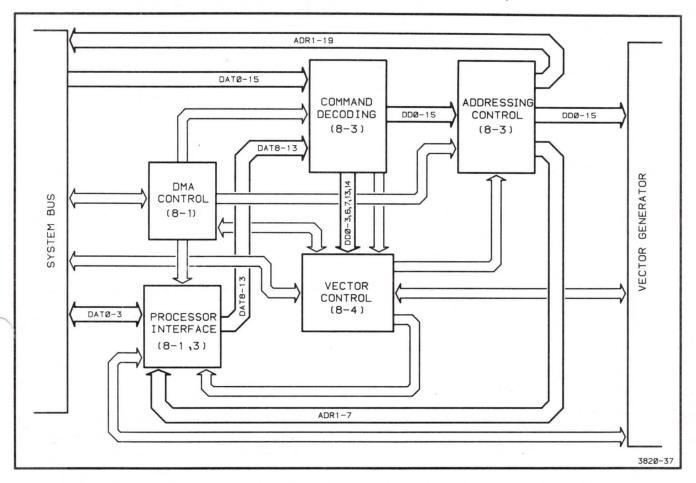

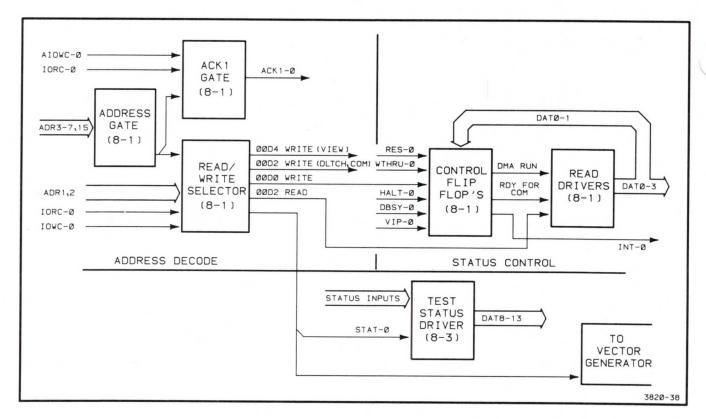

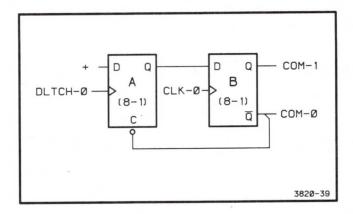

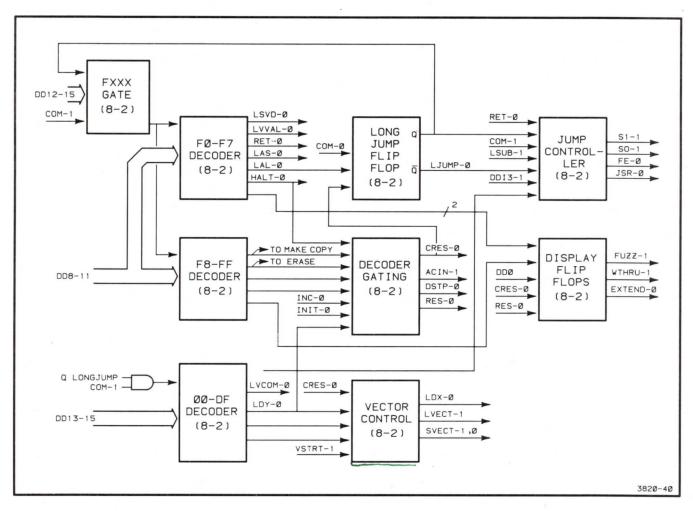

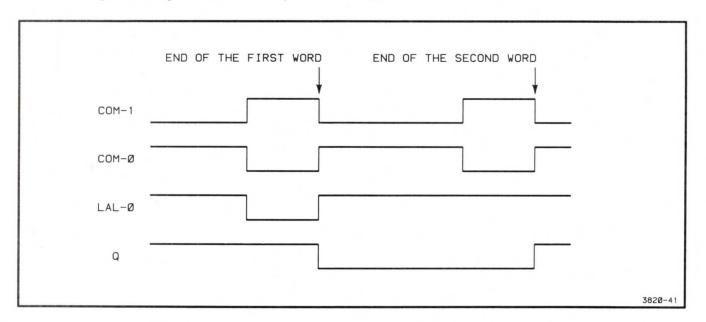

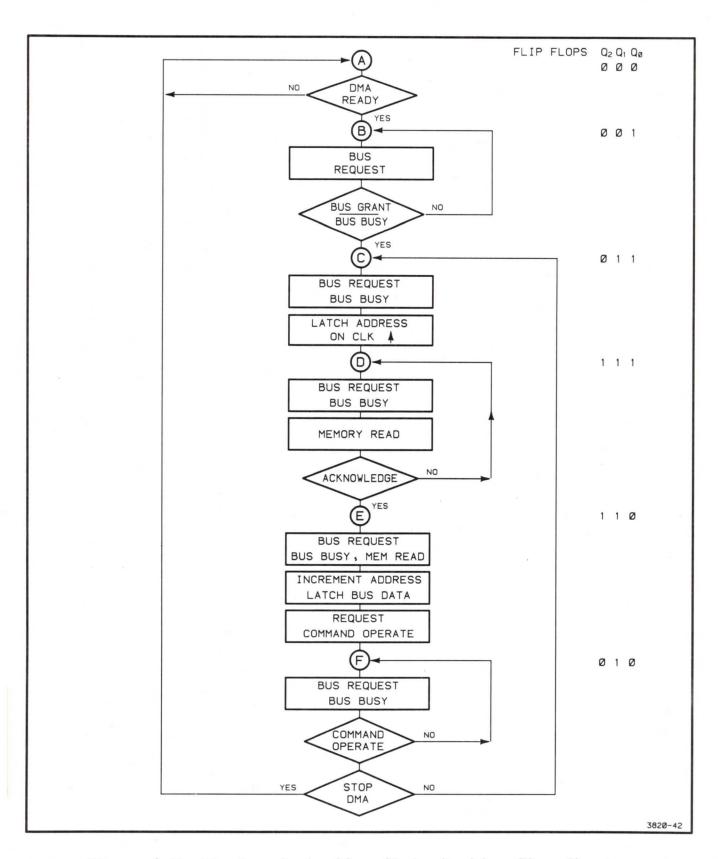

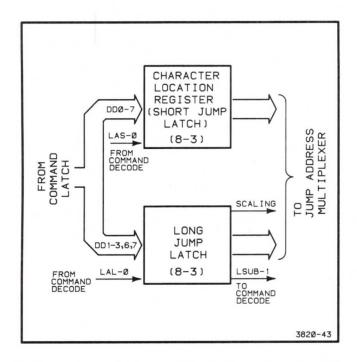

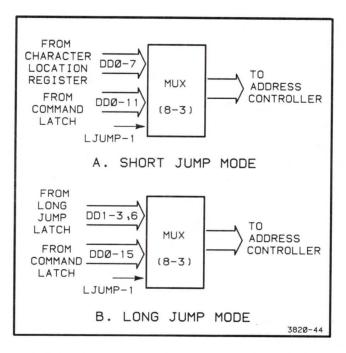

| 8-1<br>8-2<br>8-3<br>8-4<br>8-5<br>8-6<br>8-7<br>8-8<br>8-9 | Display Control Circuitry Block Diagram  Display Controller Simplified Block Diagram  Processor Interface Simplified Block Diagram  Initiate Command Logic Diagram  Command Decode Logic Diagram  Long Jump Timing Signals  Display Controller State Machine Flow Chart  Jump Address Latches Logic Diagram  Jump Address Multiplexer Modes | 8-3<br>8-4<br>8-8<br>8-9<br>8-10<br>8-13 |

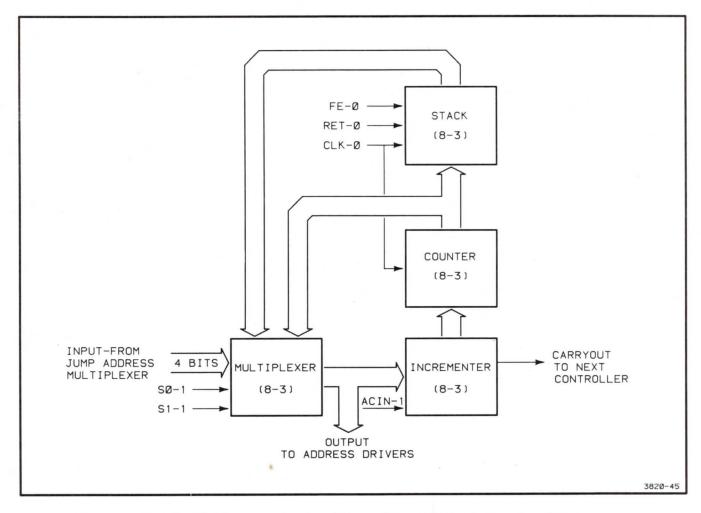

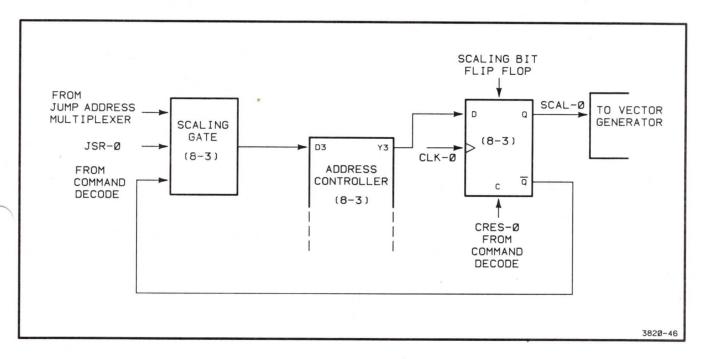

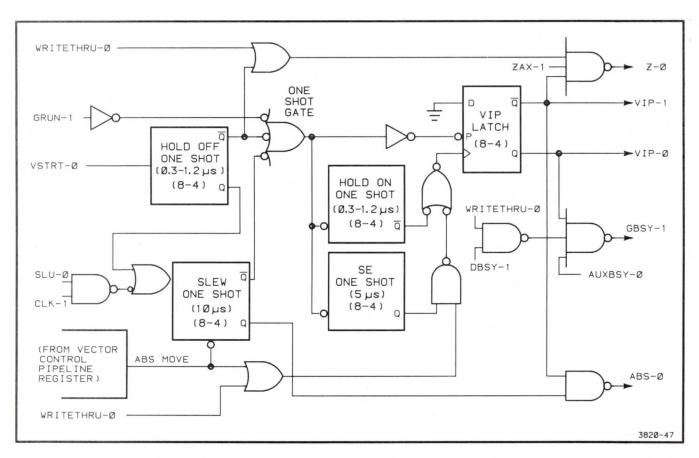

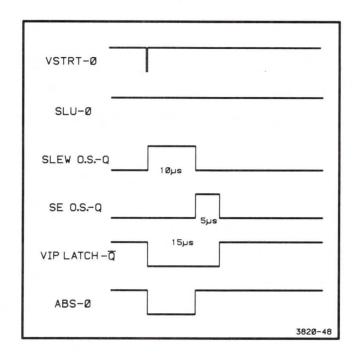

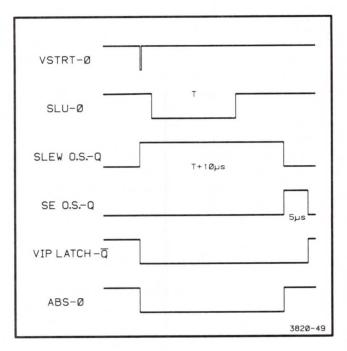

| 8-10<br>8-11<br>8-12<br>8-13                                | Address Controller Simplified Logic Diagram Scaling Control Logic Diagram Vector Timing Simplified Logic Diagram Timing Diagram for Absolute Postioning Without Slewing                                                                                                                                                                     | 8-17<br>8-19<br>8-22                     |

| 8-14                                                        | Timing Diagram for Absolute Positioning With Slewing                                                                                                                                                                                                                                                                                        |                                          |

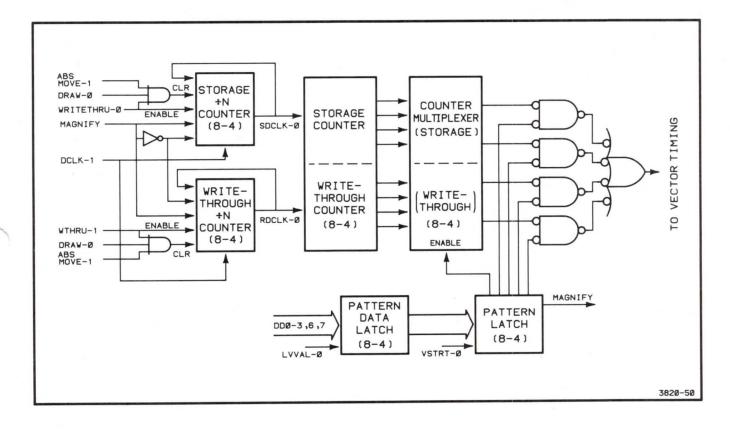

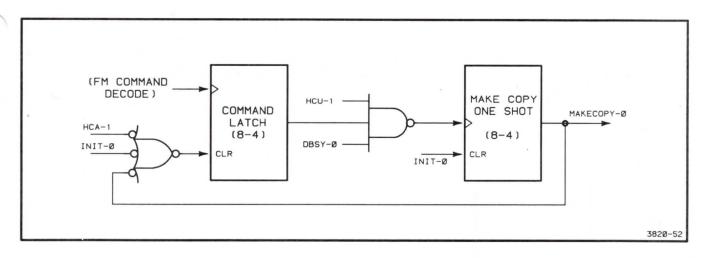

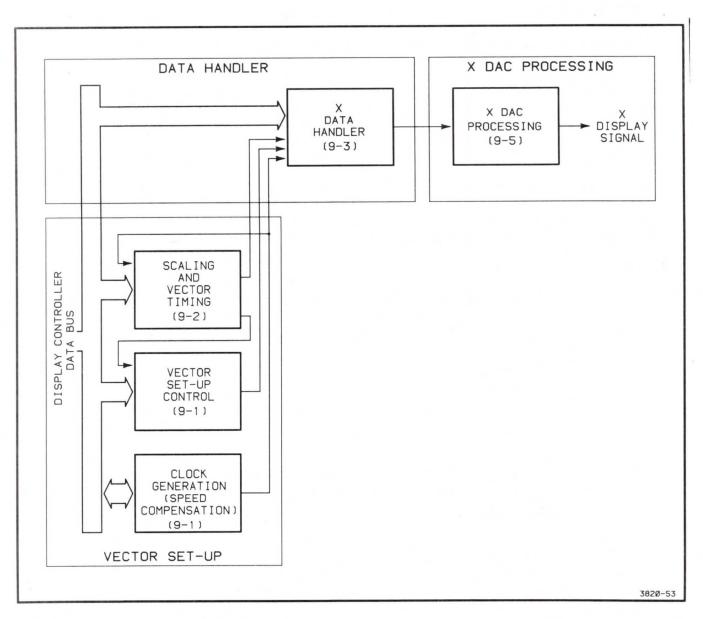

| 8-15<br>8-16<br>8-17<br>8-18<br>8-19                        | Dot-Dash Generator Simplified Logic Diagram  Availability Simplified Logic Diagram  Make Copy Simplified Logic Diagram  Vector Generator Simplified Block Diagram  Vector Set-Up State Machine Block Diagram                                                                                                                                | .8-25<br>.8-26<br>.8-27<br>.8-30         |

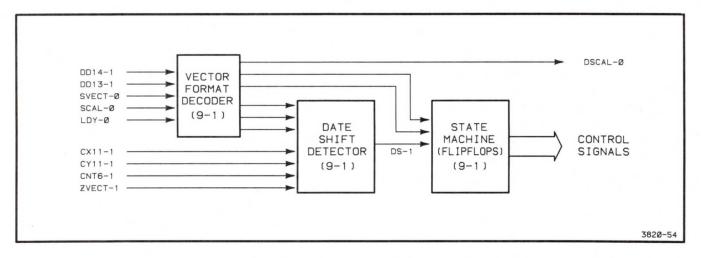

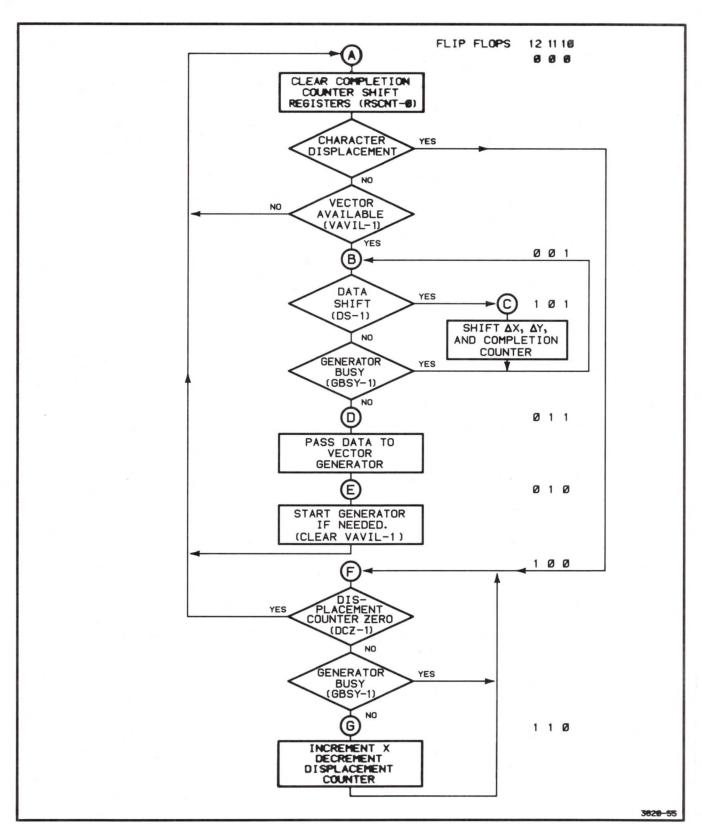

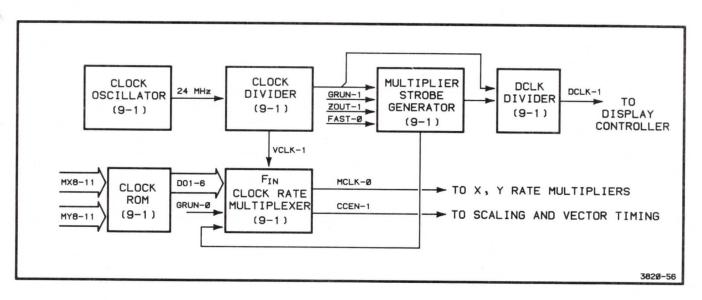

| 8-20<br>8-21                                                | Vector Set-Up Control State Machine Flow Chart Clock Generation Simplified Diagram                                                                                                                                                                                                                                                          | .8-35                                    |

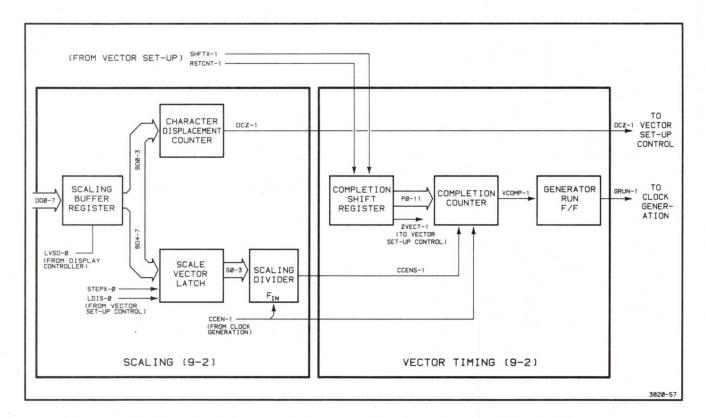

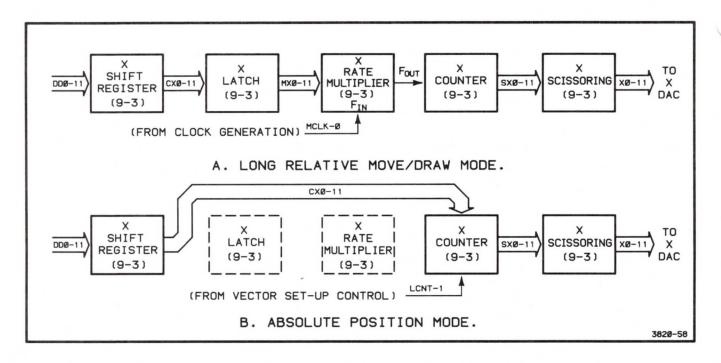

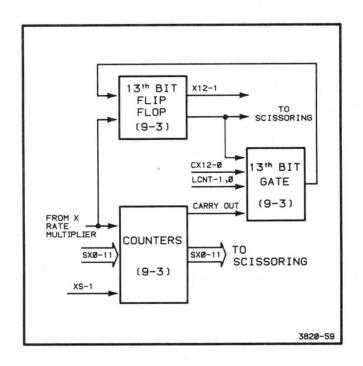

| 8 <b>-</b> 22<br>8 <b>-</b> 23                              | Scaling and Vector Timing Logic Block Diagram. Circuit Configurations for the Relative and                                                                                                                                                                                                                                                  |                                          |

| 8-24<br>8-25                                                | Absolute Position Modes                                                                                                                                                                                                                                                                                                                     | . 8-44                                   |

| 8-26                                                        | in the X and Y Axes                                                                                                                                                                                                                                                                                                                         |                                          |

| 8-27<br>8-28<br>9-1                                         | X Vector DAC Processing Diagram                                                                                                                                                                                                                                                                                                             | .8-49<br>.8-52                           |

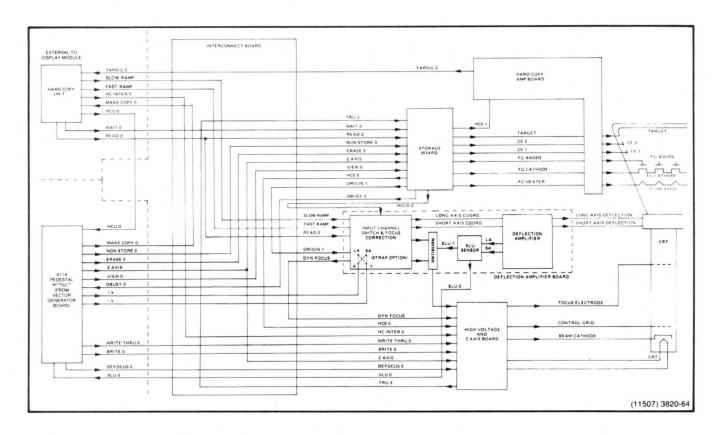

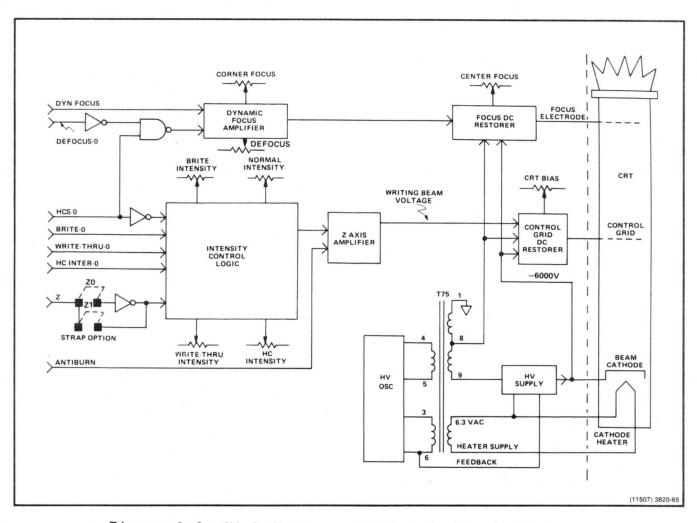

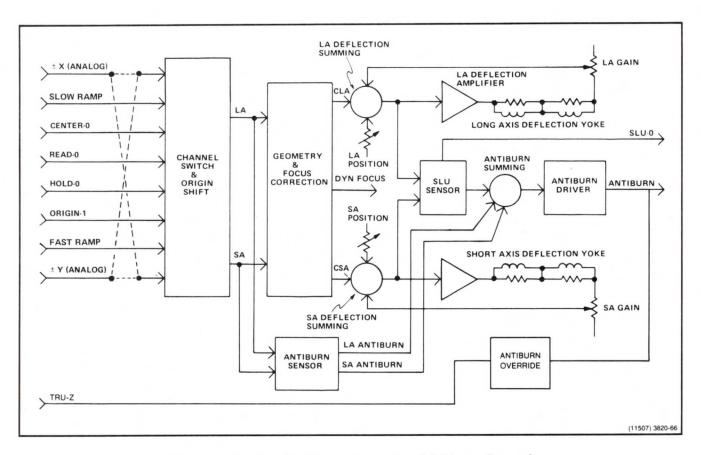

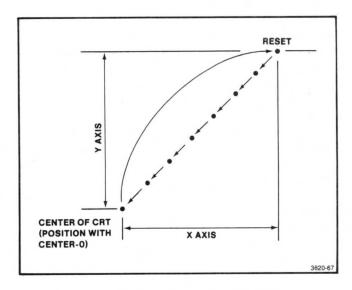

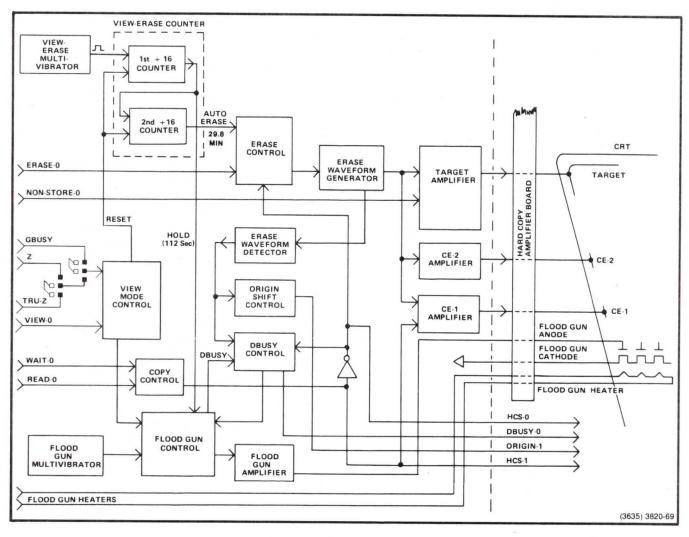

| 9-1<br>9-2<br>9-3                                           | Display Module Block Diagram                                                                                                                                                                                                                                                                                                                | .9-4                                     |

| 9-4<br>9-5                                                  | Origin Shift                                                                                                                                                                                                                                                                                                                                | .9-12                                    |

| 9-6<br>9-7                                                  | Storage Board Block Diagram                                                                                                                                                                                                                                                                                                                 | .9-17                                    |

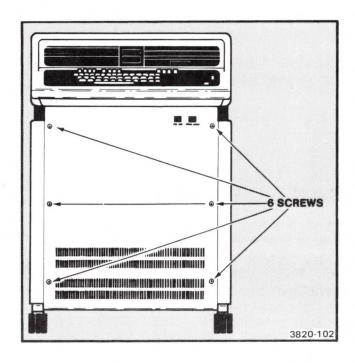

| 10-1<br>10-2                                                | Pedestal Front Cover Screw Locations                                                                                                                                                                                                                                                                                                        | . 10-14                                  |

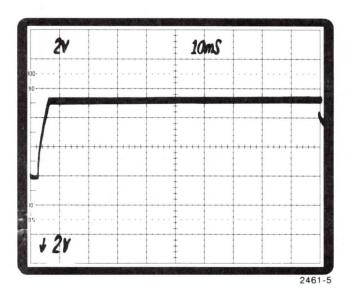

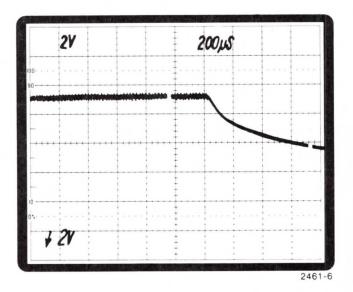

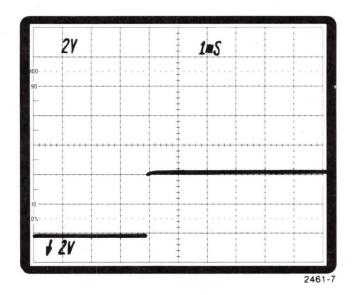

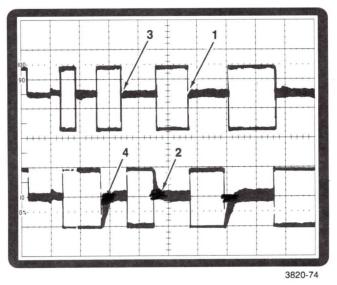

| 10-2<br>10-3<br>10-4                                        | INIT Waveform  PDWN-INIT Signal  PFAIL Waveform                                                                                                                                                                                                                                                                                             | .10-20                                   |

| Figure                         | Description                                                                      | Page    |

|--------------------------------|----------------------------------------------------------------------------------|---------|

| 10-5<br>10-6                   | Display Controller Board Adjustments<br>SELF TEST and MASTER RESET Buttons       |         |

| 10-7                           | Locations                                                                        | 10-25   |

| 10-3                           | Charge Pump Waveform                                                             | 10-27   |

| 10-9                           | Adjusted Charge Pump Waveform                                                    | . 10-27 |

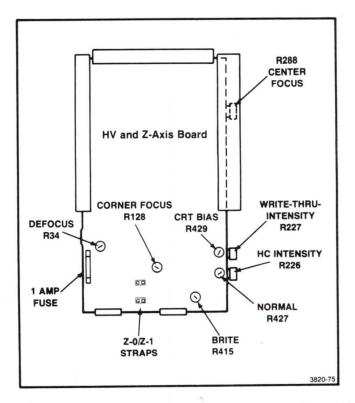

| 10-10                          | High Voltage and Z Axis Board Straps and Adjustments                             | 10-31   |

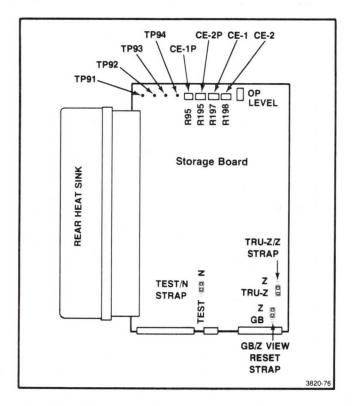

| 10-11                          | Storage Board Straps, Test                                                       |         |

| 10-12                          | Points, and Adjustments                                                          | . 10-32 |

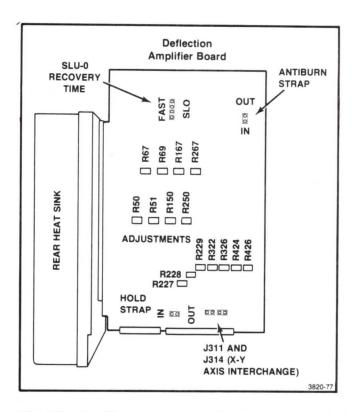

| 10-12                          | Deflection Amplifier Board Straps, Test Points, and Adjustments                  | 10-33   |

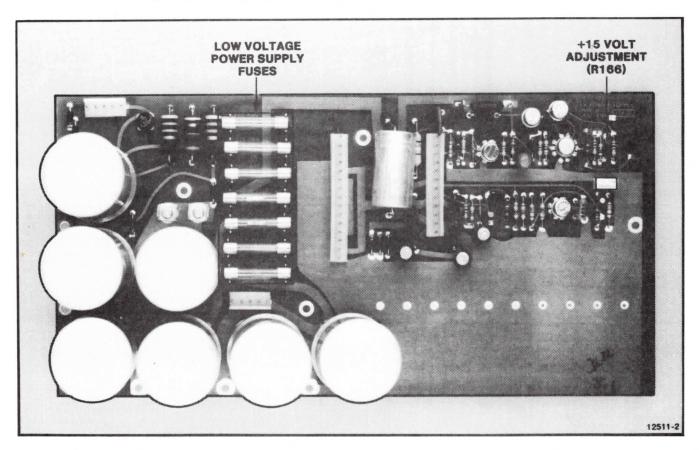

| 10-13                          | Low Voltage Power Supply Board Fuse Locations.                                   |         |

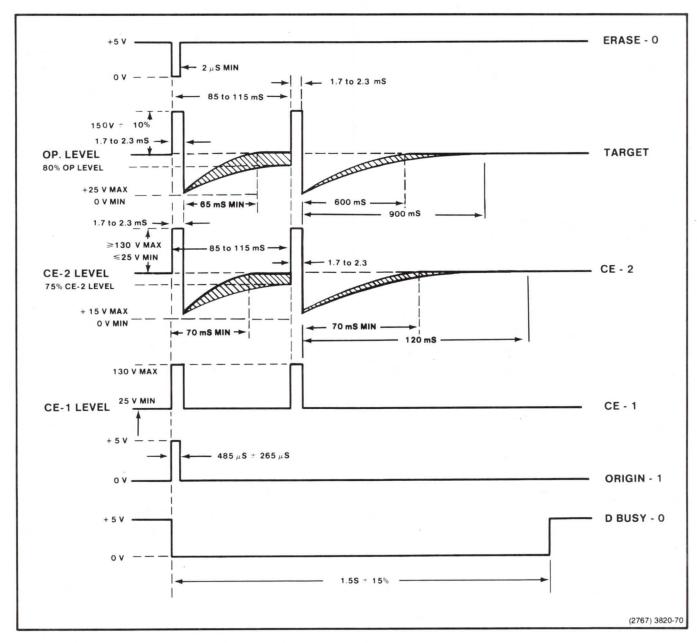

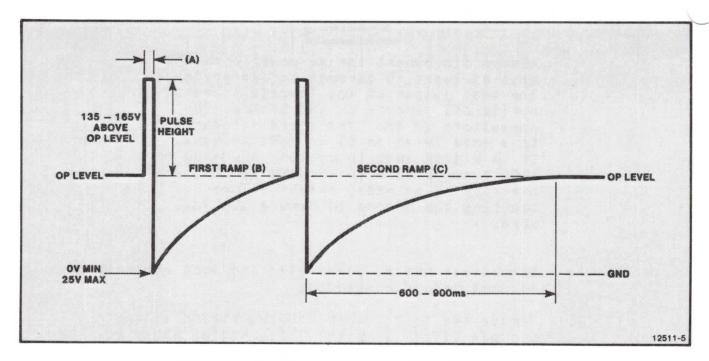

| 10-14                          | Target Erase Waveform                                                            |         |

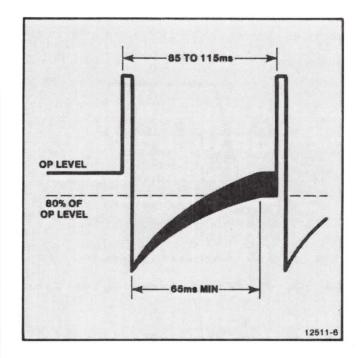

| 10-15                          | Target Erase Waveform Enlarged                                                   |         |

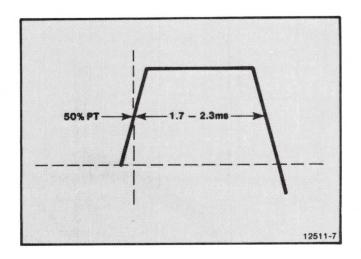

| 10-16                          | Target Erase Pulse Waveform                                                      | 10-42   |

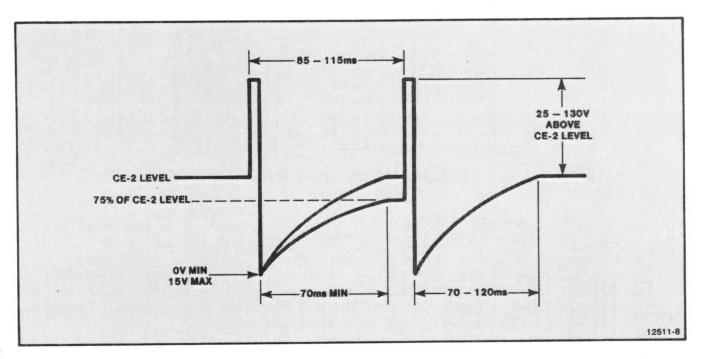

| 10-17                          | CE-2 Waveform                                                                    |         |

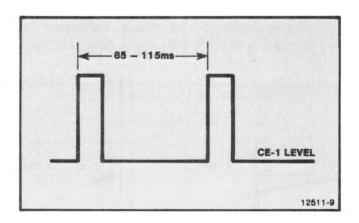

| 10-18                          | CE-1 Waveform                                                                    |         |

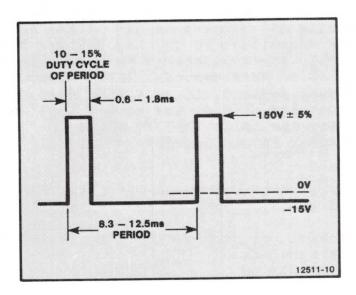

| 10-19                          | Flood Gun Anode Waveform                                                         |         |

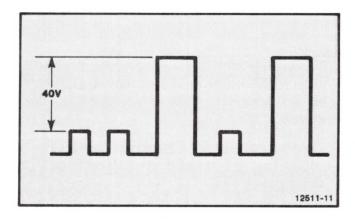

| 10-20                          | Waveform at R246                                                                 | . 10-48 |

| 10-21                          | X and Y Frequency Compensation Adjustments                                       |         |

| 10-22                          | Dynamic Focus Waveform                                                           |         |

| 10-23                          | Dropout and Fade-Positive Display Effects                                        |         |

| 10-24                          | Brite Intensity Pulse                                                            |         |

| 11 <b>-</b> 1<br>11 <b>-</b> 2 | Display Module Assemblies                                                        |         |

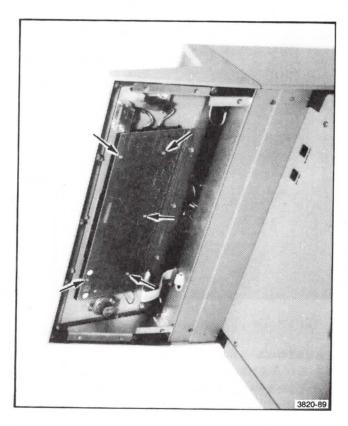

| 11-3                           | Side-View of the Display Module                                                  |         |

| 11-4                           | Crt Module                                                                       |         |

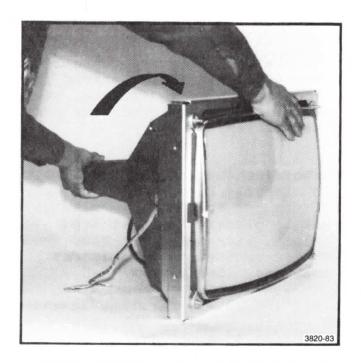

| 11-5                           | Tilting the Crt Module Forward                                                   |         |

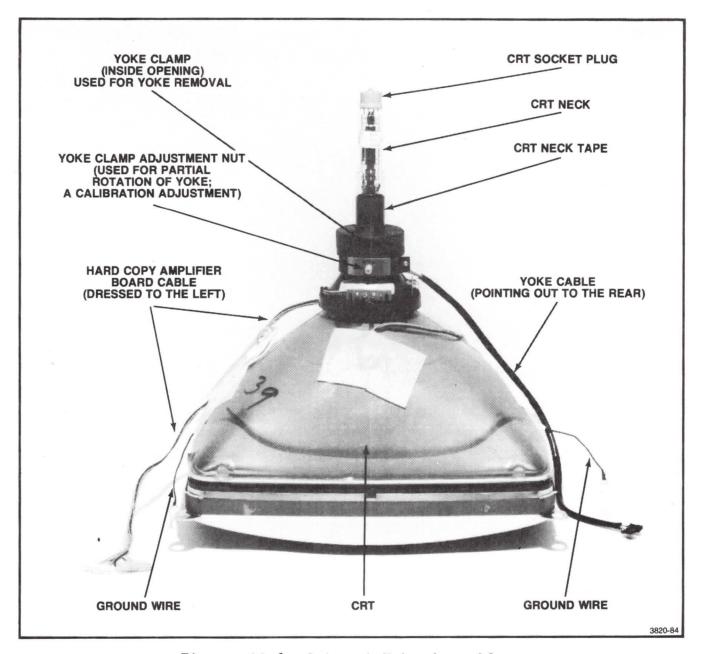

| 11-6                           | Crt and Yoke Assembly                                                            |         |

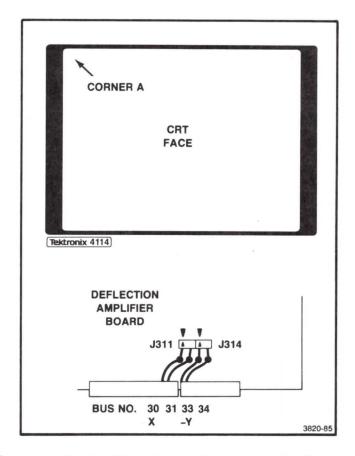

| 11-7                           | Standard Horizontal Format                                                       |         |

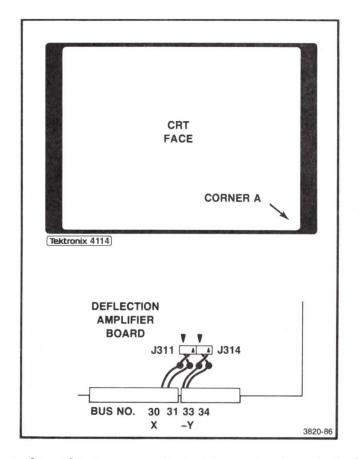

| 11-8                           | 180 Degree Rotation Horizontal Format                                            |         |

| 11-9                           | Removing the Front Cover                                                         |         |

| 11-10                          | Removing the Rear Panel                                                          |         |

| 11-11                          | Two Covers Below Keyboard                                                        | 11-42   |

| 11-12                          | Trim Grill and Cabinet Top Screw Locations                                       |         |

| 11-13                          | Removing the Keyboard                                                            | 11-44   |

| 11-14                          | Power Supply Heatsink                                                            | 11-46   |

| 11-15                          | Backplate                                                                        | 11-47   |

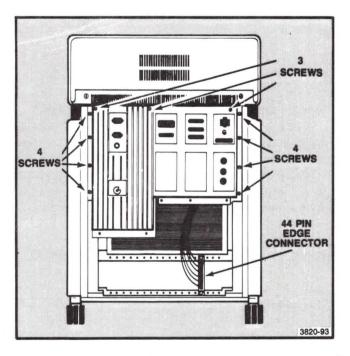

| 11-16                          | 44 Pin Connector and Bracket                                                     |         |

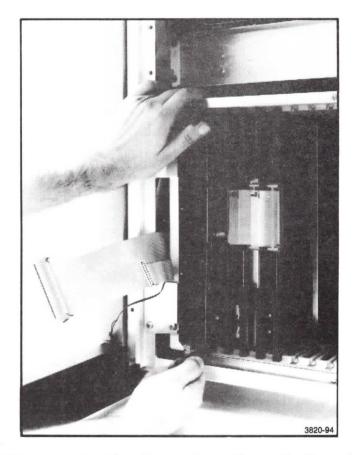

| 11-17                          | Removing the Inside Rear Panel                                                   |         |

| 11-18                          | Removing Circuit Poards                                                          |         |

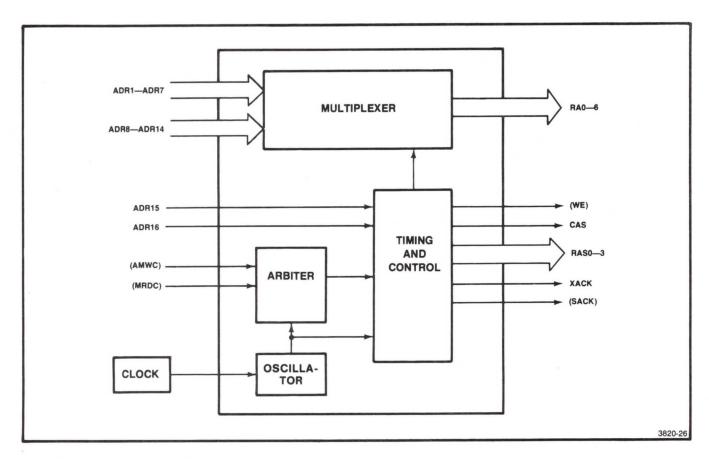

| T - 1                          | RAM Controller Foard Block Diagram                                               |         |

| D-2                            | RAM Controller Board Block Diagram                                               |         |

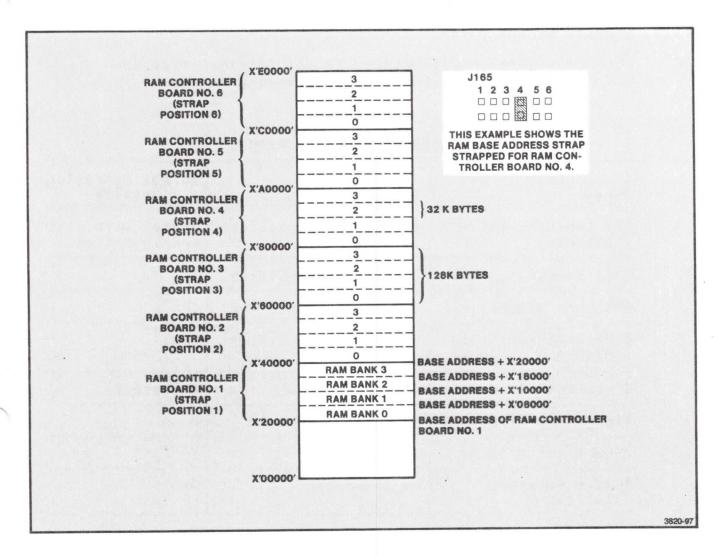

| B-3<br>C-1                     | Dynamic RAM Controller Block Diagram Strapping RAM Controller Board Base Address |         |

| 0-1                            | belapping har controller board base address                                      | 0-)     |

(a)

| Figure | Description                   | Page  |

|--------|-------------------------------|-------|

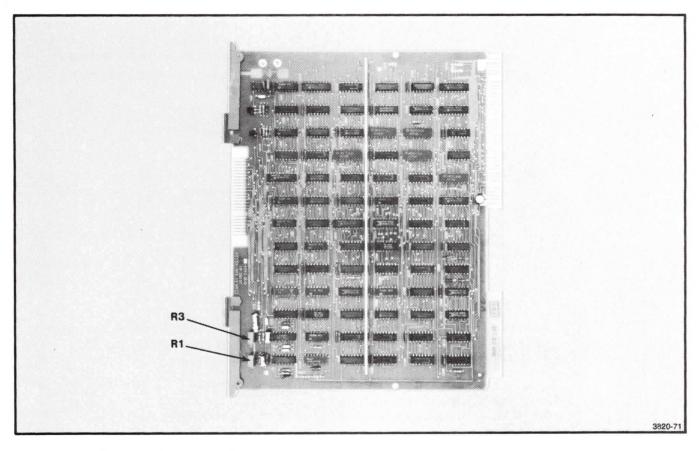

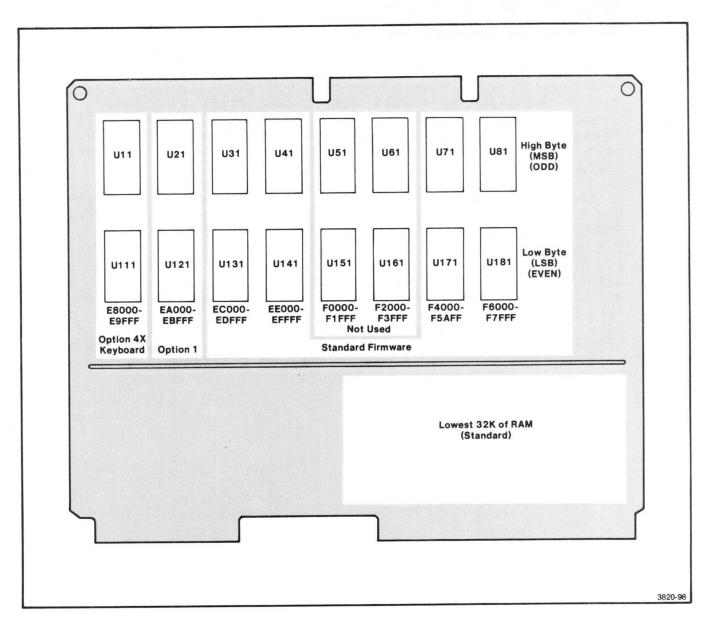

| E-1    | RAM/ROM Board                 | .E-6  |

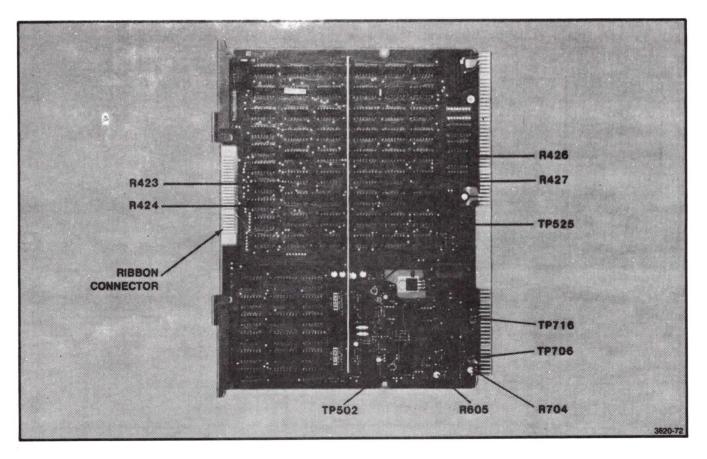

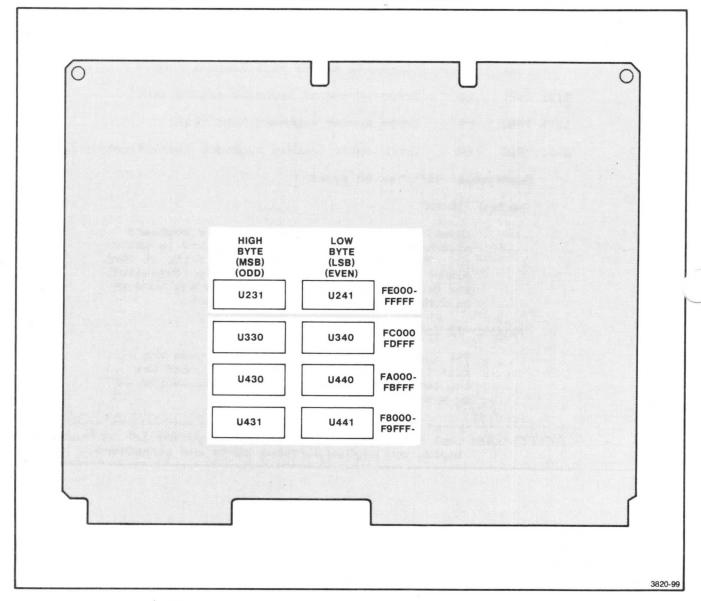

| E-2    | Processor Board RCMs          | .E-8  |

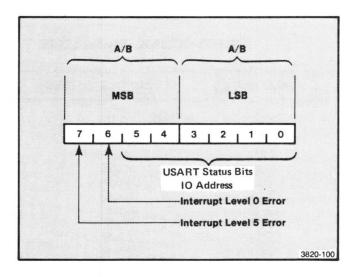

| E - 3  | I/O Address X'E8' Status Byte | .E-13 |

#### Section 1

## INTRODUCTION

The 4114 Computer Display Terminal Service Manual is divided into two volumes. Volume 1 includes introductory information, operating information, circuit theory, a detailed description of the adjustment procedure, and maintenance information. Volume 1 is primarily a reference manual. Volume 2, on the other hand, contains frequently used information that the service technician needs to troubleshoot, repair, and adjust the terminal. This information includes an abbreviated adjustment procedure, electrical and mechanical parts lists, block and schematic diagrams, installation information, and a detailed explanation of Self Test, which is a built-in, firmware troubleshooting aid.

#### RELATED DOCUMENTS

Detailed information on the use of the 4114 terminal is found in the following documents.

- o 4114 Computer Display Terminal Operator's Manual

- o 4114 Host Programmer's Reference Manual

- o 4110 Series Command Reference Manual

#### GENERAL DESCRIPTION

The 4114 is a high-resolution, microprocessor-controlled graphics computer terminal. The display is a 19-inch diagonal direct view storage tube. More than 12 million points on the display surface are individually addressable. By using these points, the display presents a graphic image made up of line segments. This image is displayed in either of two modes: Storage mode or Refresh mode. In Storage mode, the image is stable and permanent on the screen until it is erased. In Refresh mode, the image is continuously renewed, and therefore is easily moved around the screen surface. Graphics images can be contructed using both modes at the same time.

The 4114 uses microprocessor technology to create more than 100 primarily graphics-related commands. Using these commands, a host-resident software program run on a 4114 can create graphic images that can be displayed, modified, and sent to and received from a host computer. The 4114 carries most of the graphics processing-time burden if its local graphics commands are used.

The standard 4114 contains 32 K of RAM (read/write) memory and can contain up to 800 K of RAM memory on optional RAM Controller boards. As much as one megabyte of words can be stored on the optional flexible disks--512 K bytes per disk. The maximum host computer communication speed ("baud rate") is 19,200 bits per second for graphics and 38.4 K bits per second for text.

Set-Up mode uses English-language type commands to initialize many terminal operating parameters. Three of the major classifications are: general, dialog, and communications. In the general group, parameters like margin, echo, and Snoopy mode are set. In the dialog group, parameters like buffer size, line width, and number of lines are set. And in the communications group, parameters such as number of stopbits, kind of parity, and end-of-line string are set.

Most commands for the 4114 are encoded as three character ASCII codes beginning with the ESC character. The host computer controls the 4114 by sending it these three character ESC sequences in the order determined by each specific job to be done. (The Set-Up mode commands are encoded both as English-language type commands and as ESC sequences.)

Many features of the 4014 Computer Display Terminal are emulated by the 4114 terminal. Because of this, most application programs written for the 4014 run on the 4114 with very little or no modification. In addition, most peripheral devices that function connected to the 4014 also function when they are connected to the 4114. This includes Tektronix hard copy units and plotters.

#### PHYSICAL DESCRIPTION

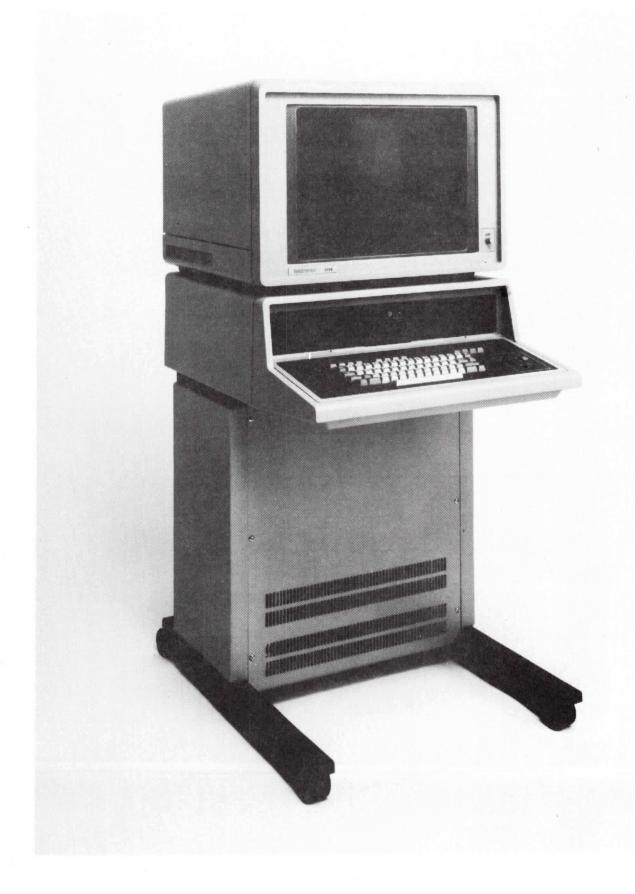

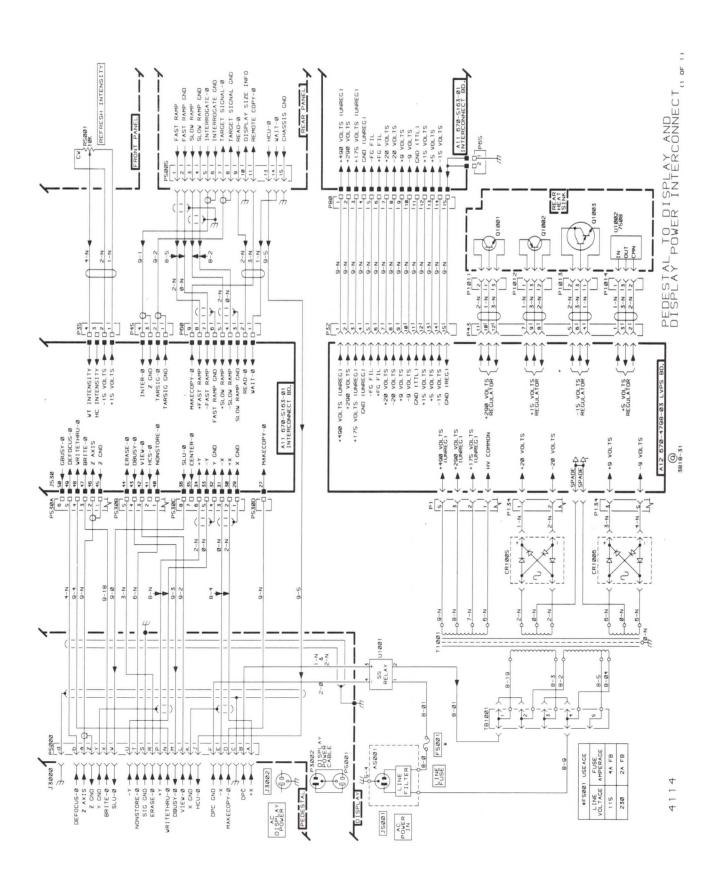

The 4114 consists of two main parts: the display module and the pedestal. The display module sits on four plastic bumpers (feet) on top of the pedestal. After the terminal is installed, the display module and pedestal are connected by two cables—the AC Display power cable and the display cable.

The display module contains a 19-inch direct view storage tube. The mechanical package is similar to the Tektronix 618 Display Monitor. The display electronics inside the display module include high voltage and Z axis, storage, deflection amplifier, hard copy amplifier, and low voltage power supply circuitry. This circuitry is similar to that in the Tektronix GMA102A Display Monitor.

The pedestal consists of the keyboard, the low voltage power supply, the card cage, and six mounting plates on the rear panel.

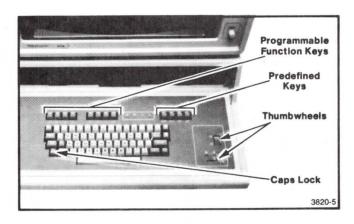

The keyboard has a standard typewriter-like layout of ASCII-encoded keys. There are eight programmable and four command keys along with four LED indicator lights situated above the standard ASCII keys. There are also two thumbwheels--one moving up and down (controlling vertical motion on the screen) and one moving across (controlling horizontal motion on the screen).

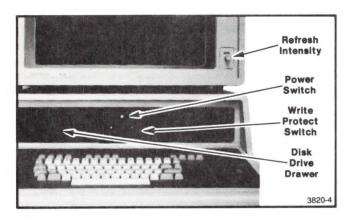

Above the keyboard is the power switch. Optional flexible disk assemblies may be installed on one or both sides of the power switch.

The card cage and low voltage power supply are found inside the pedestal below the keyboard. The card cage contains plug-in circuit boards with dimensions of 8.5 by 11.5 inches.

The standard 4114 contains the following circuit boards:

- o Motherboard. This has slots for five standard size circuit boards. The 80 pin bus of the Motherboard is the System Bus.

- o Processor board.

- o RAM/ROM board. This contains system EPROM and one 32 K RAM Array board.

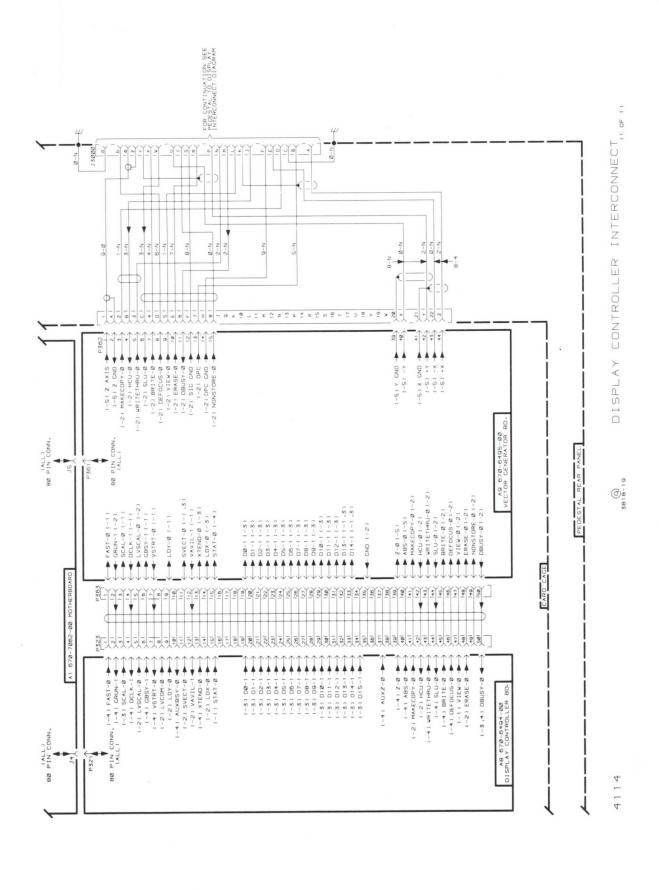

- o Display Controller board.

- o Vector Generator board.

The 4114 may contain these optional circuit boards:

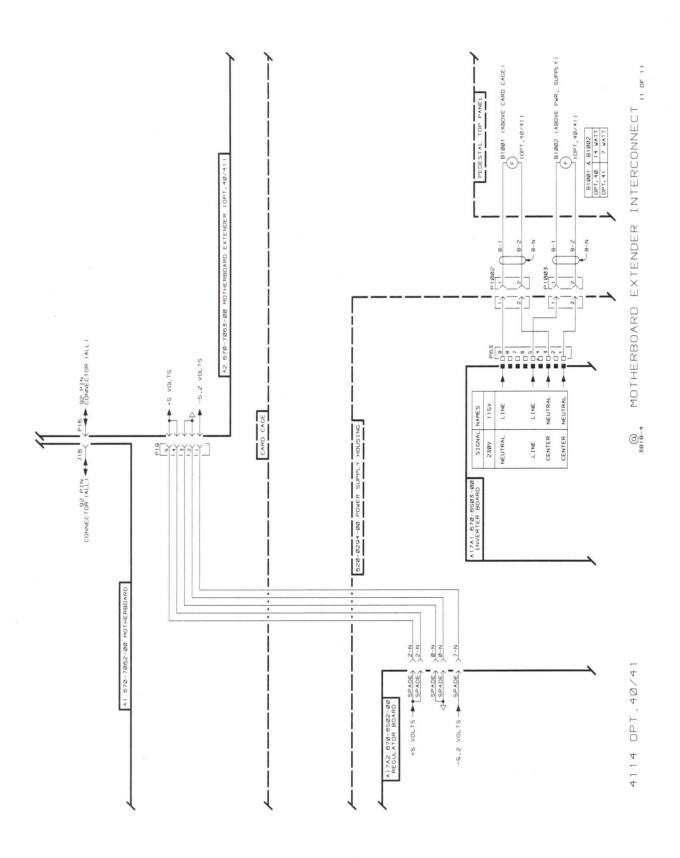

- o Motherboard Extender. This increases the System Bus slots of the Motherboard to fifteen total slots. (Option 40 or 41)

- o Three Port Peripheral Interface (3PPI) board. (Option 10)

- o Tablet Controller board. (Part of Option 13 and 14)

- o Disk Controller board. (Part of Option 42 and 43)

The low voltage power supply provides are the operating voltages for the Pedestal circuitry and is located above and to the right of the card cage--looking at the card cage from the front.

There are six removable mounting plates on the rear panel of the pedestal. One is standard and five hold optional connectors or L-brackets. The standard RS-232 host computer connector is mounted to the standard plate. The display cable connector is mounted here also.

#### OPTIONS

The following list of options is arranged in numerical order. Option numbers beginning with a letter designation are placed at the end of the list.

- Option 1 Extended Communications (includes half-duplex, block mode, and downloader).

- Option 2 Current Loop Interface (see Current Loop Interface Service Manual for detailed service information).

- Option 10 Three Port Peripheral Interface (3PPI). This option supports the following peripheral devices:

4662 and 4663 Plotters 4641 and 4642 Printers 4923 Tape Recorder with Option 1 installed and other RS-232 devices

See the 4110 Series Option 10 3PPI Service and 4114 Operator's Manuals for details.

- Option 13 Graphic Tablet. Size: 11 by 11-inches. Option hardware includes: Graphic Tablet (and pen), 411X Tablet Controller board, and Tablet Interface board. See the 4110 Series F13/14 Graphics Tablet Instruction and 4114 Operator's Manuals.

- Option 14 Graphic Tablet. Size: 30 x 40-inch. Option hardware includes: Graphic Tablet (and pen), 411X Tabet Contoller board, and Tablet Interface board. See the 4110 Series F13/14 Graphics Tablet Instruction and 4114 Operator's manuals.

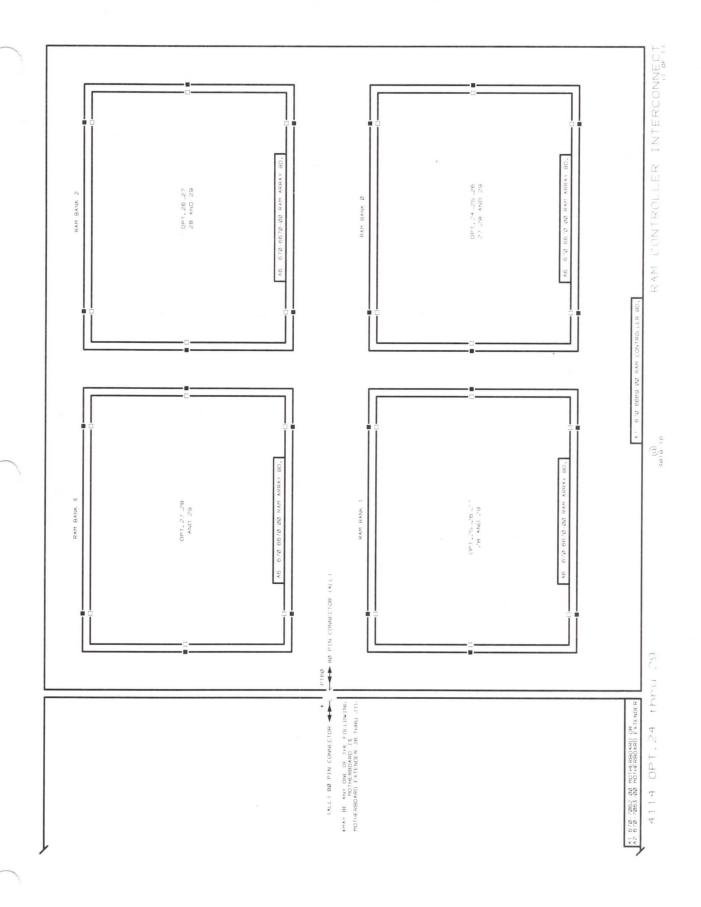

- Option 24 One RAM Controller Board. Includes 32 K bytes of RAM on one RAM Array Board. Service information is in Volume 2 of this manual.

- Option 25 One RAM Controller Board. Includes 64 K bytes of RAM on two RAM Array Boards. For service information, see Opt. 24.

- Option 26 One RAM Controller Board. Includes 96 K bytes of RAM on three RAM Array Boards. For service information, see Opt. 24.

- Option 27 One RAM Controller Board. Includes 128 K bytes of RAM on four RAM Array Boards. For service information, see Opt. 24.

- Option 28 Two RAM Controller Boards. Includes 256 K bytes of RAM on eight RAM Array Boards. For service information, see Opt. 24.

- Option 29 Four RAM Controller Boards. Includes 512 K bytes of RAM on sixteen RAM Array Boards. For service information, see Opt. 24.

- Option 31 Color Enhanced Refresh. Display Module has special DVST that writes refreshed vectors in yellow-orange.

- Option 40 Ten-Slot Peripheral Bus Extender. Includes Motherboard Extender, wire kit, and two 7 Watt fans.

- Option 42 Single Flexible Disk Drive, and one Disk Controller board. The service information is located in the Option 42/43 Service Manual, and 119-0977-01/03 Drive Unit Service Manual.

- Option 43

Dual Flexible Disk Drives and one Disk Controller board. The service information is located in the Option 42/43 Service Manual, and 119-0977-01/03 Drive Unit Service Manual.

- Option 52 Customer-specified line voltage and frequency option.

- Universal European line voltage and frequency: Option A1 220 V, 50 Hz.

- United Kingdom line voltage and frequency: 240 Option A2 V, 50 Hz.

- Australian line voltage and frequency: 240 V, 50 Option A3

- North American line voltage and frequncy: 240 V, Option A4 60 Hz.

#### ACCESSORIES

This list is divided into two parts: the standard accessories that are supplied with each 4114, and those accessories that may be ordered separately in addition to the standard accesories. The following accessories are also found in the parts list, where part numbers are listed for each item.

#### Standard Accessories:

- 4114 Operator's Manual

- o Power cord set

- o Host port RS-232 cable

- o Eight relegendable key caps

- Six function-key overlays

- 4114 Host Programmer's Reference Manual

- 4110 Series Command Reference Manual

#### Optional Accessories:

- 411X Logic Extender board

- Relegendable key caps

- Function-key overlays

- 4114 Host Programmer's Reference Manual

- 4114 Service Manual, Volume 1 (final edition) 4114 Service Manual, Volume 2 (final edition)

- 4110 Series Option 10 (3 PPI) Service Manual

- 4110 Series F13/14 Graphics Tablet Instruction Manual

- 4110 Series F42/43 Disk Options Service manual

- 119-0977-01/03 Flexible Disk Drive Instruction Manual

#### Section 2

#### SPECIFICATIONS

#### GENERAL INFORMATION

This characteristics/specifications section lists two different types of specifications: those that are classified as environmental, physical, or "static" specifications (nonuser verifiable specifications) and those that are verified as operational parameters of the 4114. The user verifiable specifications can be verified though the 4114 adjustment procedures in Section 10 of this manual. User verifiable specifications are noted in this section by an asterisk (\*) next to the specification.

Most user verifiable specifications apply to the display module of the standard 4114 because of the amount of internal adjustments necessary in the display module to achieve a good display of characters and vectors on the crt screen. The display module contains more analog circuitry than the pedestal and so requires more adjustment than the pedestal. The digital circuitry that makes up the bulk of the pedestal circuitry requires very little adjustment. This digital circuitry is designed primarily to display information to the user by means of the crt in the display module. This circuitry does not have specific operational parameters (although the pedestal does contain some adjustments that are used to verify some specifications).

An introduction to the display module and general theory follows.

#### INTRODUCTION TO THE DISPLAY MODULE

The display module is a cabinetized unit that sits on top of the pedestal. The display module consists of a 19-inch bistable storage crt and associated input and deflection circuitry that accepts display information (a combination of analog and digital signals) from the Vector Generator board in the pedestal. The only connections with the pedestal are the AC power cord and the cable which connects to the J3000 (pedestal) and contains the control signals from the Vector Generator board. Display information can be any combination of vectors and alphanumeric characters. A bi-stable tube, as the name implies, either can store or not store an image. All stored images have the same intensity.

Storage refers to the ability of the tube to retain displayed images for long periods of time (up to an hour, sometimes longer). The displayed image only needs to be written once. The ability of the storage crt to retain the image eliminates the need for local memory and associated refresh circuitry. Character and vector generation circuitry can be simplified because a storage crt does not need to generate images at refreshed speeds. Also, the display module has two additional modes which do not feature storage. One mode allows the user to display refreshed information. The other mode permits the user to display refreshed information concurrently with the previously stored information. Both of these display modes must be constantly refreshed.

The display module circuitry is contained on four circuit boards plus an Interconnect board and Low Voltage Power Supply board.

The only external control on the display module is the REFRESH INTENSITY control.

## DESCRIPTION OF THE DISPLAY MODULE

#### Hardware

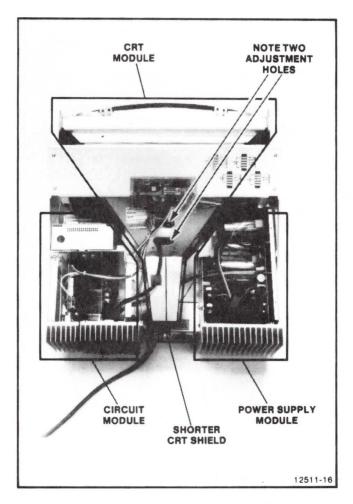

The display module consists of four modules with provisions for options, interfacing, and additional electronic circuitry. The four modules are the following:

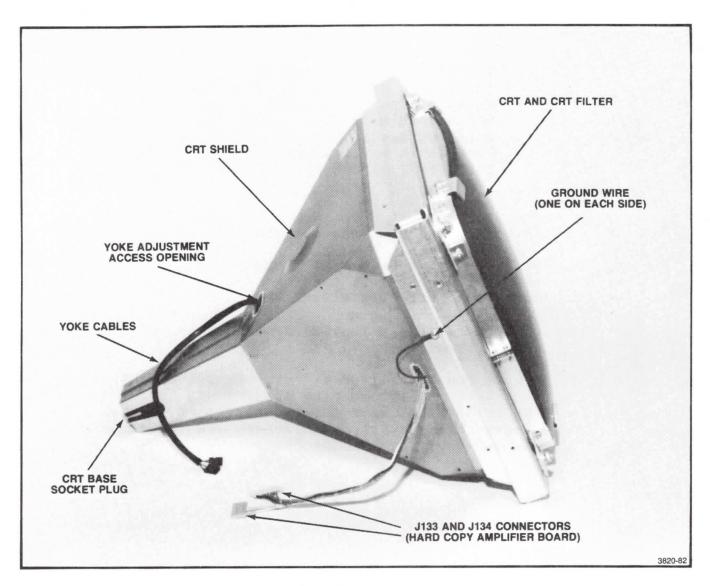

- 1. CRT MODULE. This consists of a crt, defection yoke, and crt shield. Although the Hard Copy Amplifier board is not connected to the crt shield, it is connected to the frame directly above the shield, and so, is considered part of the crt module.

- CHASSIS MODULE. This consists of a frame that supports and provides mounting for the other three modules.

- 3. POWER SUPPLY MODULE. This consists of the low voltage power supply, line voltage selection, fusing, heat sink, and a cable to distribute power to the circuit module.

4. CIRCUIT MODULE. This is a card cage that has a six-slot Interconnect board. The Interconnect board contains a High Voltage and Z-Axis board, a Deflection Amplifier board, and a Storage board. The remaining three slots are for additional circuit expansion.

## Display Features

The following display features are controlled by the pedestal via input lines to the display module.

- DEFOCUS. Increases spot size slightly when displaying long vectors.

- o BRITE. Slightly increases Z-Axis drive for vector or large character drawings.

- o ERASE. Erases the display area.

- o COPY. Initiates a hard copy when a suitable Hard Copy Unit (HCU) is attached.

- o VIEW. Switches back to full brightness from a reduced intensity (Hold Mode).

The following display features are internally controlled:

- o HOLD MODE. Automatically reduces the stored image intensity after the display has been inactive for about 1.5 to 2.5 minutes.

- o DBUSY. An outgoing signal (flag) indicating that the display is busy and will not accept additional data until the signal line is inactive.

- o ANTIBURN. Prevents excessive writing beam turn-on without crt beam movement.

- o AUTO ERASE. Erases the screen after the display has been inactive for about 30 minutes (not to be confused with Hold mode, which simply reduces the stored intensity; AUTO ERASE completely erases the screen and information cannot be restored to VEIW).

#### INTRODUCTION TO THE PEDESTAL

The pedestal is a cabinetized unit on which the display module sits. The pedestal can be thought of as an "information processor". It takes information from the user through the keyboard, the host computer, the optional flexible disk drive(s) -- Option 42 or 43, or a variety of optional peripheral devices. This unit stores the information or makes it visible to the user via the display module. The pedestal contains a built-in keyboard, the power supply for the keyboard and pedestal circuitry, one or two optional flexible disk drives, RAM and ROM memory, and terminal circuits to process information and control output to the display.

The pedestal connects to an AC power source (at J3001) and can be wired to accept input voltages of 100 V, 120 V, 220 V, or 240 V. The pedestal supplies power (at J3002) and the necessary display information (at J3000) to the display. Any time the input voltage is changed for the pedestal, the input voltage straps for the display module must also be changed. The pedestal can communicate with a host computer through the J3006 connector. In addition, with options 1, 10, 13, or 14 installed, the 4114 can interface with a 4662 or 4663 plotter, a 4641 or 4642 line printer, a 4923 tape recorder, or a graphic tablet. The pedestal also has RAM options (24 through 29) which lets the user address up to 512K bytes of local memory.

The standard 4114 pedestal circuitry is contained on four circuit boards, a Motherboard, and the power supply module.

#### DESCRIPTION OF THE PEDESTAL

The 4114 pedestal consists of six modules with provisions for options, interfacing, and additional electronic circuitry. The six modules are as follows:

1. THE KEYBOARD. The keyboard is an ASCII data entry device that accepts commands, control information, and alphanumeric characters from the user, and acts as an output device for SELF TEST failure codes. The keyboard converts the alphanumeric data into an 8-bit binary code for use by the Processor board.

- 2. THE POWER SUPPLY. The power supply can be strapped to accept input voltages of 100 V, 120 V, 220 V, and 240 V from a single phase source. It provides a direct feed to the low voltage power supply in the display. Anytime the input straps on the power supply are set for one of the four input voltages, the straps in the display must also be set for that voltage. The pedestal power supply provides output voltages of +5.10 V, +12.00 V, -5.20 V, and -12.00 V for use by the pedestal circuitry. In addition, if Options 42 or 43 are installed, the power supply provides +24.00 V for disk drive operation.

- 3. THE CARD CAGE. The card cage consists of the Mother board, Mother Board Extender (Option 40), and the framework which holds the circuit boards in place. The card cage holds the RAM/ROM board (and any RAM option boards), the Vector Generator board, the Display Controller board, the Processor board, and any other circuit boards necessary for additional options. The card cage is located at the bottom of the pedestal.

- 4. THE RAM/ROM MEMORY. The standard 4114 contains one RAM/ROM board with 32K bytes of user addressable memory. With the extended RAM options (Options 24 through 29), the user can address up to 512K bytes of memory. The ROM contains the most of the system firmware that decodes local user commands, performs the SELF TEST routines, and other system tasks.

- 5. THE DISPLAY ELECTRONICS. The display electronics consists of the Vector Generator board and the Display Controller board. These two boards, in combination, provide the display with the signals telling it what to display on the screen. The output of the Vector Generator board goes directly to J3000, the communication line between the display and the pedestal.

6. THE PROCESSOR BOARD. The Processor board can be thought of as the central processing unit, or "heart", of the 4114. This microprocessor-based board takes data from the keyboard, memory, host computer, or other source, acts on it and stores it in memory, passes it to the flexible disks, and/or sends it to the display or memory.

#### SPECIFICATIONS

The following tables and lists specify the characteristics and performance specifications of the terminal, both display and pedestal parts. The specifications are valid only when these conditions are met:

- 1. The display module must be adjusted at an ambient temperature of between +20 C and +30 C (68 F to 86 F).

- 2. The terminal must be operating in an environment as specified under Table 2-1, Environmental Specifications.

- 3. Operations must be preceded by a warmup period of at least 20 minutes.

- 4. Specified power requirements must be met. See Section 11, Operating Voltage and Fuse Selection, and Table 2-6, Power Requirements. The terminal should be operated from a power source with its neutral at or near ground potential. It is not intended for operation from two phases of a multiphase system.

The following tables provide additional information on the indicated pages:

| Table                           | Description                                                                                                                             |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5 | Environmental Specifications Physical Characteristics Display Specifications Vertical and Horizontal Deflection Graphics Specifications |

| 2-6<br>2-7<br>2-8               | Power Requirements<br>J3000, Rear Connector<br>J5005, Hard Copy Unit Connector                                                          |

Table 2-1

ENVIRONMENTAL SPECIFICATIONS

| Characteristic                                   | +10 to +40 C (43 to 104 F)                                        |  |

|--------------------------------------------------|-------------------------------------------------------------------|--|

| Temperature Operating without flexible disks     |                                                                   |  |

| with flexible<br>disks (Options<br>42 & 43)      | +10 to +38 C (43 to 100 F)                                        |  |

| Non-Operating without flexible disks             | -40 to +65 C (-40 to 149 F)                                       |  |

| with flexible disks (Options 42 & 43)            | -40 to +50 C (-40 to 122 F)                                       |  |

| Altitude(a) Non-Operating Operating              | To 50,000 ft (15240 m) To 15,000 ft (4572 m)                      |  |

| Humidity<br>Without flexible<br>disks:           |                                                                   |  |

| Non-Operating<br>Operating                       | 90-95% maximum relative humidity 70-75% maximum relative humidity |  |

| With flexible disks installed (Options 42 & 43): |                                                                   |  |

| Non-operating<br>Operating                       | 8% to 80% non-condensing 20% to 80% non-condensing                |  |

<sup>(</sup>a) Maximum operating temperature decreases 1 degree  ${\tt C}$  for every 1,000 feet above 5,000 feet in altitude.

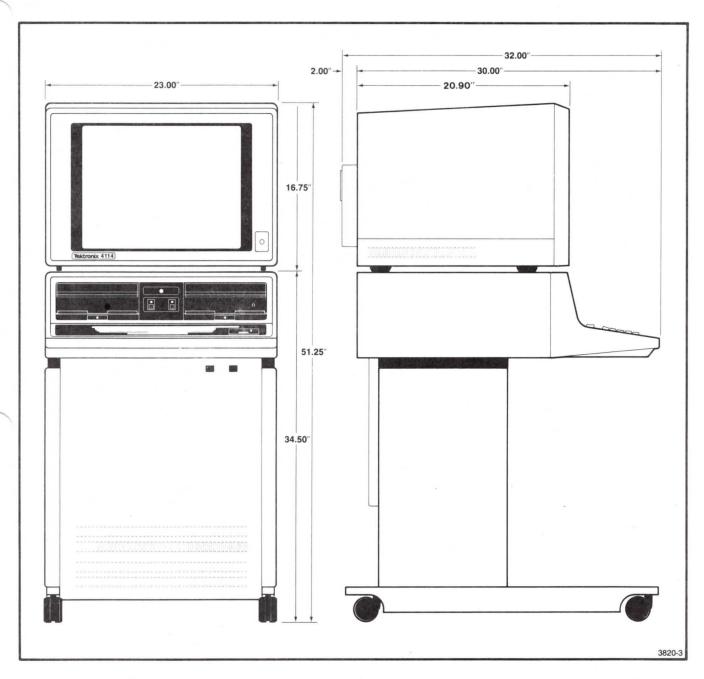

Table 2-2 PHYSICAL CHARACTERISTICS

| Characteristic               | Specification                                                                                       |  |

|------------------------------|-----------------------------------------------------------------------------------------------------|--|

| Weight of the Display Module | Approximately 100 lbs                                                                               |  |

| Weight of the Pedestal       | Approximately 150 lbs (This weight varies depending on the options installed; this is an average.)  |  |

| Display Module Dimensions    | Height 16.75 in (425.5 mm)<br>Length 22.90 in (581.7 mm)<br>Width 23.00 in (584.2 mm)               |  |

| Pedestal Dimensions          | Height 34.50 in (876.3 mm)                                                                          |  |

|                              | Length 30.00 in (762.0 mm) (The greatest length measured from the back to the end of the keyboard.) |  |

|                              | Width 23.25 in (590.6 mm)                                                                           |  |

| Total Weight of the terminal | Approximately 250 lbs                                                                               |  |

| Dimensions of the terminal   | Total Height 51.25 in (1301.8 mm)                                                                   |  |

| (See Figure 2-1.)            | Widest point 23.25 in (590.6 mm)                                                                    |  |

|                              | Longest length 30.00 in (762.0 mm)                                                                  |  |

Figure 2-1. 4114 Dimensions

Table 2-3

DISPLAY SPECIFICATIONS

| Performance Requirement                                                                                                                                                                                                                           |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 19 in (480 mm) curved face direct view storage tube.                                                                                                                                                                                              |  |

| 14.5 in (368.3 mm) Long Axis<br>10.9 in (276.9 mm) Short Axis                                                                                                                                                                                     |  |

| 13.9 x 10.5 in (353.1 x 266.7 mm)                                                                                                                                                                                                                 |  |

| Green P1                                                                                                                                                                                                                                          |  |

| 750 BTU per hour                                                                                                                                                                                                                                  |  |

| Recommended 15 minutes or less, but may be extended to one hour without permanent damage to the storage target. If a residual image is retained after a long viewing time, the target may be returned to normal condition by successive erasures. |  |

| greater than or equal to 150 M/sec greater than or equal to 600 M/sec                                                                                                                                                                             |  |

| 1.5 seconds, <u>+</u> 12%                                                                                                                                                                                                                         |  |

| 112 seconds $\pm 20\%$ after last display activity.                                                                                                                                                                                               |  |

| Occurs 30 minutes <u>+</u> 20% after entering and remaining in Hold mode.                                                                                                                                                                         |  |

| Within +1.2 degrees of 90 degrees at center screen.                                                                                                                                                                                               |  |

|                                                                                                                                                                                                                                                   |  |

<sup>(</sup>a) User verifiable specification.

# Table 2-3 (cont) DISPLAY SPECIFICATIONS

| Characteristic                                   | Performance Requirement                                                                                                                                                                                             |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parallelism(a)                                   | Within +1.5 degrees at edges of quality area.                                                                                                                                                                       |

| Rectangle<br>Short Axis Sides<br>Long Axis Sides | +1.25% of long axis<br>+1.25% of long axis                                                                                                                                                                          |

| Positional Accuracy                              | All points within the crt quality area are addressable with accuracy of $\pm 1.25\%$ of the long axis.                                                                                                              |

|                                                  | The combined errors due to linearity, orthogonality, parallelism, geometry, and gain shall not cause positional inaccuracies greater than $\pm$ 1.25% of the long axis in either axis for any point of the display. |

| Linear Deflection Speed                          | Greater than or equal to 600/sec.                                                                                                                                                                                   |

| No. of Character<br>Lines                        | 64 maximum                                                                                                                                                                                                          |

| No. of Characters<br>per Line                    | 133 maximum                                                                                                                                                                                                         |

| Standard Character Set                           | Full ASCII character set 94 dis-<br>playable characters; 128 display-<br>able characters in "snoopy" mode.                                                                                                          |

| Linearity                                        | ,                                                                                                                                                                                                                   |

| Full Scale                                       | Within 1.25% (spot shall be within 1.25% of full screen width of proper position for voltage applied).                                                                                                              |

| Incremental                                      | No more than 10% difference in spacing between any two points for a given incremental voltage input.                                                                                                                |

## NOTE

The earth's magnetic field may cause some noticeable display position, size, or shape changes if the display module is moved from or faced in any direction other than that in which it was adjusted.

Table 2-4

VERTICAL AND HORIZONTAL DEFLECTION

|                | ·                                                                                                                                                                              |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Characteristic | Performance Requirement                                                                                                                                                        |

| Input Signals  | The X and Y inputs to the Deflection Amplifier are analog and differential. When driving from a single-ended source, the unused input should be grounded at the signal source. |

| Polarity       |                                                                                                                                                                                |

| +X             | Positive voltage applied to positive input moves the beam right. Negative voltage moves the beam left.                                                                         |

| -X             | Positive voltage applied to the negative input moves the beam left. Negative voltage moves the beam right.                                                                     |

| <b>+</b> Y     | Positive voltage applied to positive input moves the beam up. Negative voltage moves the beam down.                                                                            |

| <b>-</b> Y     | Positive voltage applied to the negative input moves the beam down. Negative voltage moves the beam up.                                                                        |

| Sensitivity    |                                                                                                                                                                                |

| Long Axis      | 5 V (10 V p-p) for full screen deflection horizontally.                                                                                                                        |

| Short Axis     | 3.75 V (7.5 V p-p) for full screen deflection vertically.                                                                                                                      |

#### NOTE

Polarity is the same whether the crt has been rotated 180 degrees or not, providing the deflection input wiring on the Deflection Amplifier board is adjusted accordingly. (See Selecting X- and Y-Axis Inputs under Rotating the crt 180 degrees, Section 11.)

Table 2-5

GRAPHICS SPECIFICATIONS

| Characteristic            | Specification                                                                                                                                   |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Addressability            | 4096X x 4096Y Points                                                                                                                            |  |

| Graphic Command<br>Syntax | Plot 10, 4010 Series, & IGL Syntax compatable                                                                                                   |  |

| Line Types                | Solid, dashed, and defocused                                                                                                                    |  |

| Interactive Graphics      | Thumbwheels in the keyboard control a graphic cursor. The graphic cursor may have its shape defined by the user (with crosshairs as a default). |  |

|                           | The user can also control scrolling and the alpha cursor position by keyboard keys.                                                             |  |

Table 2-6

POWER REQUIREMENTS

| Performance<br>haracteristic                                                                                                    | Requirement                                                                |

|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| isplay Module                                                                                                                   |                                                                            |

| Power Consumption at 115 Vac, 60 Hz, full internal load.                                                                        | 220 W                                                                      |

| Maximum running line current in 120 V connection. Line Fuse 100 V Connection 120 V Connection 220 V Connection 240 V Connection | 2.6A  4 A slow-blow 4 A slow-blow 2 A slow-blow 2 A slow-blow              |

| Line Voltage Ranges<br>100 VAC<br>120 VAC<br>220 VAC<br>240 VAC                                                                 | 90 to 110 V<br>108 to 132 V<br>198 to 242 V<br>216 to 250 V                |

| edestal Power Supply  Maximum running line current in a 120 V connection.                                                       | 6.8A                                                                       |

| Maximum running line current in a 220 V connection.                                                                             | 3.4A                                                                       |

| Line Fuse 100 V connection 120 V connection 220 V connection 240 V connection                                                   | 10.0 A fast-blow<br>10.0 A fast-blow<br>5.0 A fast-blow<br>5.0 A fast-blow |

| Line Voltage ranges<br>100 VAC<br>120 VAC<br>220 VAC<br>240 VAC                                                                 | 90 to 110 V<br>108 to 132 V<br>198 to 242 V<br>216 to 250 V                |

#### NOTE

The 4114 has component recognition under Standard UL 478 (Data Processing) for line voltages up to 240 V. It also is certified by CSA according to standard C22.2, No. 154, for line voltages up to 125 V. It meets or exceeds DHEW X-Ray emmission standard; code of Federal Regulations, 21 CFR, sub-chapter J, parts 1020 and 1030, and TEK X-Ray standard 062-1860-00.

Table 2-7

# REAR CONNECTOR (J3000)

(J3000 on the pedestal, which are also the pins on P5000 of the display)

| Name       | Type(a) | Pin | Signal | Description                                                                                                                               |

|------------|---------|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------|

| +X         | D       | A   | Linear | <pre>Input. Negative voltage (- V) moves beam left. Posi- tive voltage (+V) moves beam right.</pre>                                       |

| -X         | D       | Е   | Linear | <pre>Input. +V moves beam leftV moves beam right.</pre>                                                                                   |

| X GND      |         | K   |        | Shield GND.                                                                                                                               |

| <b>+</b> Y | D       | Р   | Linear | Input. +V moves beam upV moves beam down.                                                                                                 |

| <b>-</b> Y | D       | U   | Linear | InputV moves beam up. +V moves beam down.                                                                                                 |

| Y GND      |         | Y   |        | Shield GND.                                                                                                                               |

| Z Axis     | D       | а   | TTL    | Input. TTL true turns on Z-Axis, providing certain conditions are met. Can be strapped to accept either polarity and to reset View Timer. |

<sup>(</sup>a) C designates a Control line to the display; D, a Data input line; and F, a Flag signal.

Table 2-7 (cont)

REAR CONNECTOR (J3000)

| Name         | Type | Pin | Signal | Description                                                                                                                                                                                                |

|--------------|------|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Z GND        |      | Z   |        | Shield GND.                                                                                                                                                                                                |

| CHASSIS GND  |      | S   |        | Shield-chassis ground.                                                                                                                                                                                     |

| MAKE COPY-0  | С    | D   | TTL    | Loop-thru input. Low initiates a hard copy when the HCU is connected and ready.                                                                                                                            |

| HCU-O        | F    | J   | TTL    | Output. Low tells the Display Controller that a HCU is connected and will accept a MAKE COPY-0 command.                                                                                                    |

| WRITE-THRU-O | С    | N   | TTL    | Input. Initiates a reduced Z-Axis signal to prevent display storage for refreshed operation. Any prior stored information is kept in view.                                                                 |

| NON STORE-0  | С    | Т   | TTL    | Input. Low disable storage for directed beam re-freshed operation. Written data storage is prevented by reducing target voltage.                                                                           |

| BRITE-0      | С    | х   | TTL    | Input. When low, the crt writing beam intensity is increased slightly. Can be used with a focused beam to display medium sized characters or a defocused beam to display large characters or long vectors. |

# Table 2-7 (cont) REAR CONNECTOR (J3000)

| Name      | Type | Pin | Signal | Description                                                                                                                                                                                                           |

|-----------|------|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DEFOCUS-0 | С    | b   | TTL    | Input. When DEFOCUS-0 is low, the crt writing beam is slightly defocused. Useful for displaying long vectors. Can be used with WRITE-THRU, NORMAL, or BRITE INTENSITY. See Table 9-1, Intensity and Focus Selections. |

| DBUSY-0   | С    | М   | TTL    | Output. Low indicates that the display is busy during an erase cycle, is in Hold mode, or is making a hard copy.                                                                                                      |

| VIEW-O    | С    | L   | TTL    | Input. Low triggers active flood gun cycle of about 1.5 to 2.5 minutes, making it possible to store information on the crt and view previously stored information.                                                    |

| SLU-0     | F    | W   | TTL    | Output. Low indicates deflection system has not settled and is lagging the input deflection signal.                                                                                                                   |

| ERASE-0   | С    | R   | TTL    | Input. Low initiates the Erase cycle. 2 us minimum duration.                                                                                                                                                          |

Table 2-7 (cont)

REAR CONNECTOR (J3000)

| Name    | Type | Pin | Signal | Description                                                                                                                                            |

|---------|------|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| DPC GND |      | F   |        | Display Power Control ground. Goes to negative lead of solid state relay.                                                                              |

| DPC     |      | В   |        | Display Power Control. Supplies power to the display module when the 4114 pedestal power is turned on. Goes to positive lead of the solid state relay. |

<sup>(</sup>a)  ${\tt C}$  designates a Control line to the display; D, a Data input line; and F, a Flag signal.

Table 2-8

HARD COPY UNIT CONNECTOR (J5005)

| Name              | Pin | Signal | Description                                                                                                                          |

|-------------------|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------|

| FAST RAMP<br>GND  | 1 2 | Linear | Fast scan ramp from the Hard Copy Unit (HCU). Ramp amplitude is 10 V centered at 0 V. Adjustable centering.                          |

| SLOW RAMP<br>GND  | 3 4 | Linear | Slow scan ramp from HCU. Ramp amplitude is 10 V, centered at 0 V. Adjustable centering.                                              |

| HC Inter-0<br>GND | 5   | TTL    | Input. Controls Z-Axis during HC Scan. 400 ns pulse width at a 1.4 us pulse repetition rate.                                         |

| Tarsig-O<br>GND   | 7 8 | TTL    | Output. Goes low when scan crosses a written area on the crt. Causes the HCU to reproduce on paper what is stored on the crt screen. |

| Read-0            | 9   | TTL    | Input. Causes display unit to switch into HC mode.                                                                                   |

| Display Size-0    | 10  | TTL    | Output. Low output indicates 19-inch display to HCU (tied to ground).                                                                |

| Remote Copy-0     | 11  | TTL    | Output. Initiates one HC cycle. Useful for remote control. Requires ground closure (TTL low) for > 1 ms.                             |

| Copy Busy         | 13  | TTL    | Input. High when HC is busy (applies to HCUs without multiplexing capability).                                                       |

Table 2-8 (cont)

HARD COPY UNIT CONNECTOR (J5005)

| Name      | Pin | Signal | Description                                                                                 |

|-----------|-----|--------|---------------------------------------------------------------------------------------------|

| HCU-0     | 13  | TTL    | Input. Low if HCU having multiplexing capability is connected and is ready.                 |

| Wait-0    | 14  | TTL    | Input. Low until display has been scanned (does not apply to HCU without multiplex option). |

| Frame GND | 15  |        | Earth (Cable Shield).                                                                       |

#### Section 3

#### OPERATING INFORMATION