Processing Unit Models D25 and D26 Theory-Maintenance Diagrams

### **PREFACE**

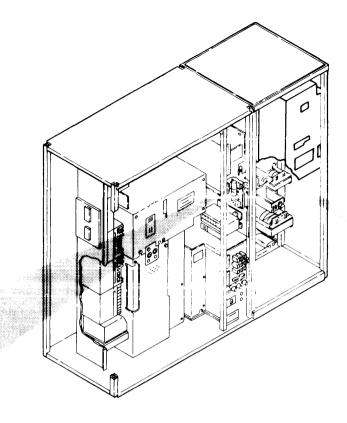

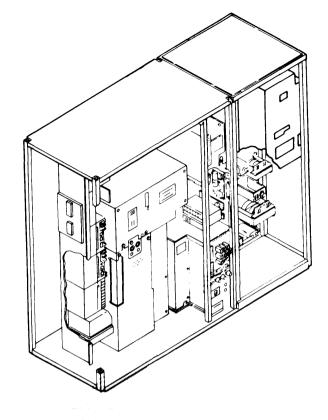

This manual contains the theory of operations, maintenance diagrams, and service information for the IBM 5415 Processing Unit Models D25 and D26. All references to Model 15D mean Models 15 D25 and 15 D26.

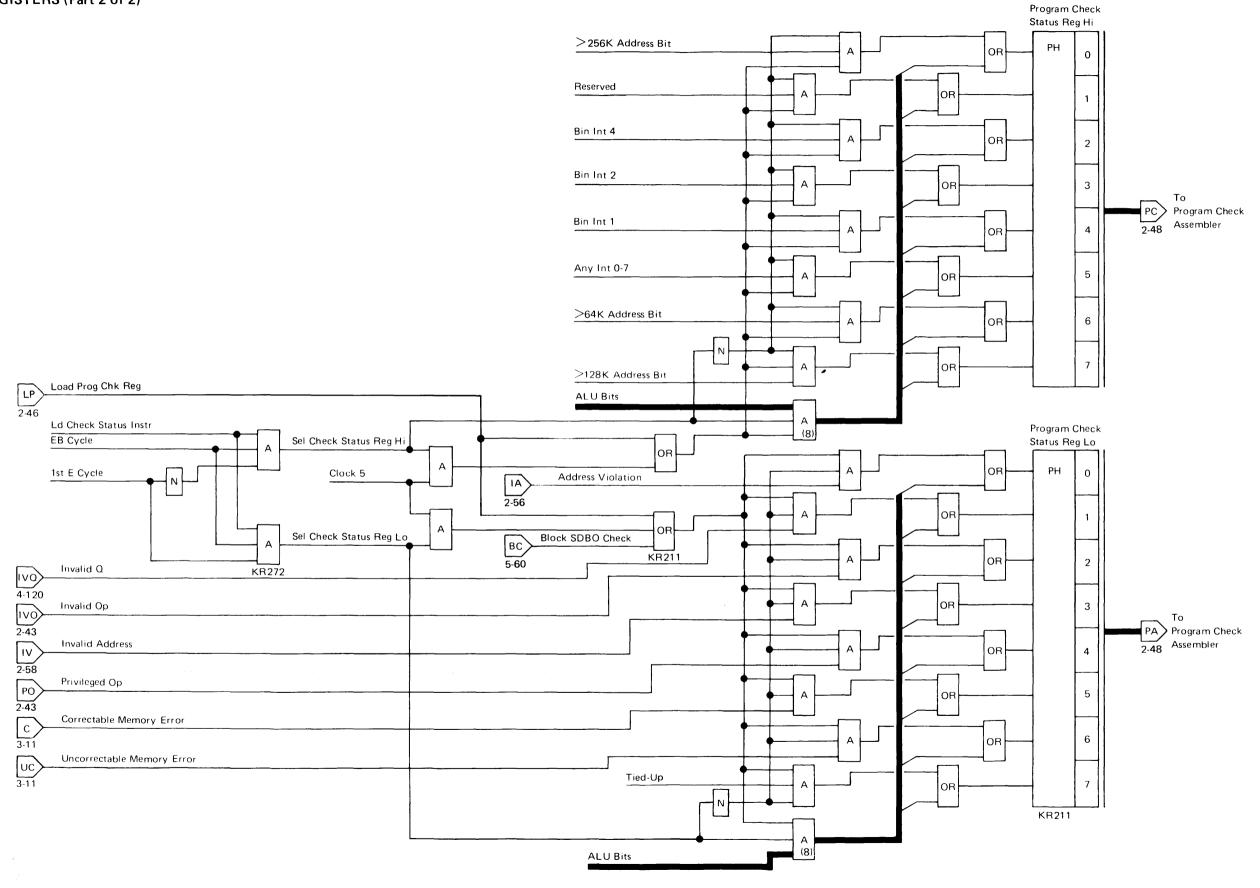

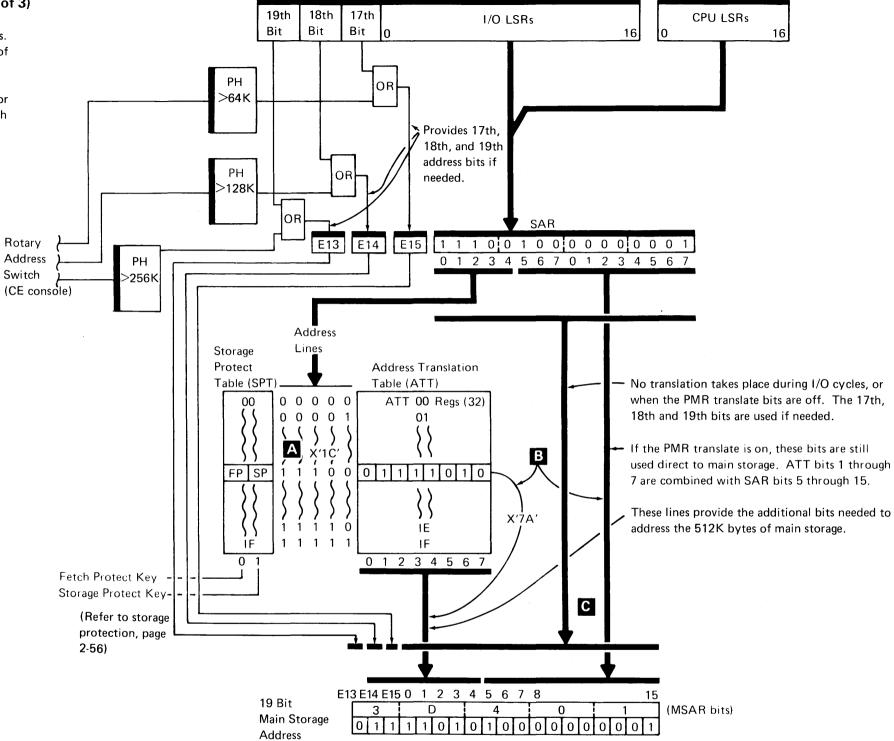

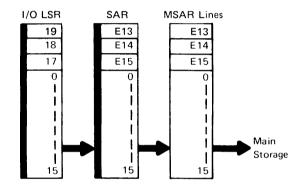

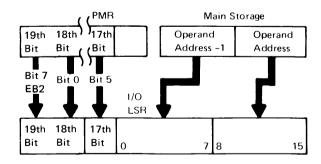

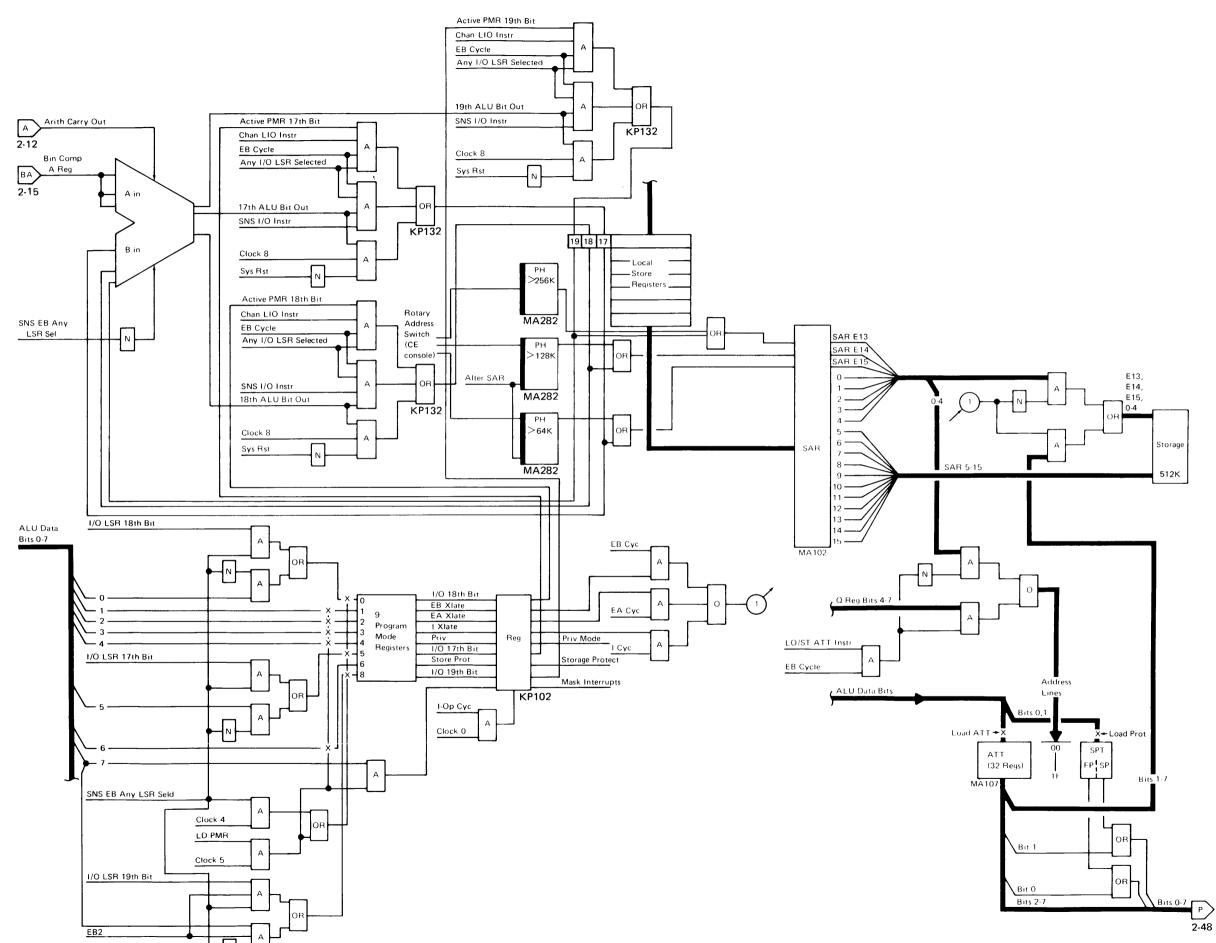

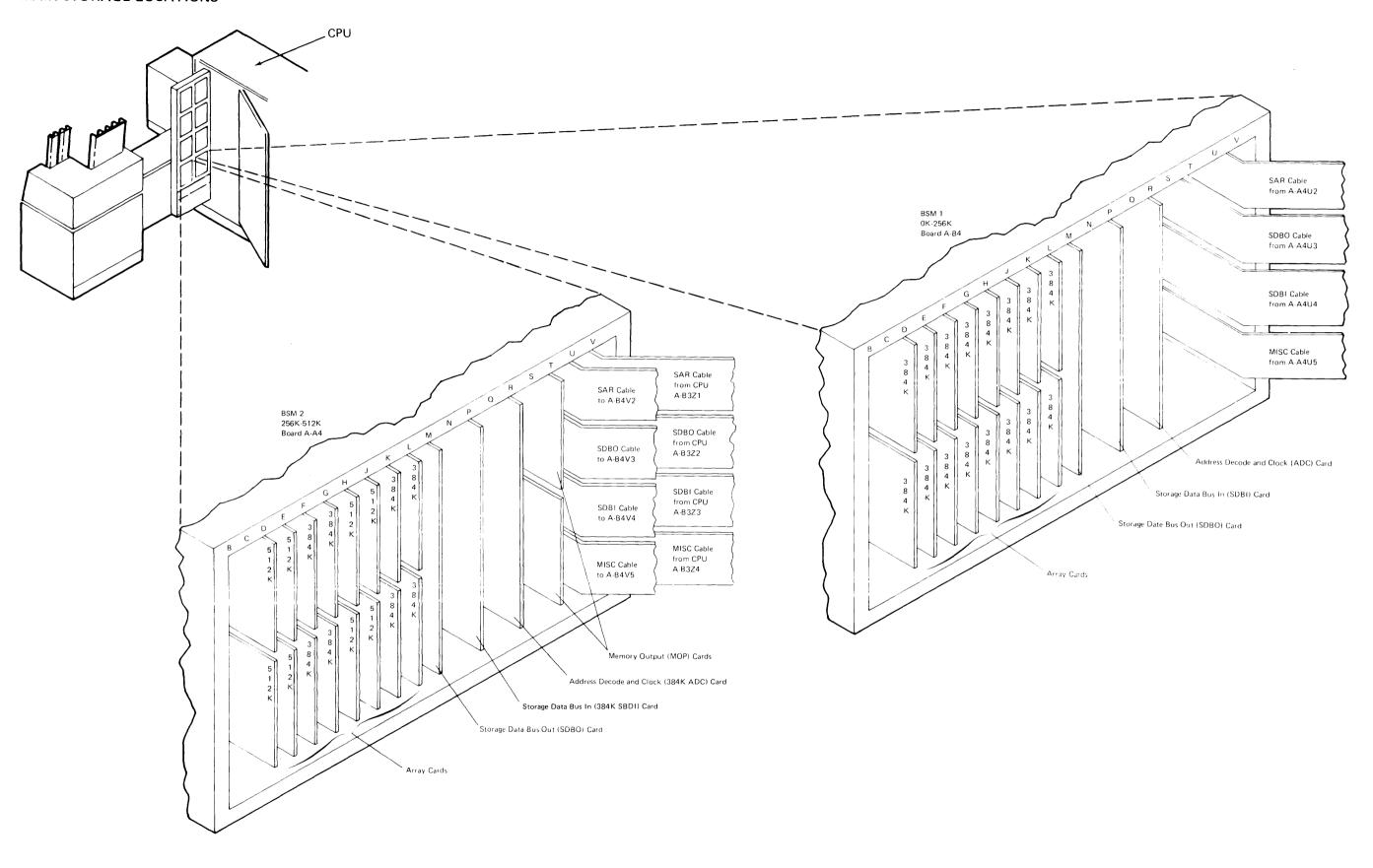

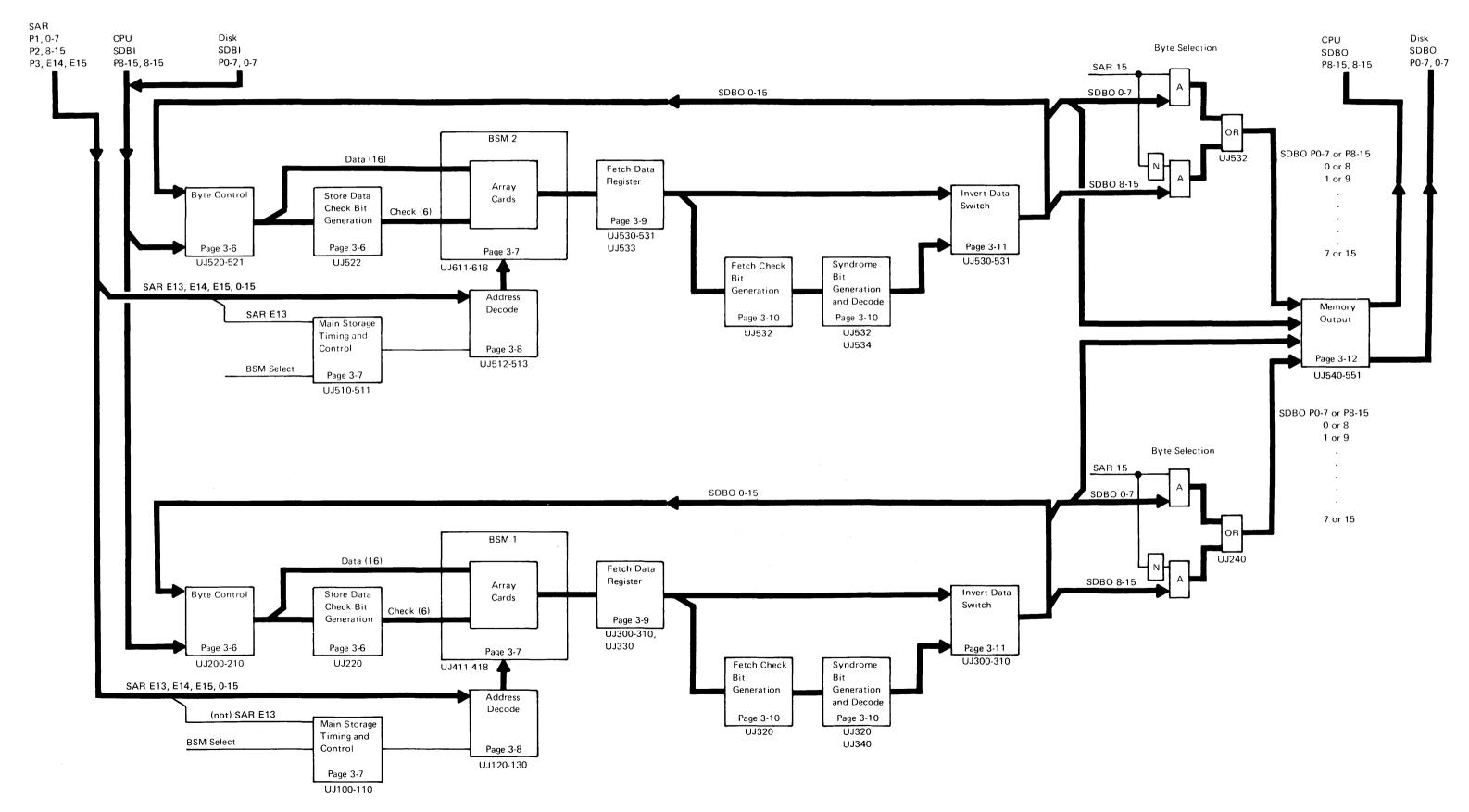

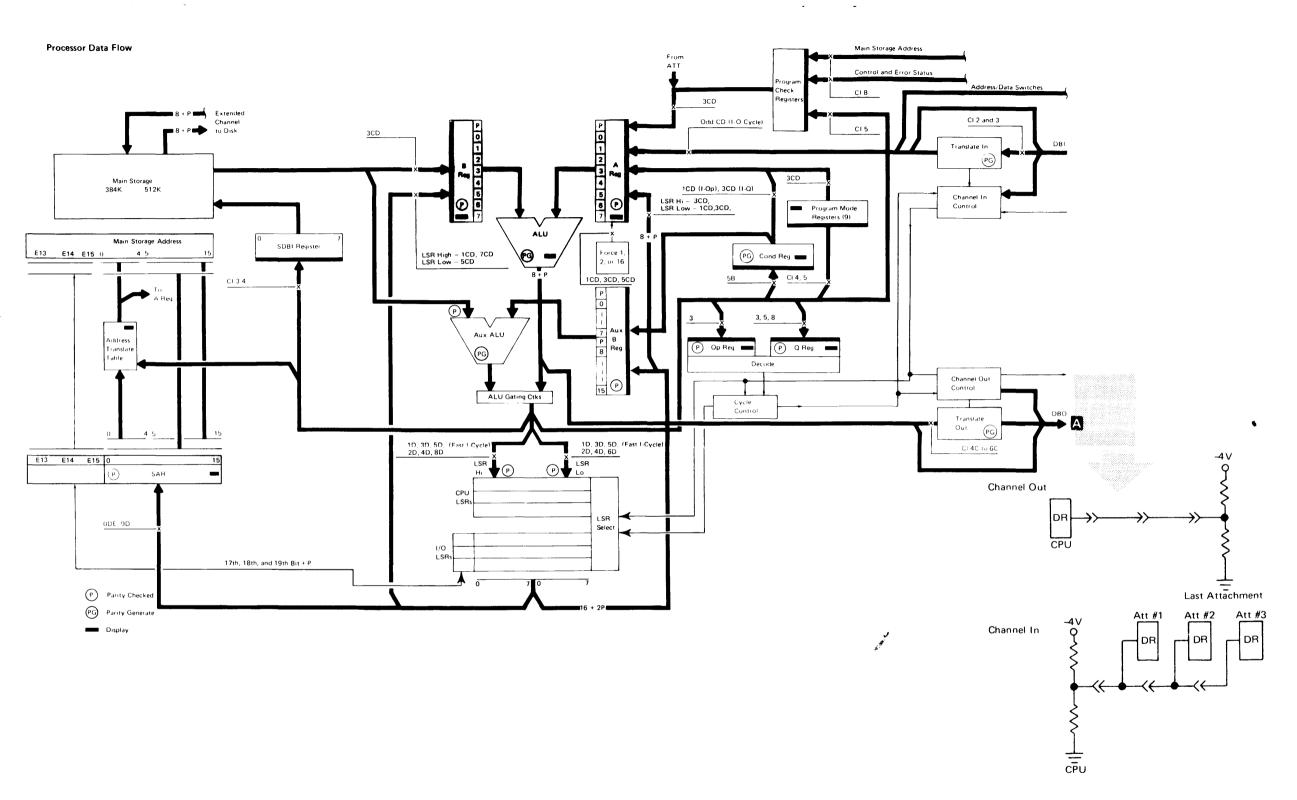

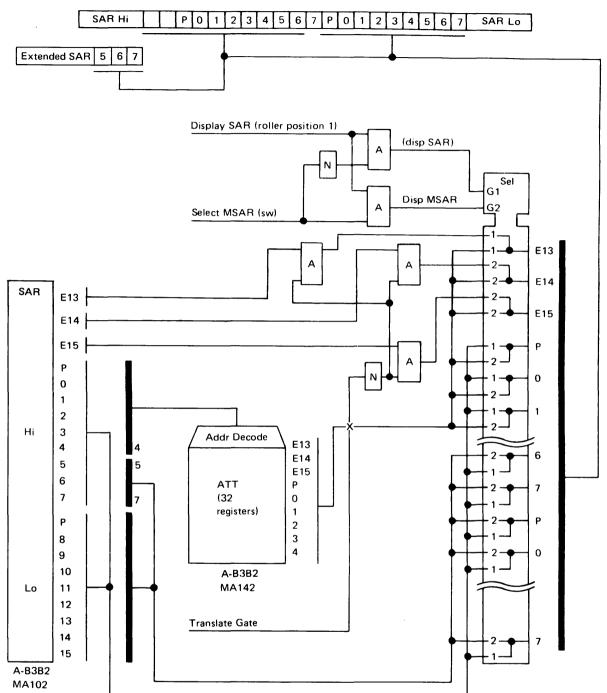

The Models 15 D19 through 15 D24 have a maximum of 256K bytes of storage, while the Models 15 D25 and 15 D26 have 384K and 512K bytes of storage respectively. To handle the additional storage, the Models 15 D25 and 15 D26 have the following changes:

- Replacement of the > 64K and > 128K ADDR BITS toggle switches with an eight-position rotary switch to provide a > 256K selection.

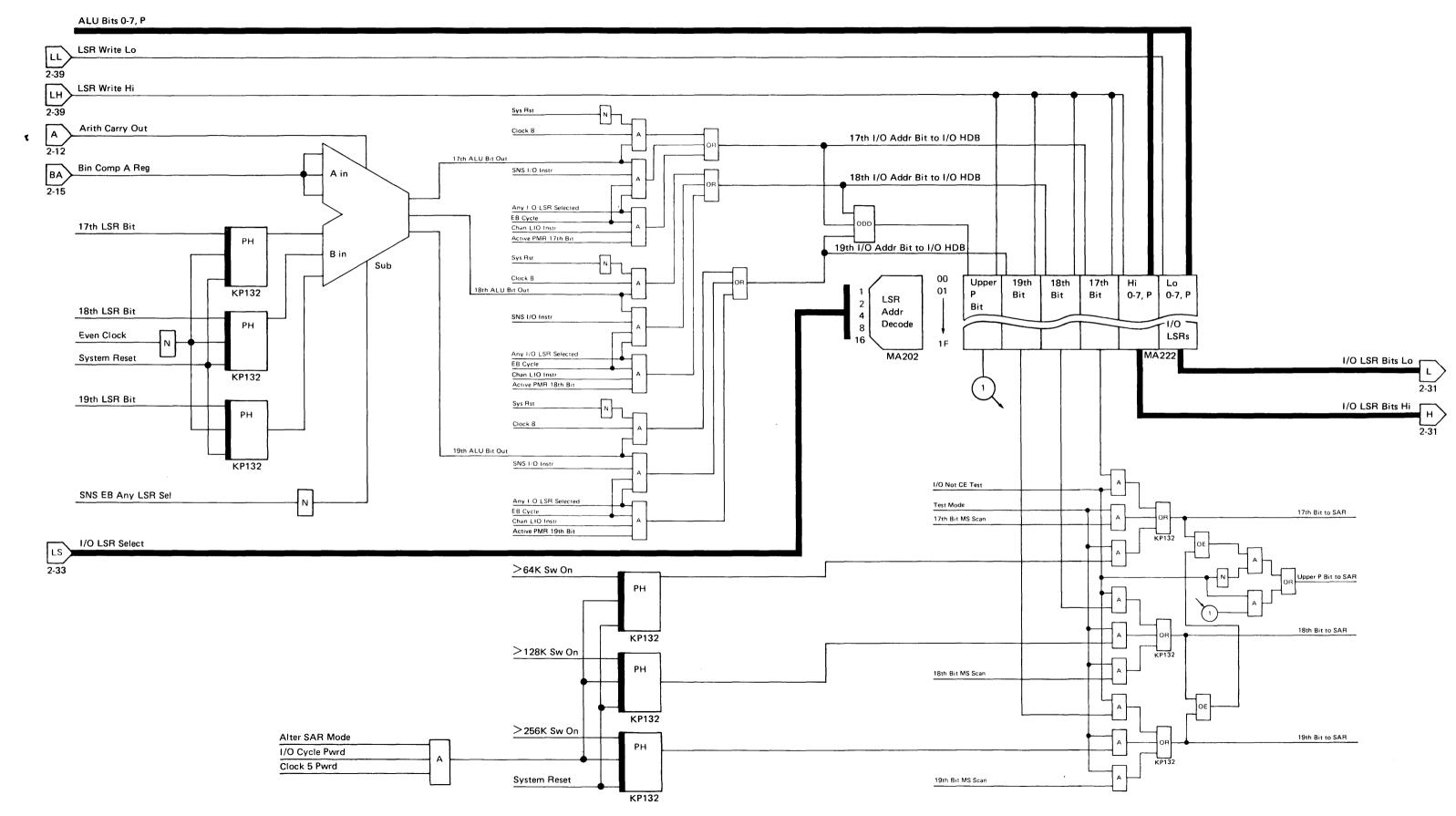

- Addition of a > 256K PH latch and circuit.

- Addition of a 19th bit circuit to condition SAR bit E13.

- Replacement of the roller drum to include an I/O > 256K position.

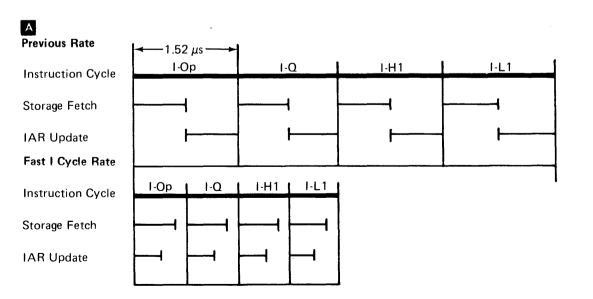

The Model D processing unit includes fast I cycle processing, a maximum of 512K bytes of main storage, and 3340/3344 disk drives. Refer to SY31-0367 for information about 5415 Models A and B, SY31-0417 for information about 5415 Models C, or SY31-0464 for information about 5415 Models D19 through D24.

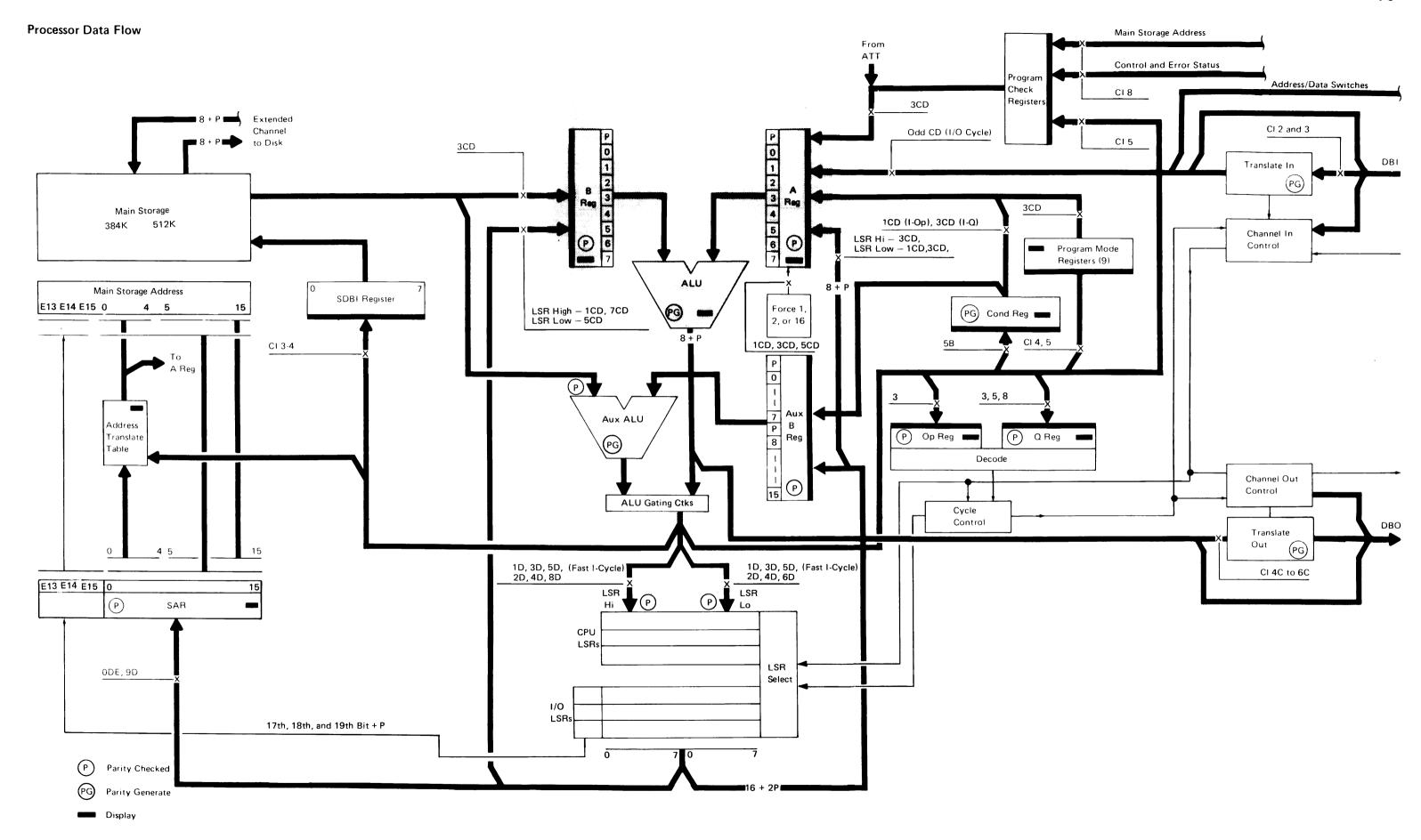

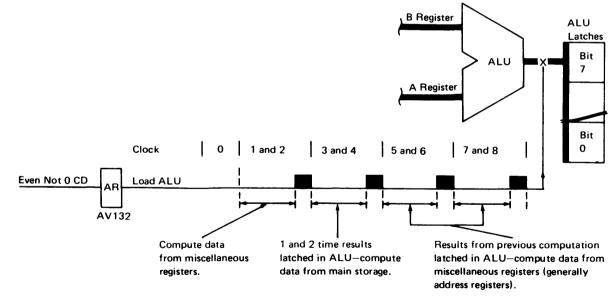

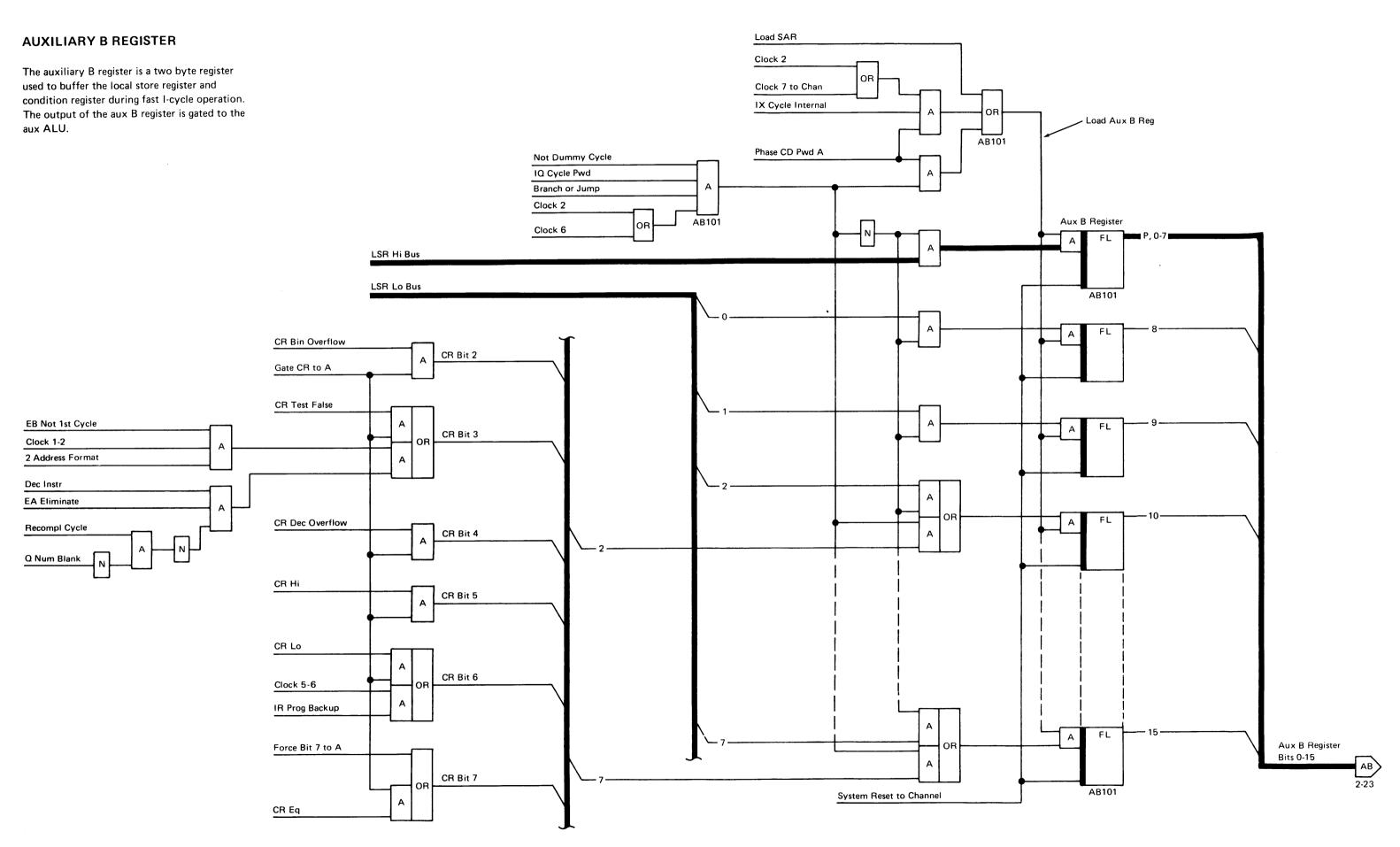

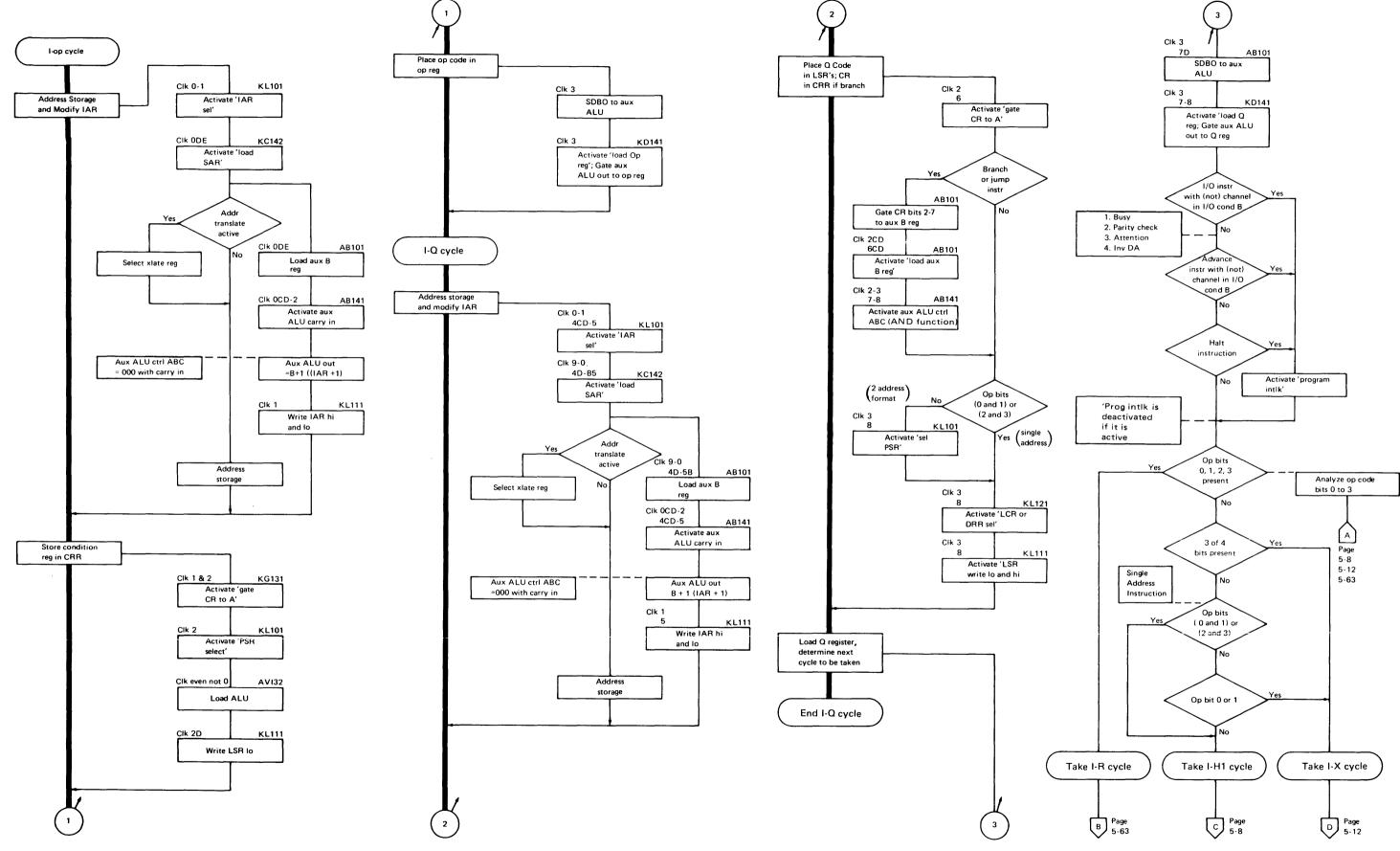

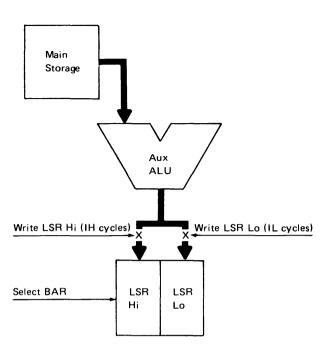

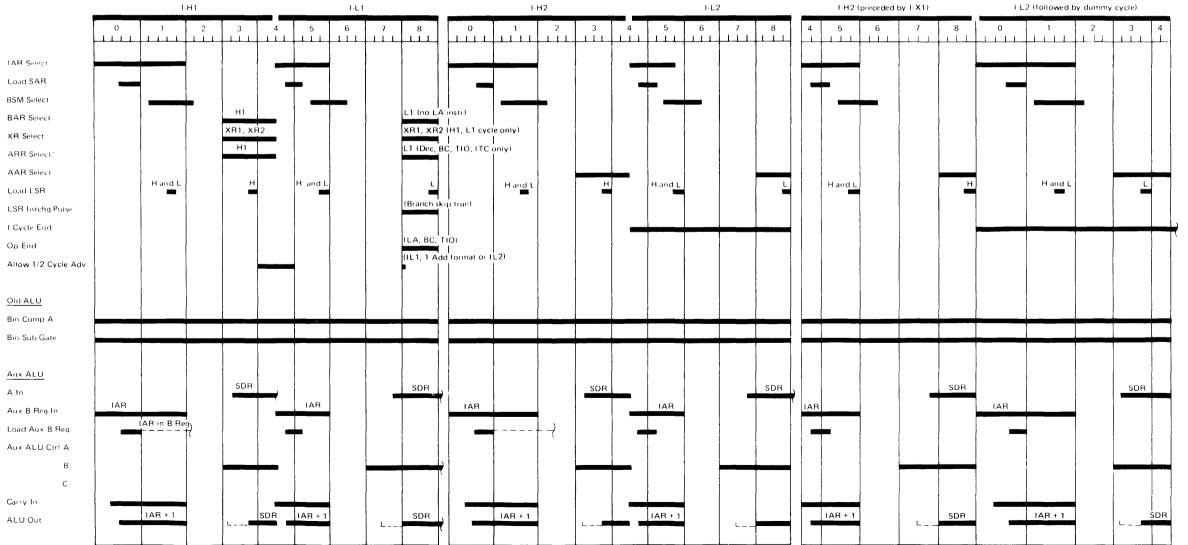

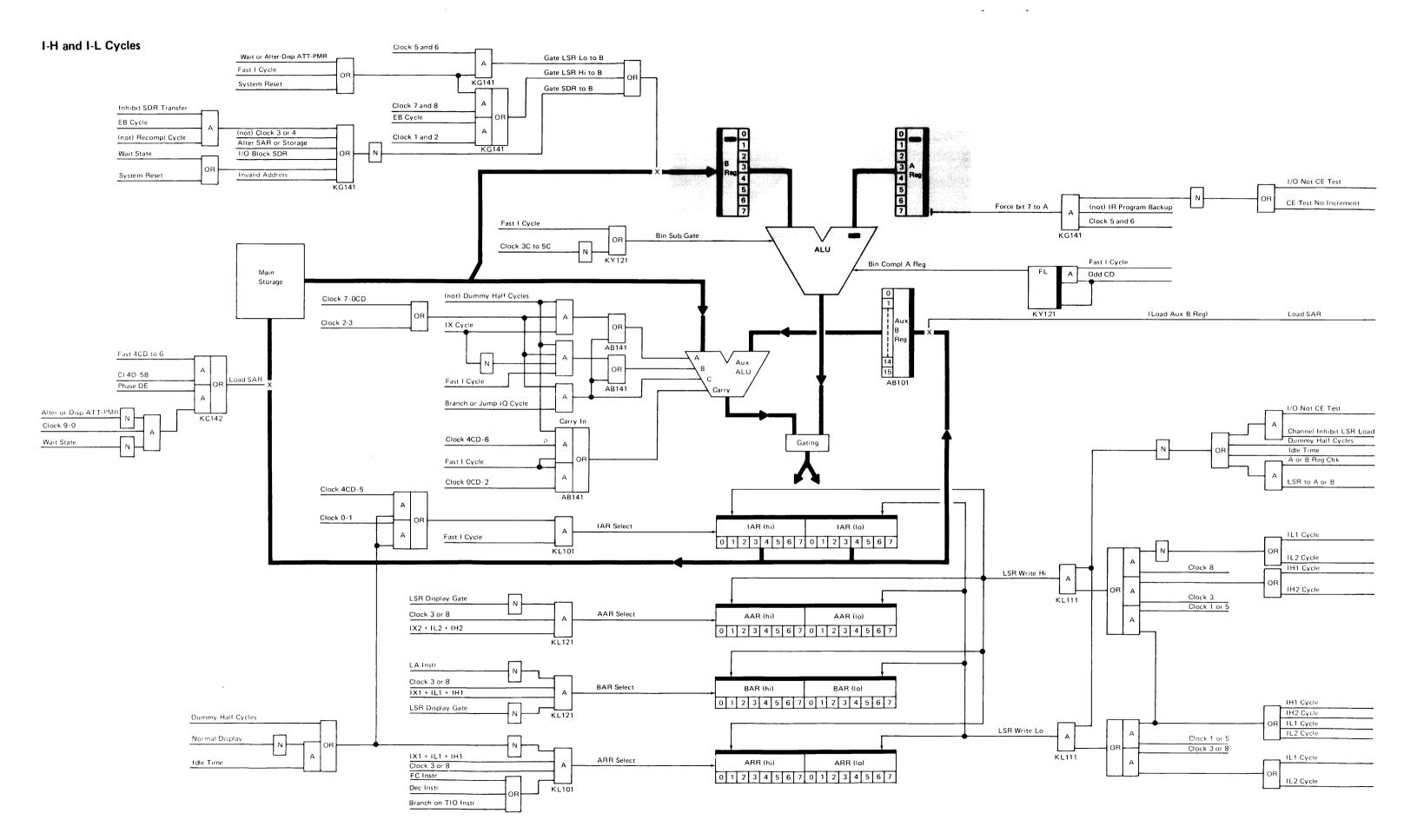

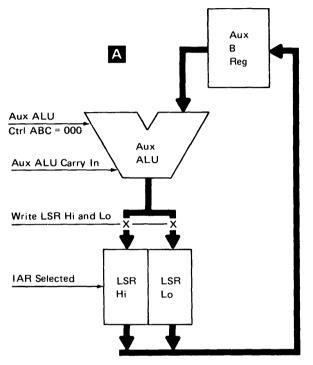

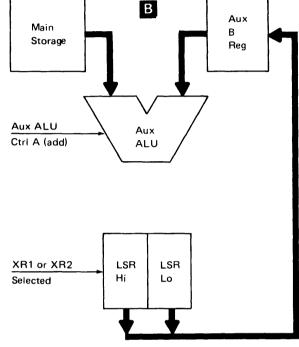

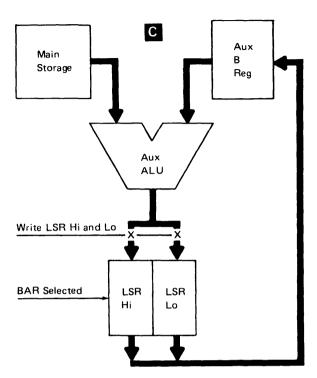

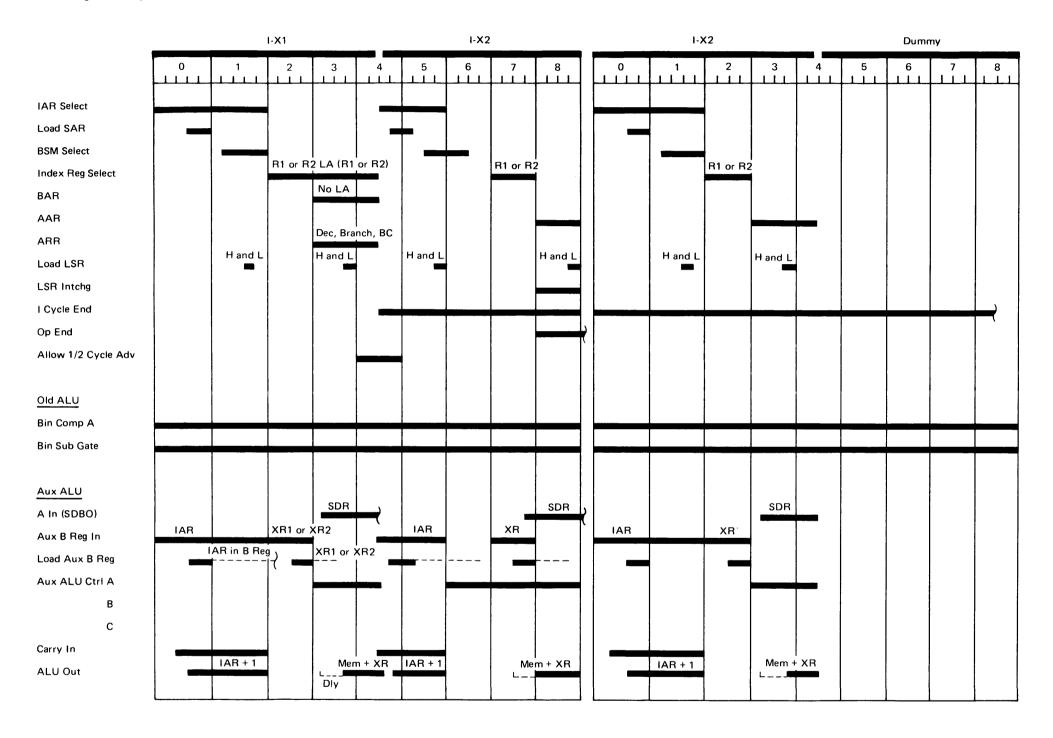

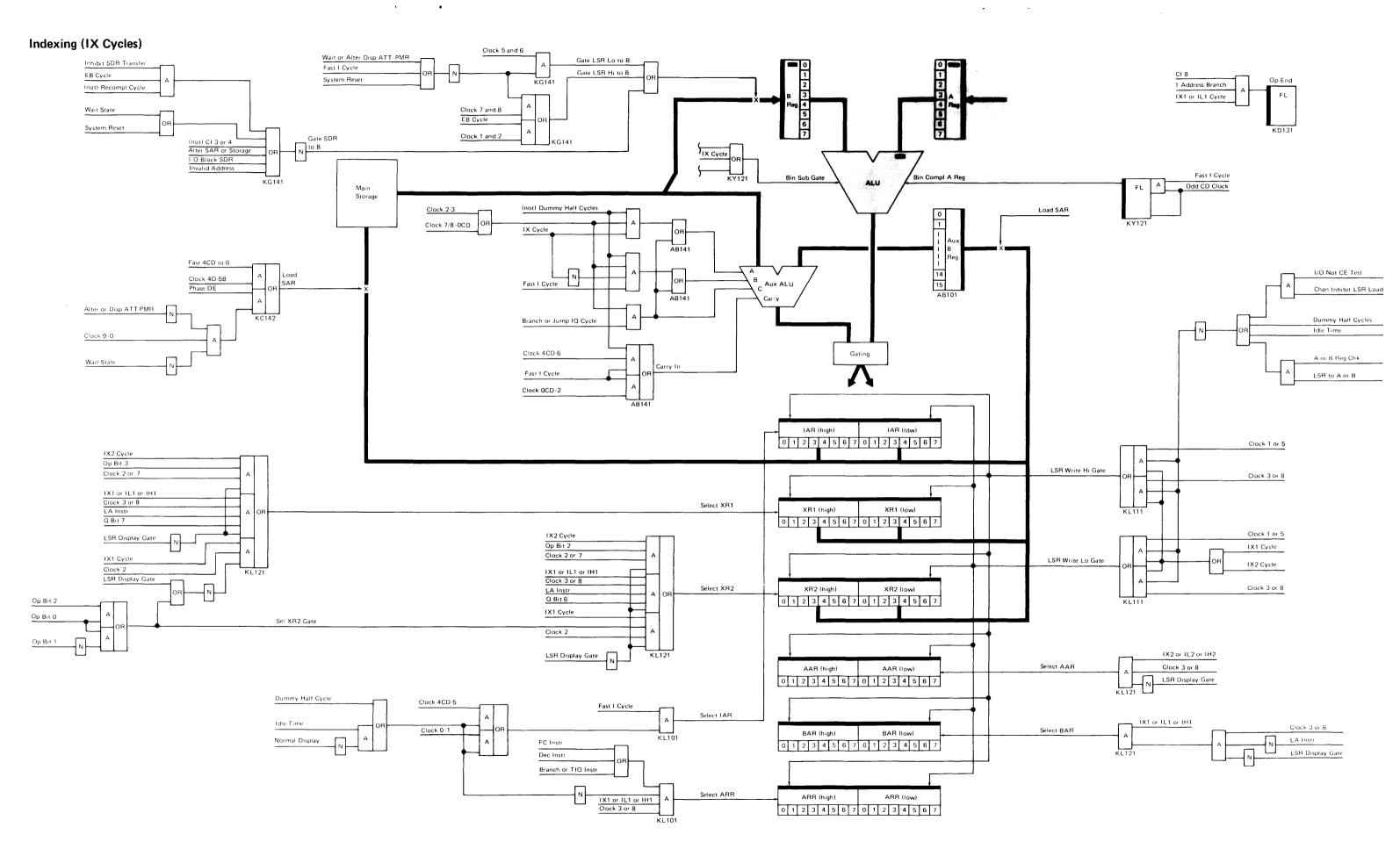

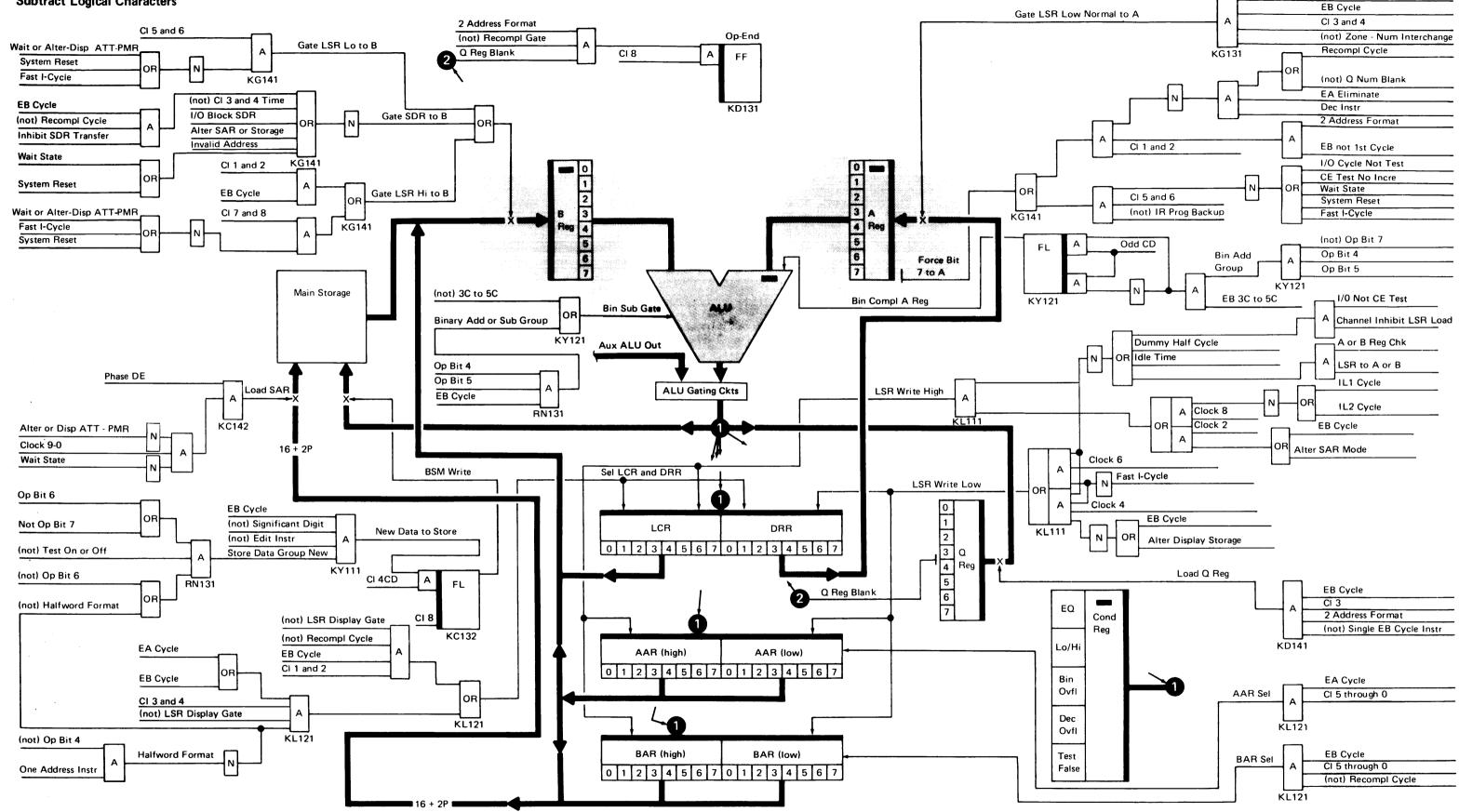

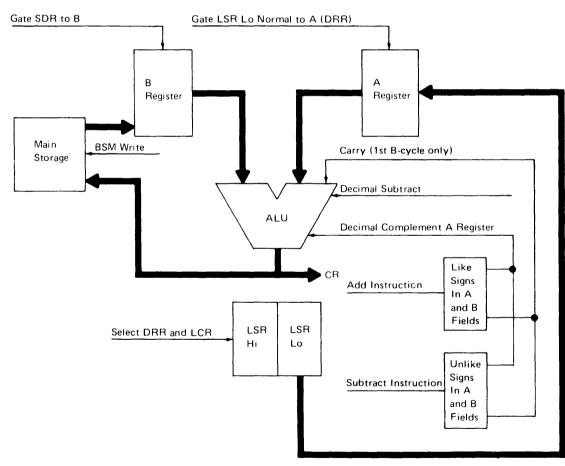

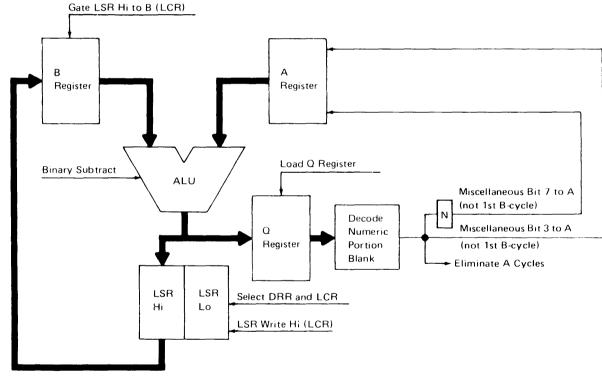

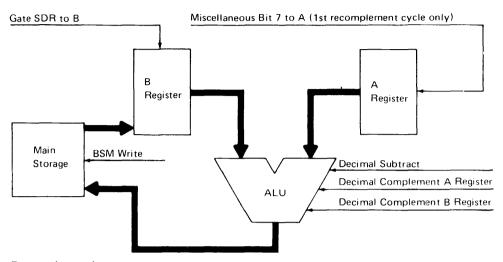

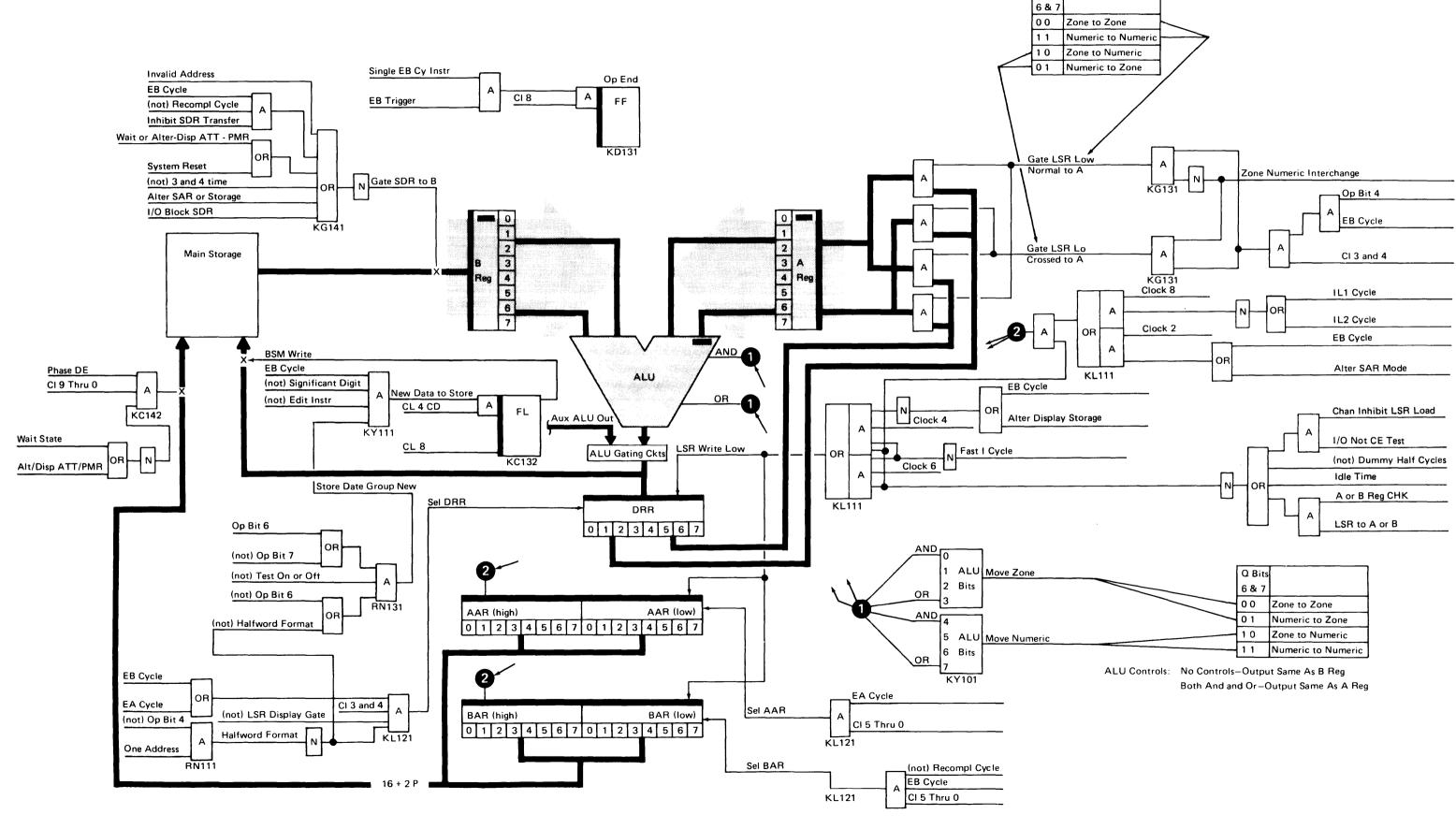

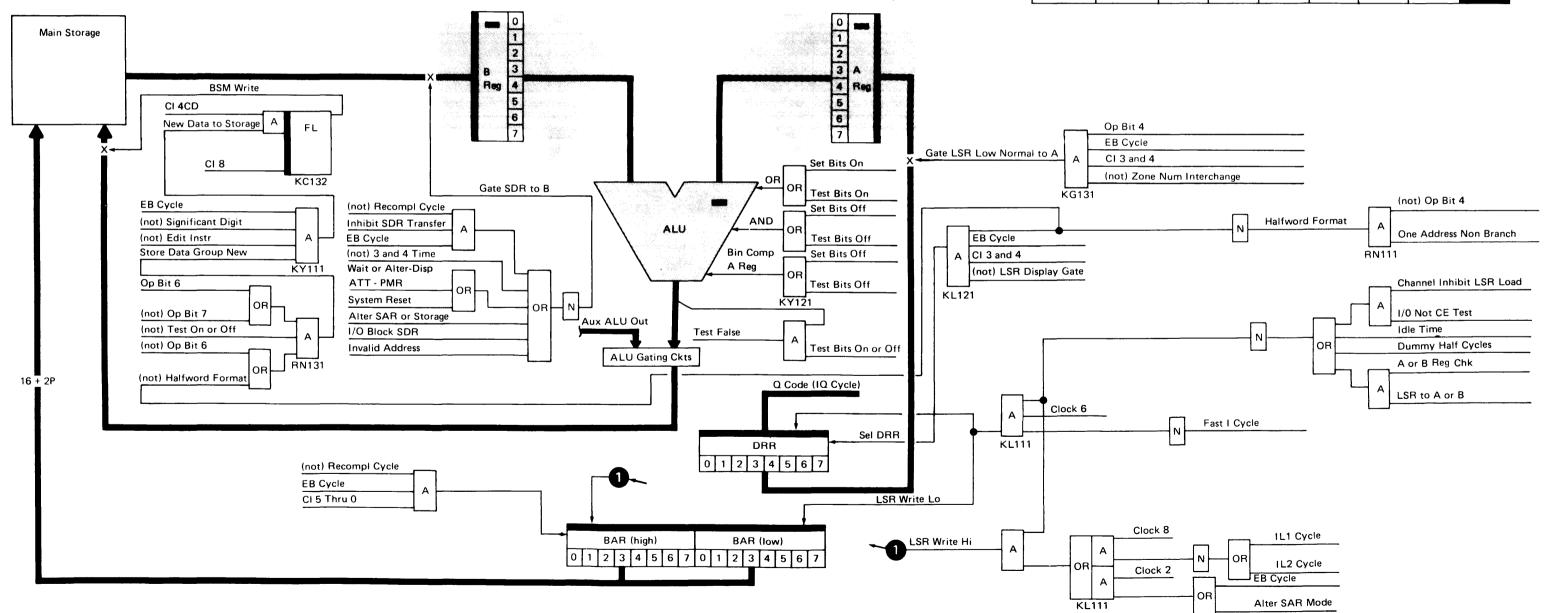

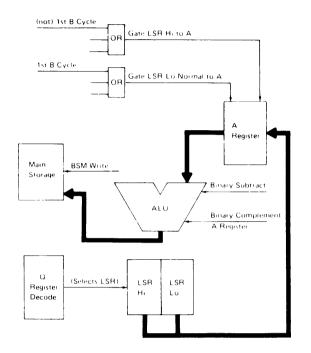

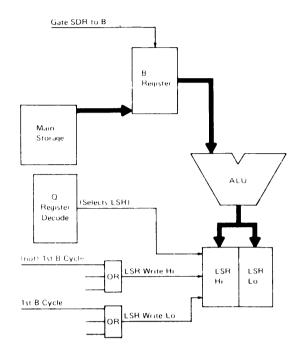

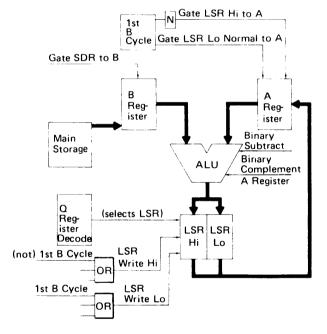

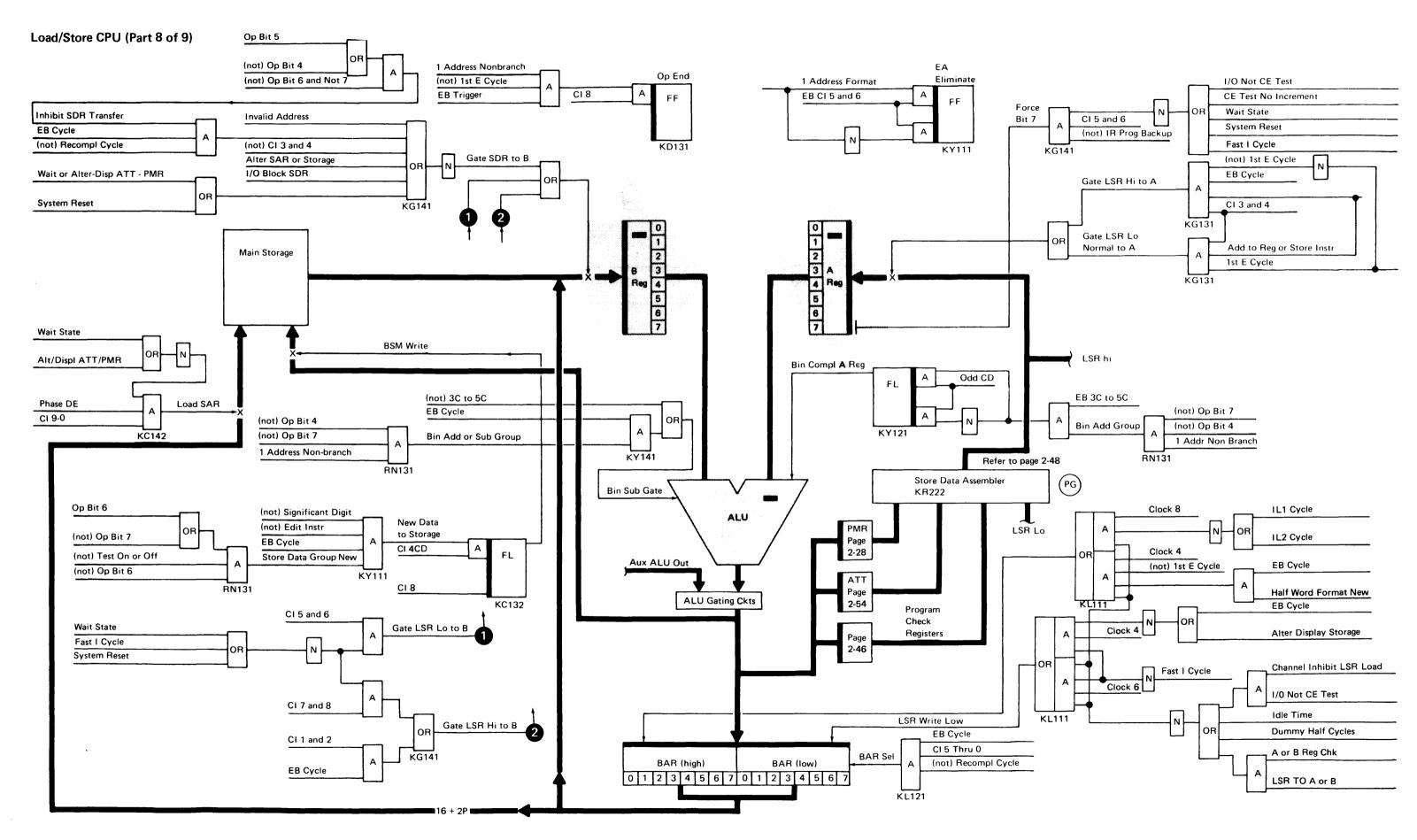

A 16-bit ALU was added to the Model D CPU for fast I cycle processing and is referred to in this manual as the auxiliary (aux) ALU. Wherever just ALU is used, it refers to the original Model 15 ALU.

This manual is intended for use by GSD customer engineers for use in the classroom and for recall when servicing in a free-lance mode.

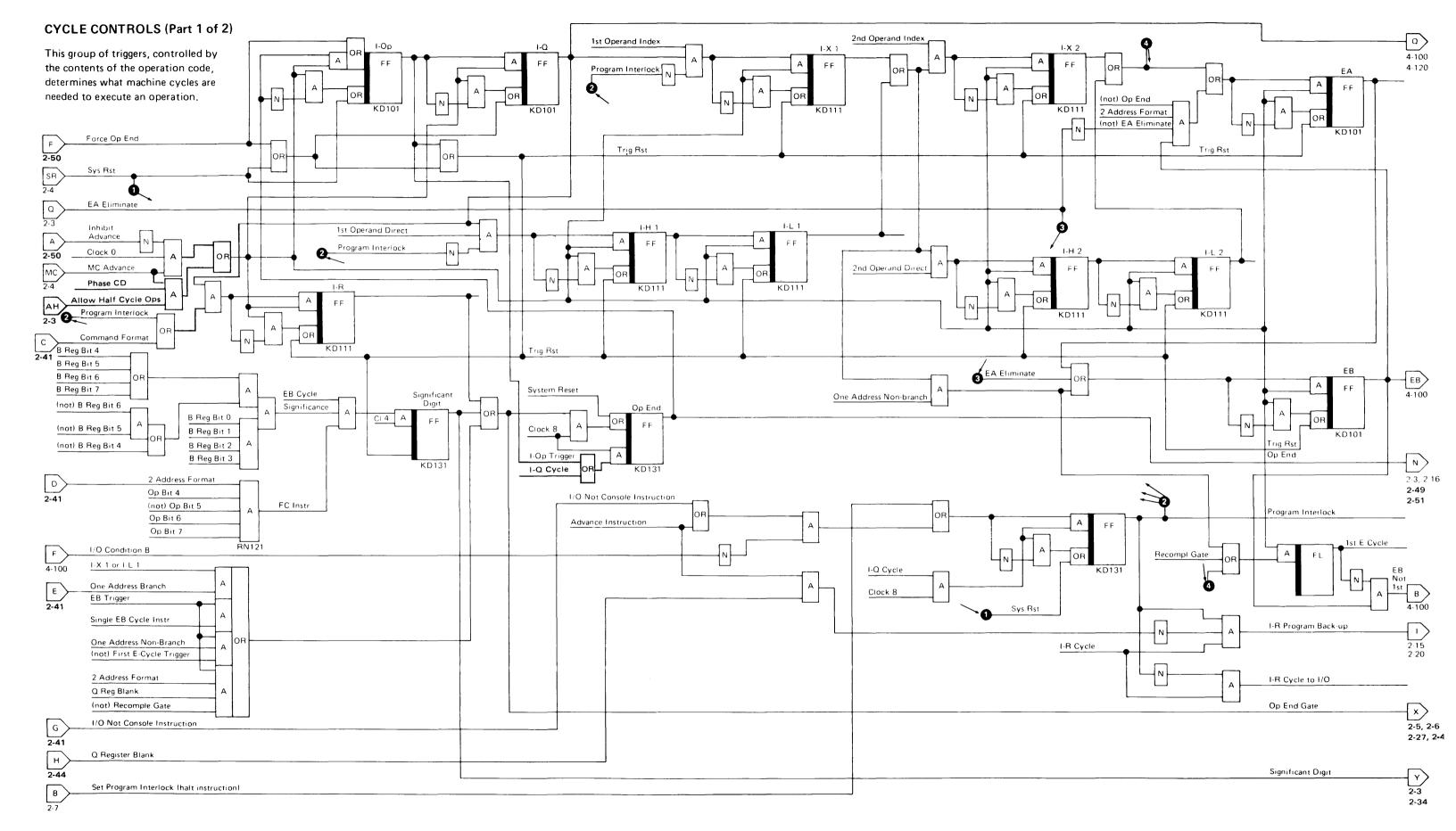

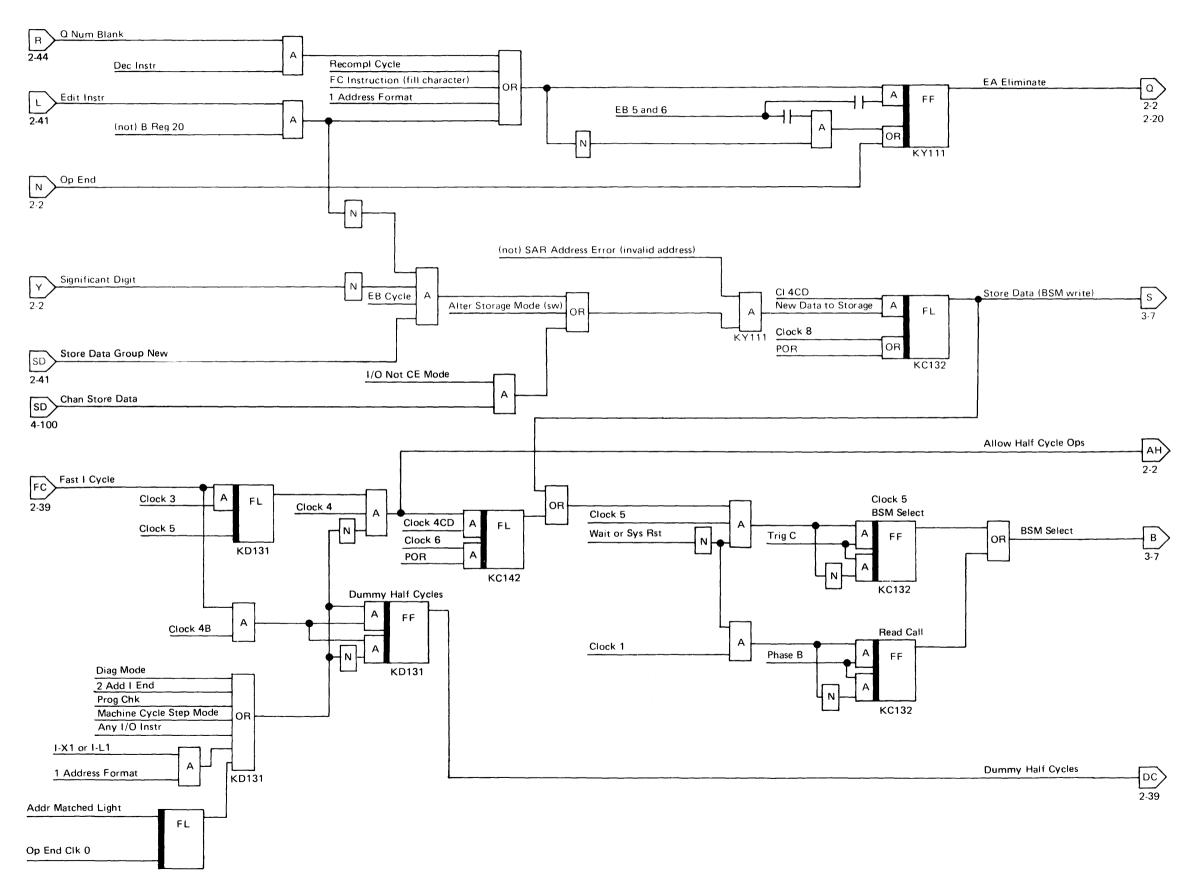

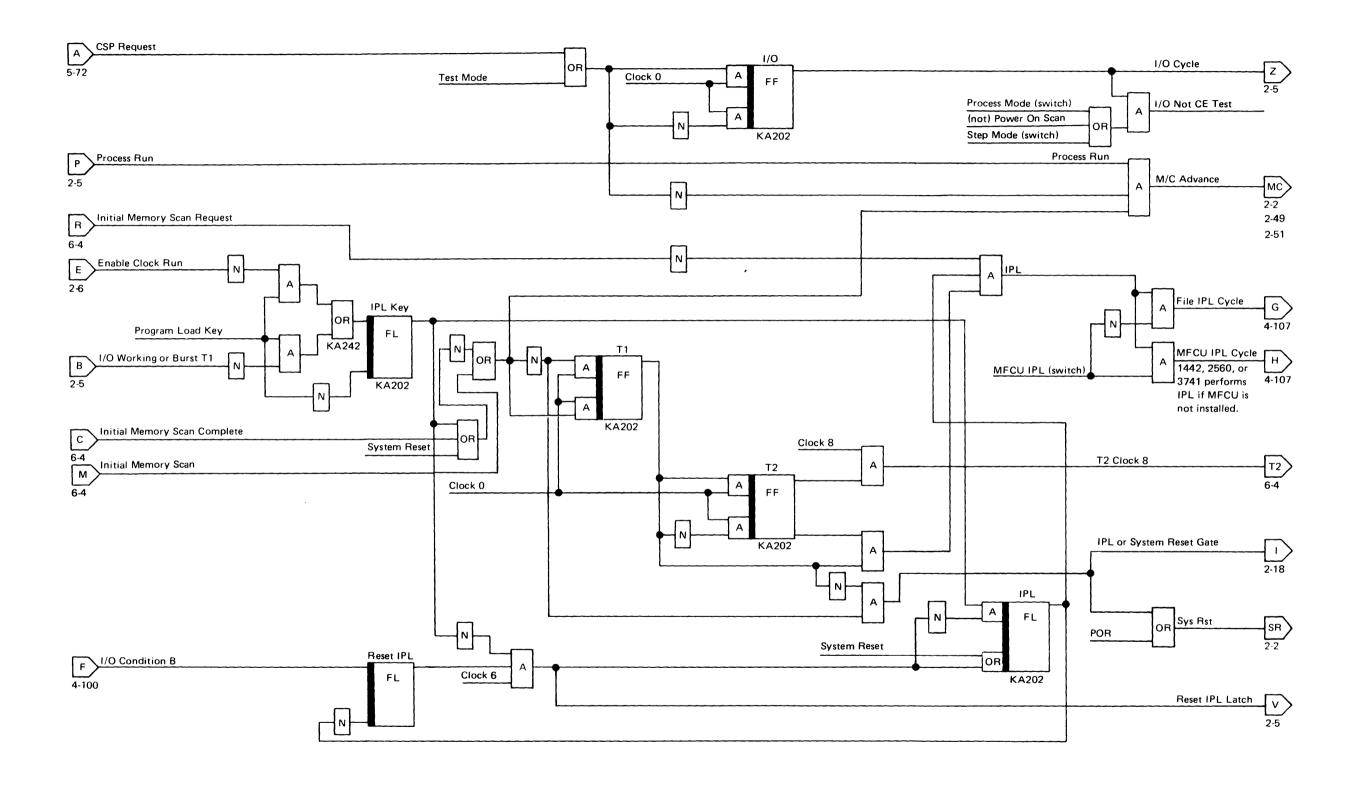

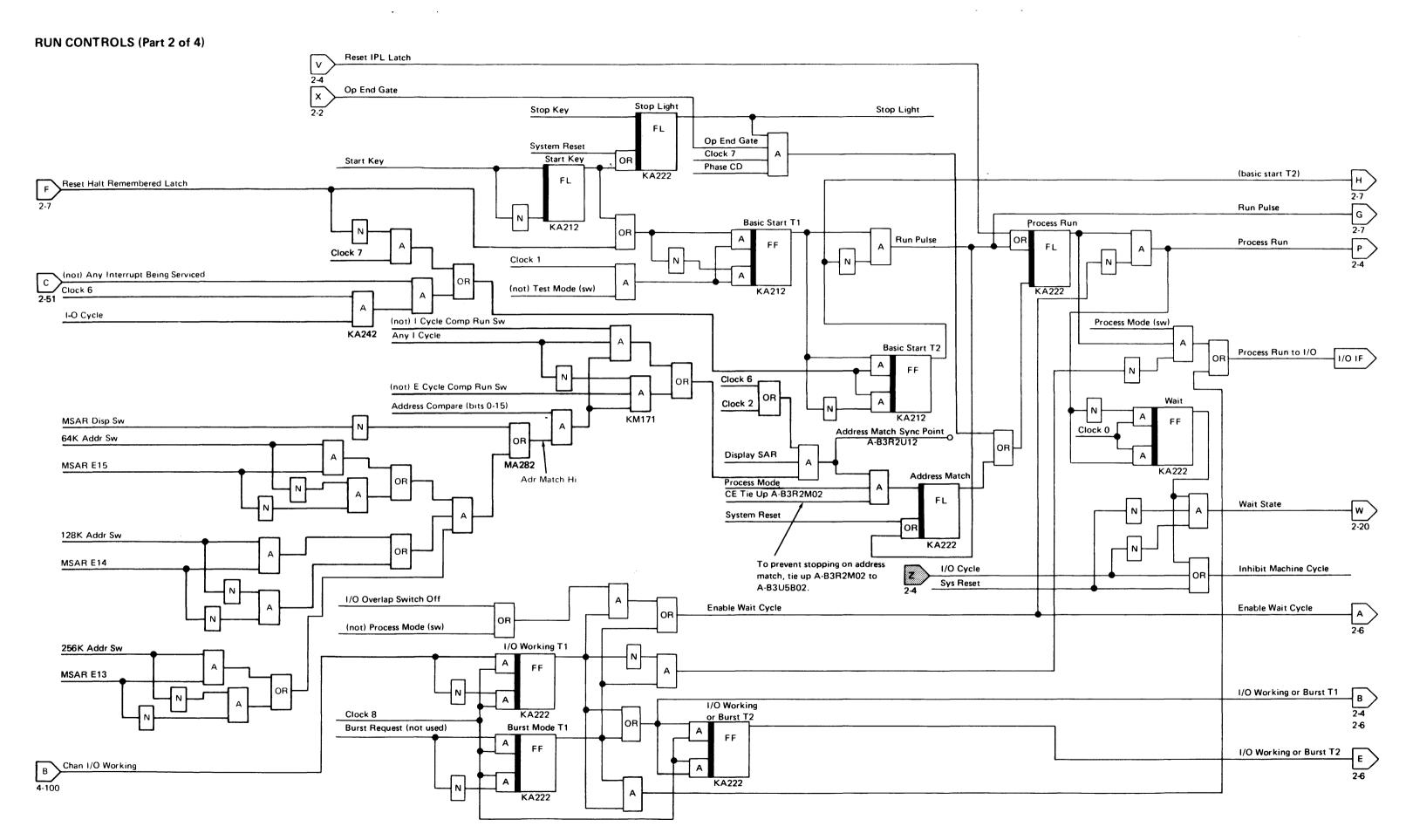

The manual gives an explanation of the logical circuit functions and major objectives. With this information, the CE can interpret the operation of circuits illustrated in the companion diagrams.

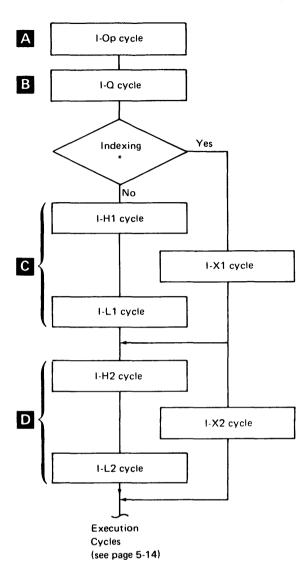

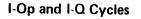

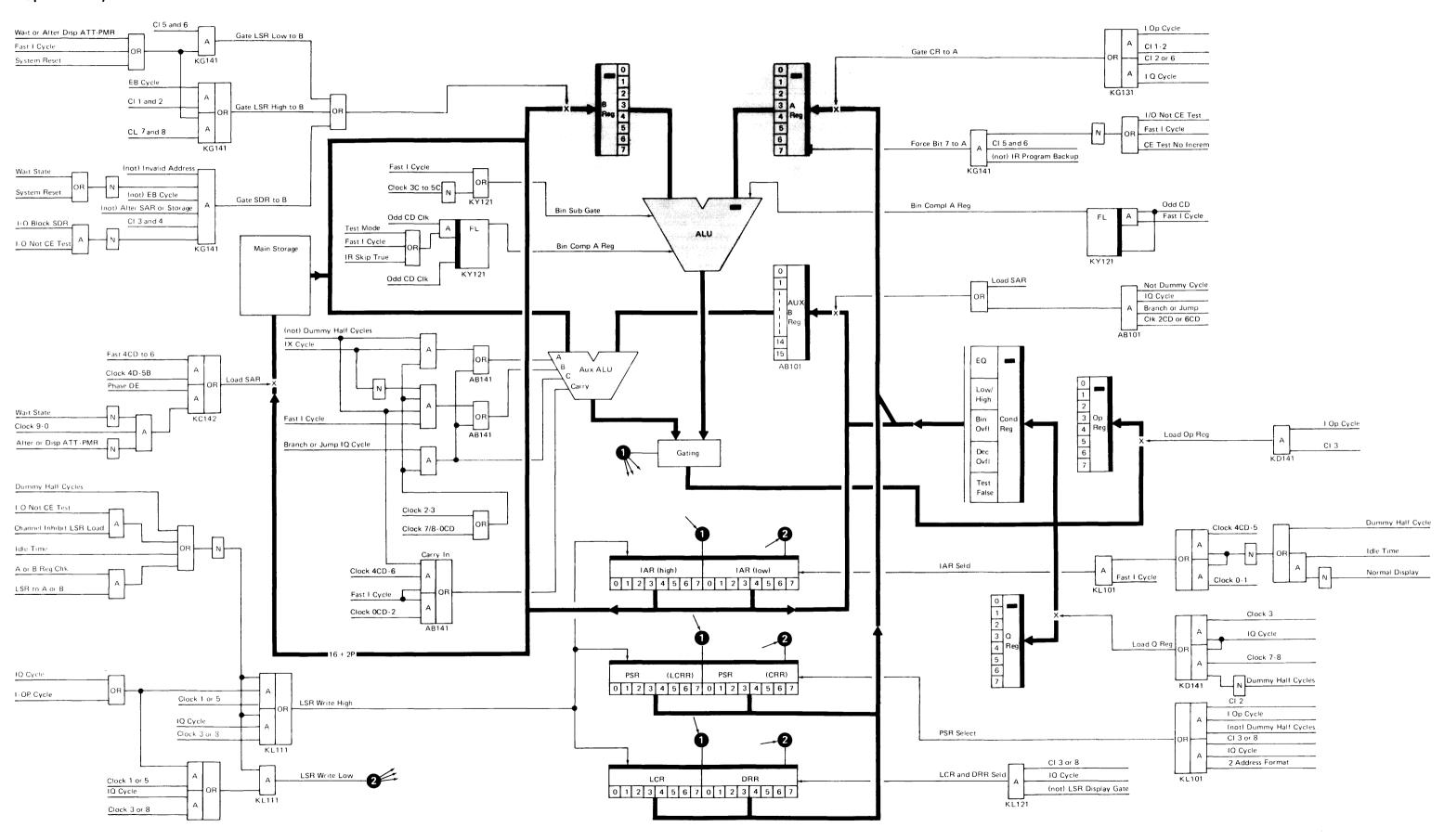

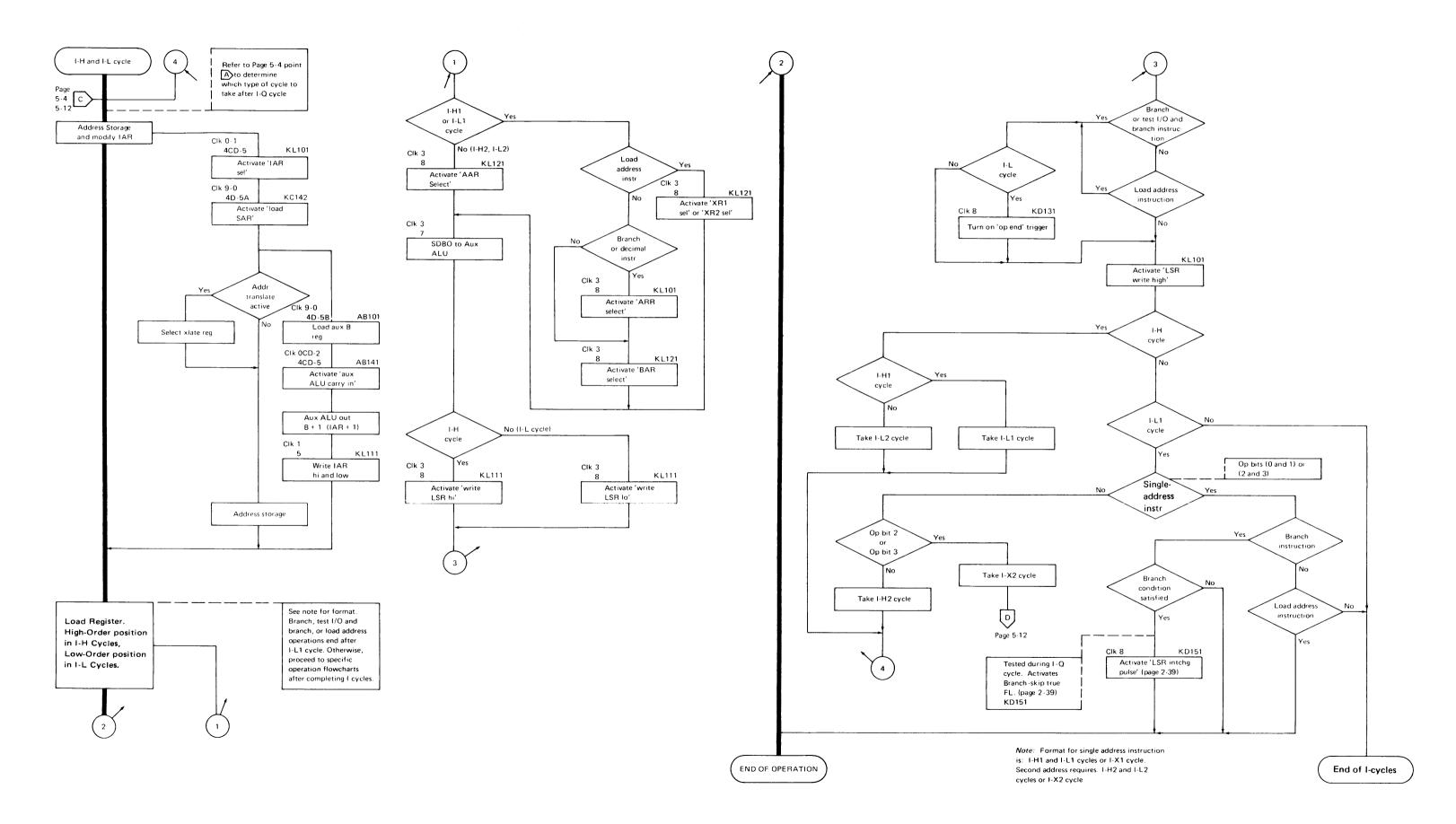

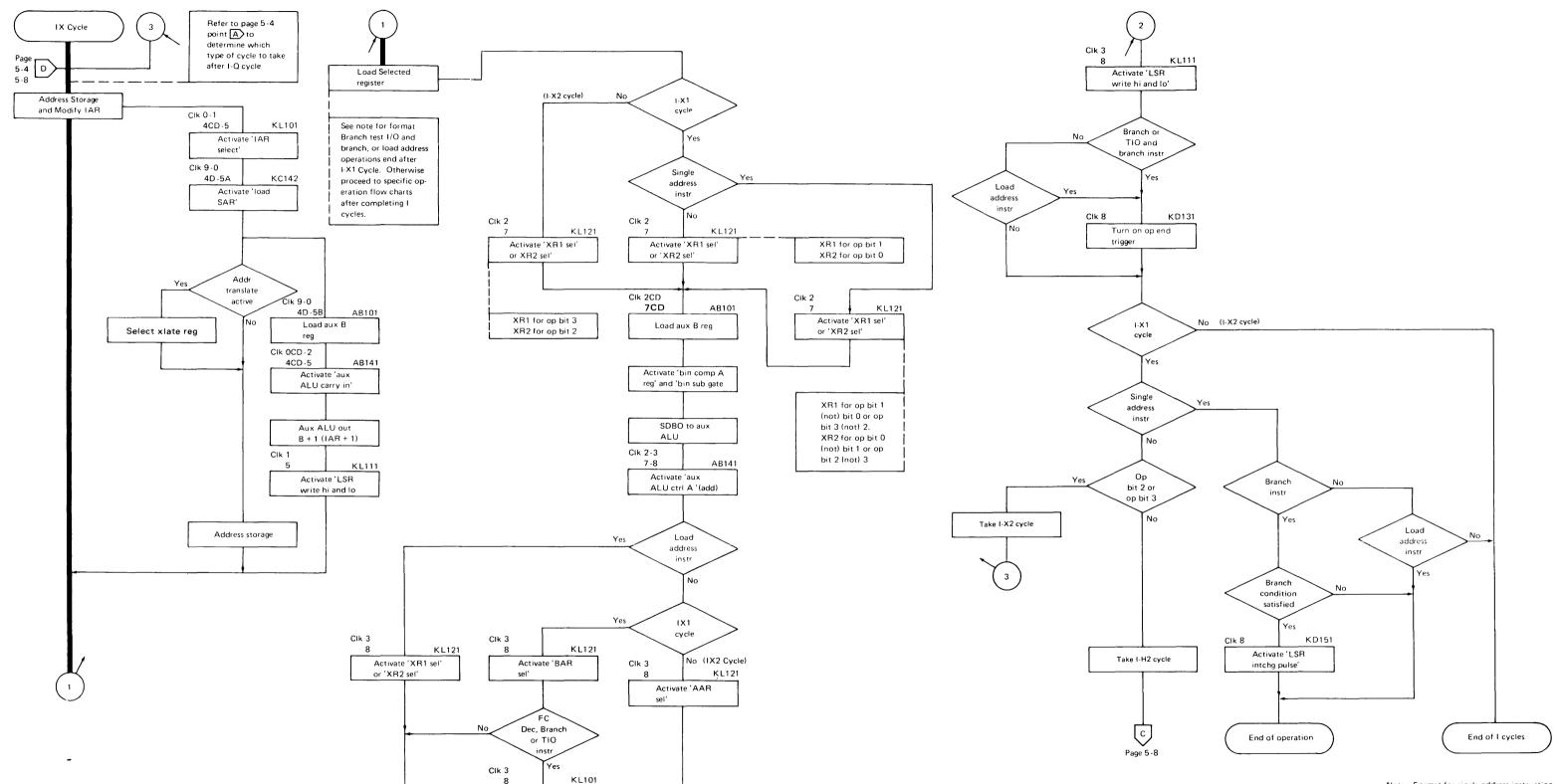

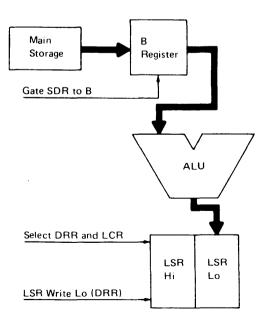

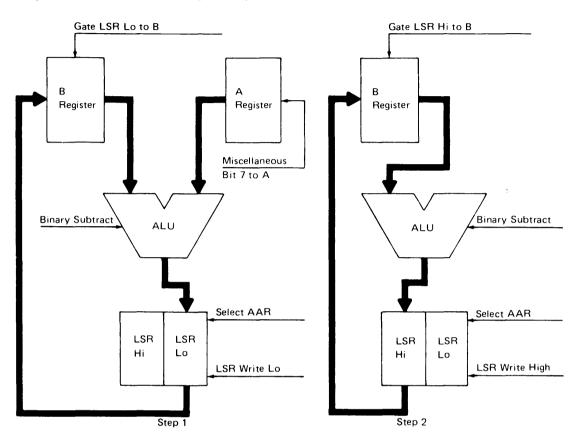

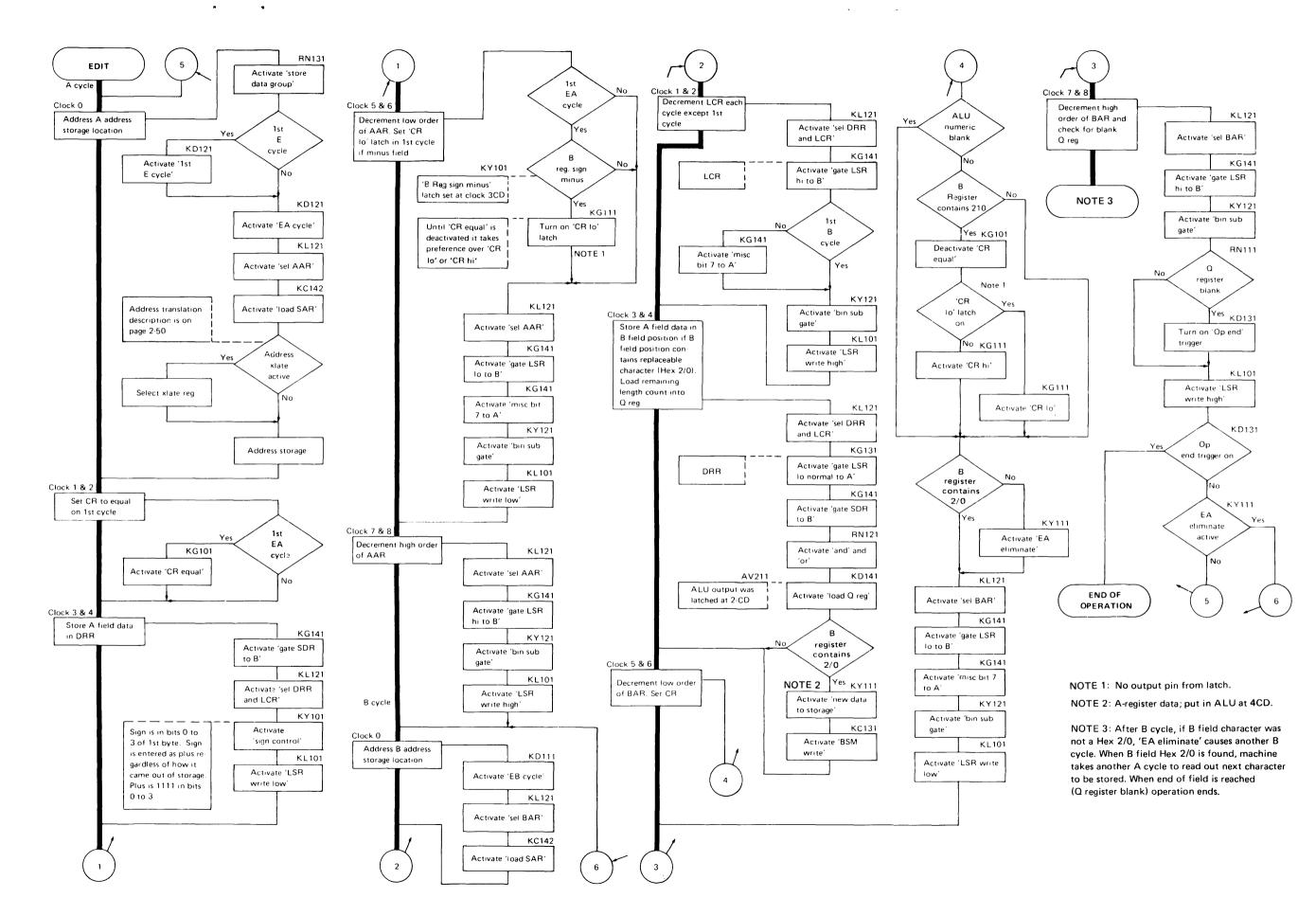

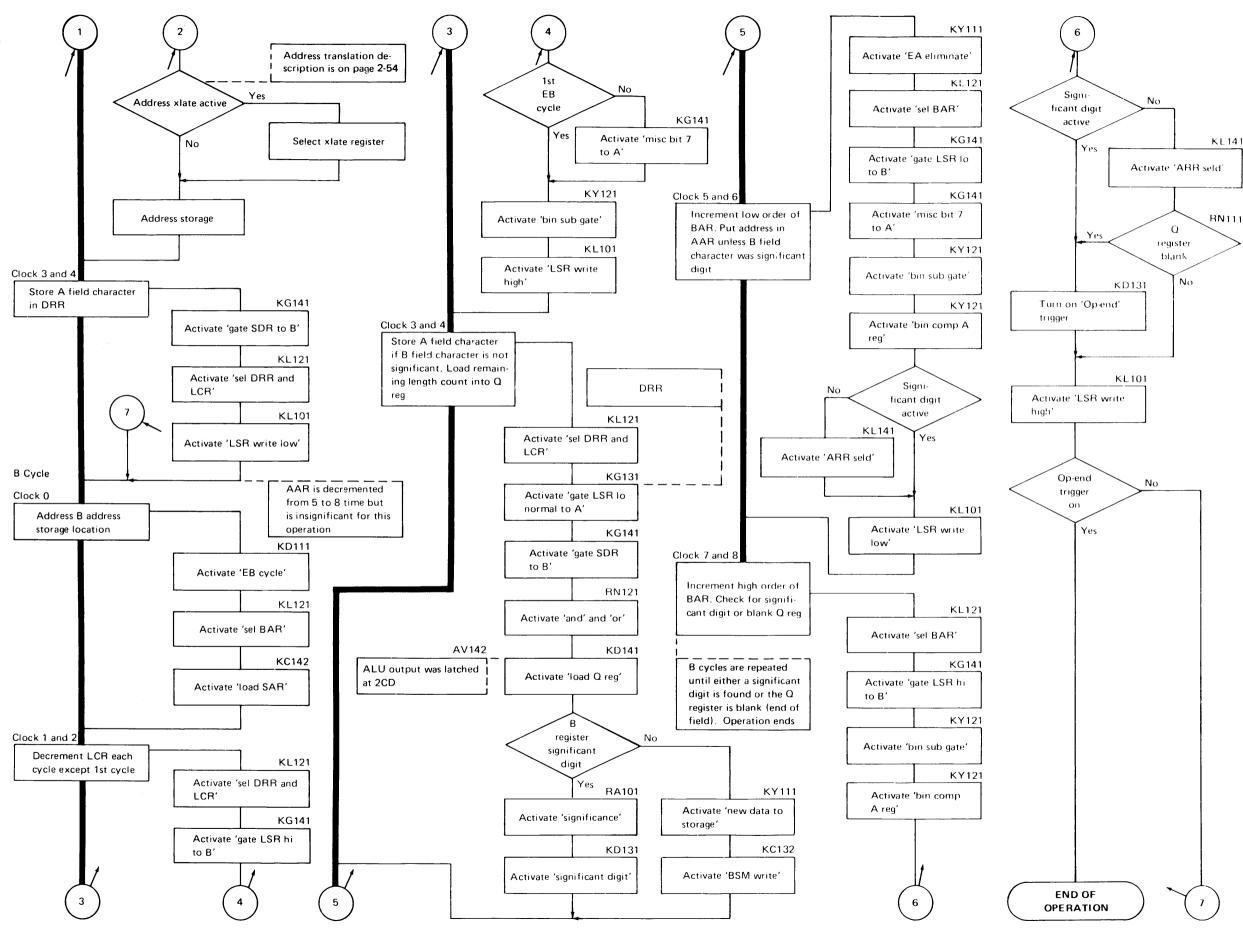

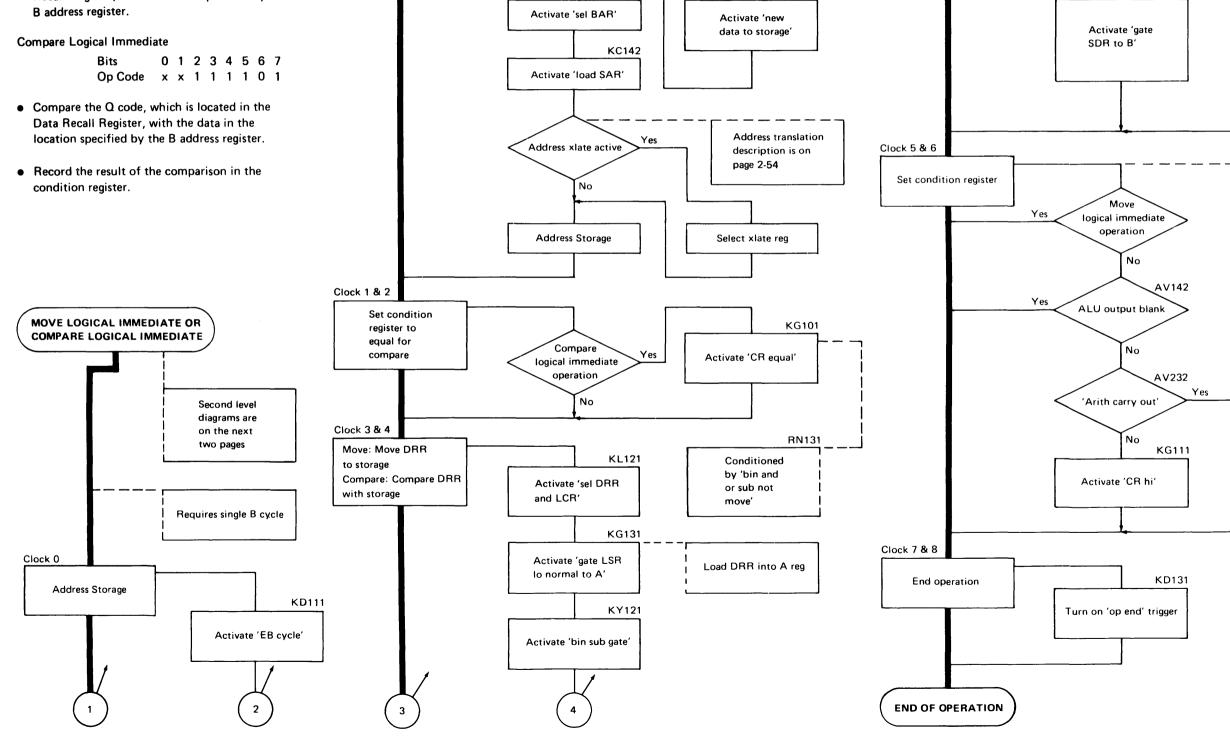

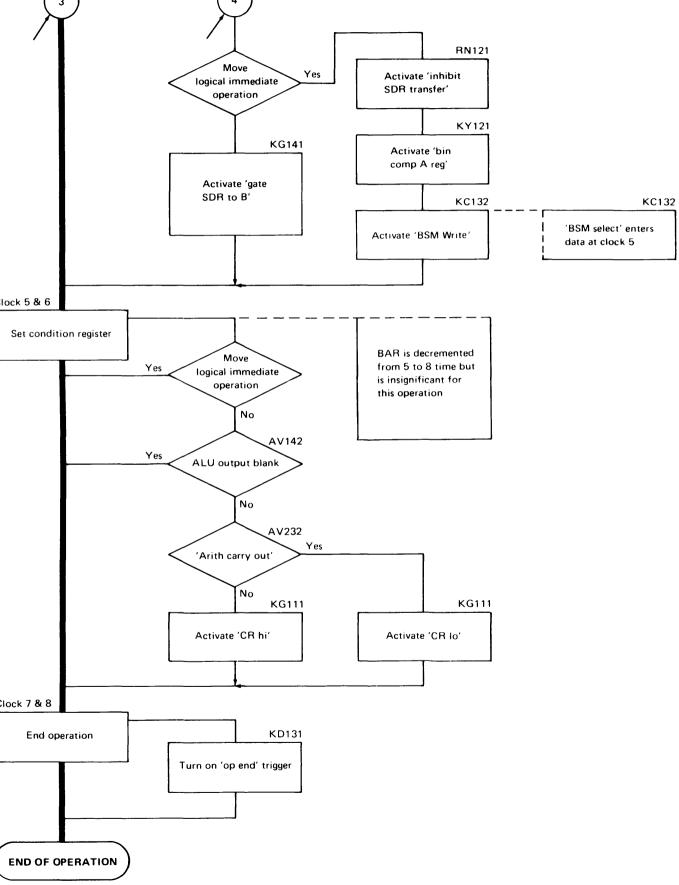

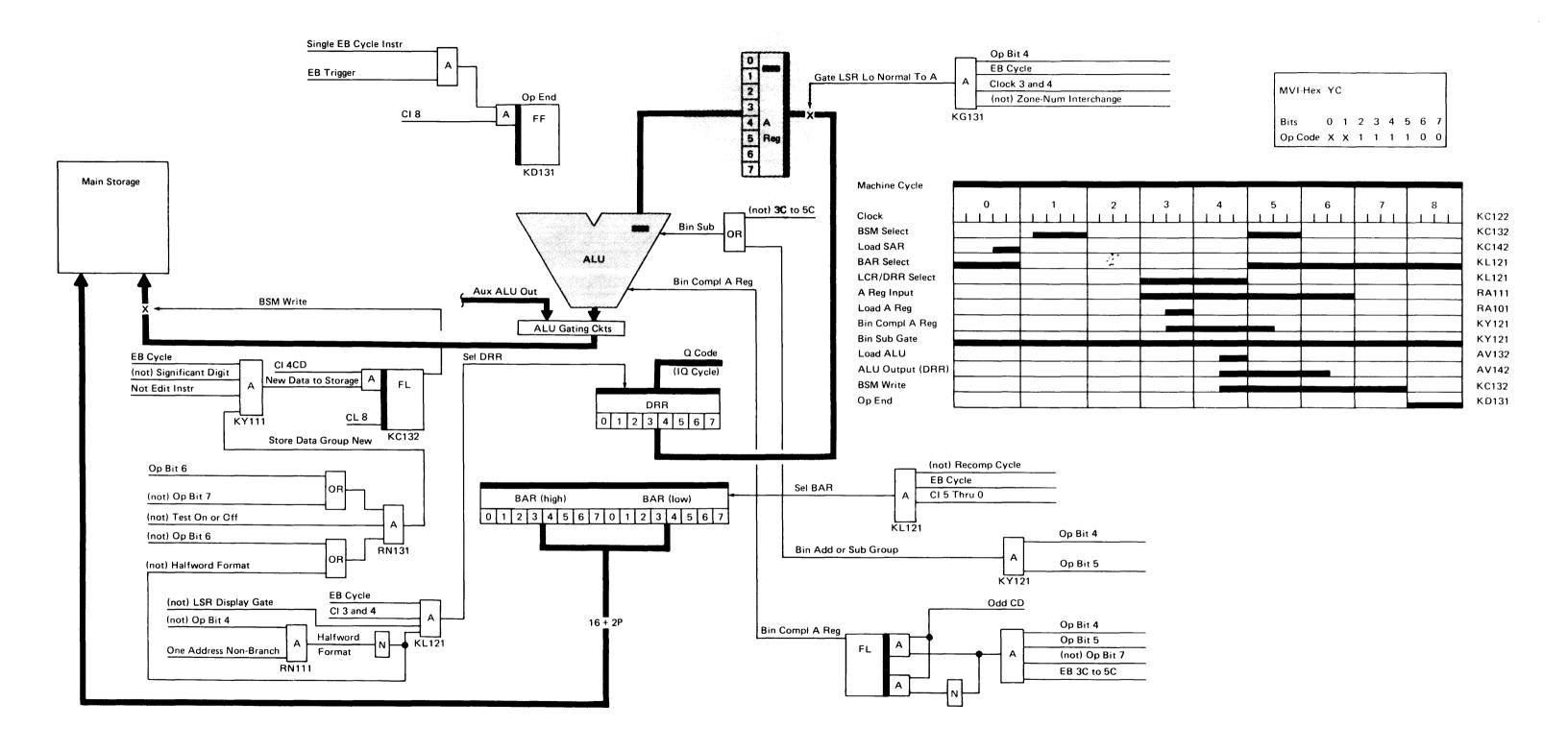

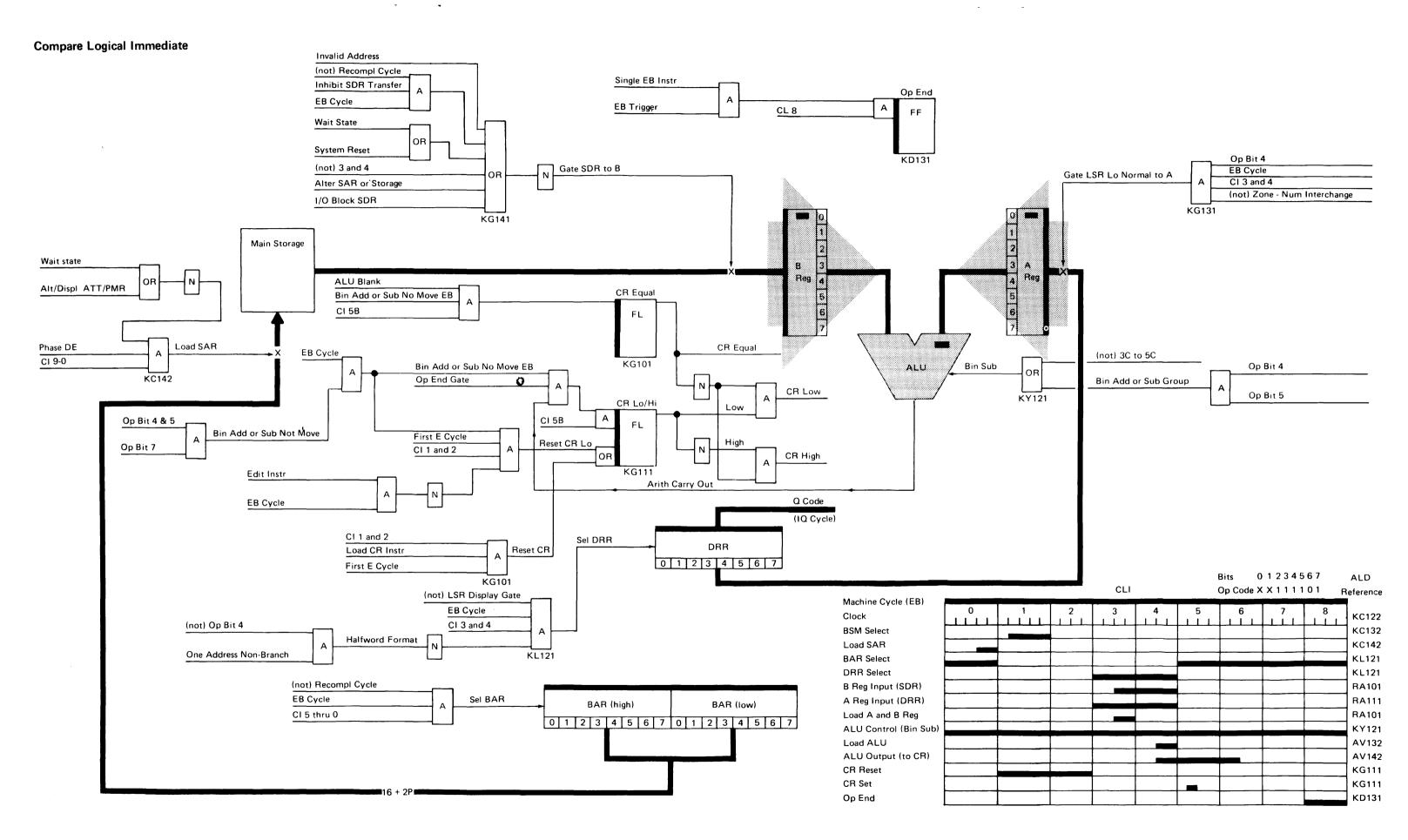

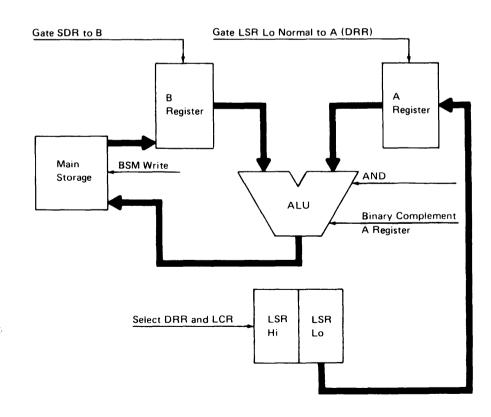

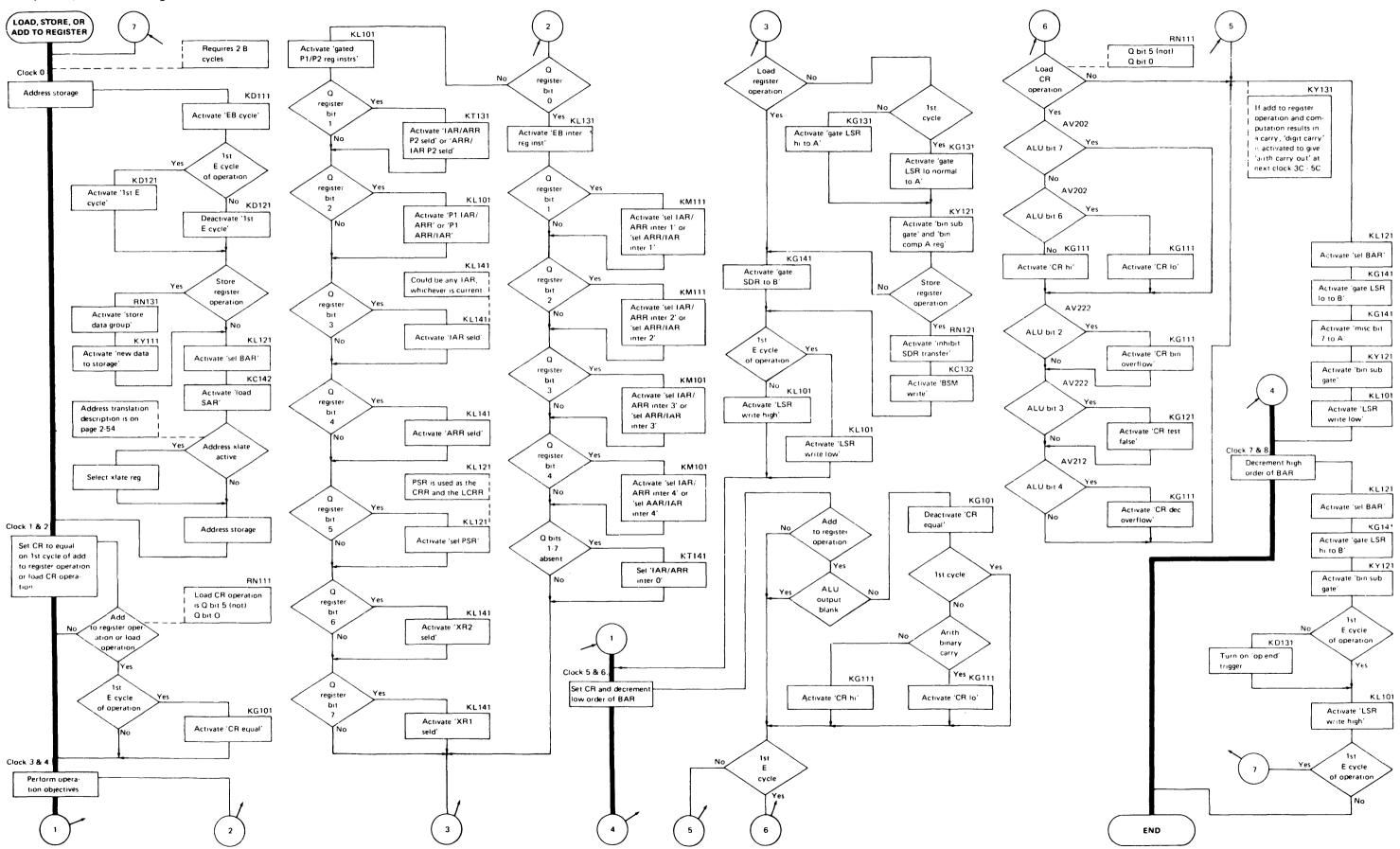

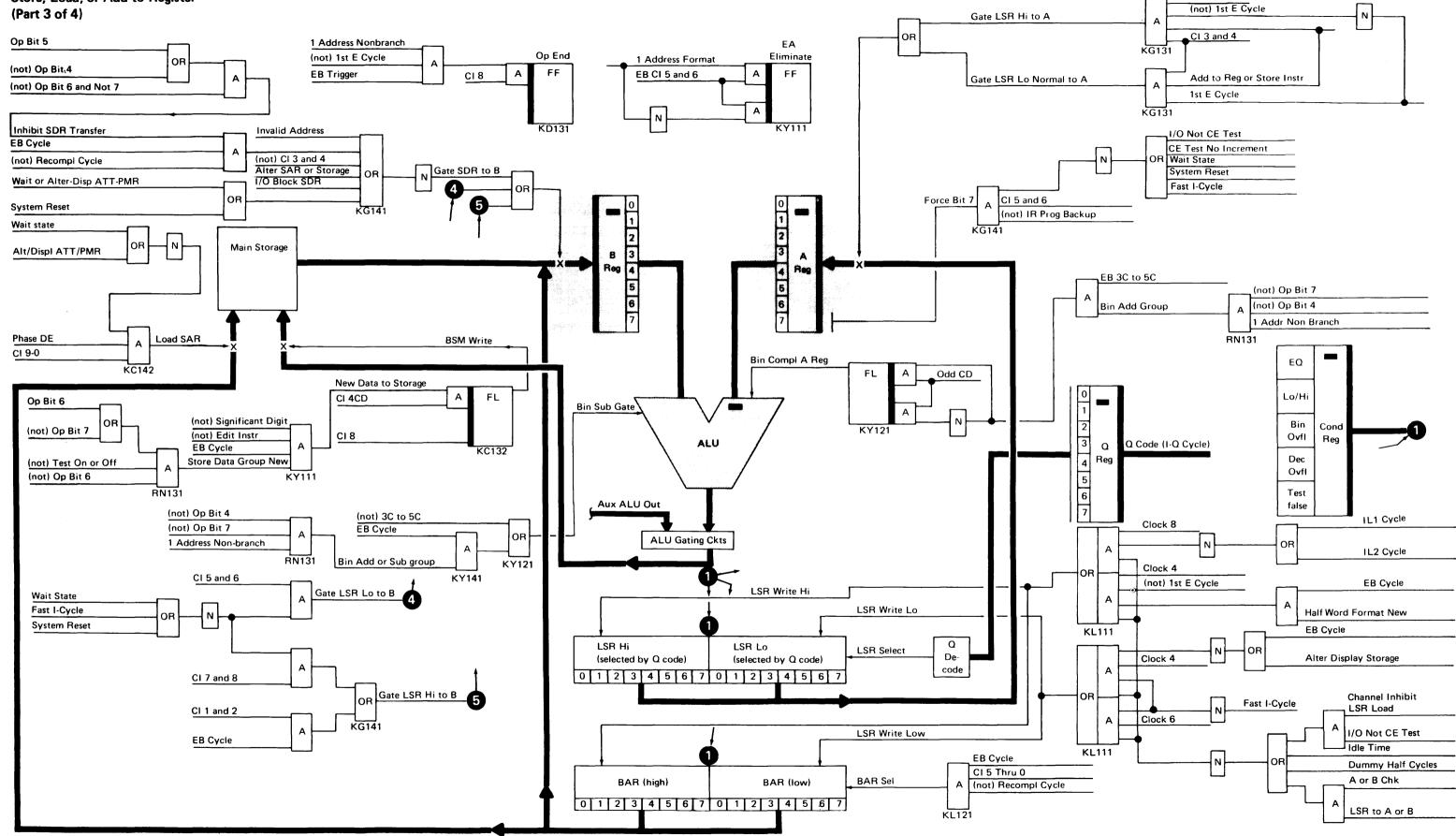

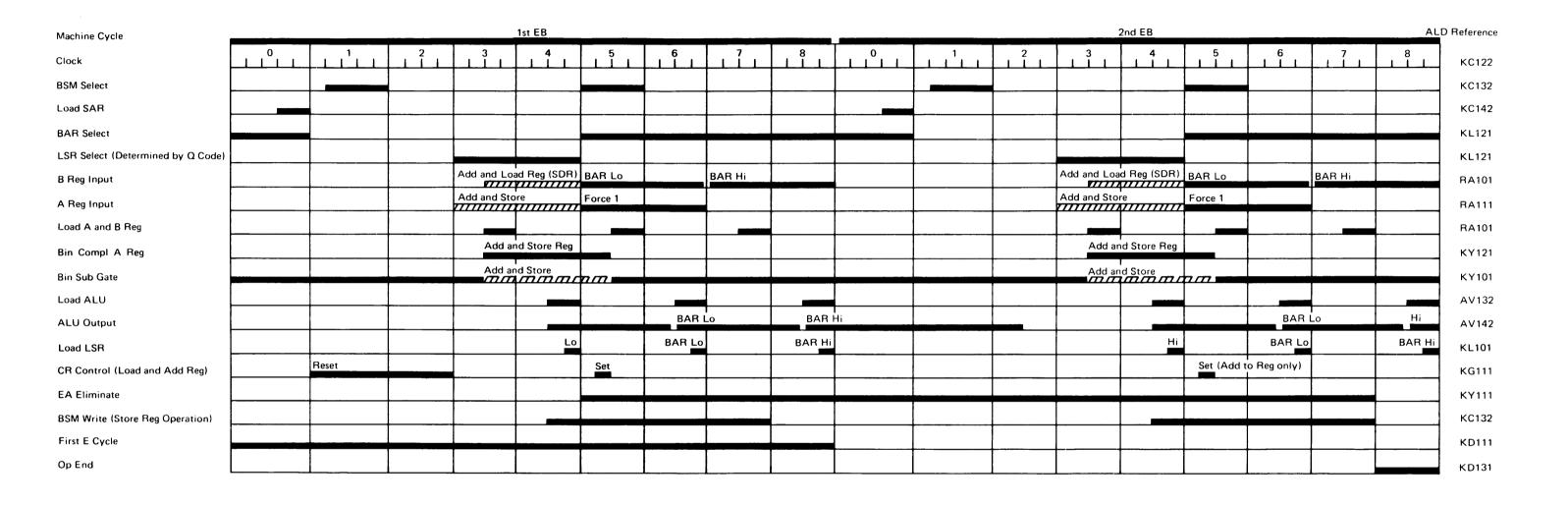

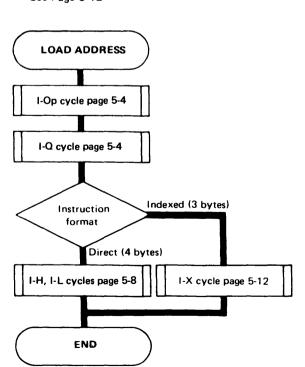

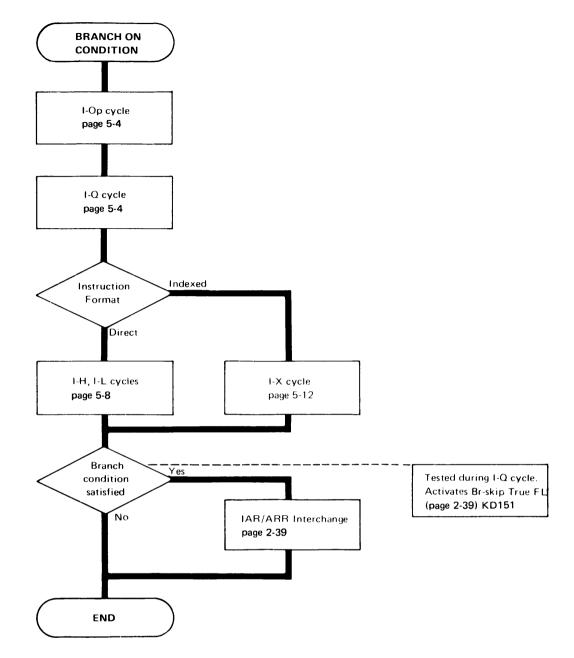

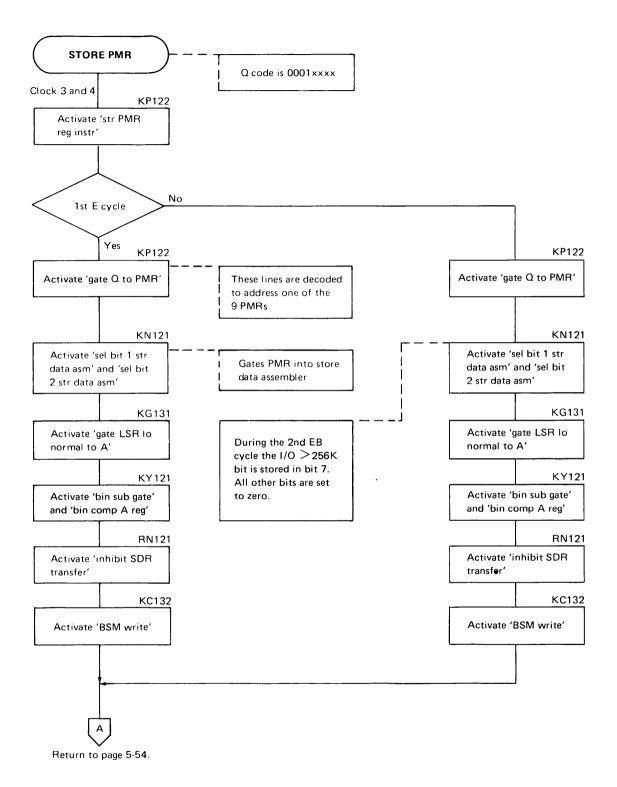

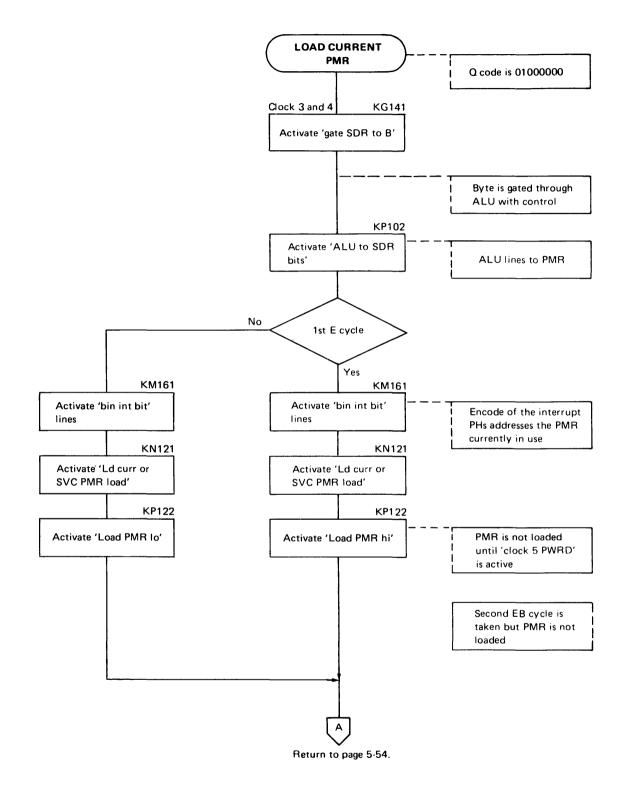

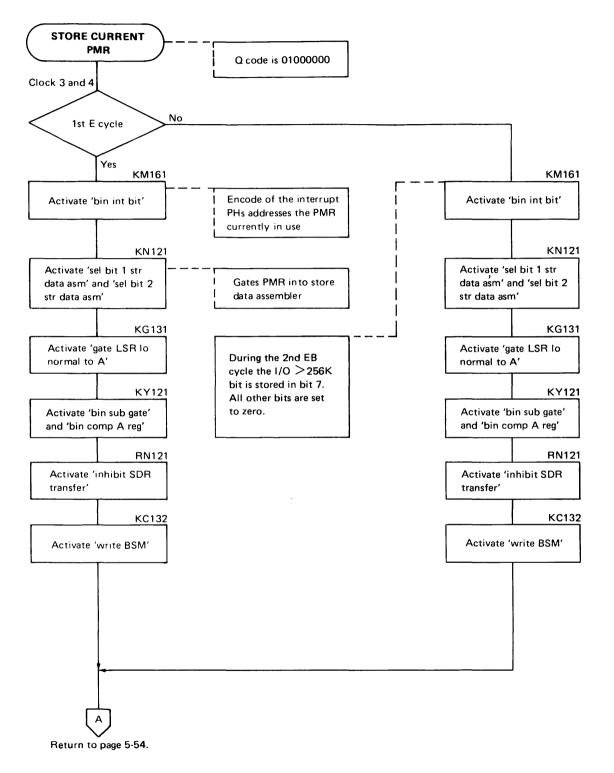

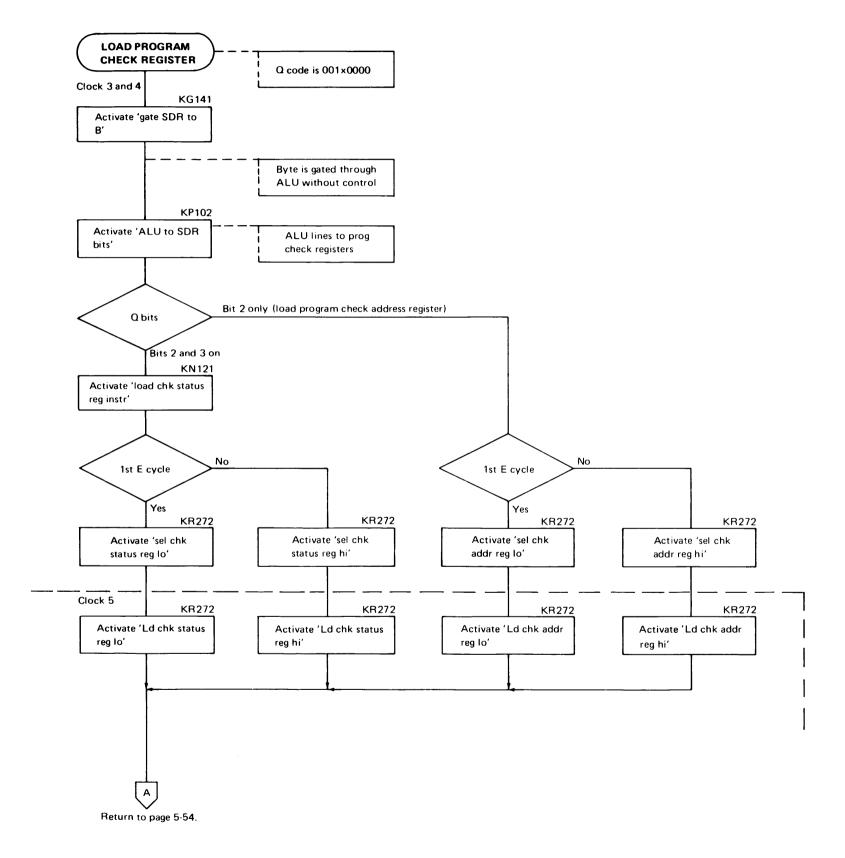

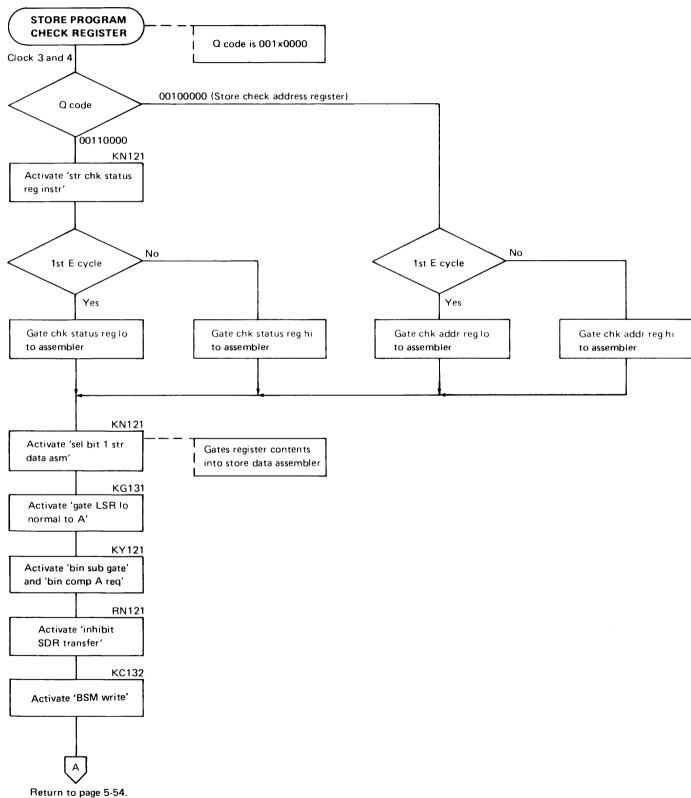

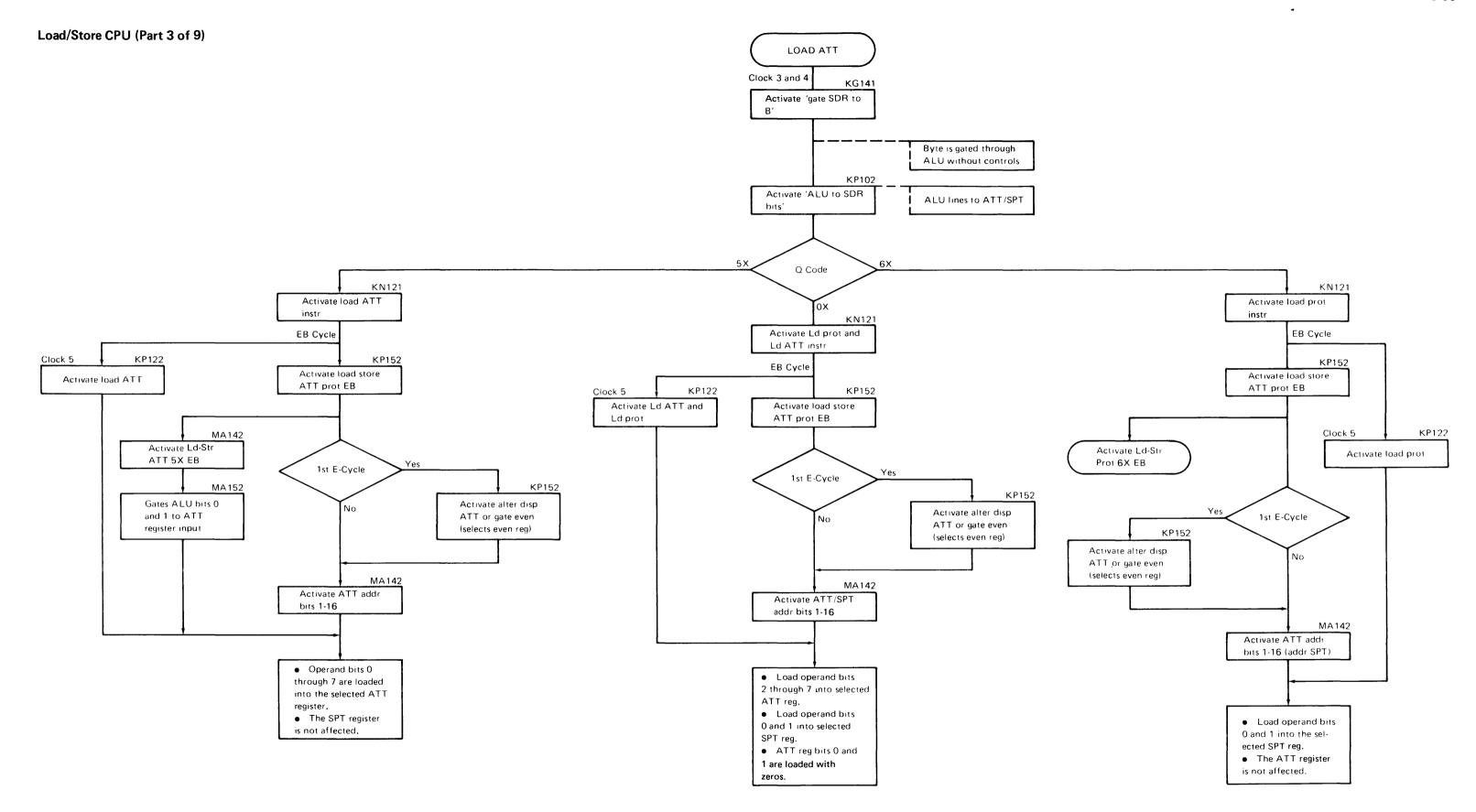

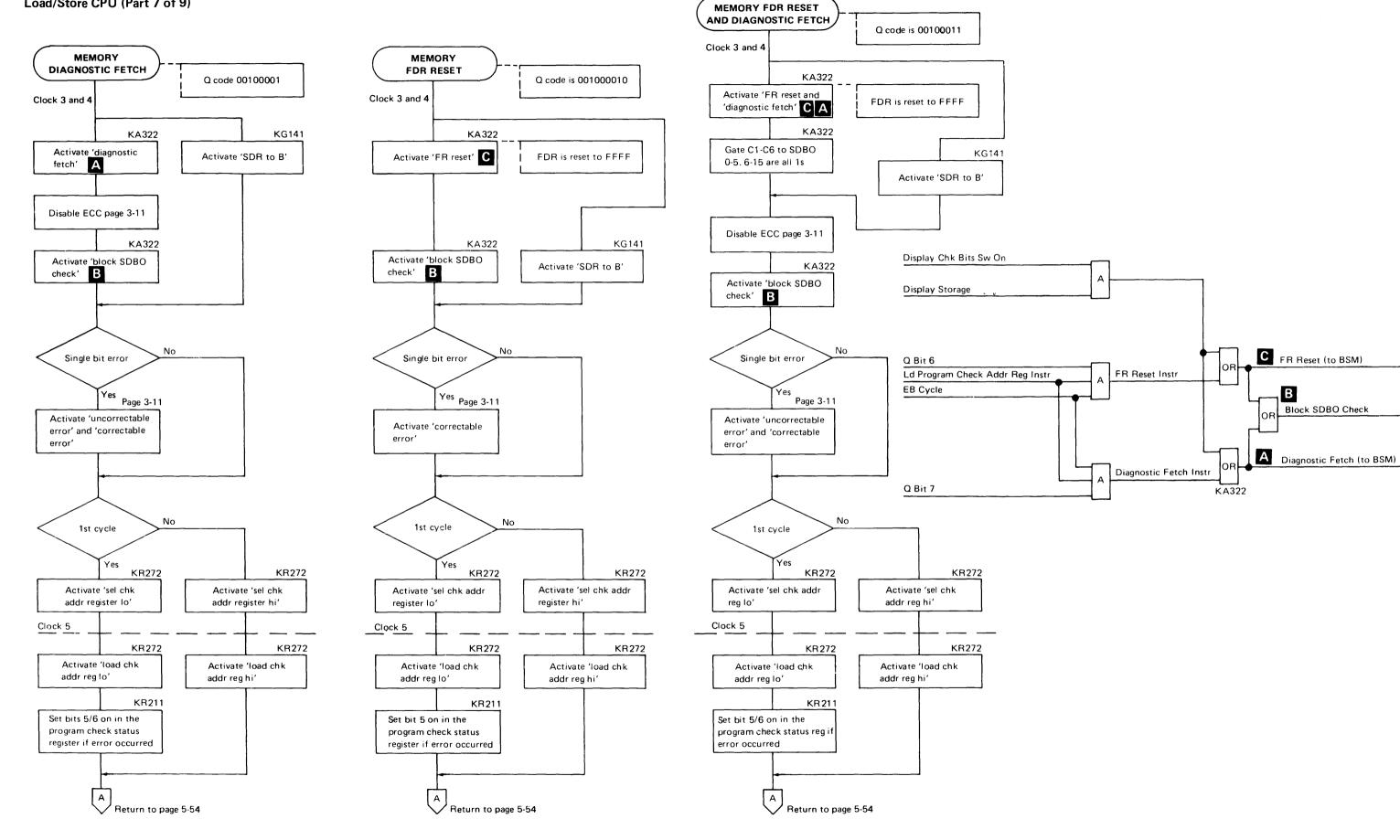

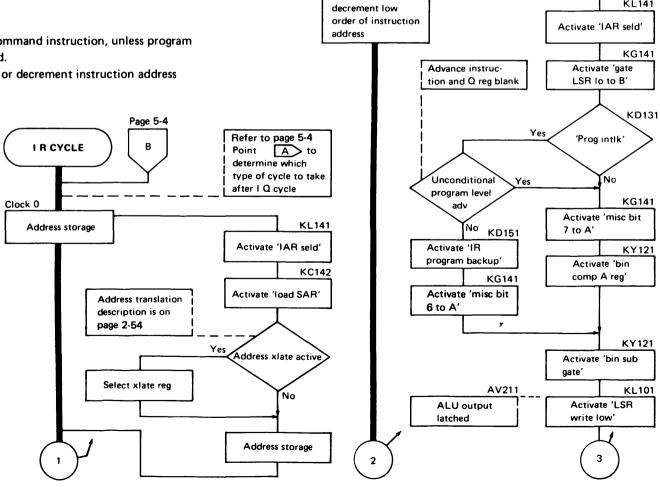

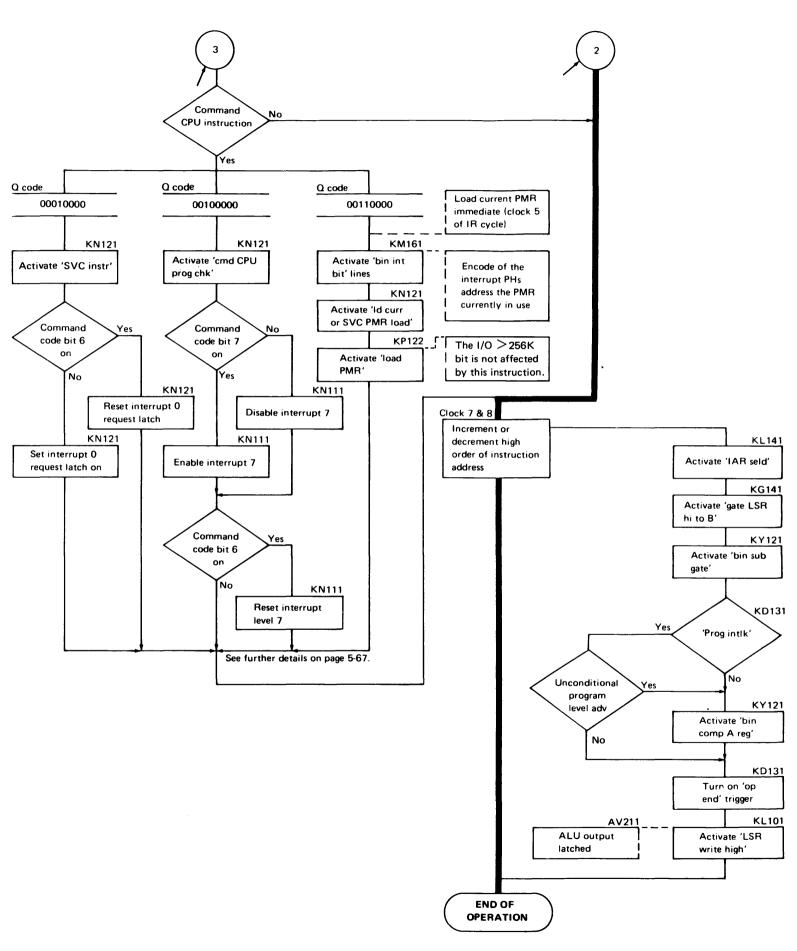

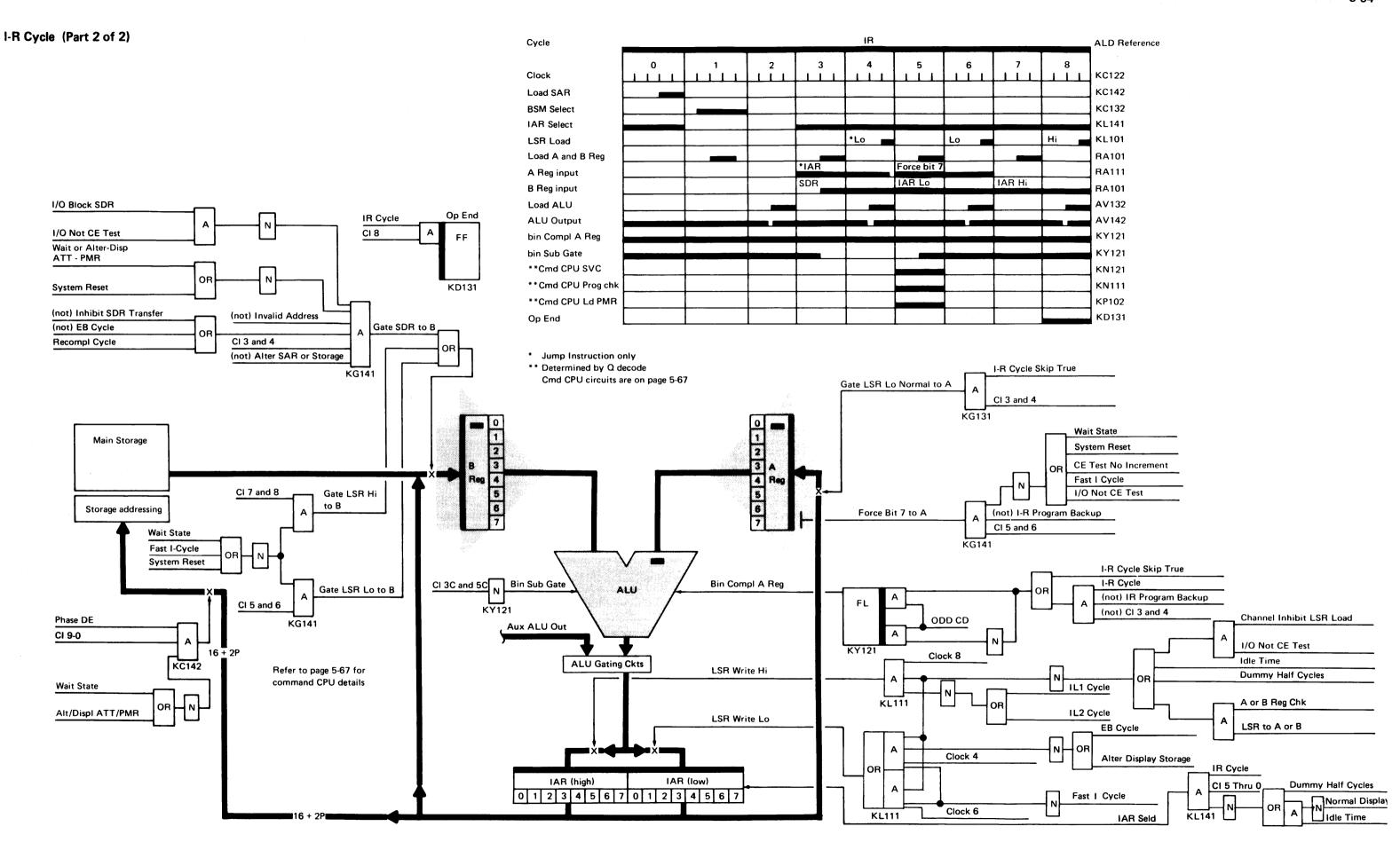

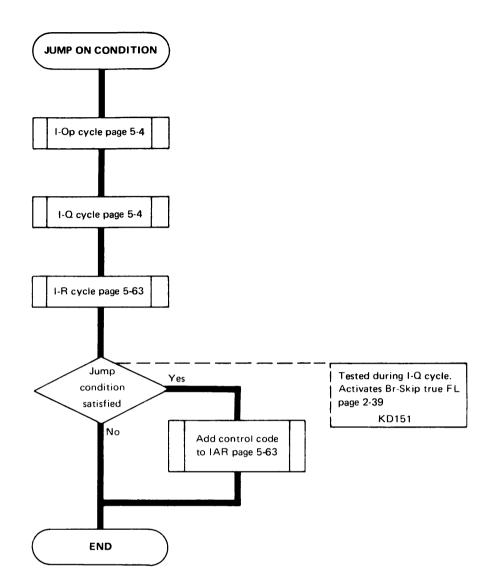

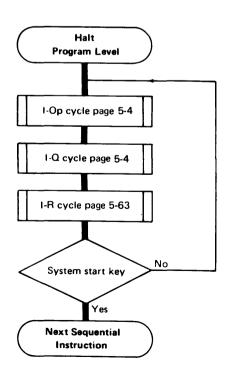

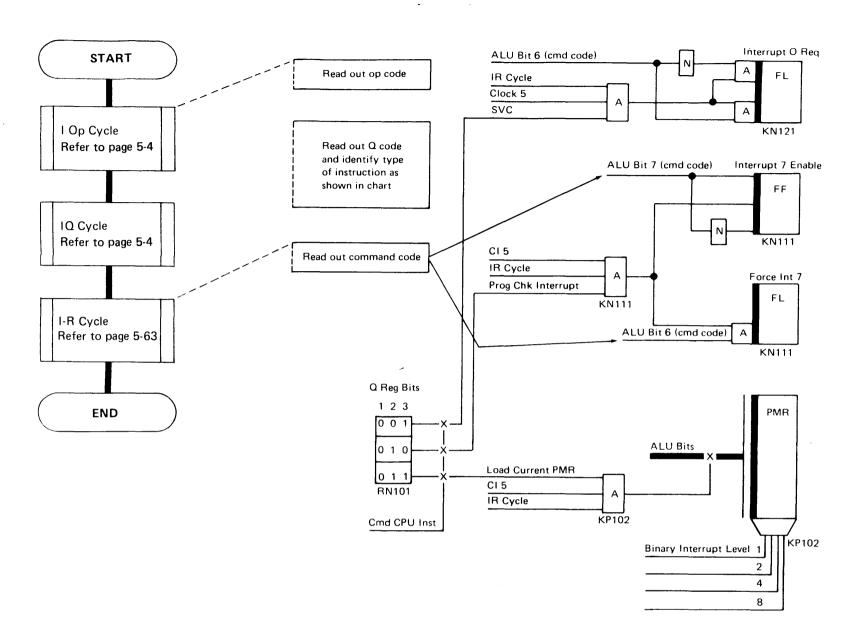

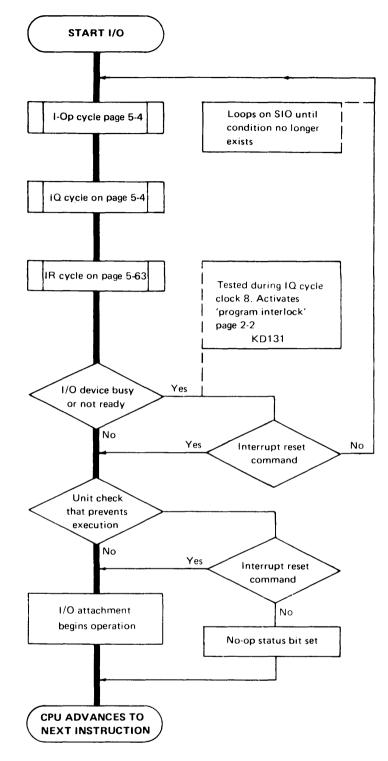

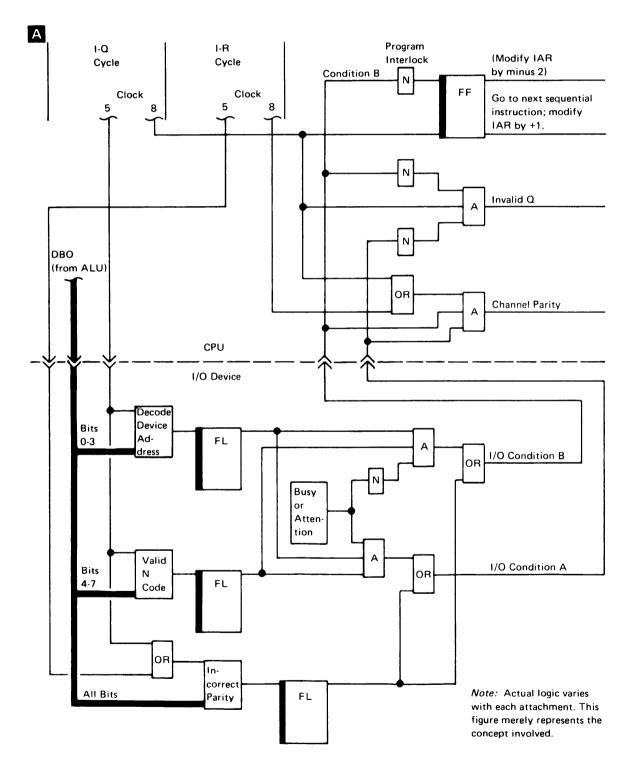

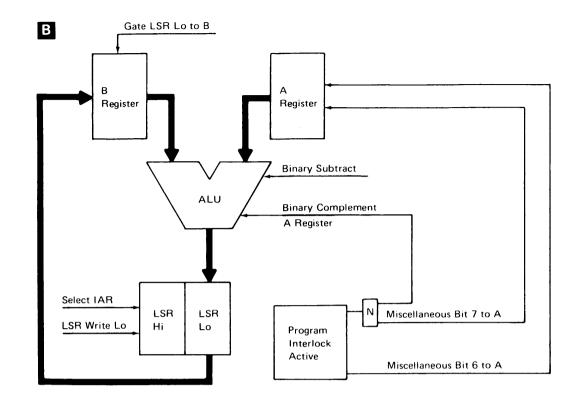

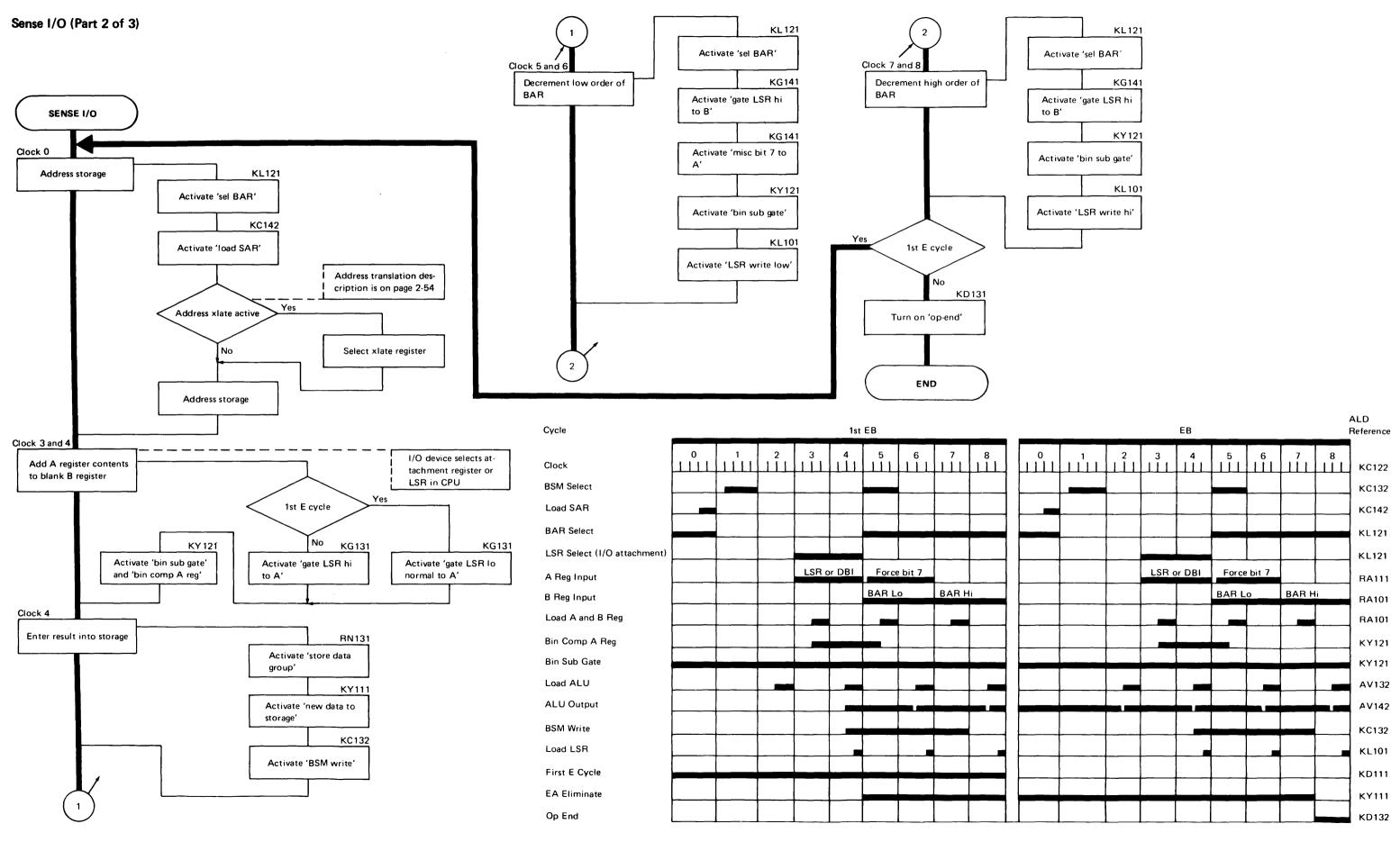

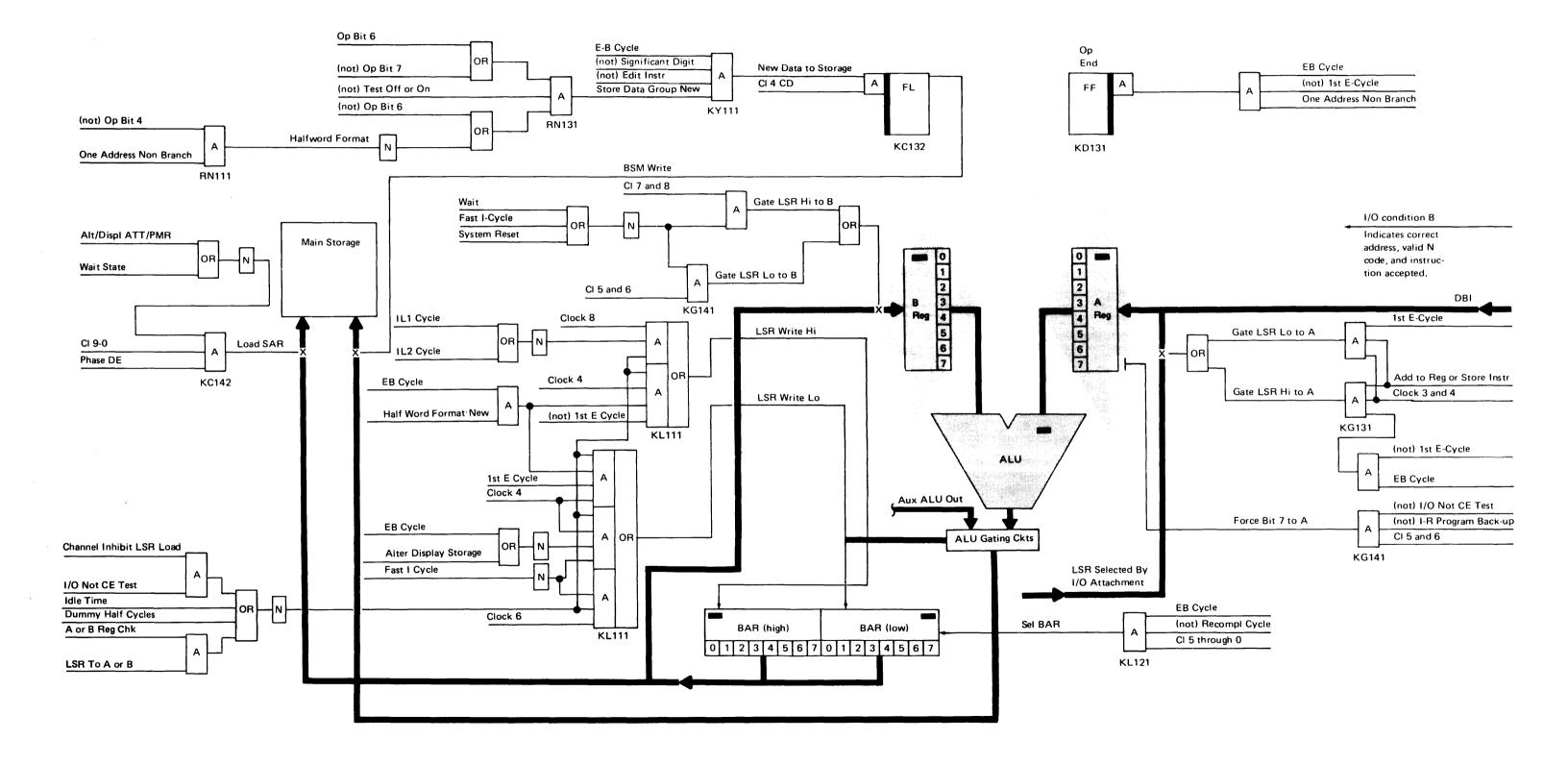

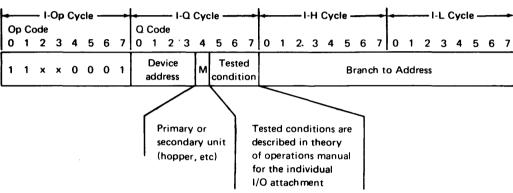

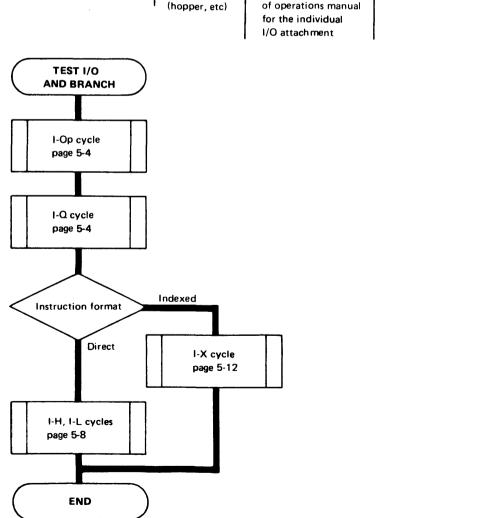

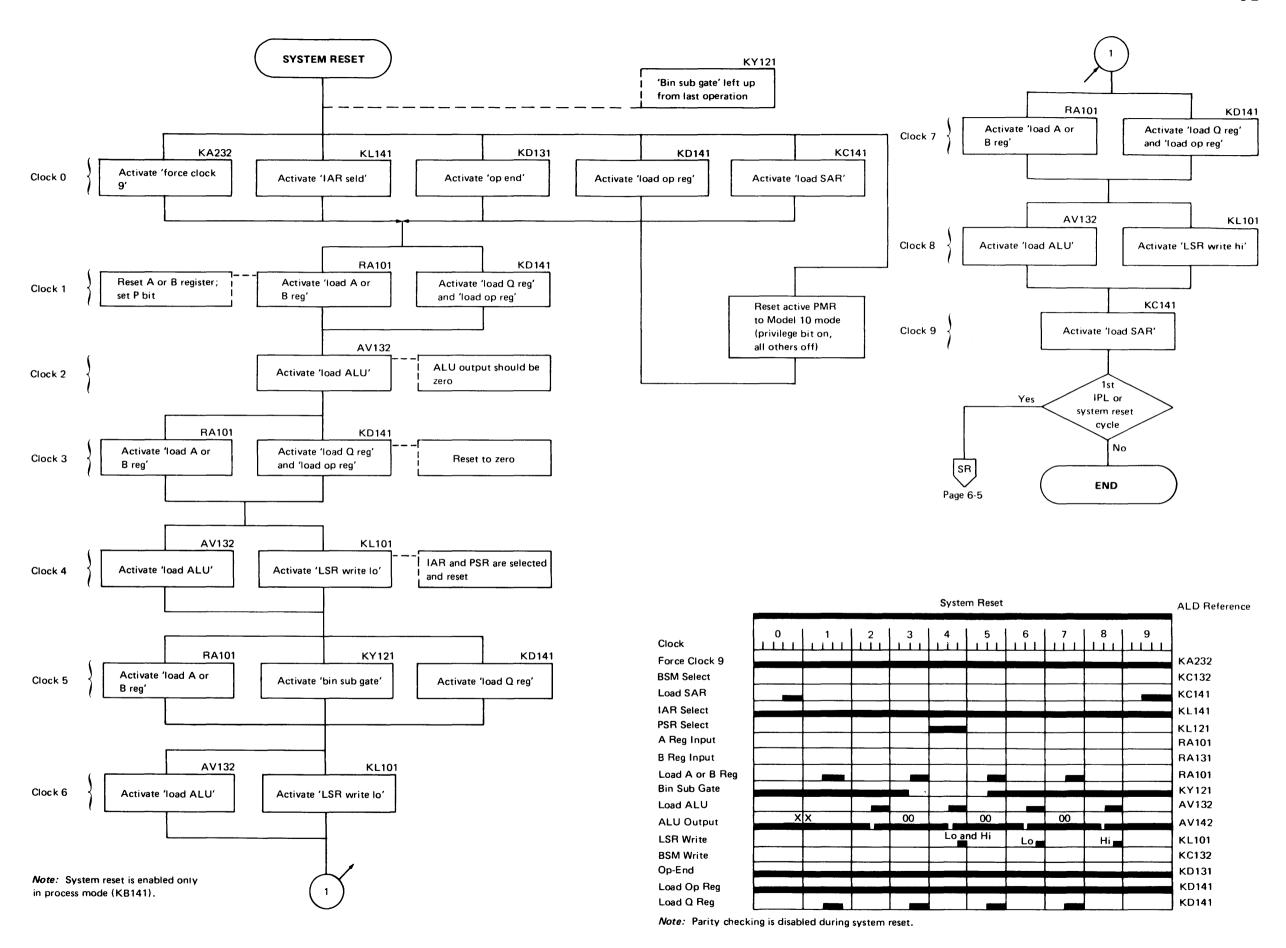

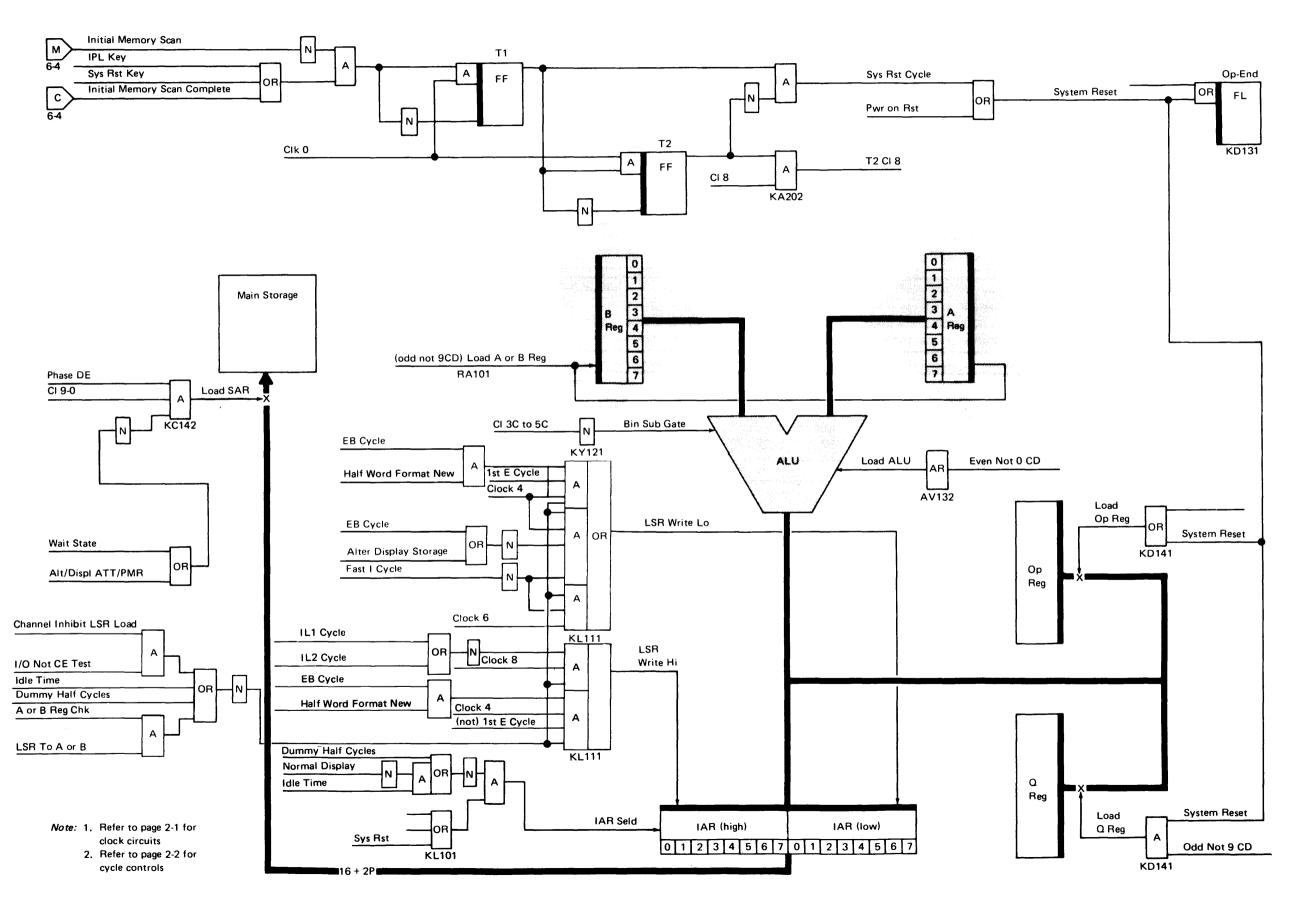

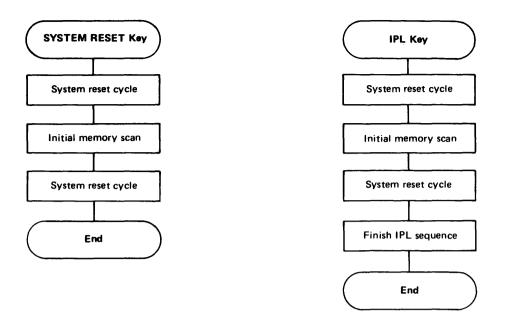

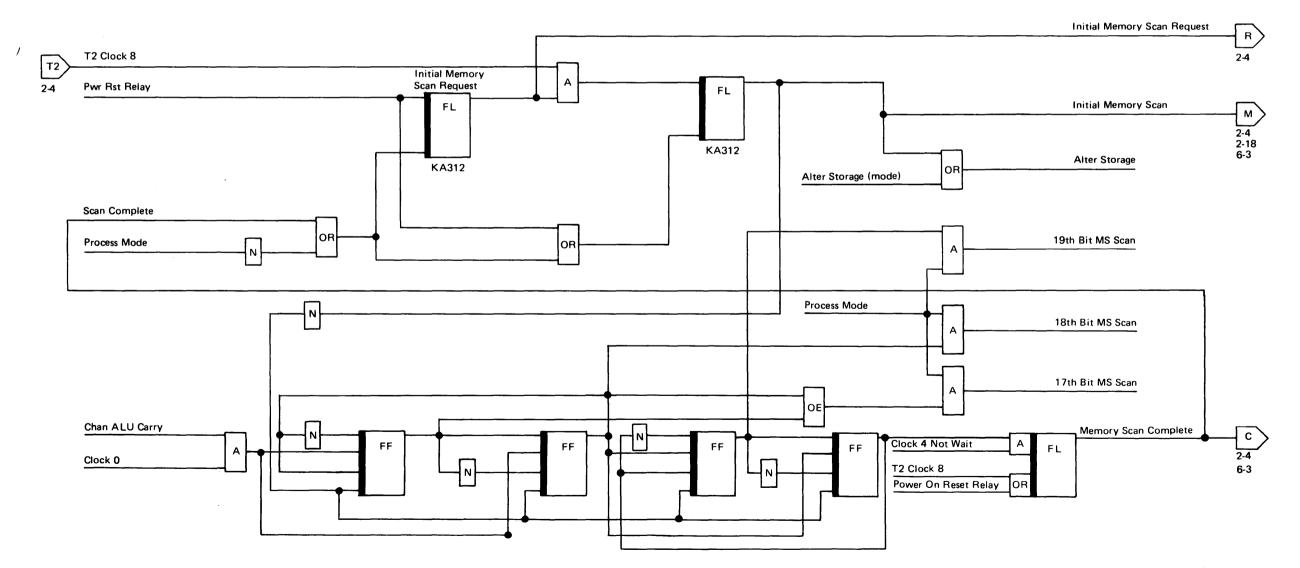

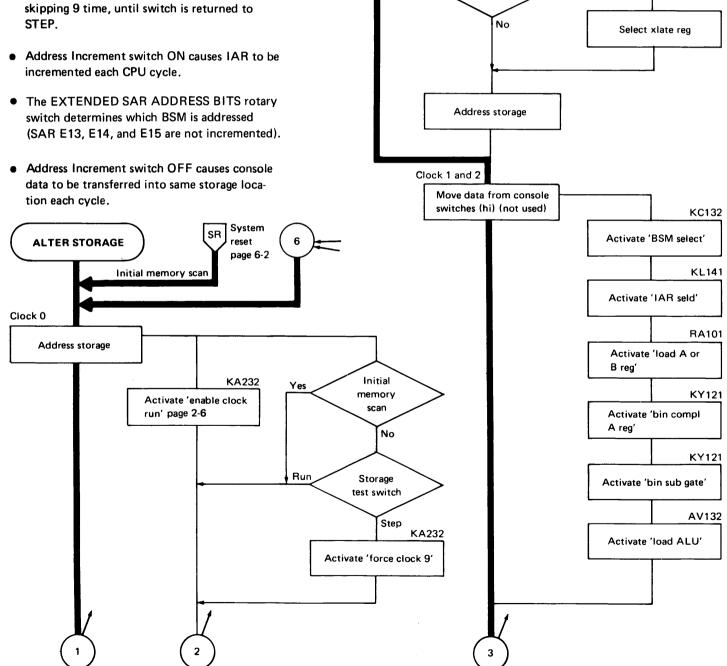

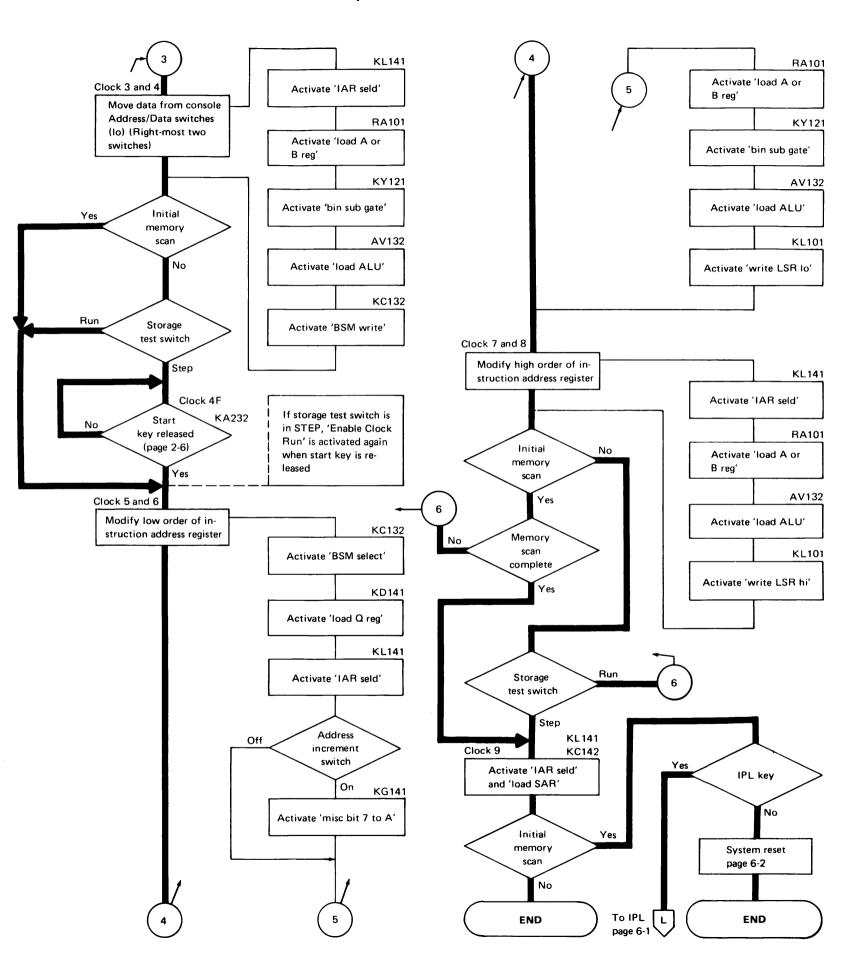

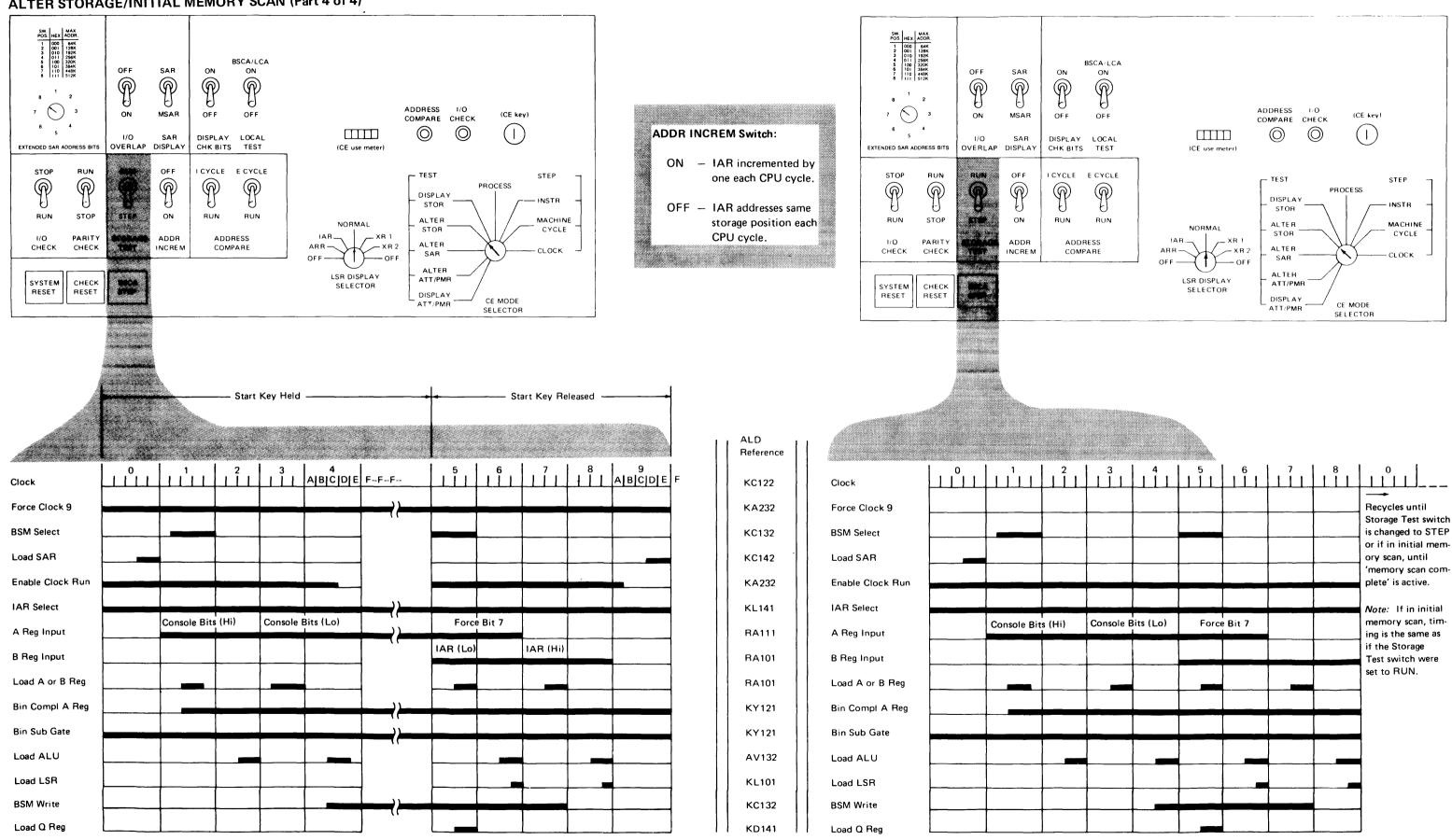

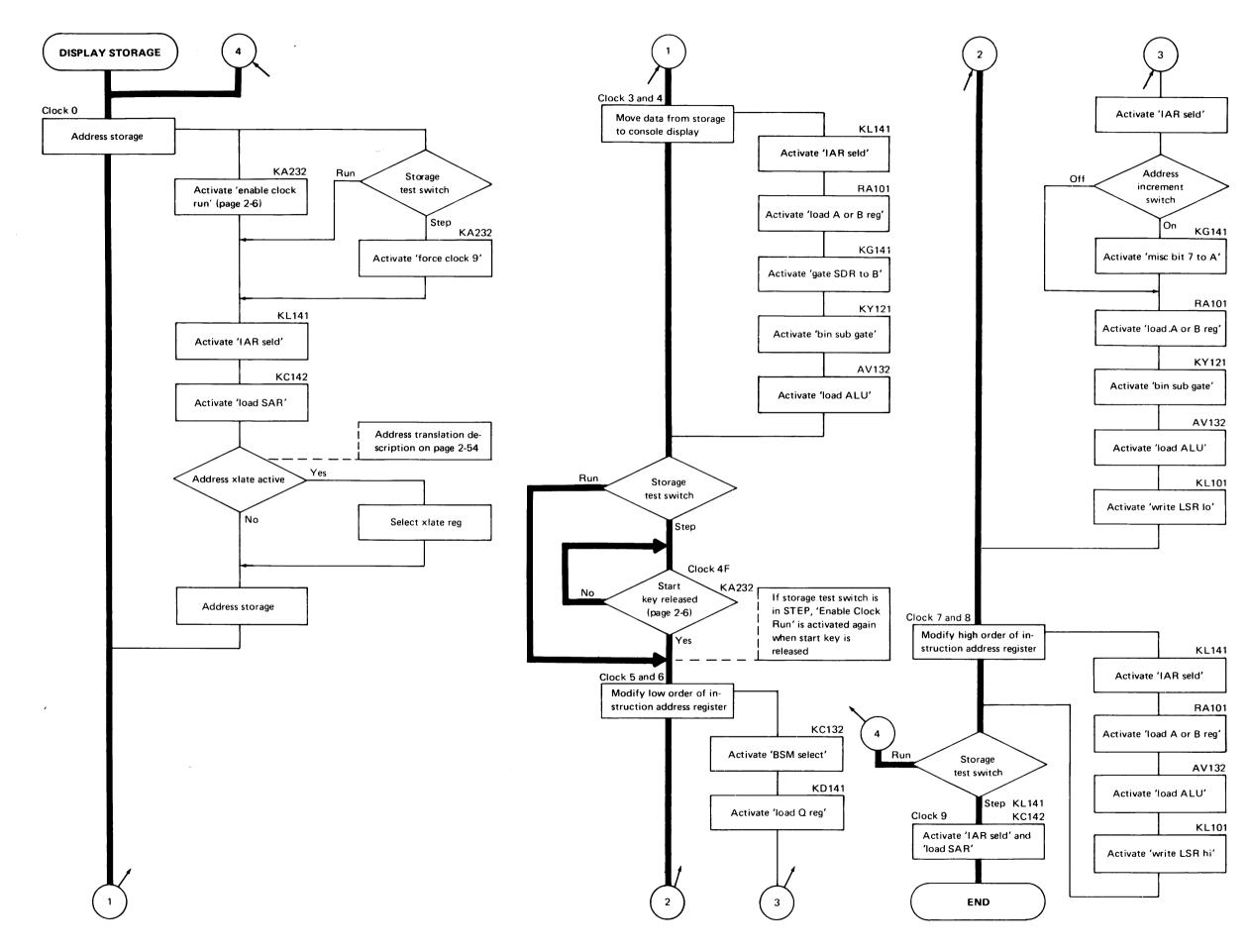

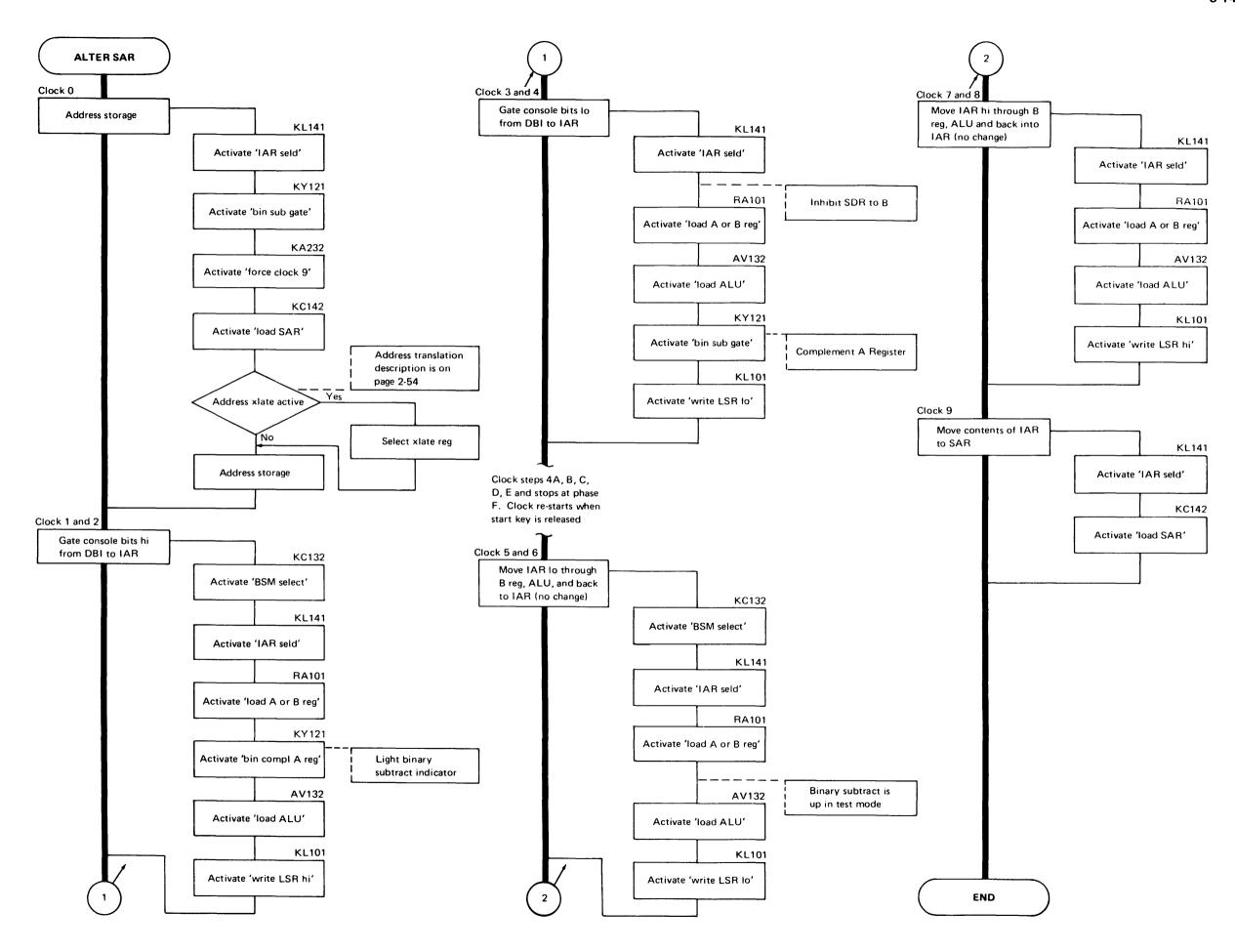

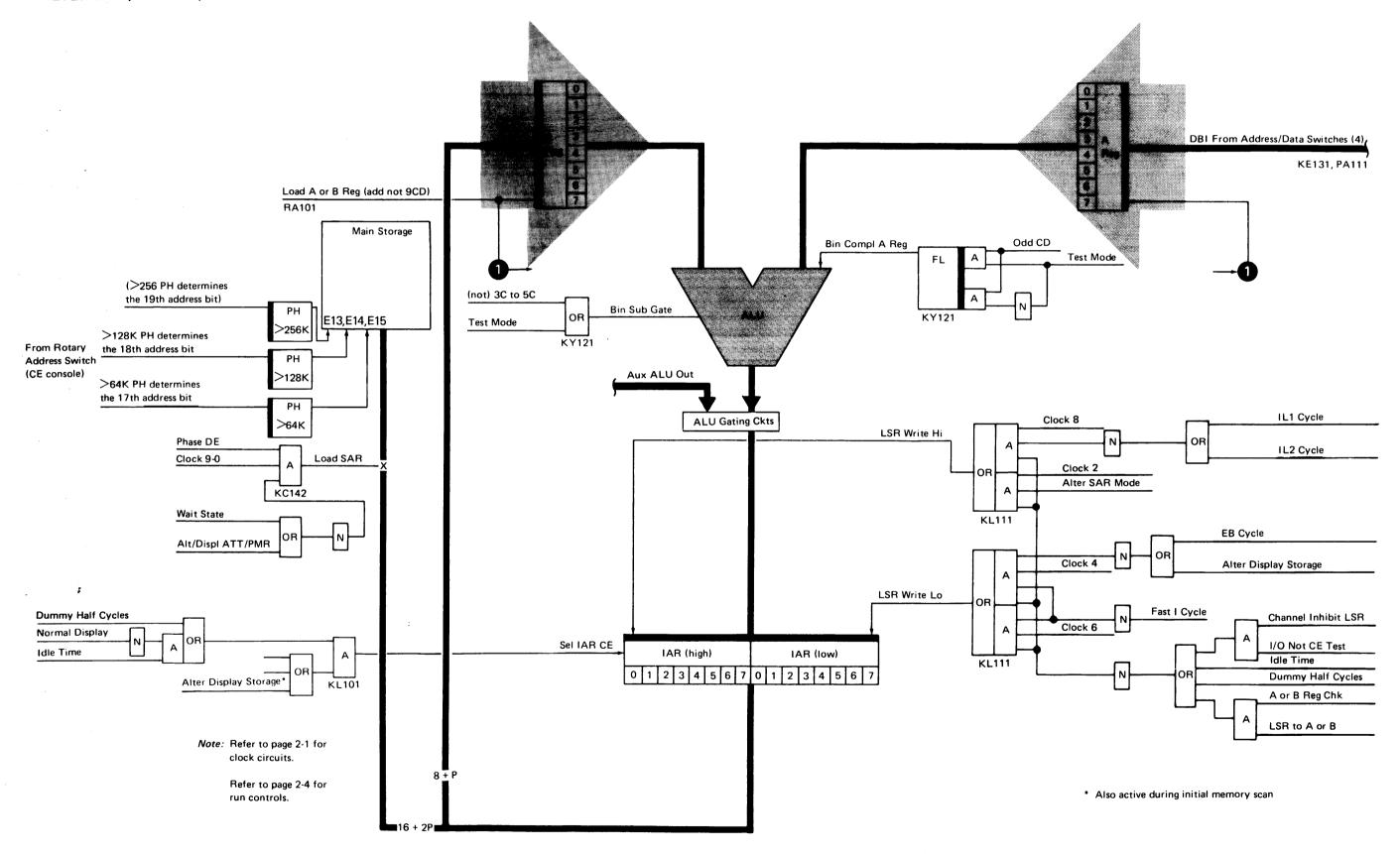

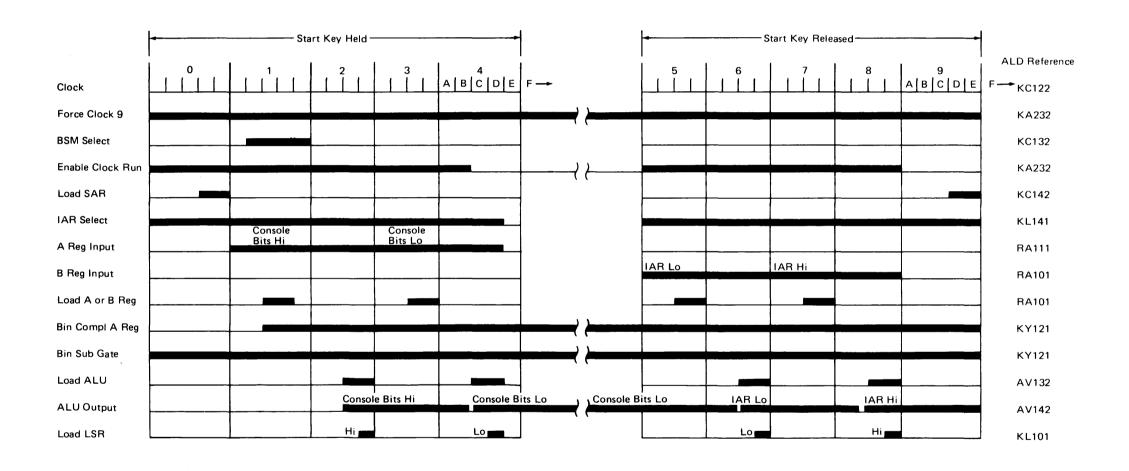

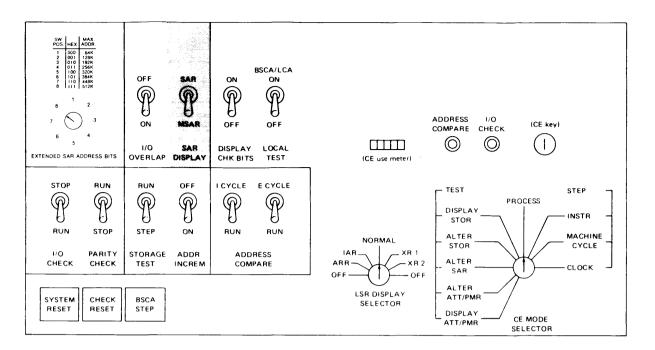

Machine operations are presented in operational flowcharts, most of which are *two-level*. The general flow path indicated by the heavy line of the two-level charts shows the major objectives of an operation or instruction. Detailed flow paths of major objectives are to the right of the general flow path.

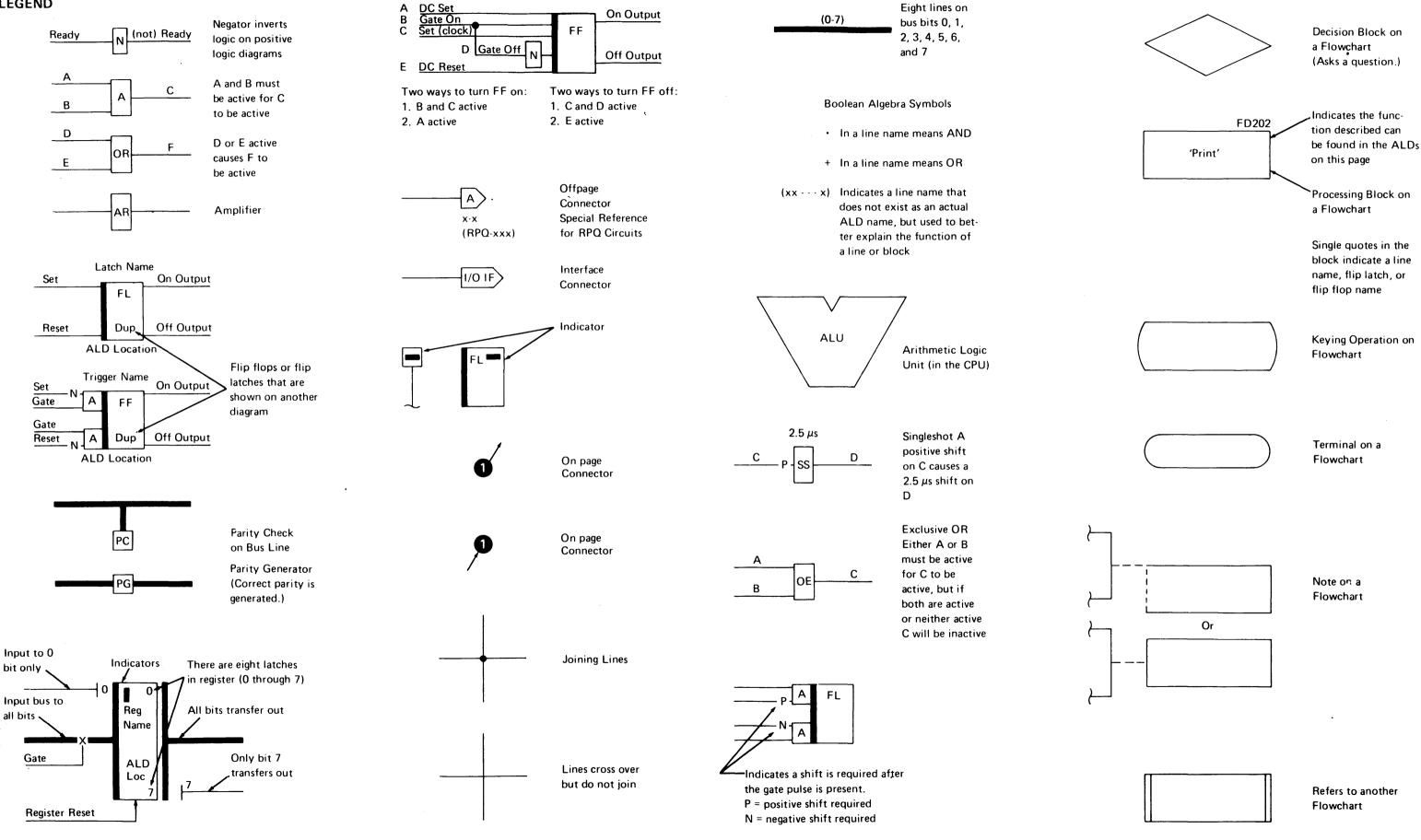

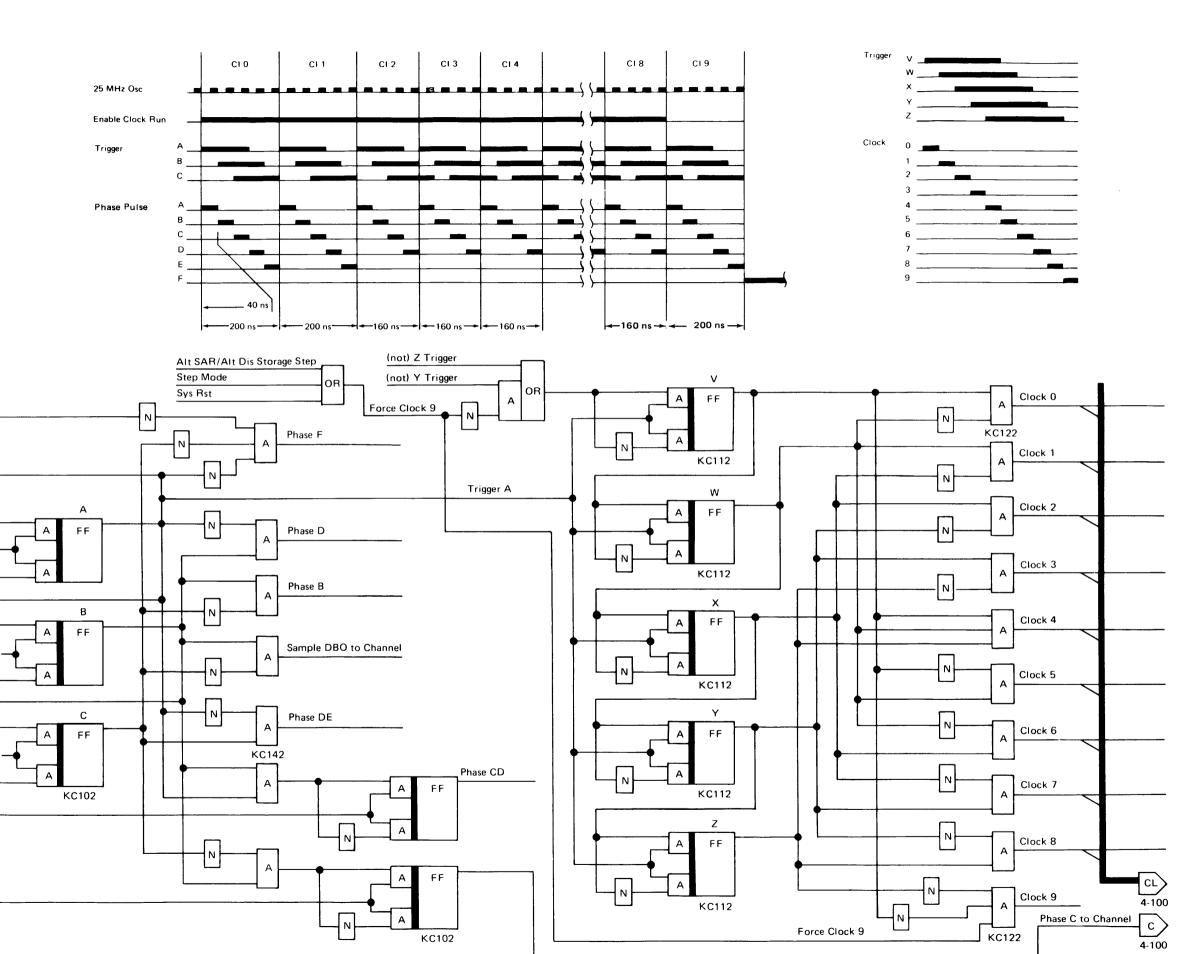

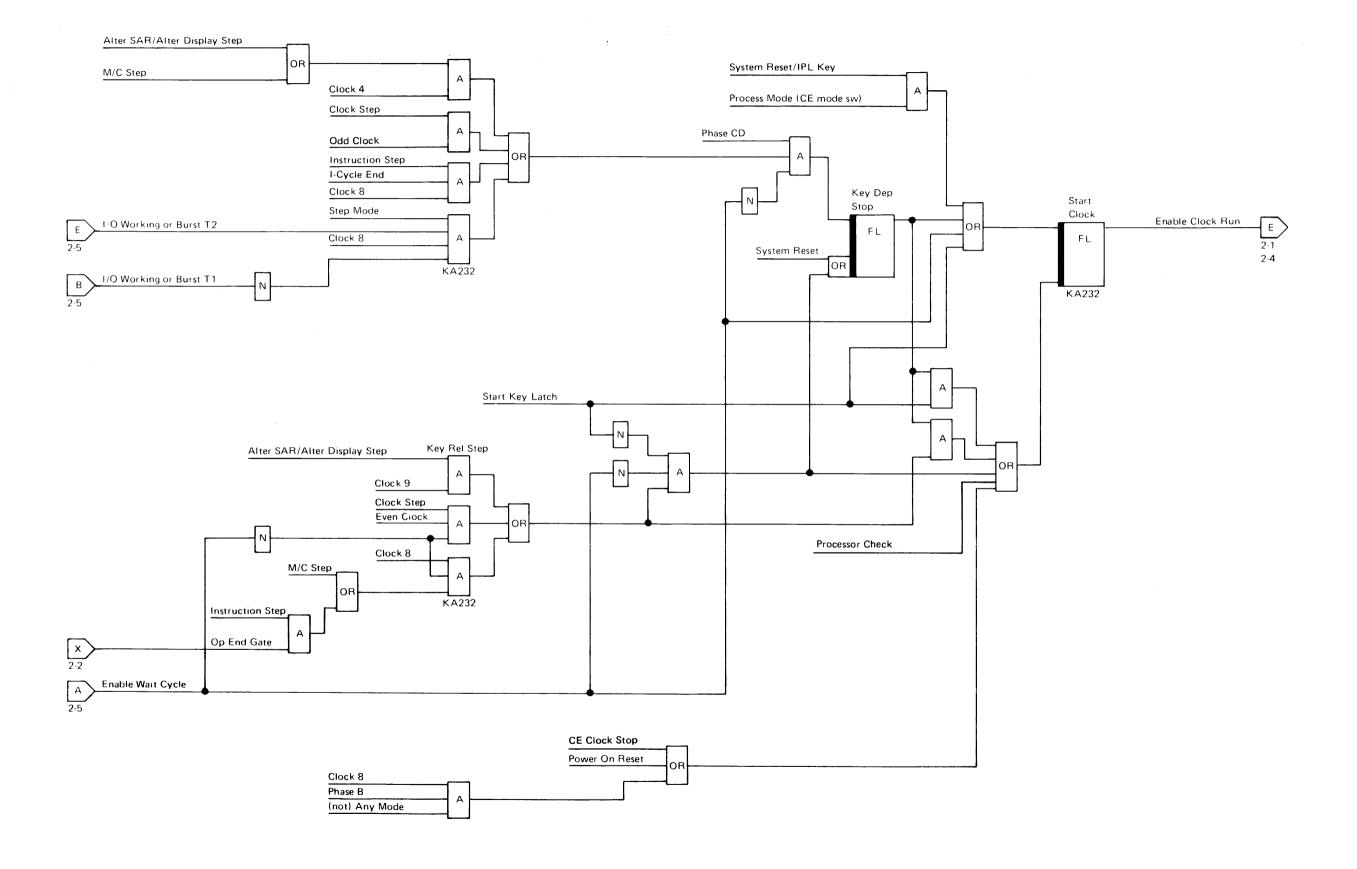

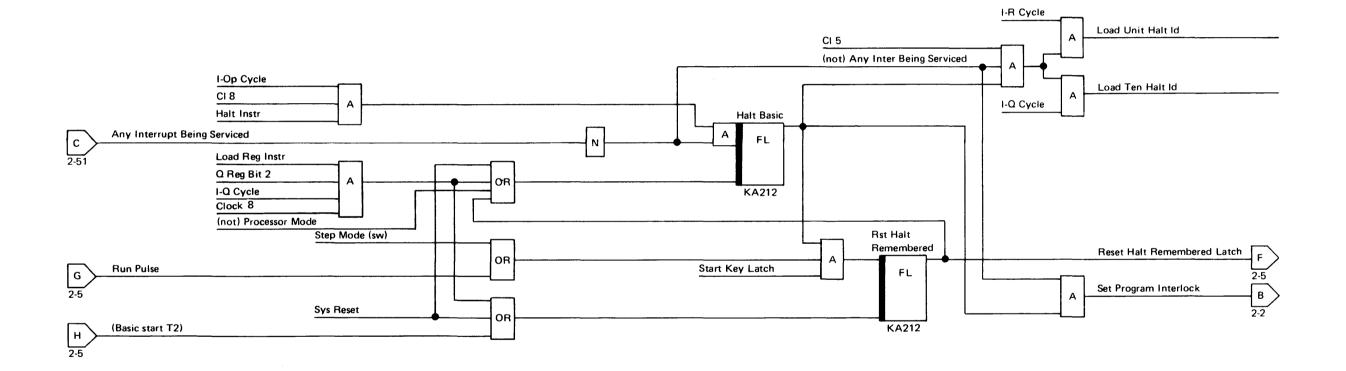

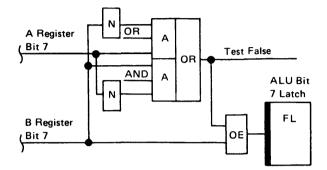

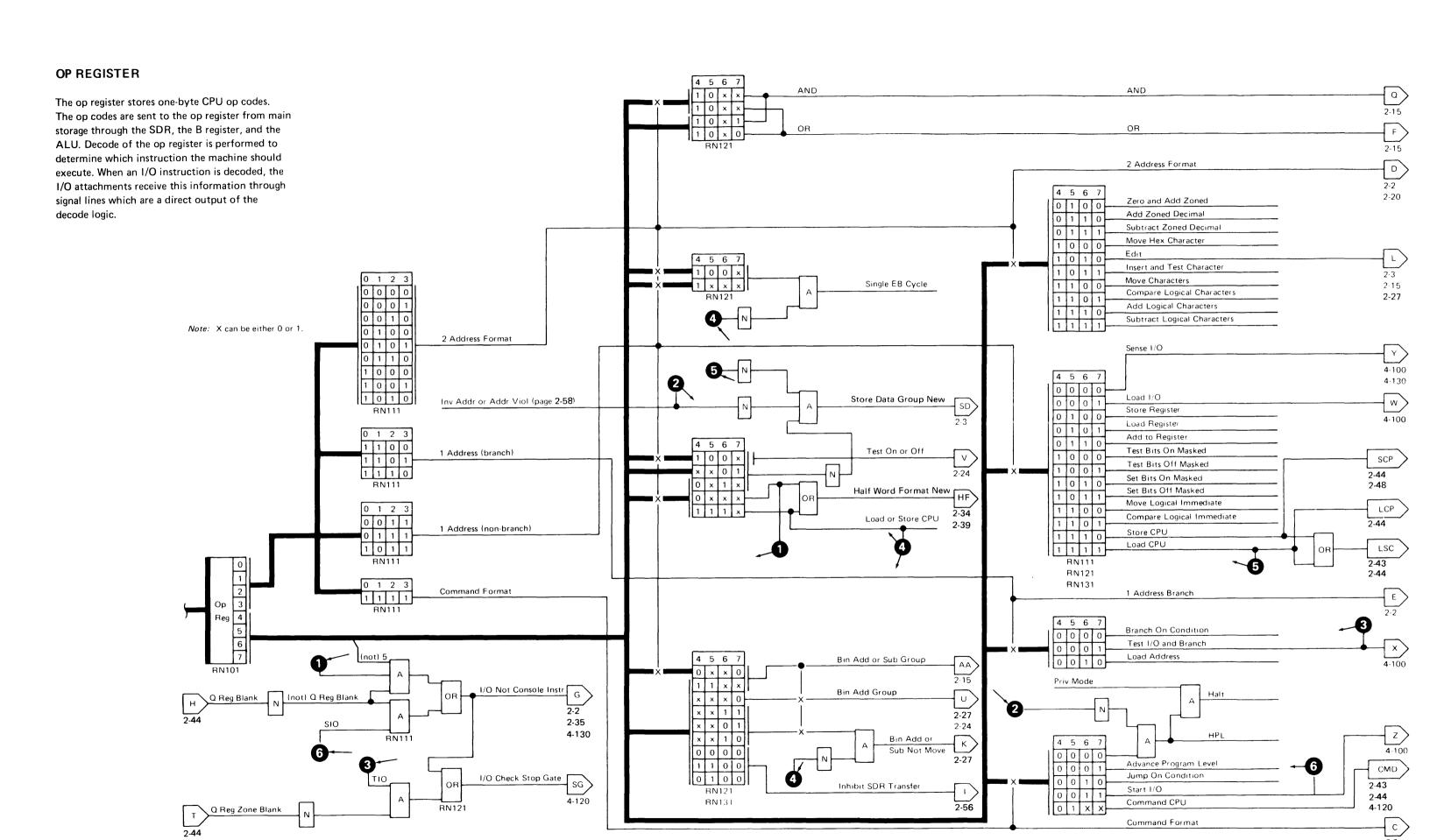

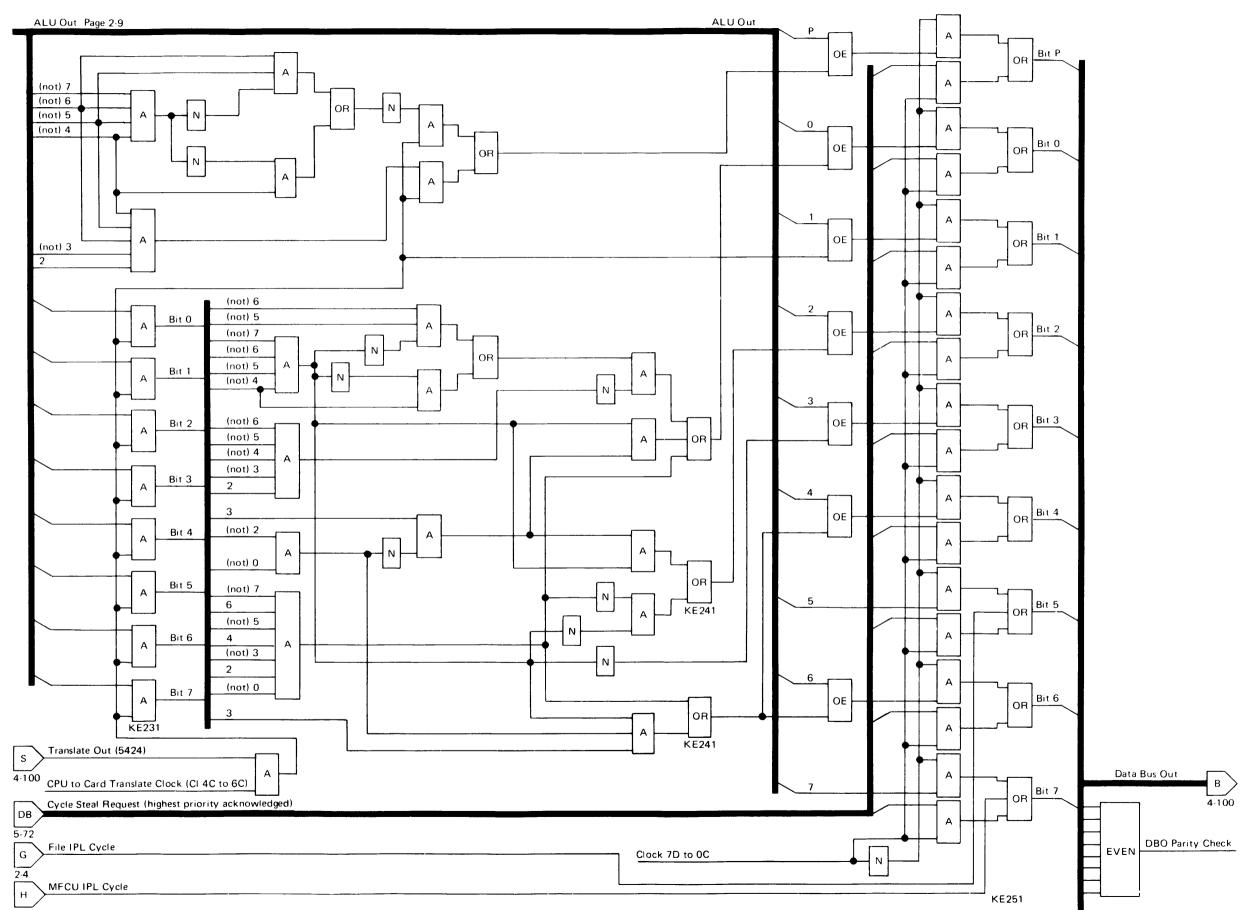

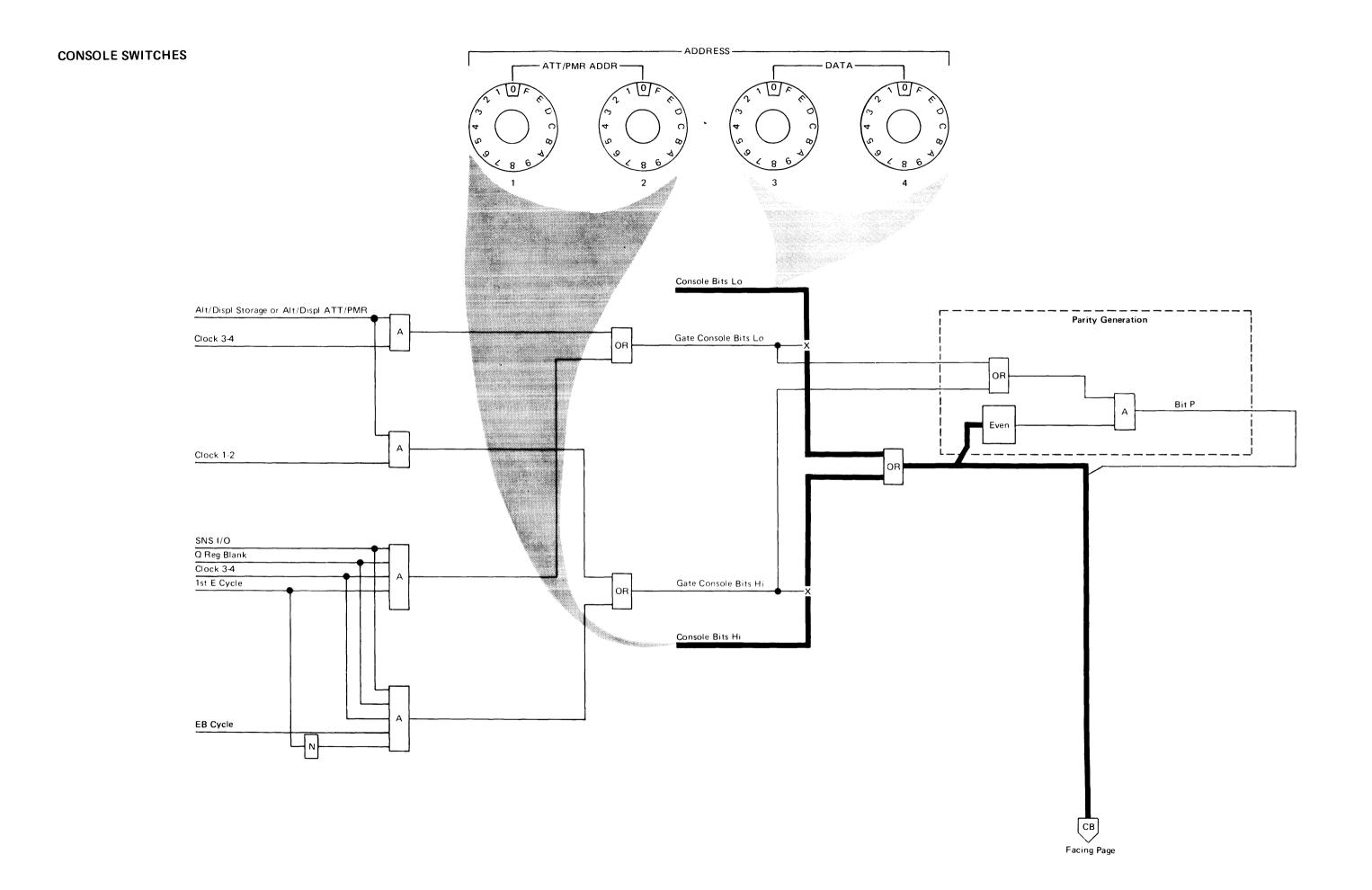

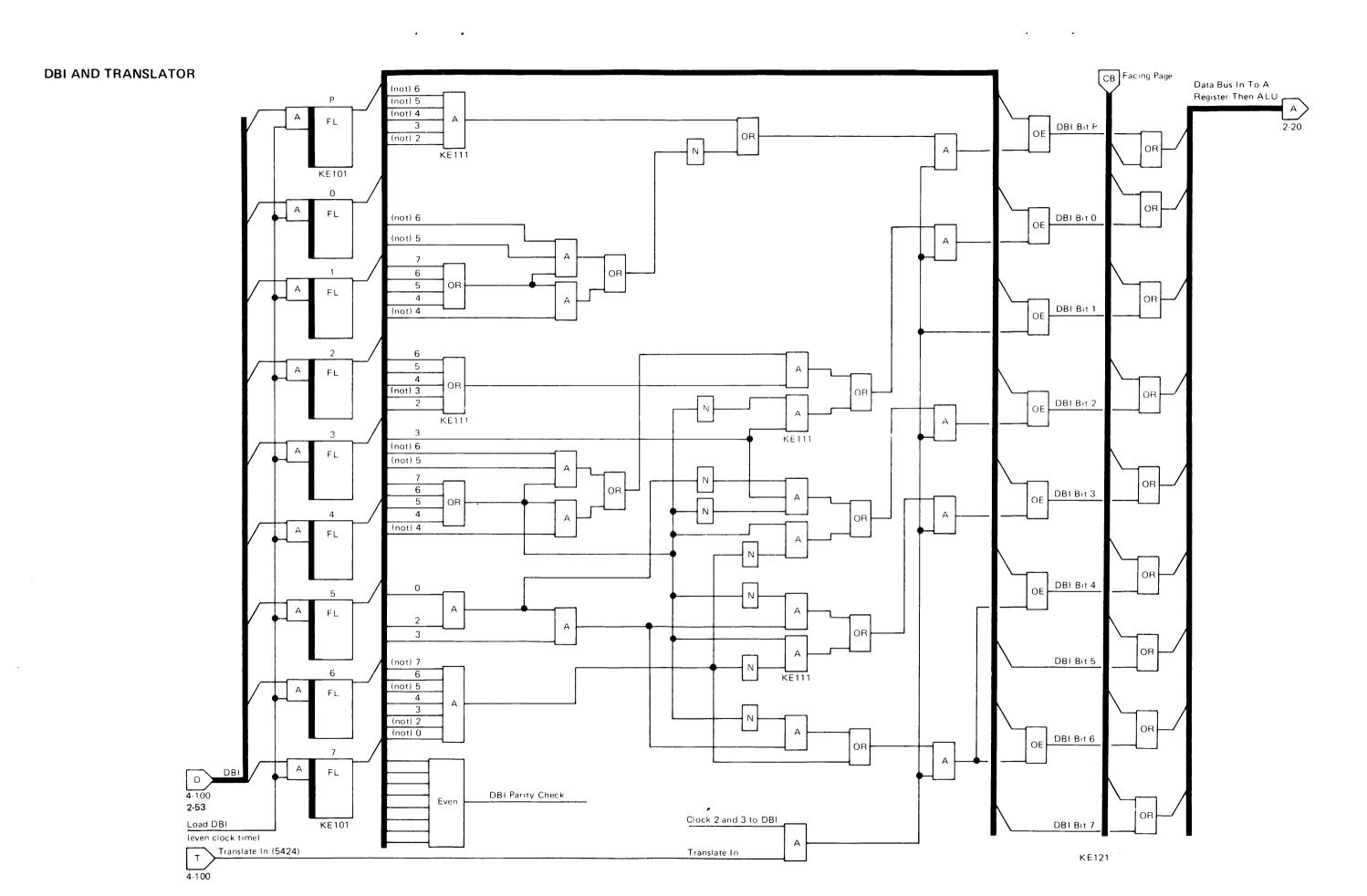

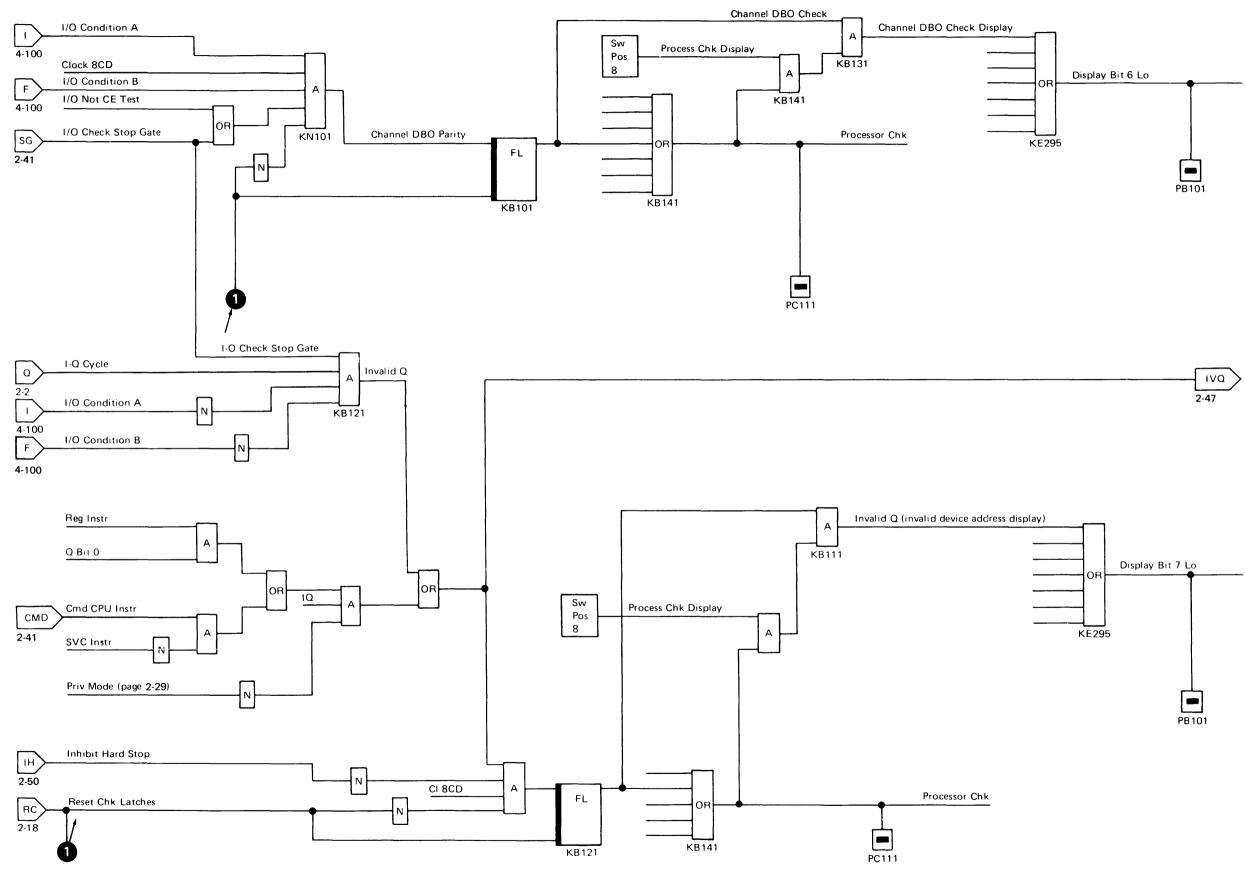

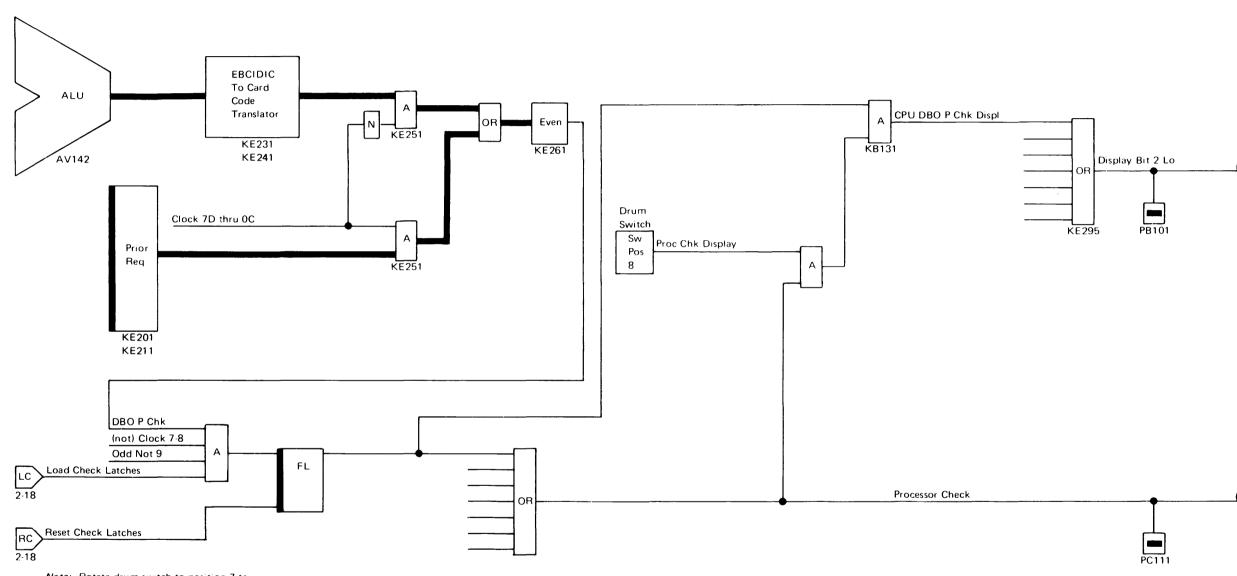

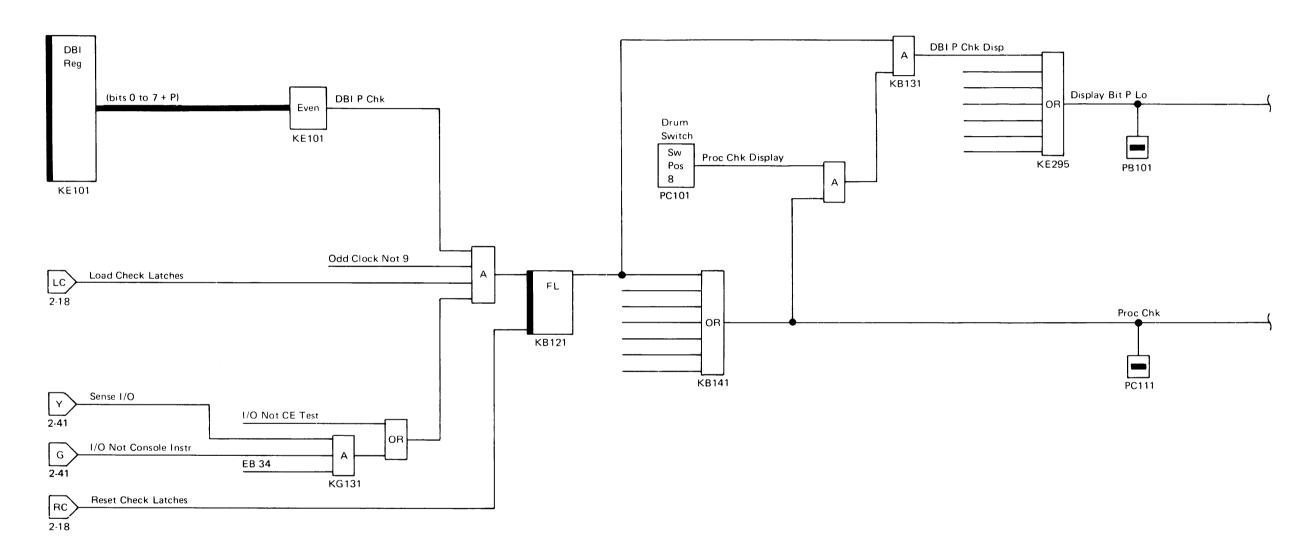

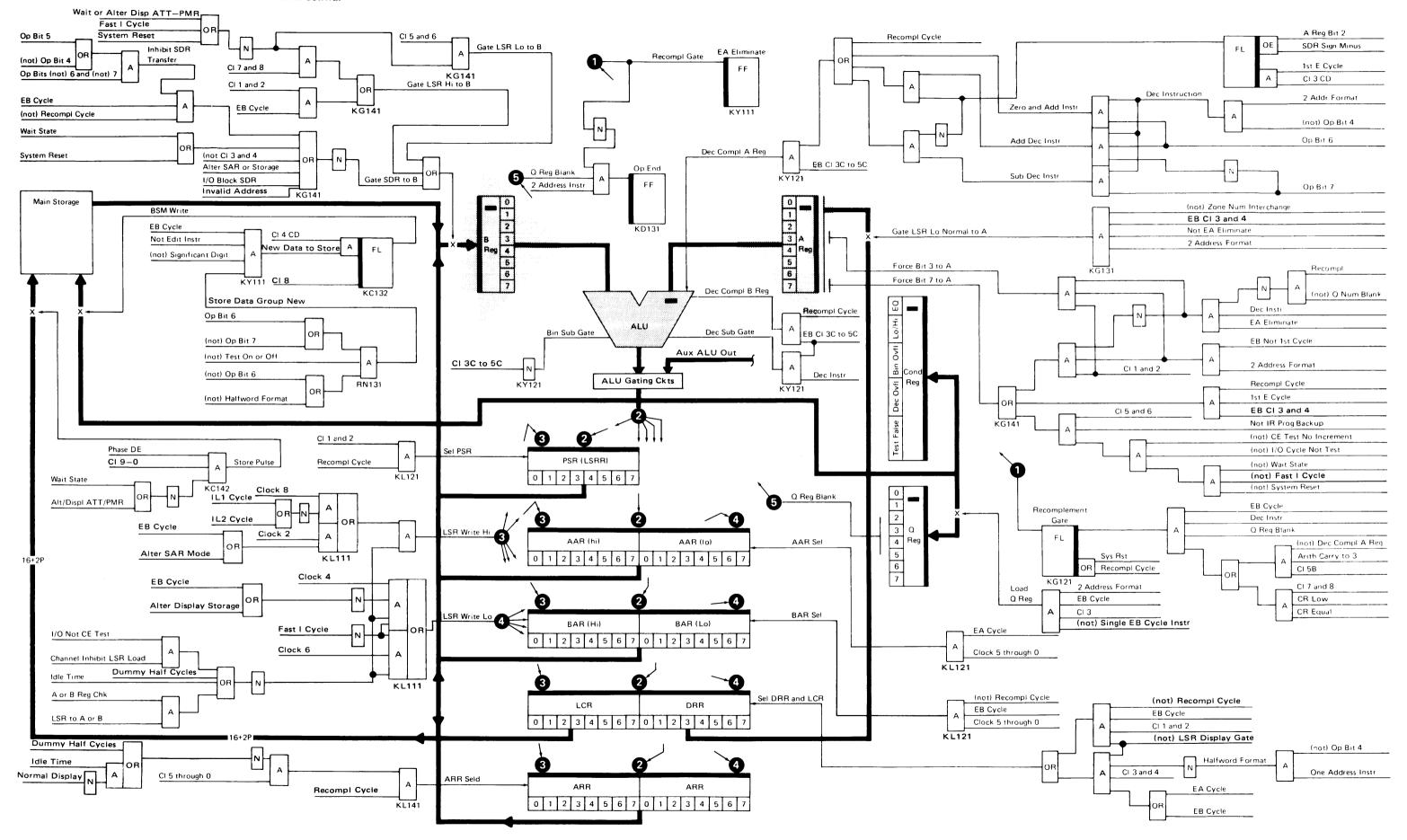

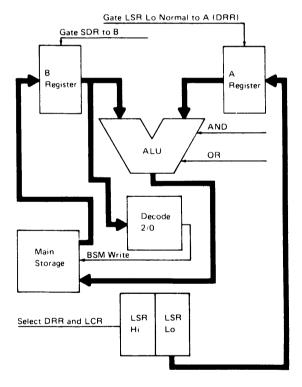

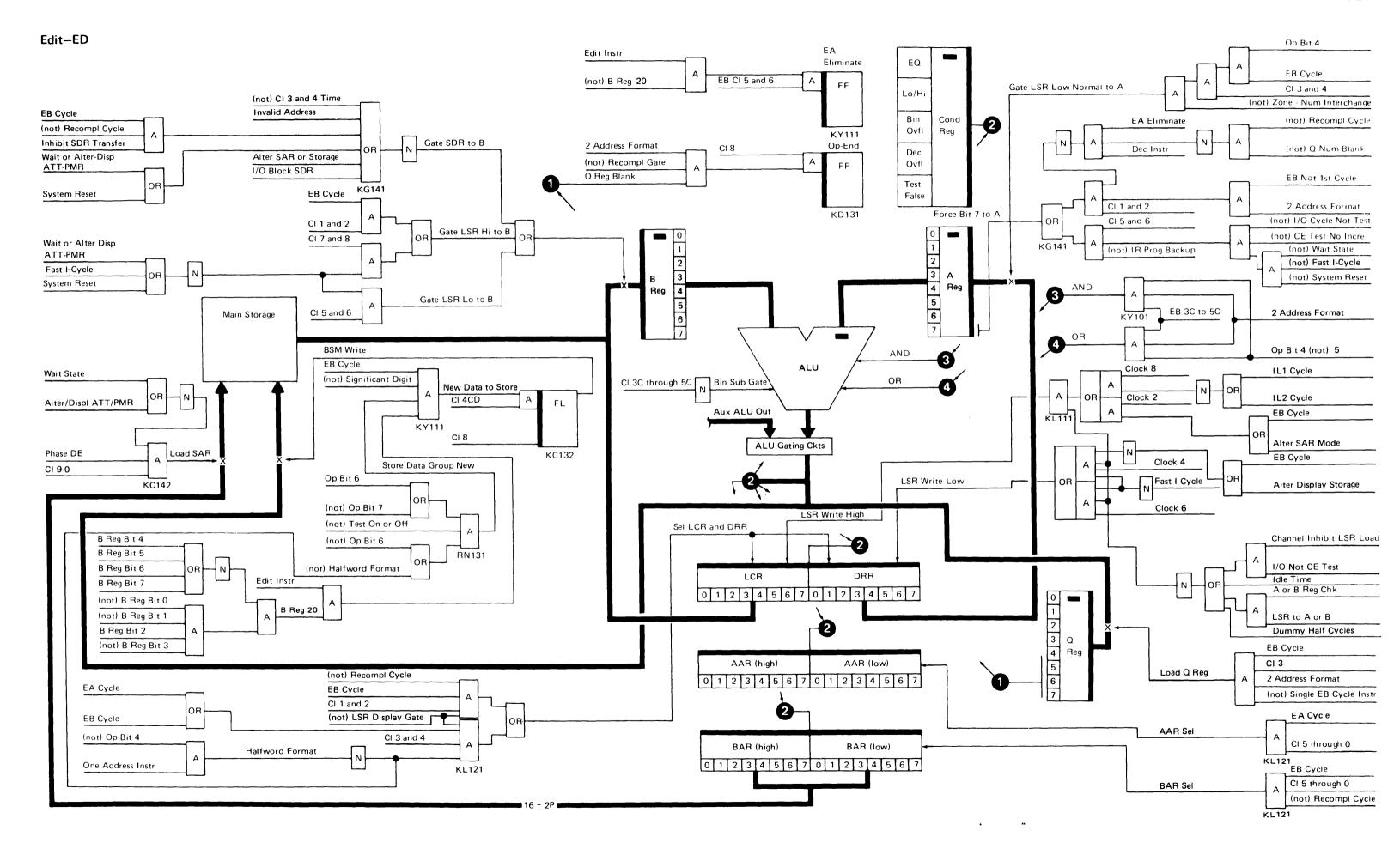

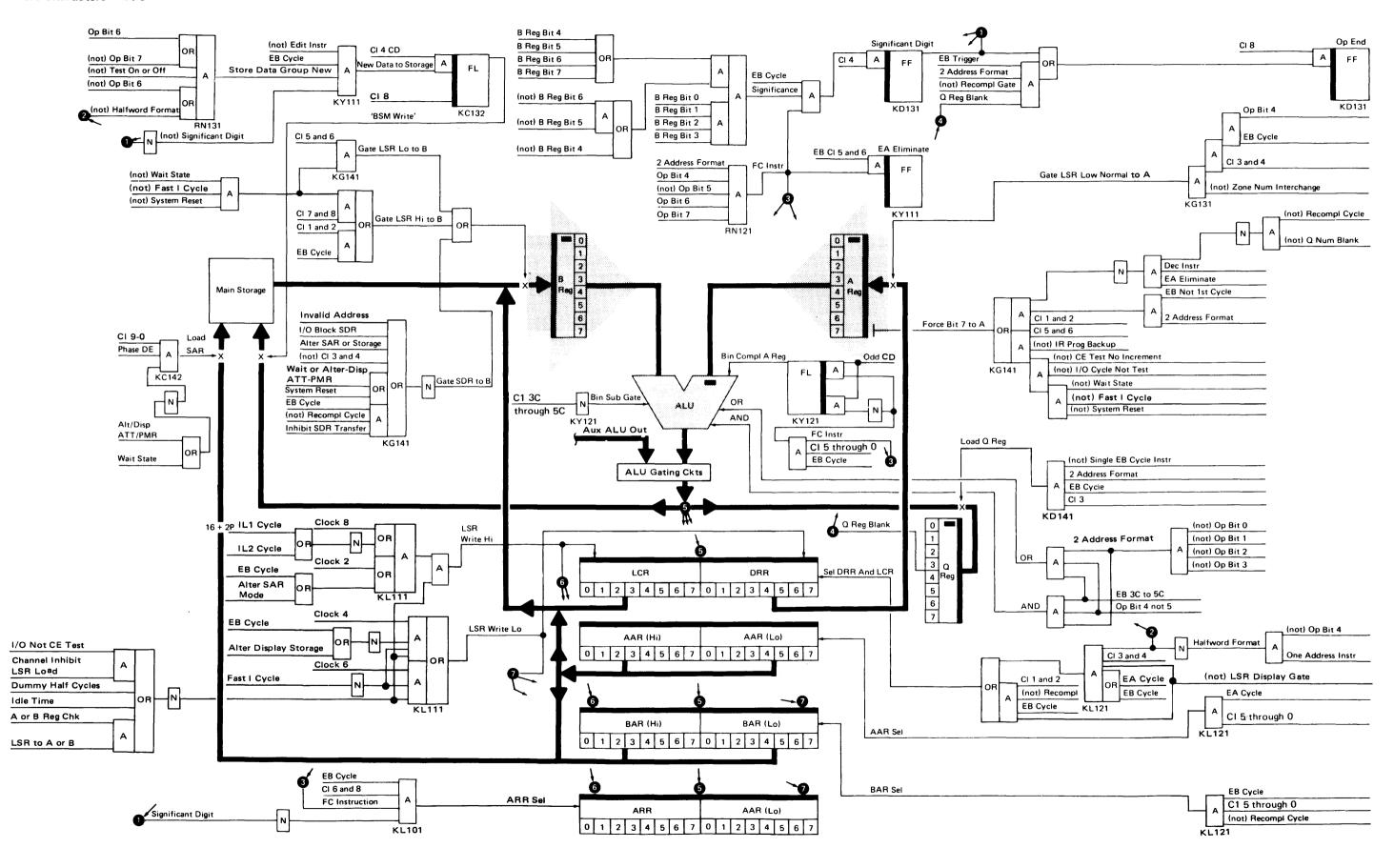

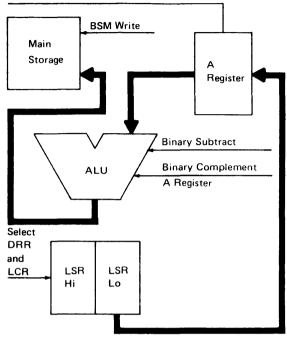

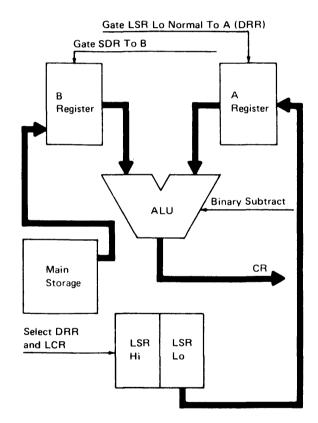

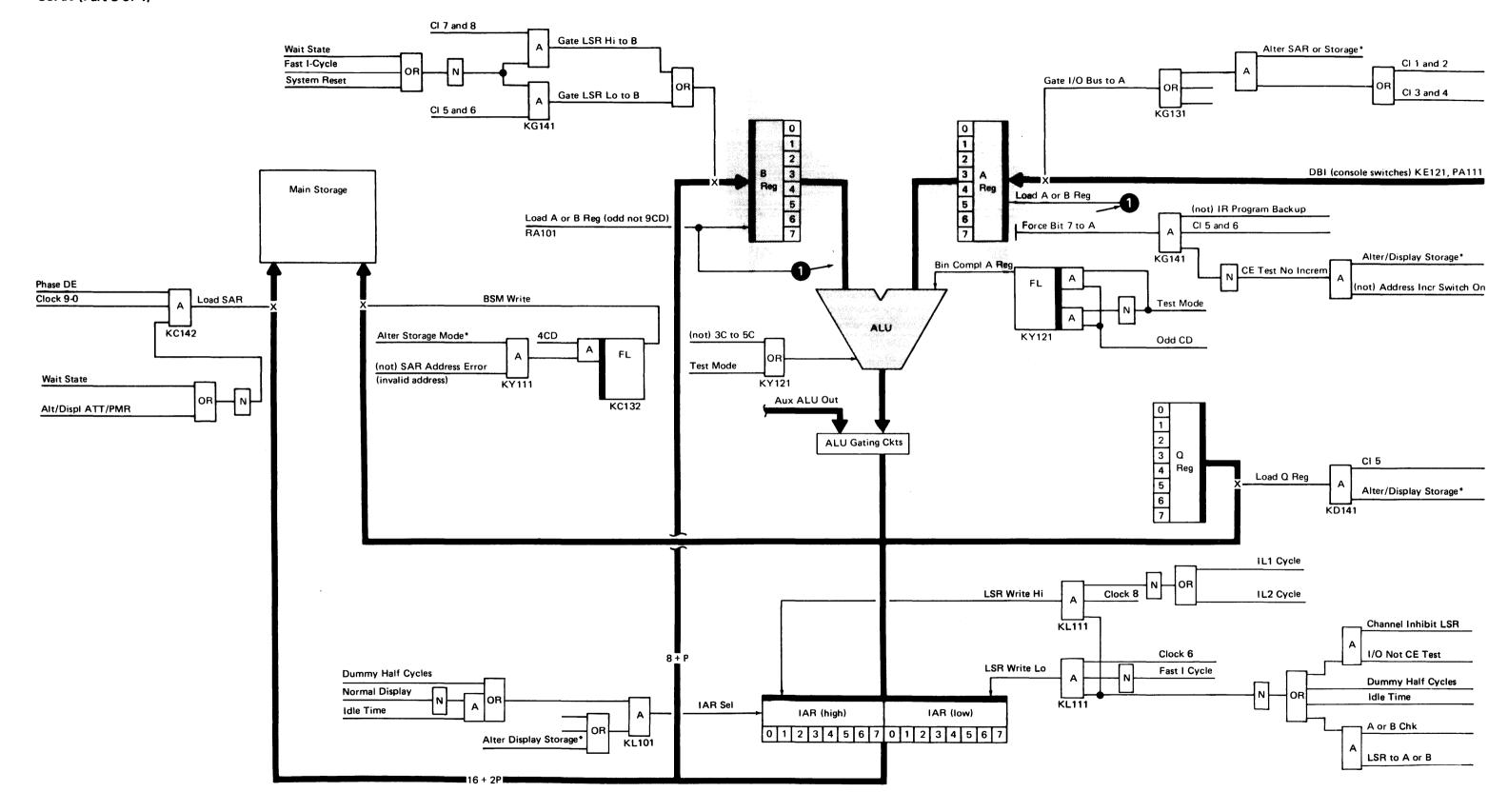

Positive-logic diagrams support the operational flowcharts. They show logical circuit operation without regard to signal levels. Most of the logic diagrams in this manual are not block for block representations of ALDs (automated logic diagrams). Rather, only blocks necessary for a logical understanding of the operation are shown.

For machine characteristics and installation instructions, refer to the *IBM System/3 Installation Manual—Physical Planning*, GA21-9084.

### First Edition (November 1977)

Changes are continually made to the specifications herein; any such change will be reported in subsequent revisions or technical newsletters.

Address comments concerning the contents of this publication to IBM Corporation, Publications, Department 245, Rochester, Minnesota 55901. Comments become the property of IBM.

© Copyright International Business Machines Corporation 1977

### SAFETY

### **Personal Safety**

Read and follow the safety suggestions in the *CE* Safety Practices Manual, S229-1264, a pocket-sized card issued to all IBM customer engineers.

### Remember:

- Loose clothing can become entangled in moving parts of the machine.

- Drive belts, because of their internal cable construction, can cause serious injury. DO NOT crank a machine by pulling on the drive belts.

- Heat sinks are at an electrical potential. DO NOT short heat sinks to each other or to the machine side frame.

- Always unplug machine power and wait ONE FULL MINUTE before attempting repairs or adjustments in the power supply area.

- Voltages developed in the resonant circuit of regulating power supplies are apt to be much greater than the line voltages.

- Follow the specific safety precautions that accompany many of the adjustment procedures in this manual.

Be aware that an I/O device motor and/or clutches can operate unexpectedly. Conditions that could cause this are:

- Program commands.

- Loss of dc voltage to a machine, gate, board or chassis, card, or pin.

- Removing or inserting a card or cable.

- Probing and accidentally shorting a pin.

### **Equipment Safety**

### **Electrical**

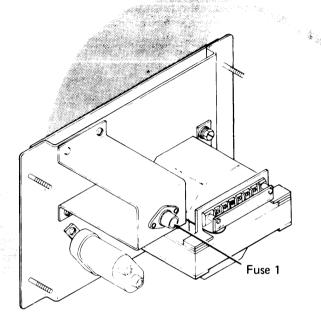

Always replace blown fuses with fuses of the same type and rating. Using fuses of a different type or higher rating could result in component damage.

Remove power from the machine before replacing logic cards, magnets, or solenoids. Failure to do this could result in damage to the card being replaced or to other cards in the net.

#### Mechanical

Do not operate the machine under power with units disassembled, removed, or maladjusted. Keep tools clear of the mechanism when the machine is operating under power.

**CAUTION:** Do not use IBM cleaning fluid on plastic parts.

iii

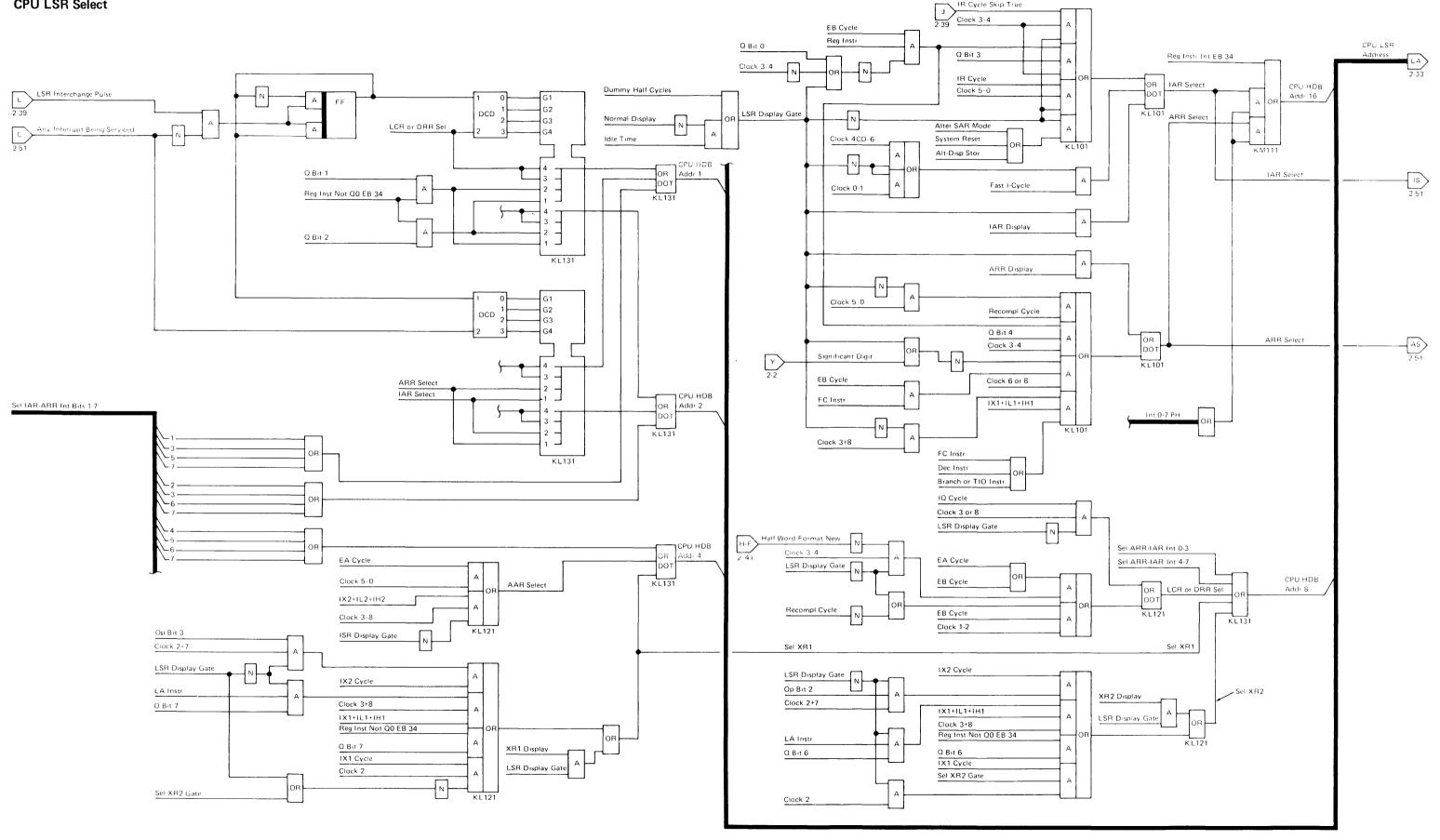

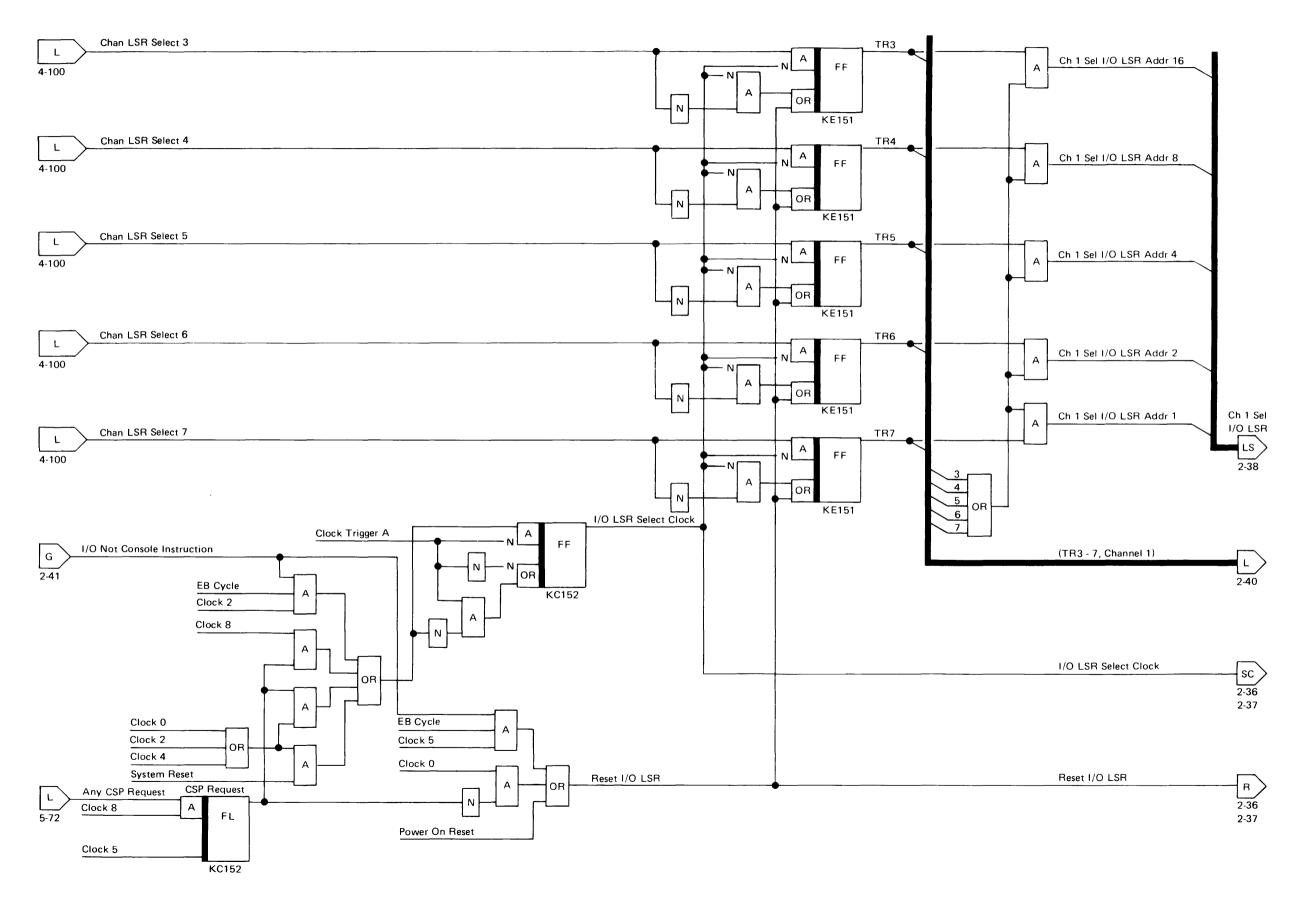

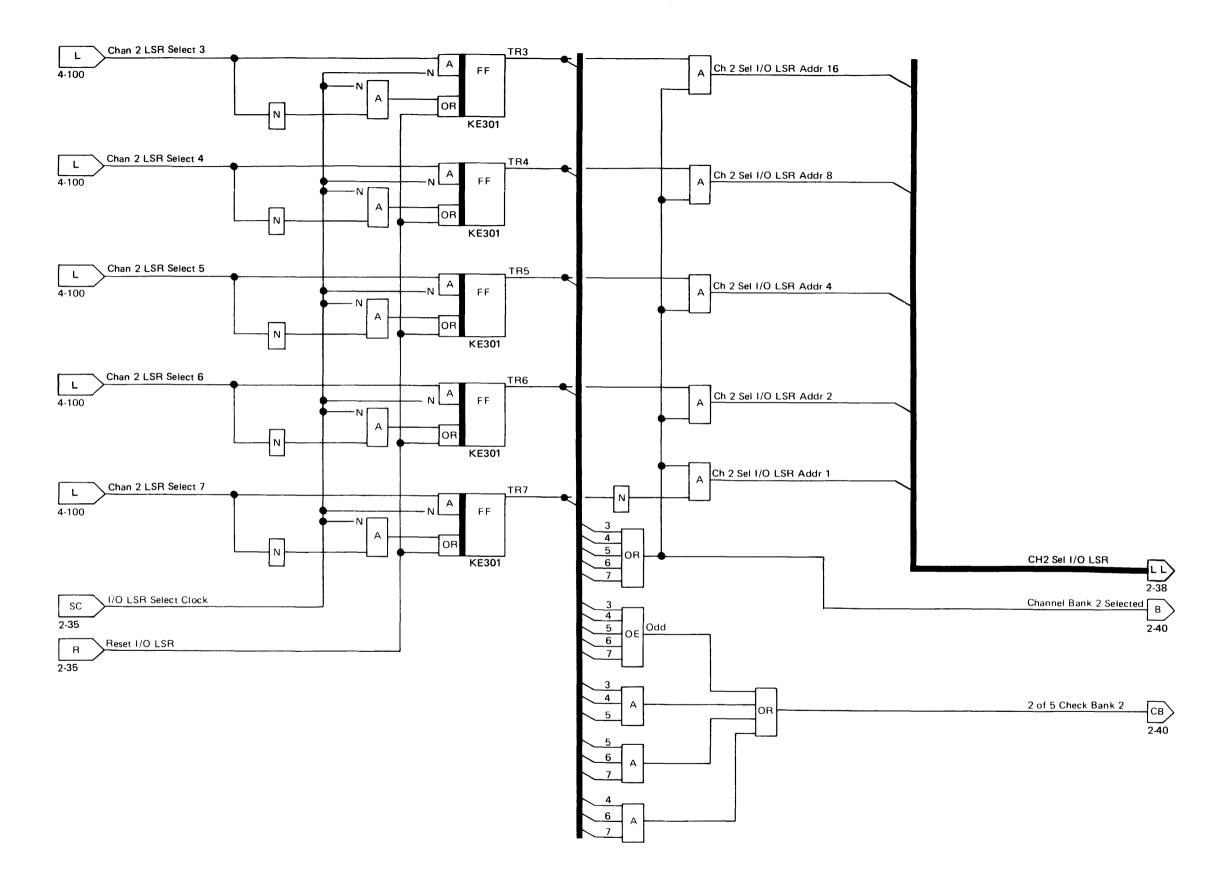

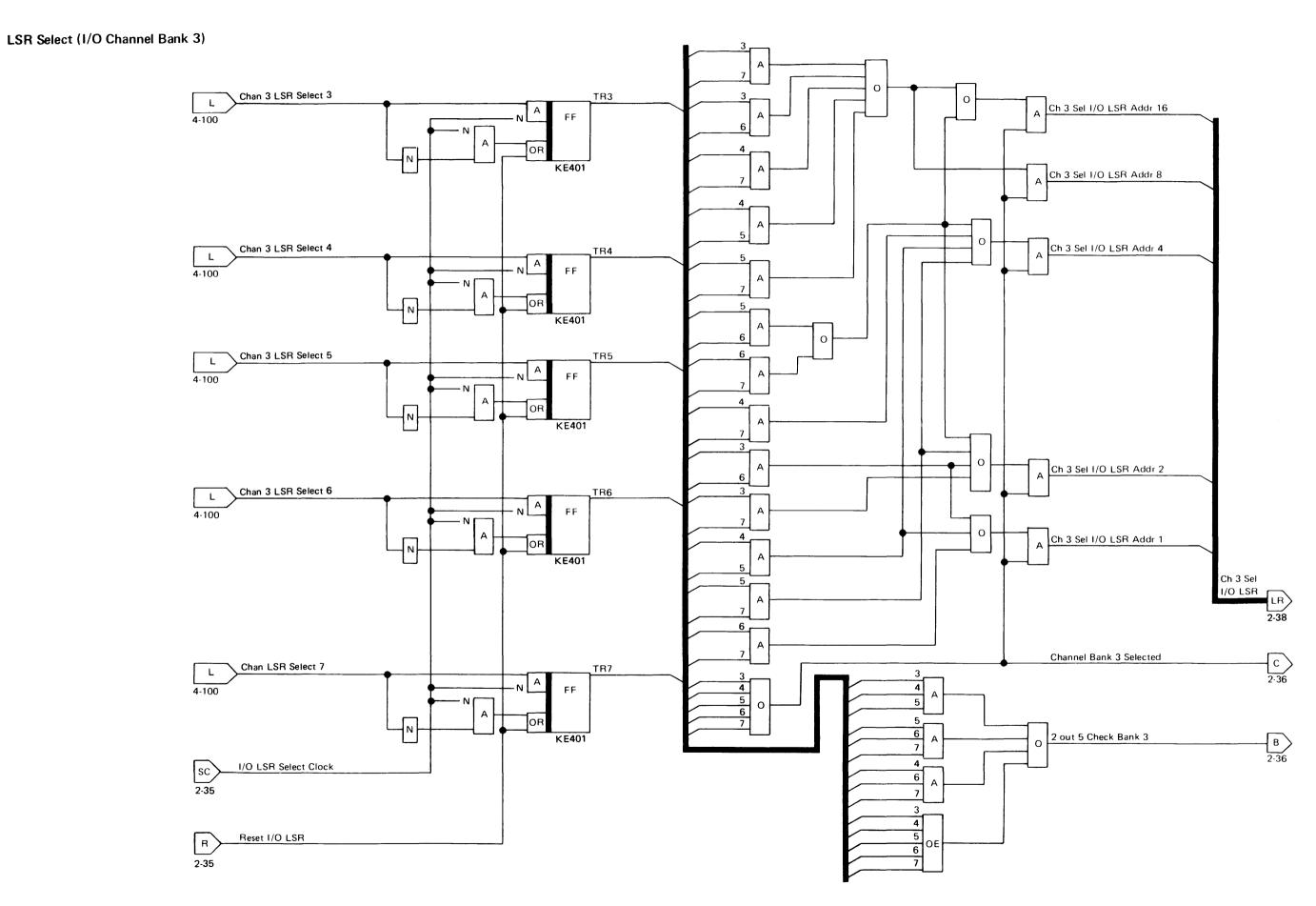

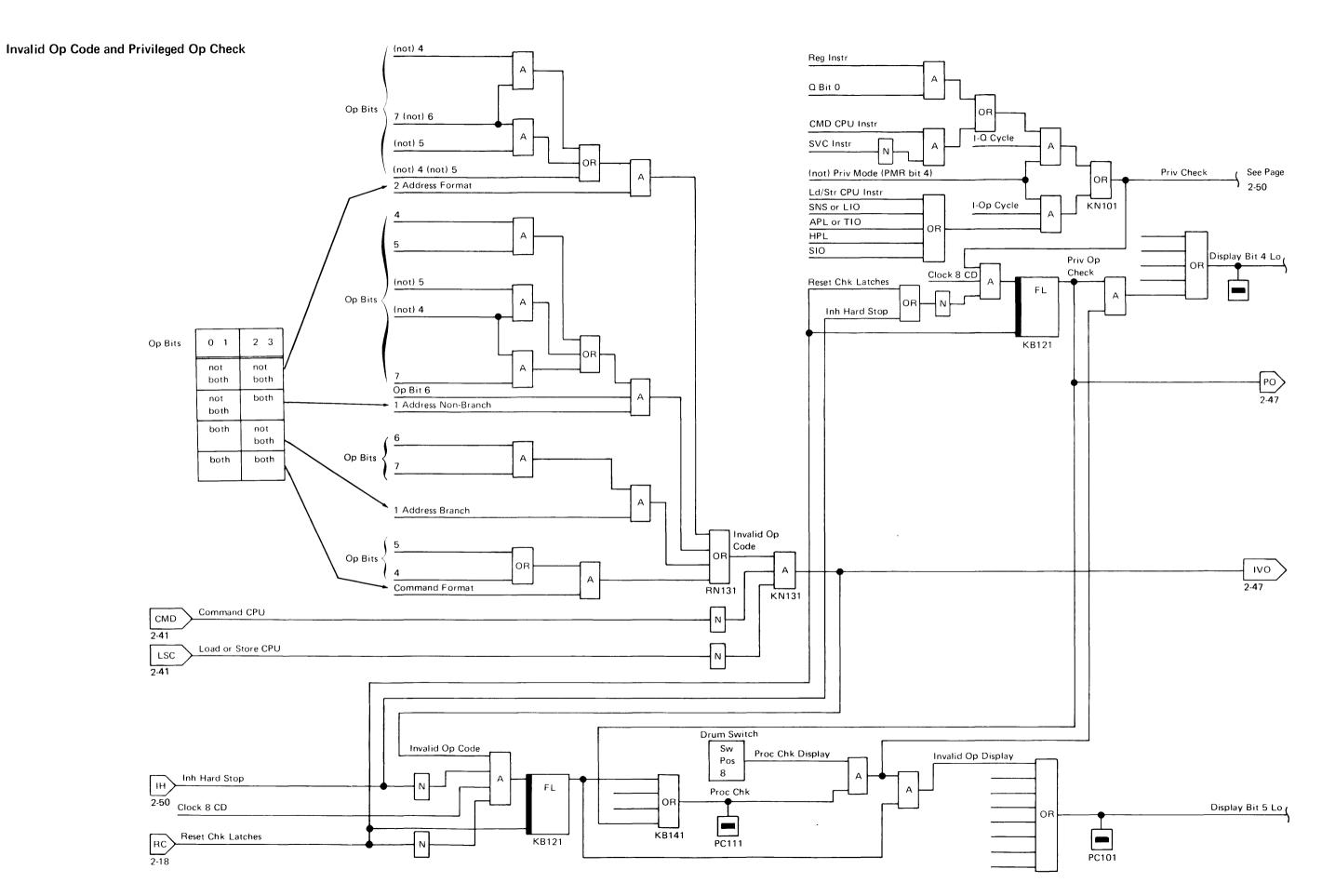

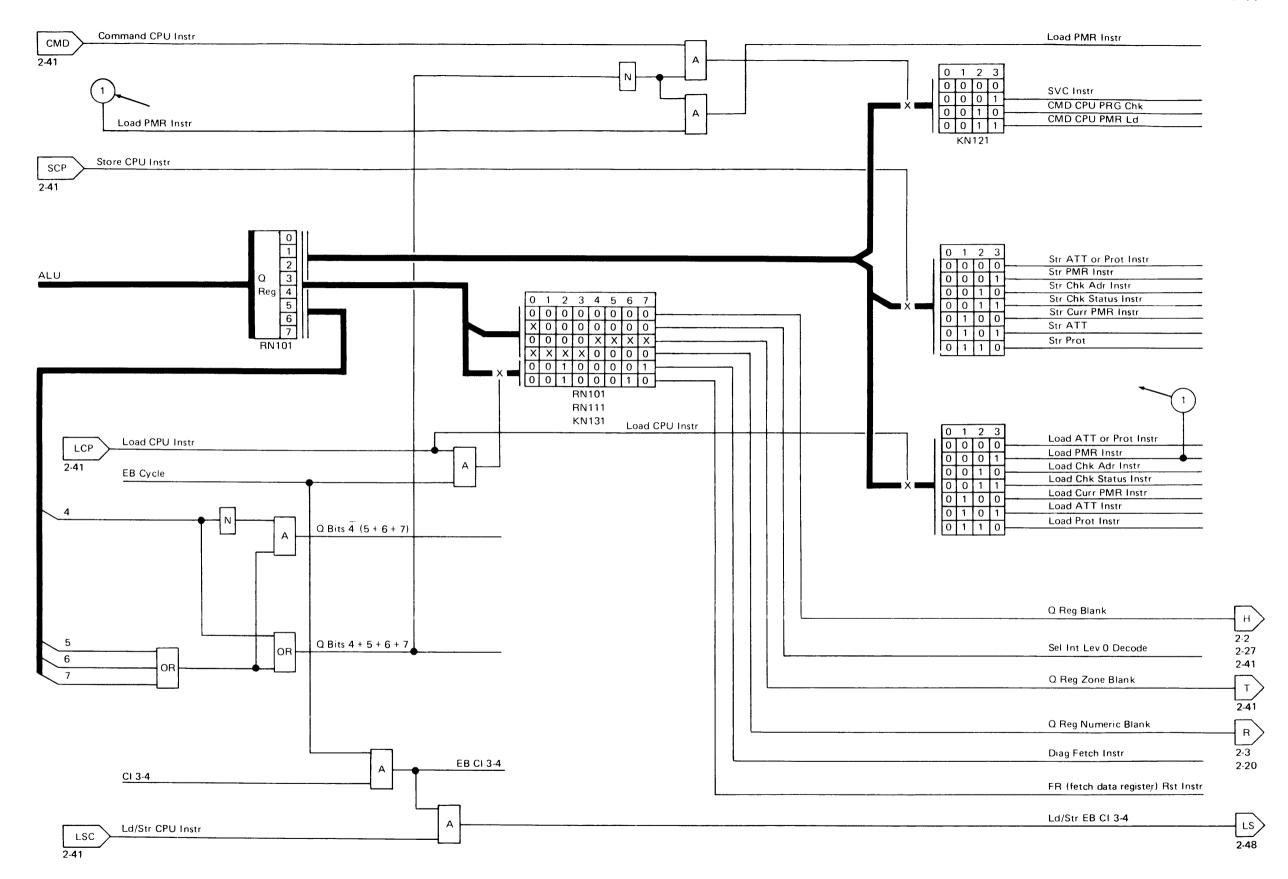

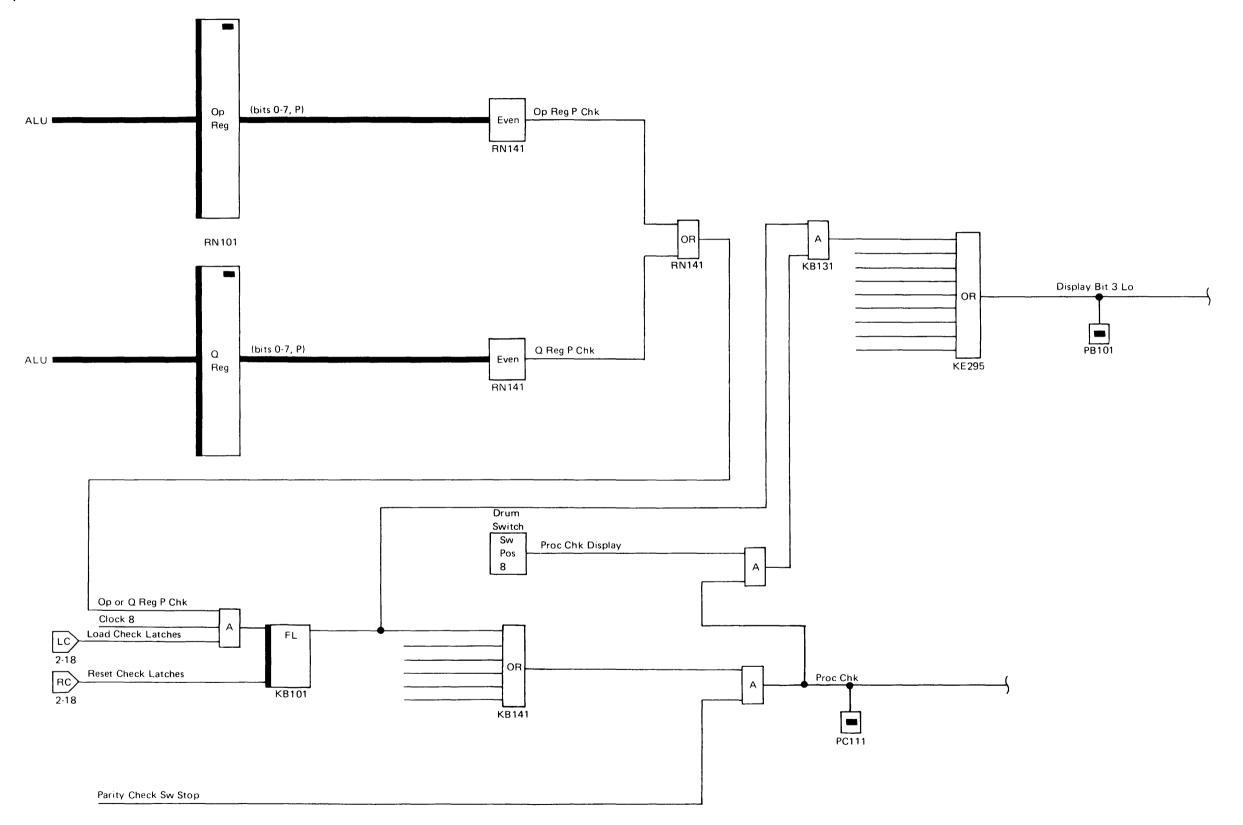

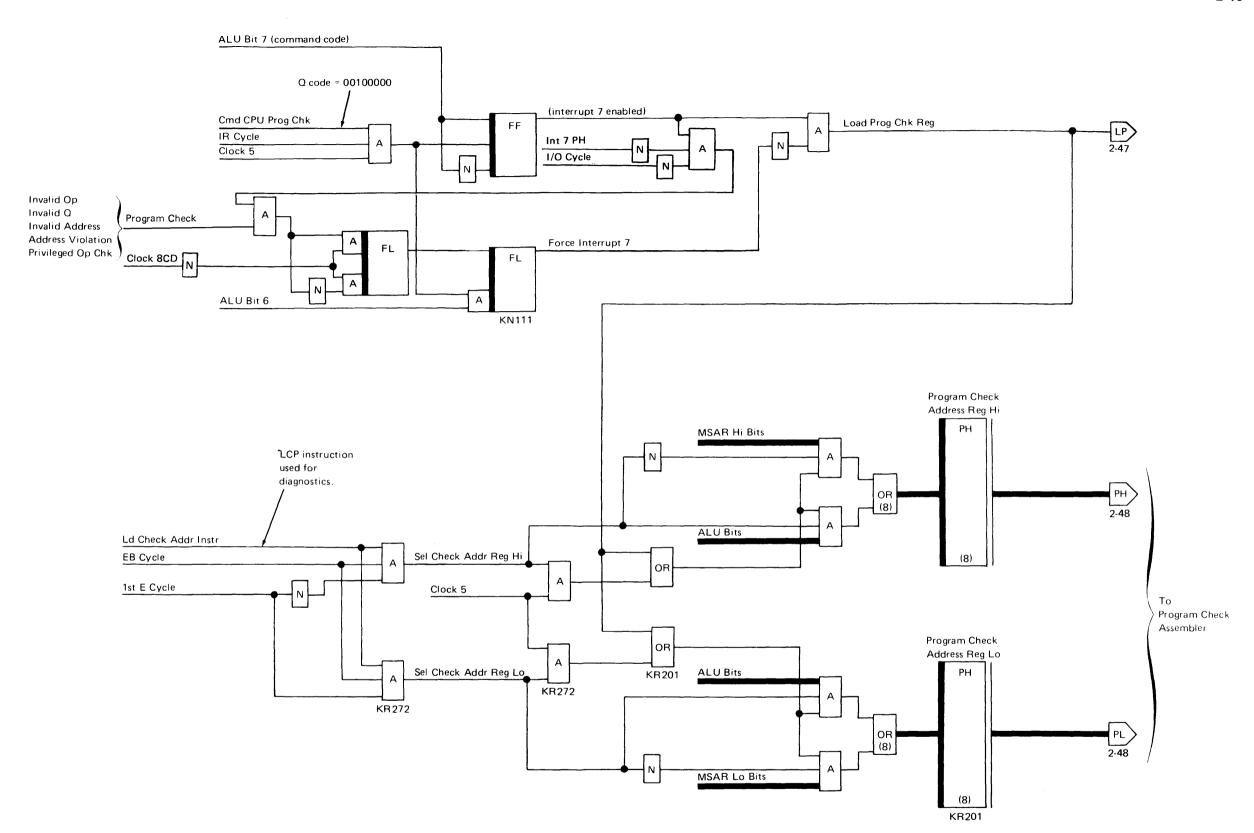

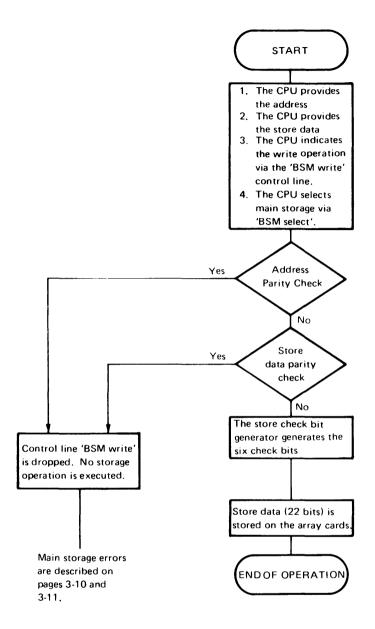

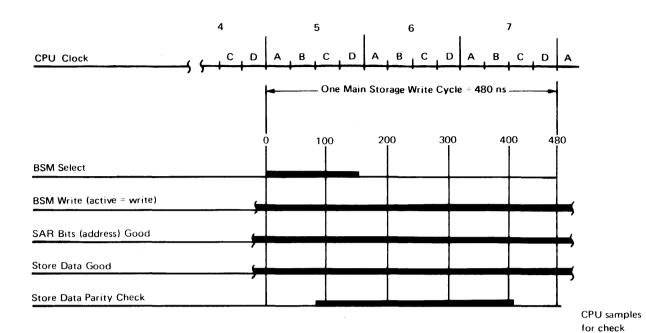

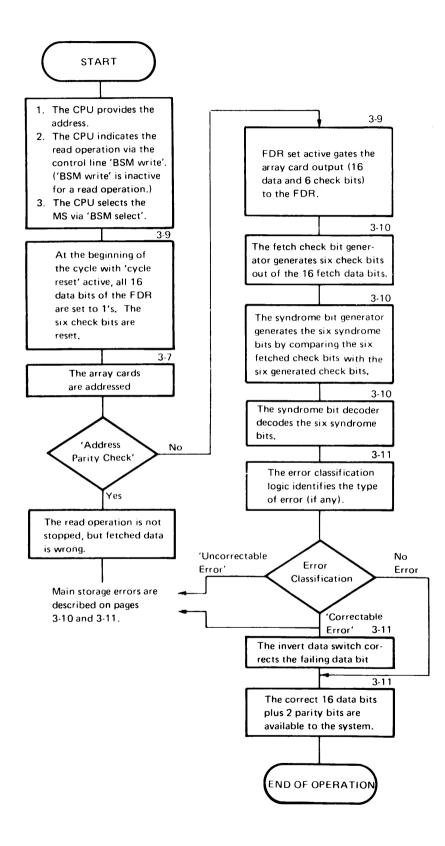

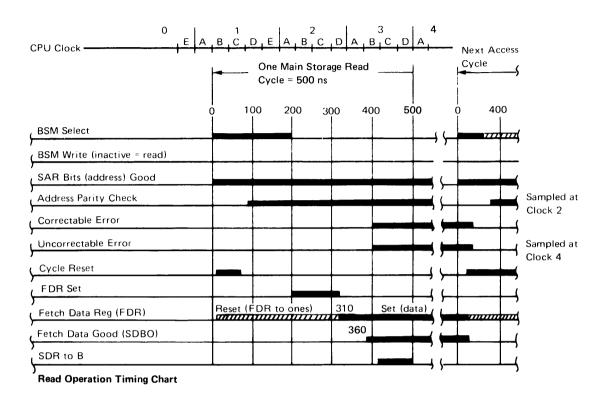

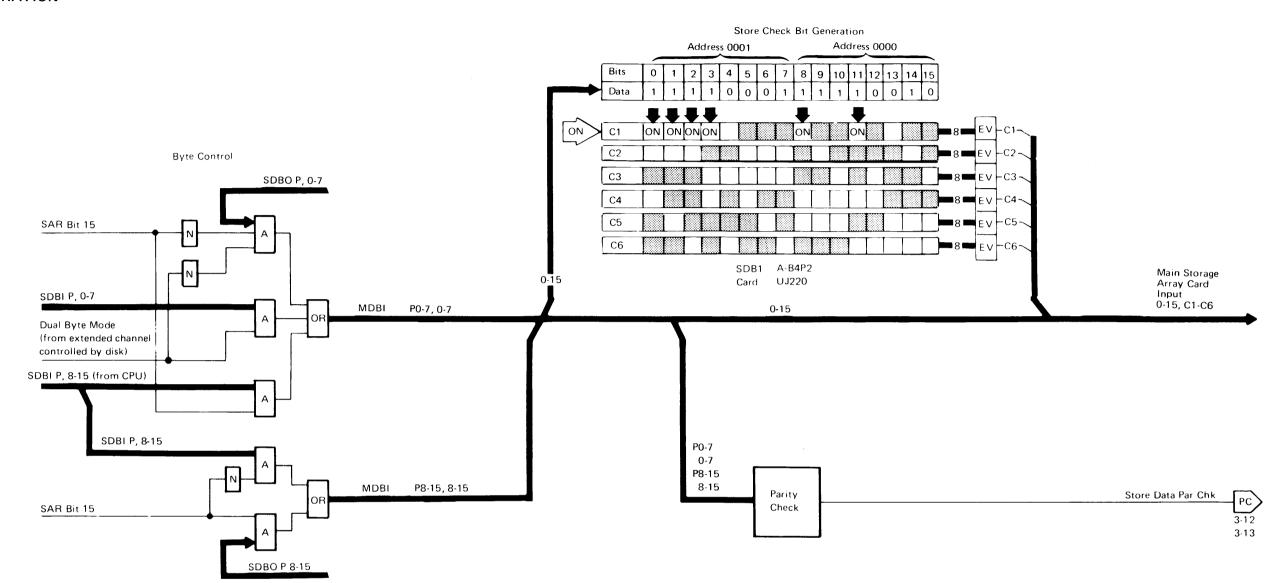

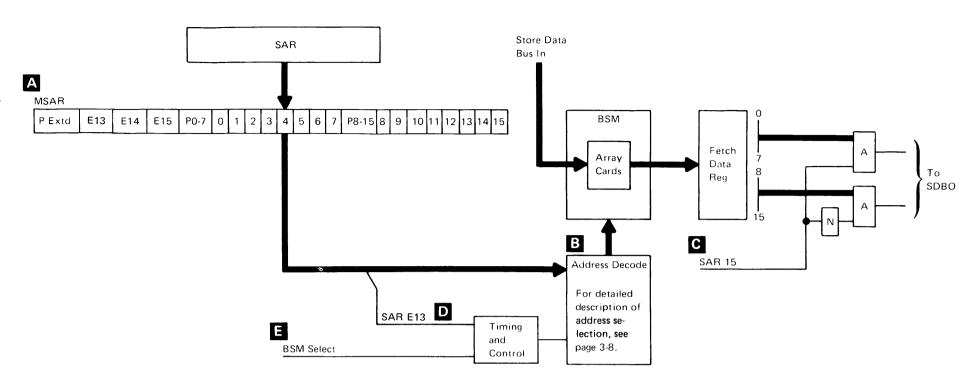

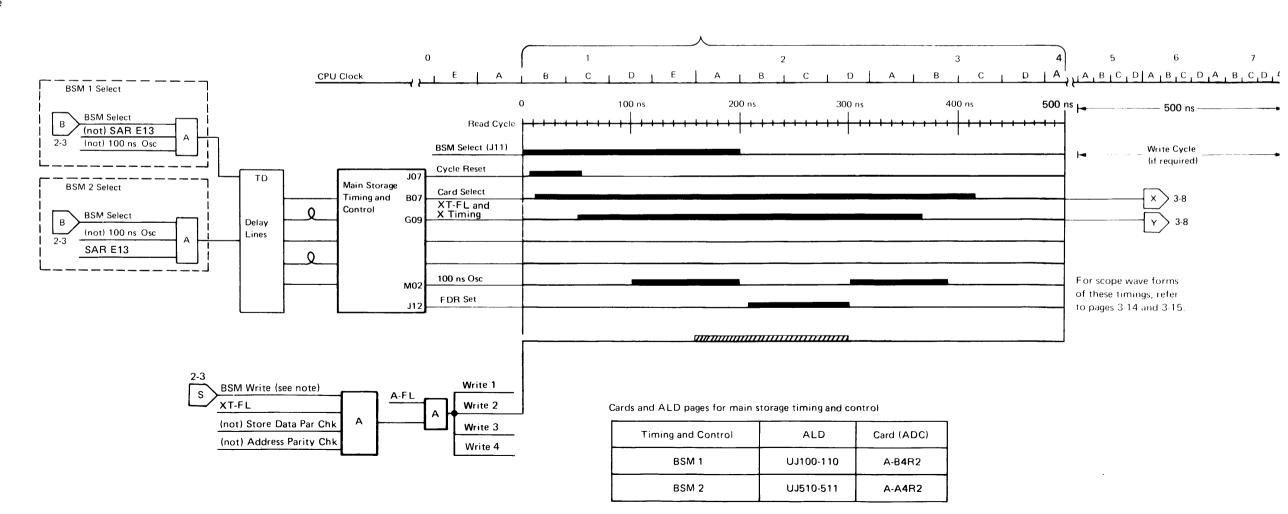

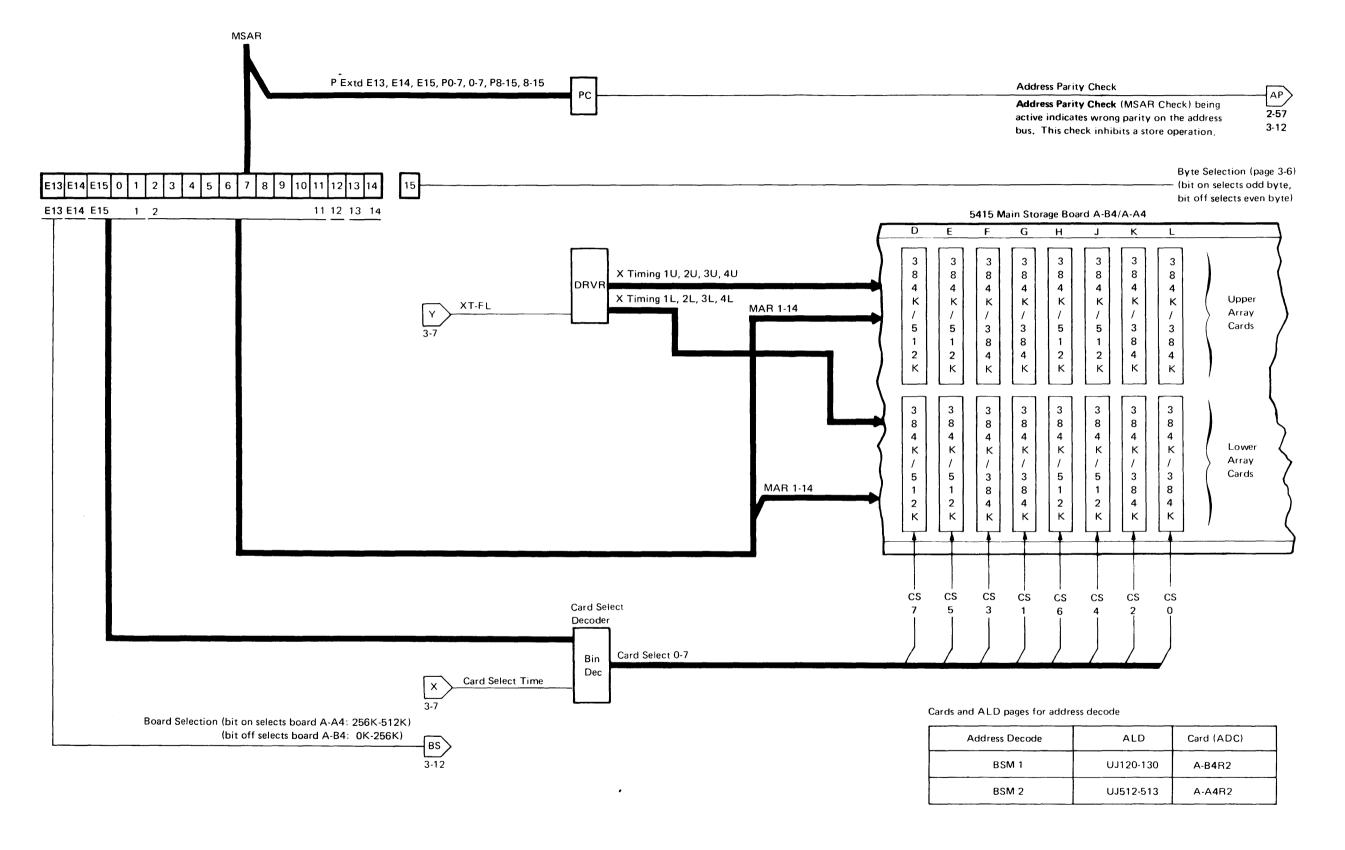

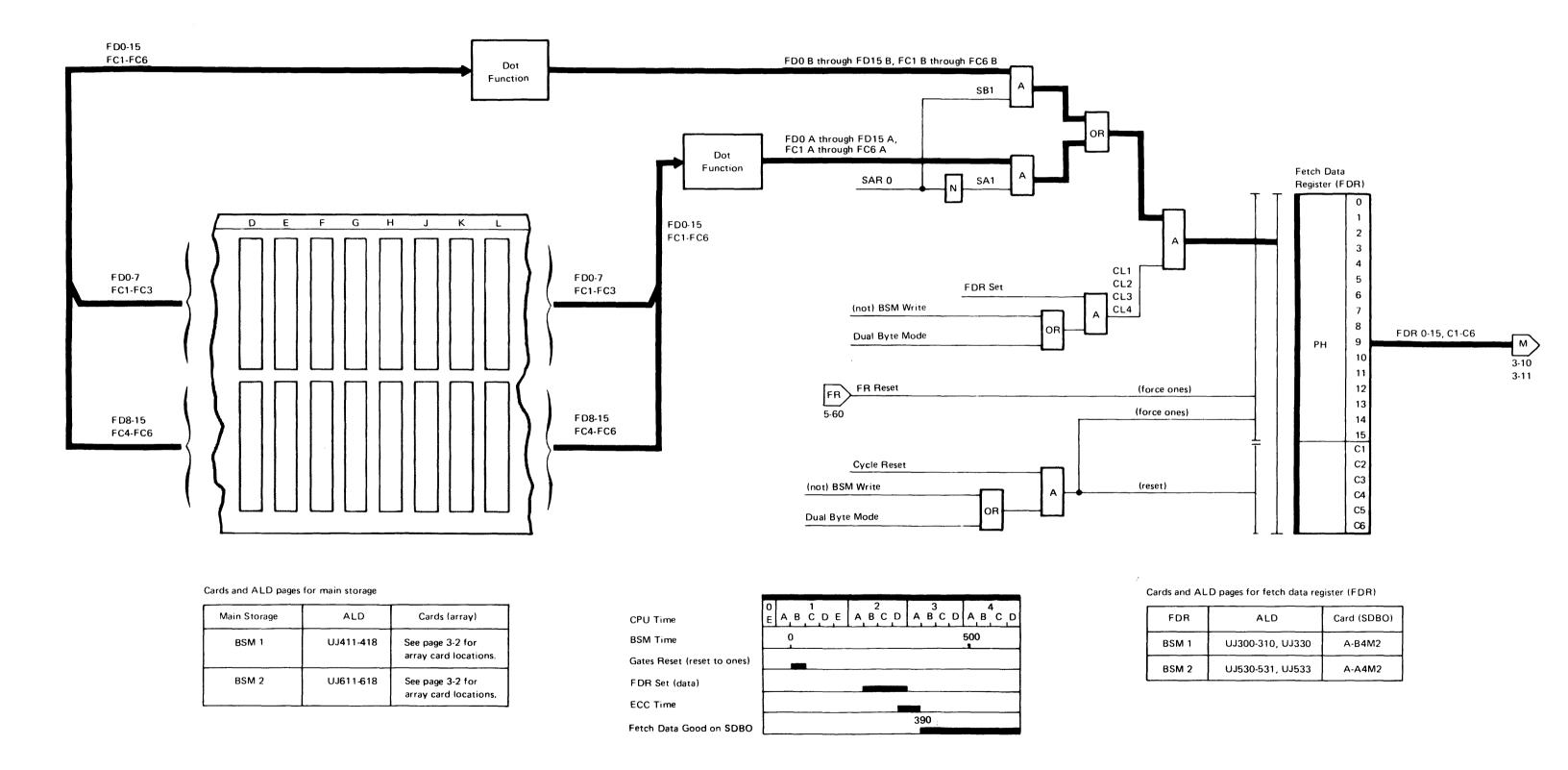

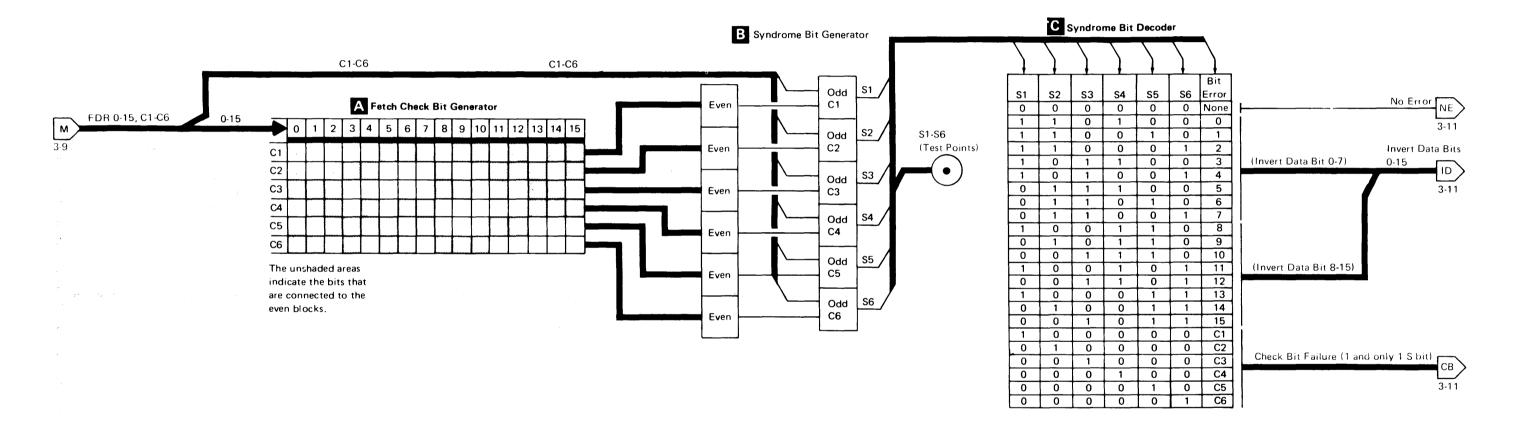

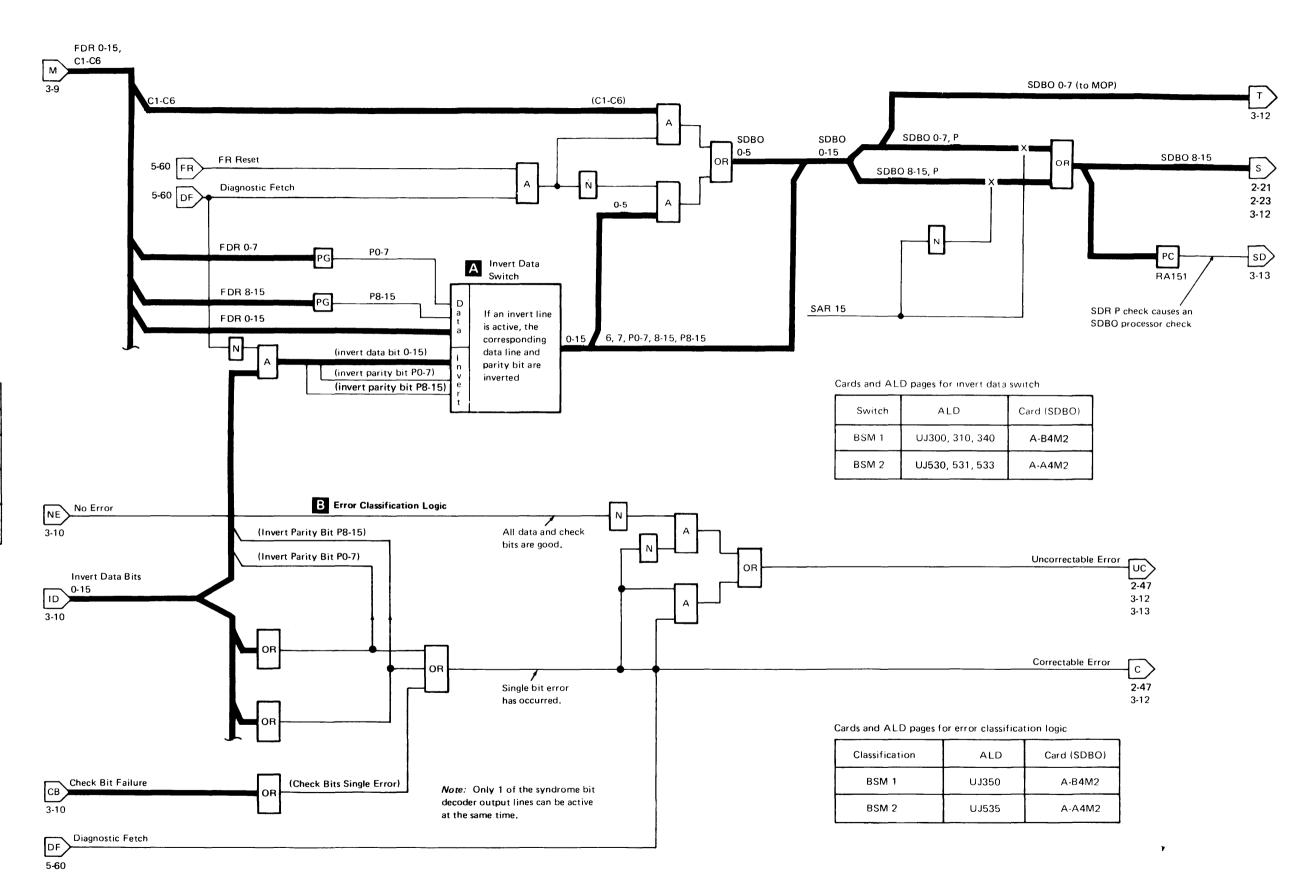

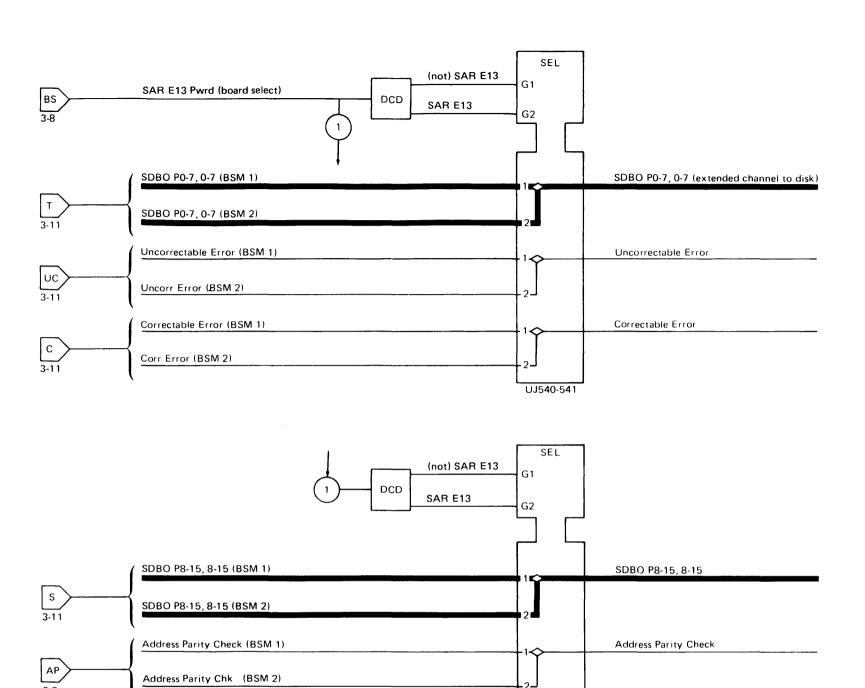

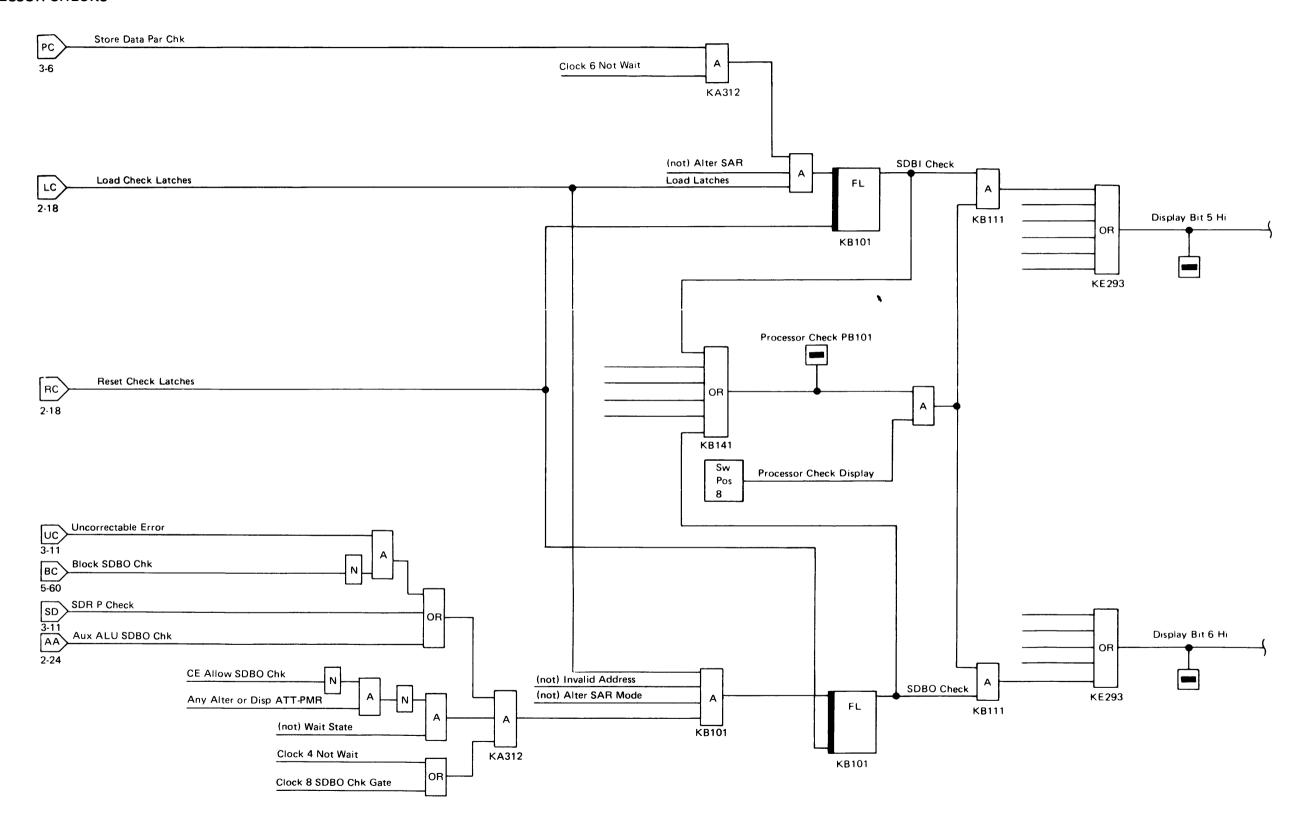

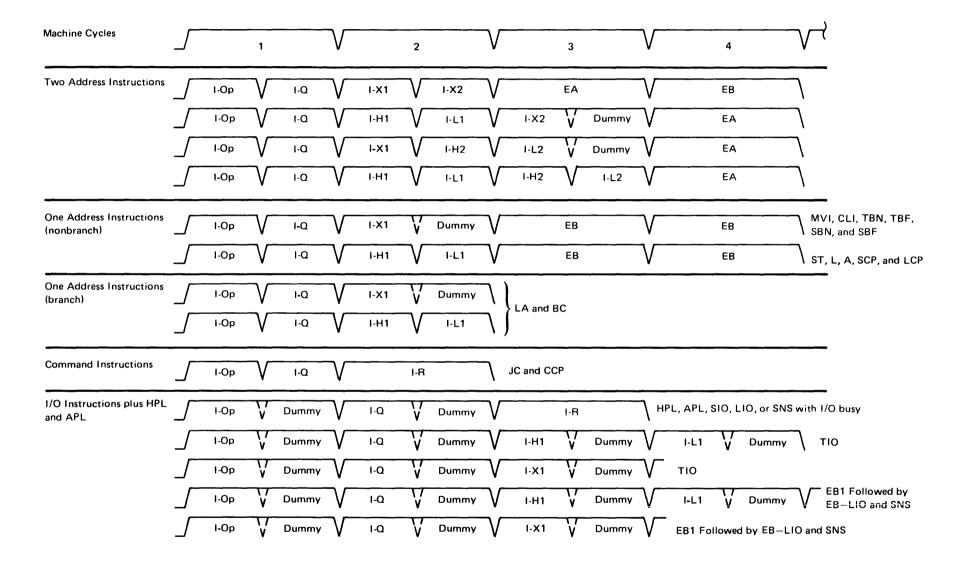

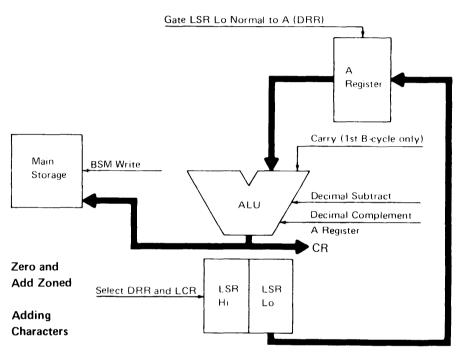

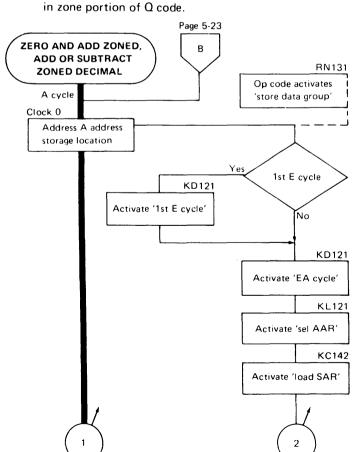

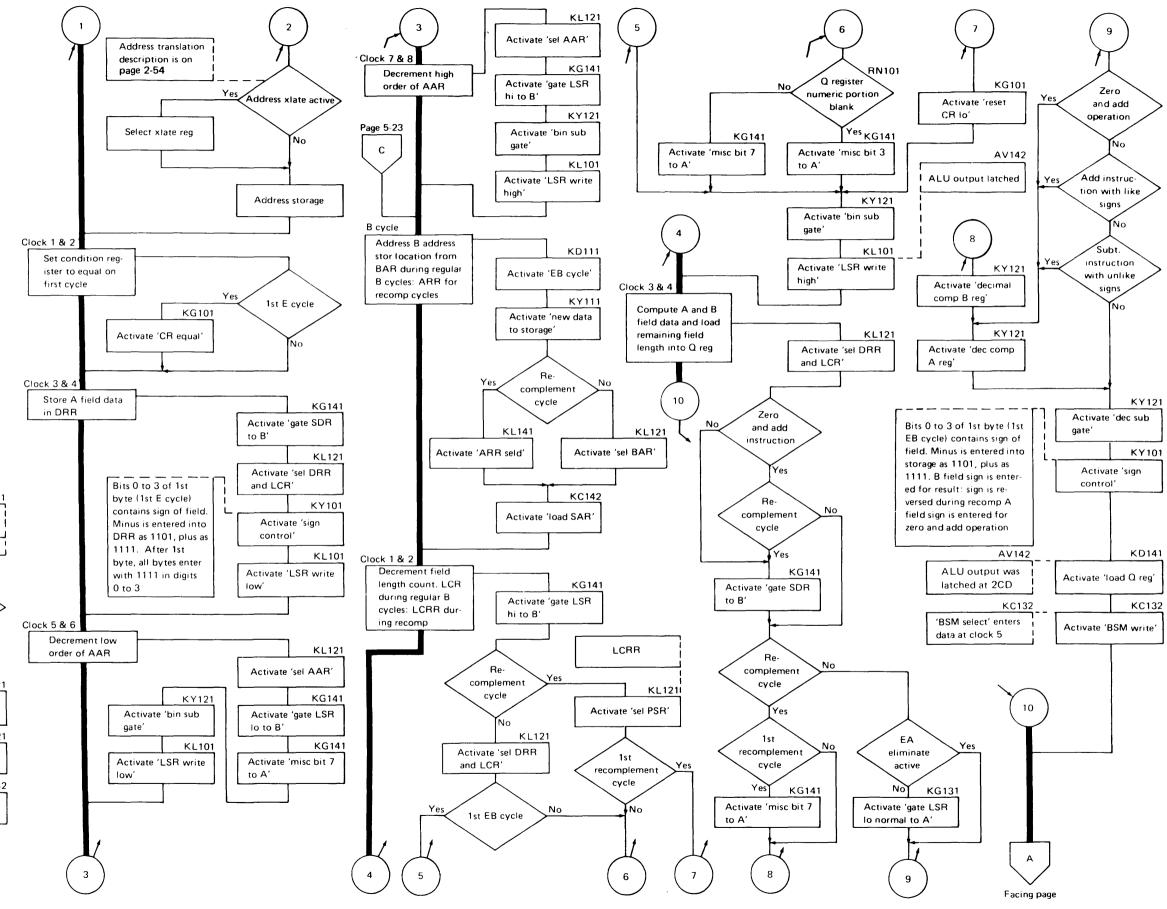

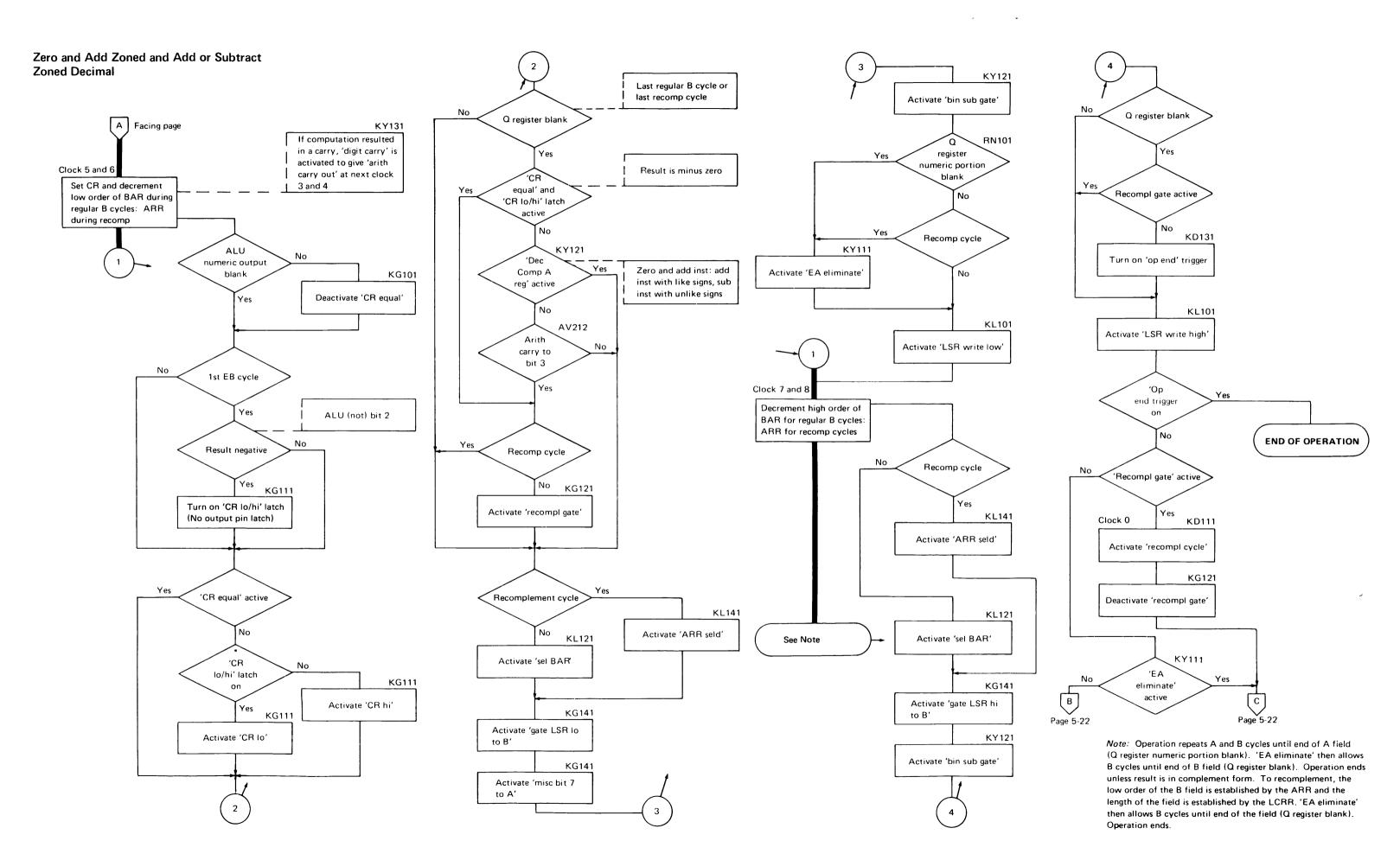

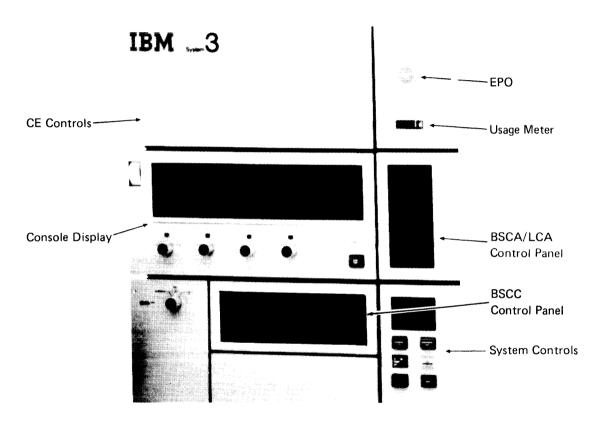

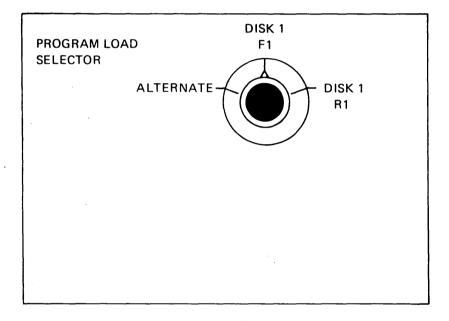

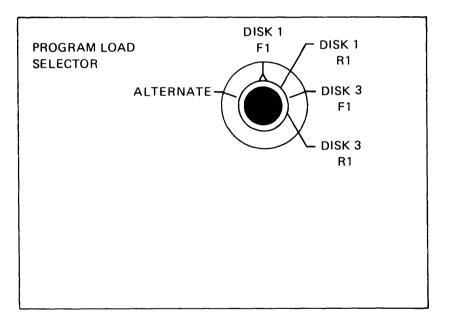

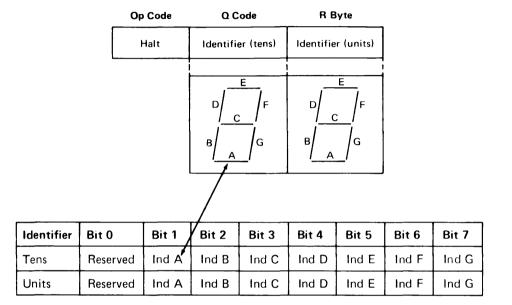

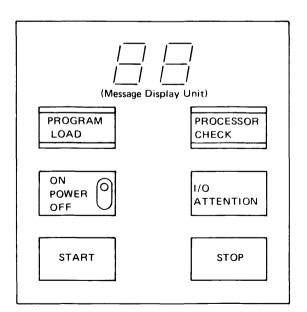

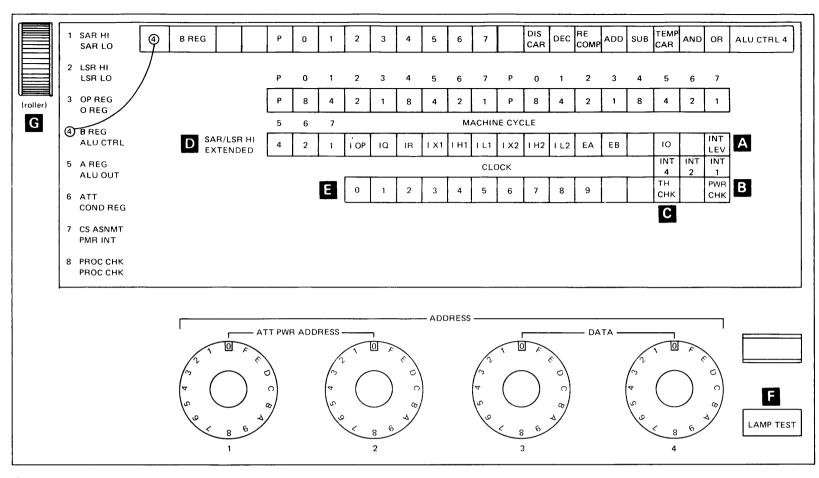

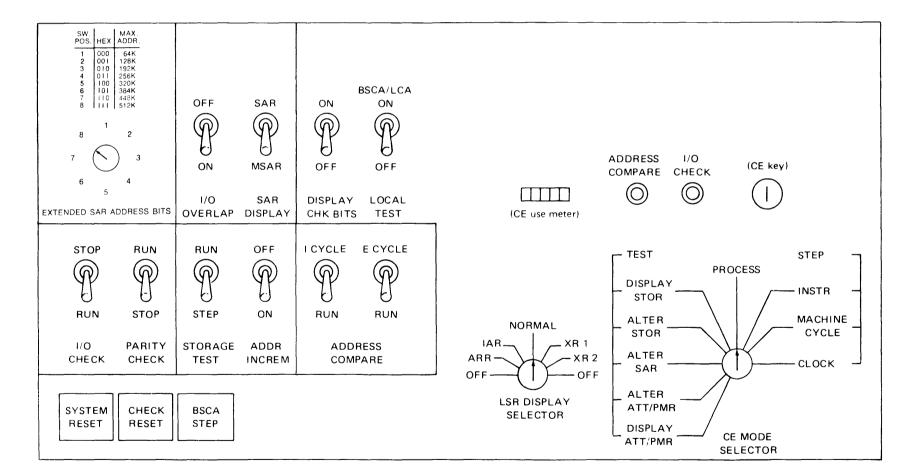

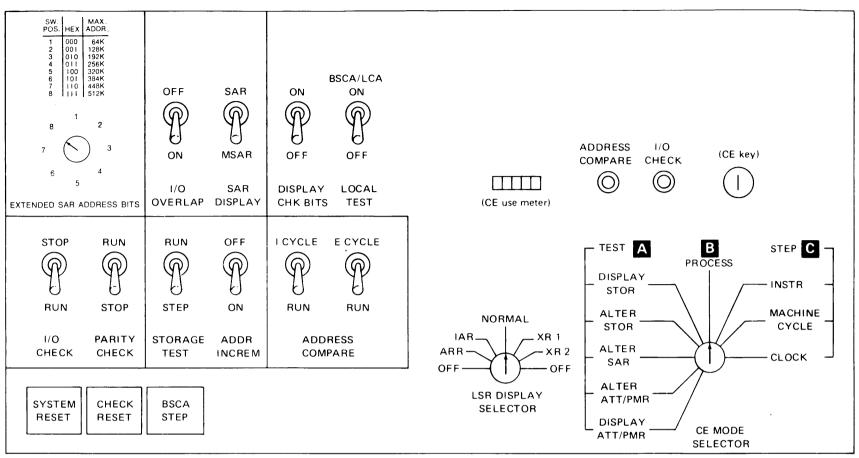

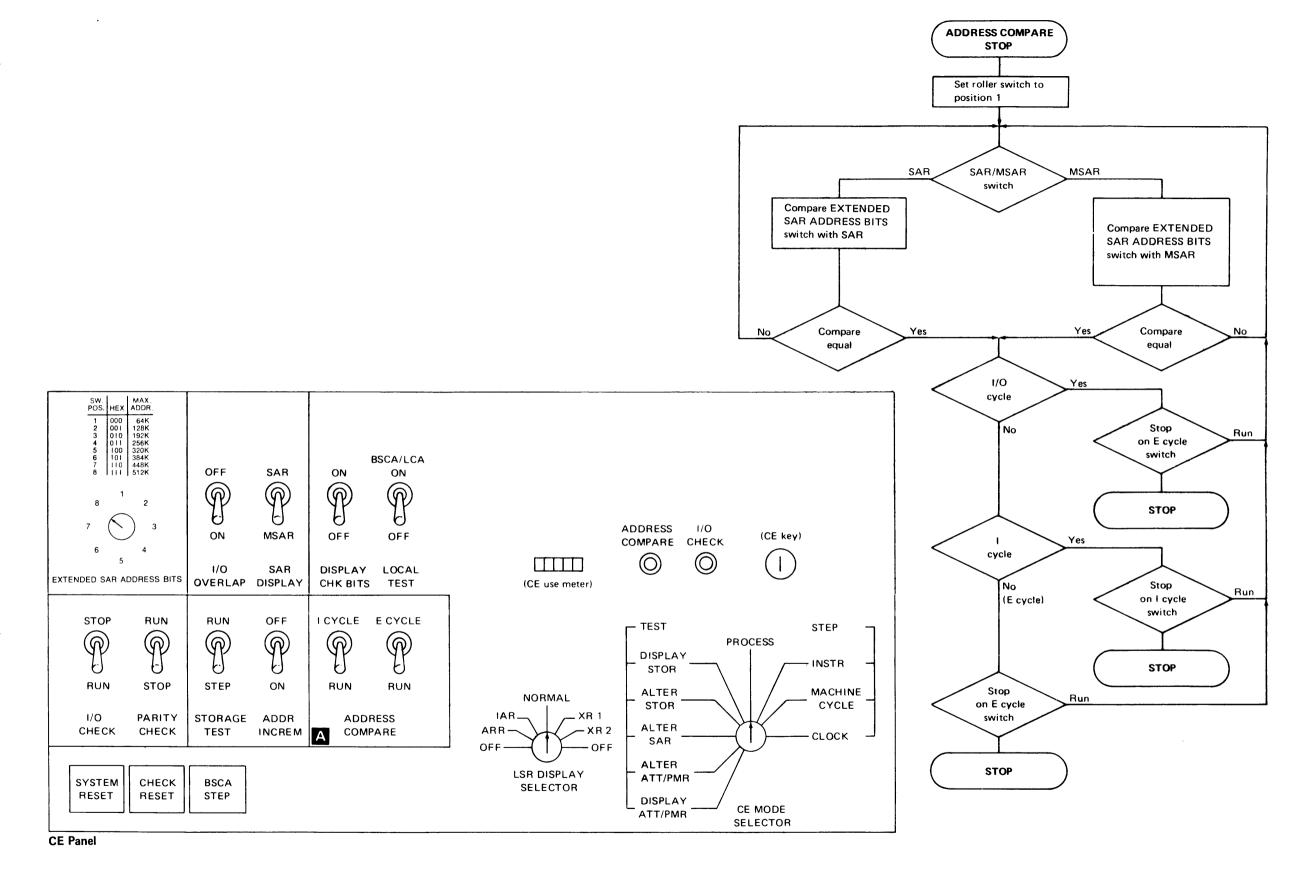

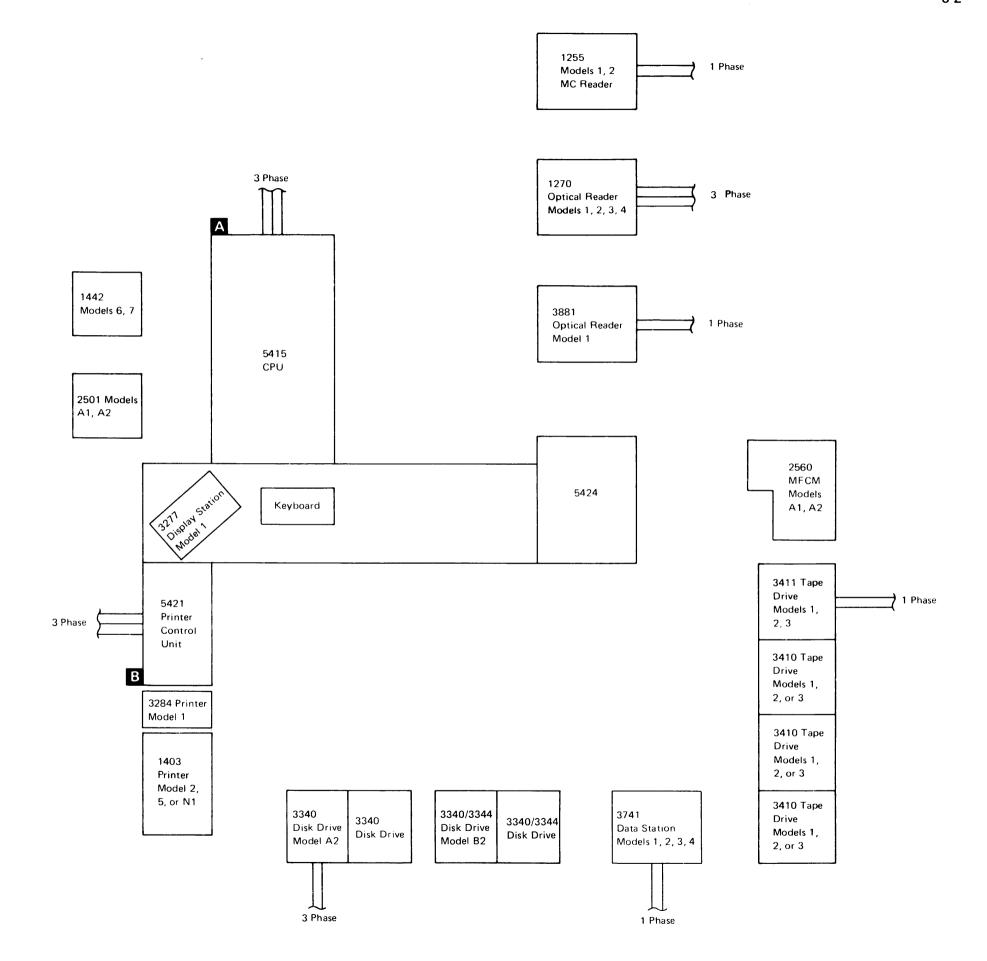

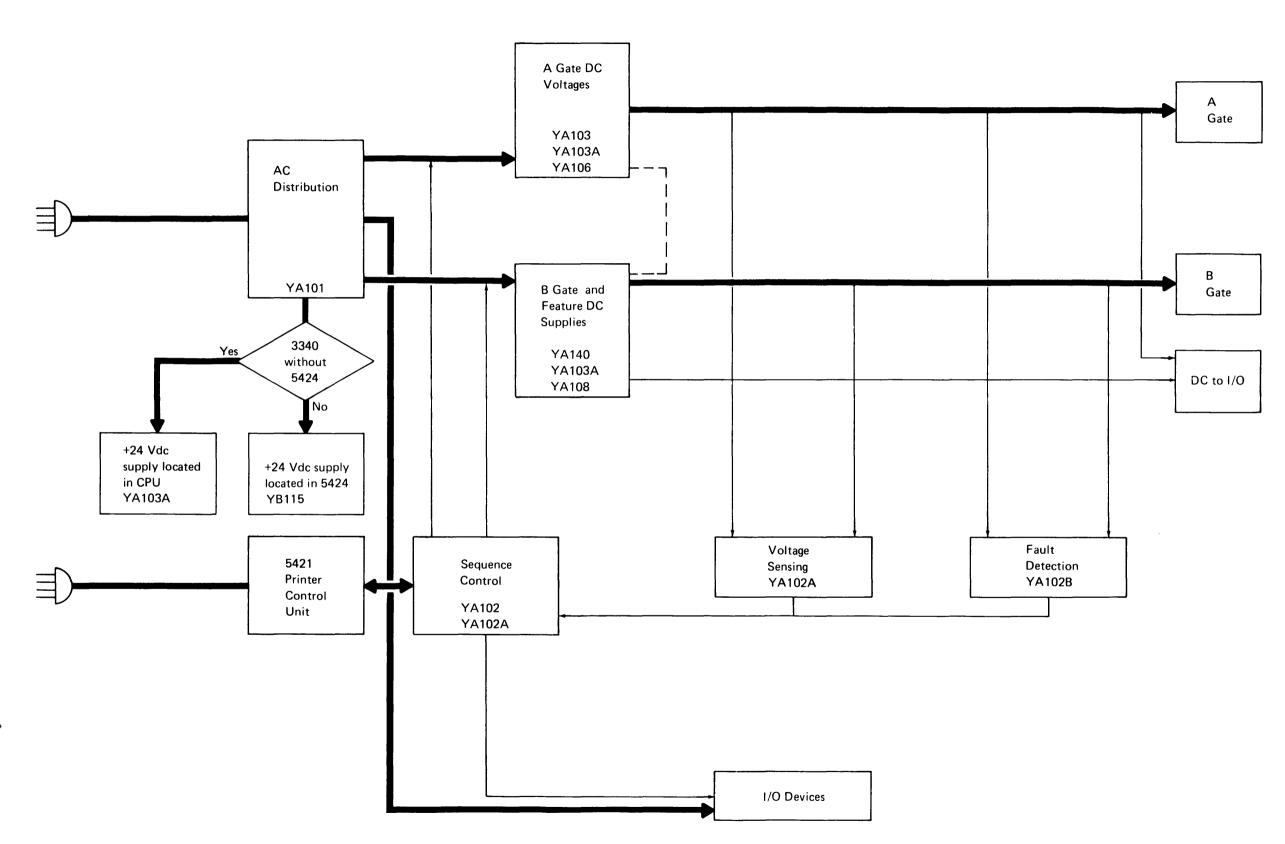

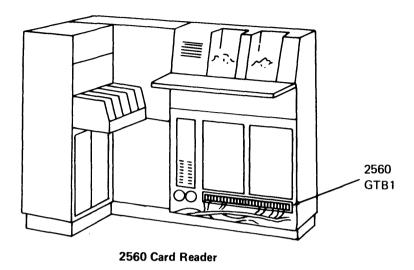

#### BSM READ OPERATION . . . . . . . . . AAR (A-Address Register) . . . . . . . . 1-9 CONTENTS BYTE CONTROL AND CHECK BIT GENERATION BAR (B-Address Register) . . . . . . . . 3-6 Index Register 1 and Index Register 2 . . . . 2-30 1-9 1-9 ARR (Address Recall Register) . . . . . . 2-30 3-7 1-10 LCR (Length Count Register) . . . . . . 3-7 3-7 DRR (Data Recall Register) . . . . . . PSR (Program Status Register) . . . . . . 2-30 3-7 1-10 Hexadecimal to Binary and Binary to Hexadecimal FETCH DATA REGISTER AND CONTROL . . 3-9 MRDAR (MFCU Read Data Address Register) . 2-30 MPCAR (MFCU Punch Data Address Register) 2-30 ERROR CHECKING AND CORRECTION . . . 1-10 Instruction Formats . . . . . . . . . . . . . . . . 1-11 MPTAR (MFCU Print Data Address Register) . 2-30 Fetch Check Bit Generator . . . . . . . . . . . . 2-30 3-10 1-11 LPDAR (Line Printer Data Address Register) . 2-30 3-10 LPIAR (Line Printer Image Address Register) . Processing Unit LSRs . . . . . . . . . . . . . . 1-11 2-31 Error Classification Logic . . . . . . . . . . 3-11 1-11 I/O LSRs . . . . . . . . . . . . . . . . . 2-32 3-11 3-11 LSR Select (I/O Channel Bank 1) . . . . . . MEMORY OUTPUT (MOP) . . . . . . . . . Instruction and Execute Cycle . . . . . . . 1-12 LSR Select (I/O Channel Bank 2) . . . . . . 2-36 IBM SYSTEM/3 MODEL 15D . . . . . . . . Sequential Instruction Execution . . . . . . SDBI/SDBO PROCESSOR CHECKS . . . . . . 2-37 1-12 LSR Select (I/O Channel Bank 3) . . . . . . 1-2 System Control Programming . . . . . . . . . MAIN STORAGE MAINTENANCE . . . . . 2-38 1-13 Multiprogramming . . . . . . . . . . . . 1-2 1-13 1-2 4-005 2-40 1-13 3277 Display Station/Keyboard . . . . . . 1-2 4-010 CHANNEL CABLING (CPU) . . . . . . . . 1-2 DBO TRANSLATOR (5424) . . . . . . . . . 4-095 PRIVILEGED MODE/MODEL 10 COMPATIBILITY 2-42 PROCESSOR FUNCTIONAL UNITS . . . . . IBM 2501 Card Reader . . . . . . . . . . 1-2 2-1 IBM 2560 Multi-Function Card Machine . . . 1-3 2-42 IBM 3340 Direct Access Storage Facility . . . . 1-3 4-107 Invalid Op Code and Privileged Op Check . . . . 2-43 DBO AND TRANSLATOR . . . . . . . . IBM 3741 Data Station Models 1 and 2 IBM 3741 2-44 CONSOLE SWITCHES . . . . . . . . . . . . . 2-8 Programmable Work Station Models 3 and 4 . . . 4-115 2-45 DBI AND TRANSLATOR. . . . . . . . . . 2-8 IBM 3344 Direct Access Storage . . . . . . 1-3 2-46 CHANNEL DBO PARITY, INVALID DEVICE IBM 5424 Multi-Function Card Unit . . . . PROGRAM CHECK ASSEMBLER, STORE DATA Binary Subtraction . . . . . . . . . . . . . . . ADDRESS . . . . . . . . . . . . . . . 4-120 IBM 1442 Card Read Punch . . . . . . . 1-4 DBO PARITY . . . . . . . . . . . . . . . 4-125 IBM 3410 Magnetic Tape Unit . . . . . . 2-49 IBM 1403 Printer Model 2, Model 5, and Model DBI PARITY . . . . . . . . . . . . . 4-130 2-12 2-49 1.5 Supervisor Program (Interrupt Level 0) . . . . CPU INSTRUCTIONS . . . . . . . . . . . . 5-1 1-5 Op End Interrupt (Interrupt Level 5) . . . . . 2-50 INSTRUCTIONS AND SIGNAL REFERENCE. . . Program Check Interrupt (Interrupt Level 7). . . INSTRUCTION CYCLES (FAST I-CYCLE) . . . TWO-ADDRESS INSTRUCTIONS . . . . . . LCA (Local Communications Adapter) . . . Parity Generation and Parity Check . . . . . . 2-52 MLTA (RPQ) . . . . . . . . . . . . . . . . 2-52 **BSCC** (Binary Synchronous Communications 5-3 Channel Terminate Feature . . . . . . . MAIN STORAGE ADDRESSING . . . . . . 1-5 2-19 5-7 A-REGISTER AND CONTROLS . . . . . . I/O LSR 17th, 18th, and 19th Bits . . . . . . 2-55 I-H and I-L Cycles . . . . . . . . . . . . . 1-5 5-7 Scheduled Maintenance . . . . . . . . . . . . I-H2 and I-L2 Cycles . . . . . . . . . . . 1-5 2-20 5415 PROCESSING UNIT (CPU) B REGISTER AND CONTROLS Invalid Address/Storage Protect Check . . . . . 2-58 5-14 A/B REGISTER PARITY CHECKING . . . . 2-22 1-6 1-6 AUXILIARY ALU . . . . . . . . . . . . . . . 2-59 5-14 5-14 2-24 1-7 AUXILIARY ALU CARD CHECK . . . . . . 3-1 Add Logical Characters—ALC . . . . . . . 1-7 Subtract Logical Characters—SLC . . . . . . 1-7 CONDITION REGISTER (CR) . . . . . . . 2-26 3-1 5-15 Condition Register Settings . . . . . . . . . 3-1 Compare Logical Characters—CLC . . . . . . 5-16 1-7 2-26 PROGRAM MODE REGISTERS (PMR) . . . . Move Characters—MVC . . . . . . . . . . . . 3-1 1-7 3-1 Move Characters or Compare, Add, or Subtract 1-7 3-2 2-28 MAIN STORAGE LOCATIONS . . . . . . . . 5-17 1-7 LOCAL STORAGE REGISTERS (LSR) . . . . 3-3 Add or Subtract Zoned Decimal—AZ—SZ . . . . 5-20 1-8 IAR (Instruction Address Register) . . . . BSM WRITE OPERATION . . . . . . . . . . . . 3-4 5-21 1-9

| Recomplementing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-21         | Alter Storage                                  | 6-5                    | CE CONTROLS                                                               | 7-7        | SUPPLY NO. 3 (Lower Boards)                     | 8-12         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------------------------------|------------------------|---------------------------------------------------------------------------|------------|-------------------------------------------------|--------------|

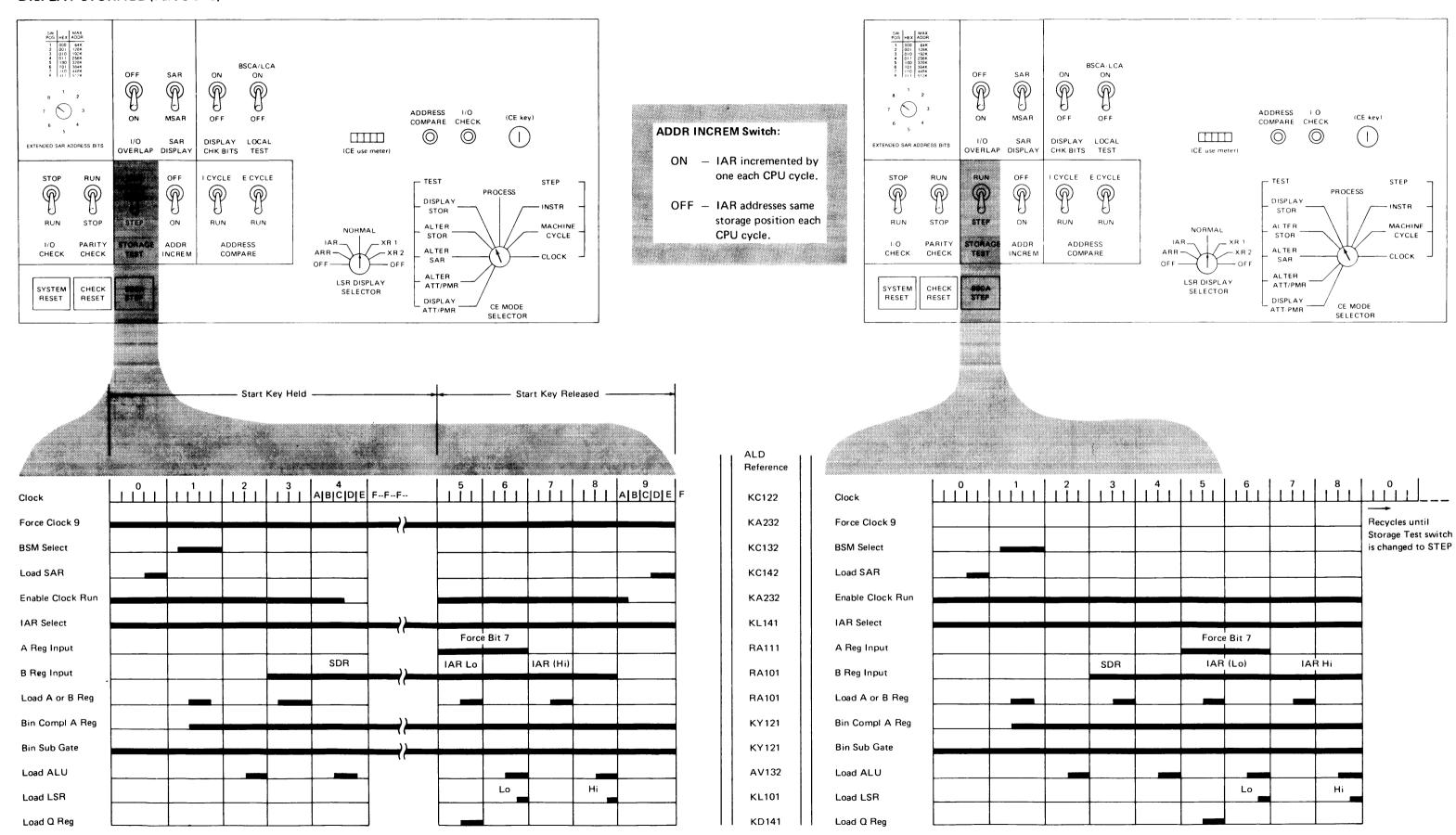

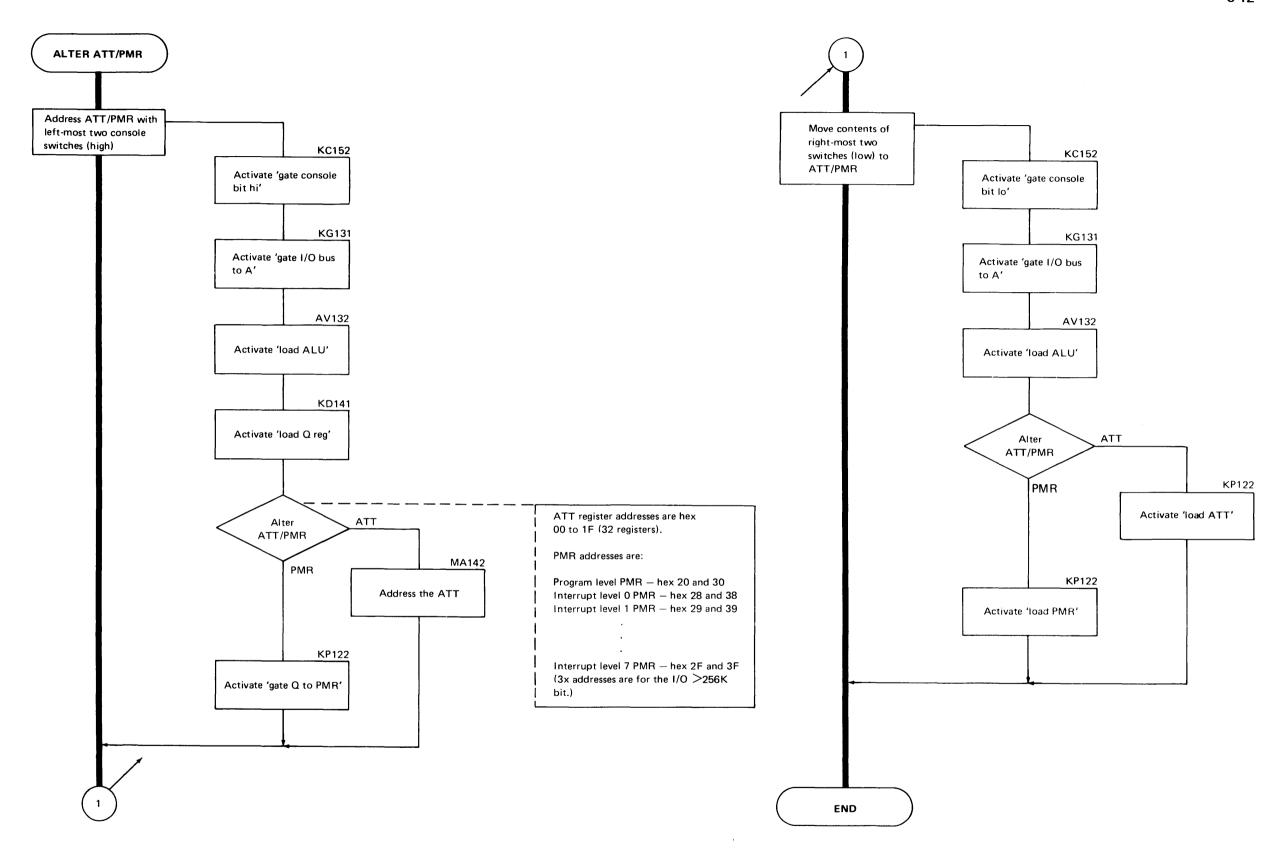

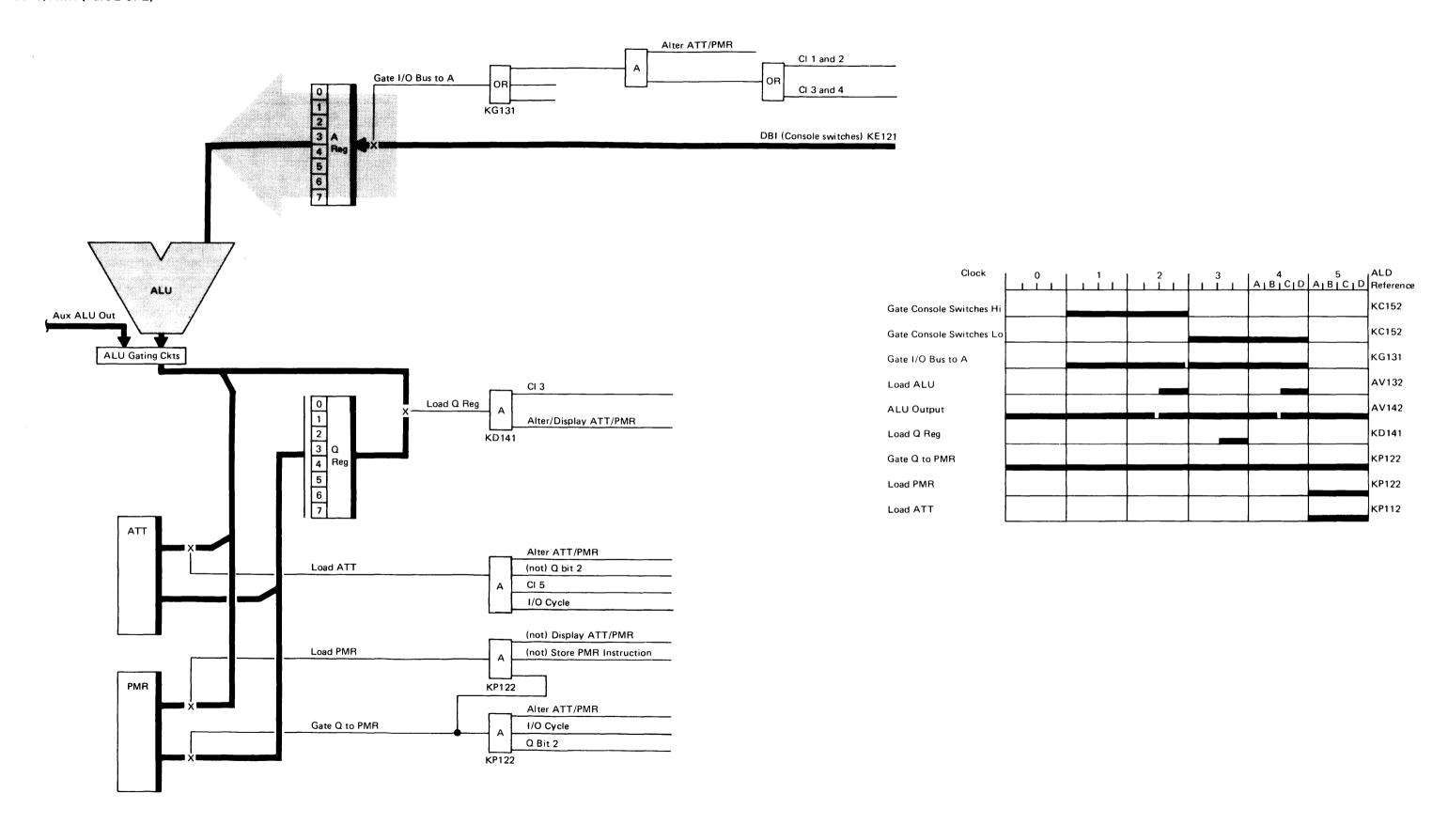

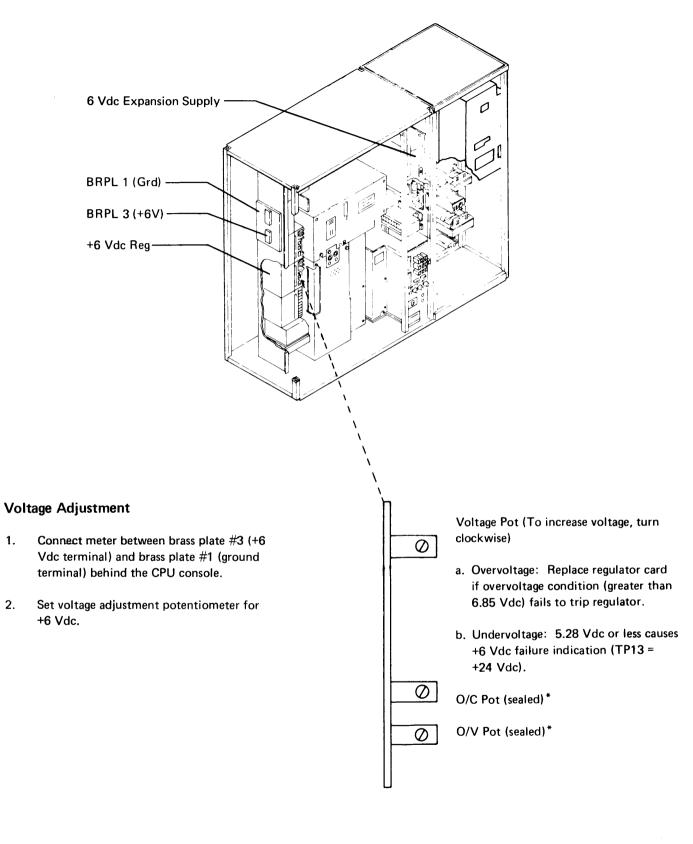

| Zero and Add Zoned —ZAZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-21         | DISPLAY STORAGE                                | 6-8                    | ADDRESS/DATA Switches (Below Console                                      |            | Voltage Adjustment                              | 8-12         |

| Zero and Add Zoned and Add or Subtract Zoned                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              | Objectives                                     | 6-8                    | Display) (ALD PA111)                                                      | 7-7        | End View of -4V Regulator Card                  | 8-12         |

| Decimal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-22         | ALTER ATT/PMR                                  | 6-12                   | SYSTEM RESET Key (ALD PC101)                                              | 7-7        | +6 VOLT LOGIC SUPPLY                            | .8-13        |

| Edit-ED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-26         | Objectives                                     | 6-12                   | CE Key Switch (ALD PC111)                                                 | 7-7        | +6 Vdc Regulator                                | 8-13         |

| Insert and Test Character—ITC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-30         | ALTER SAR                                      | 6-14                   | CHECK RESET Key (ALD PC101)                                               | 7-7        | +6V Expansion Bulk Supply (Feature)             |              |

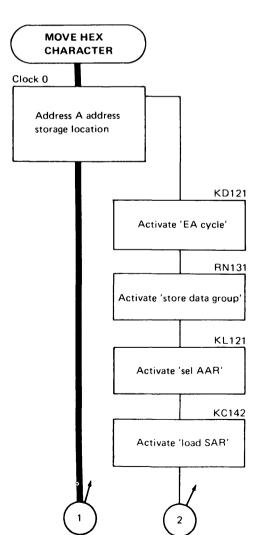

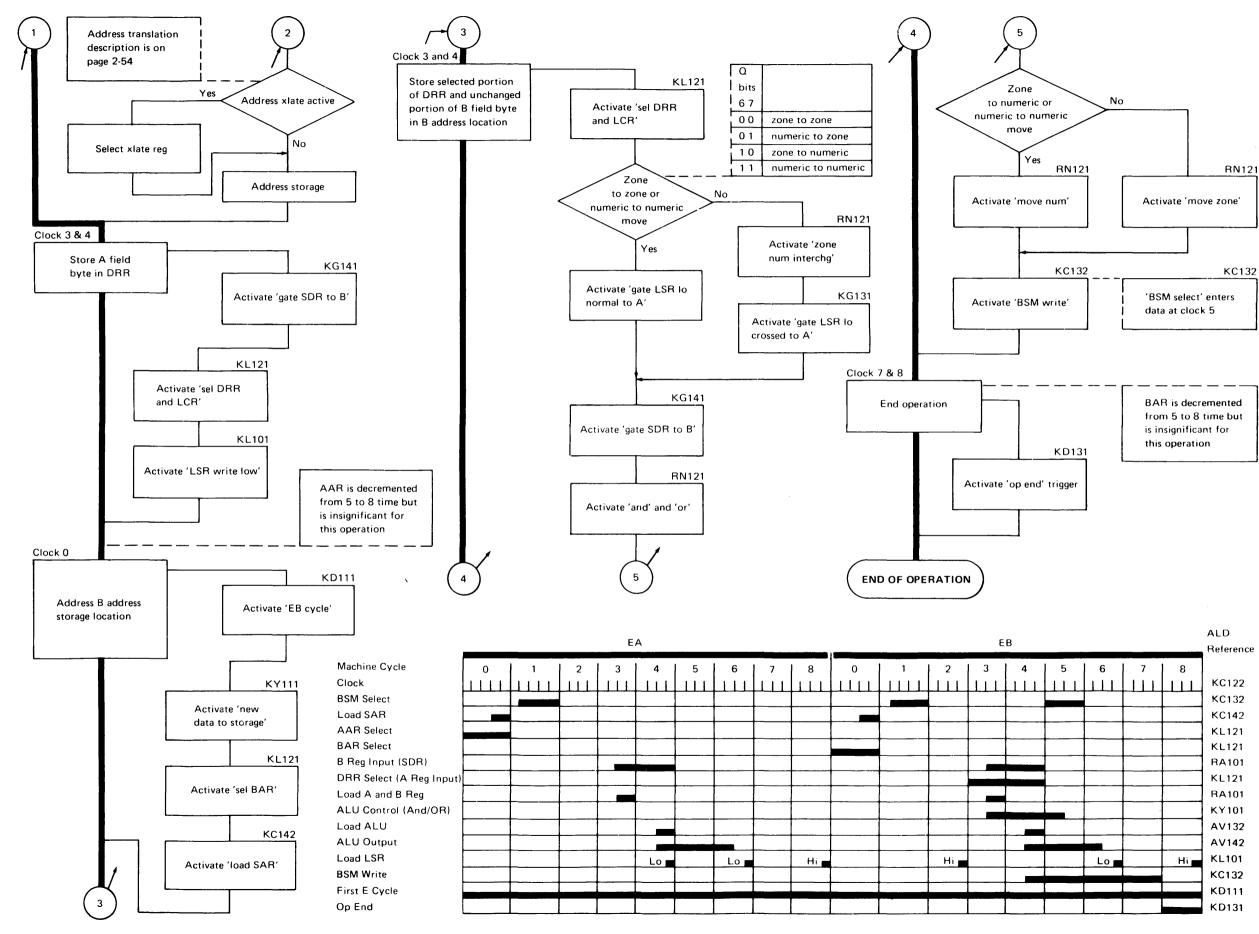

| Move Hex Character – MVX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-34         | Objectives                                     | 6-14                   | BSCA STEP Key (ALD HE160)                                                 | 7-7        | Voltage Adjustment                              |              |

| ONE ADDRESS INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-38         | DISPLAY SAR/MSAR                               | 6-18                   | ADDRESS COMPARE Light (ALD PB121)                                         | 7-7        | End View of +6V Regulator Card                  |              |

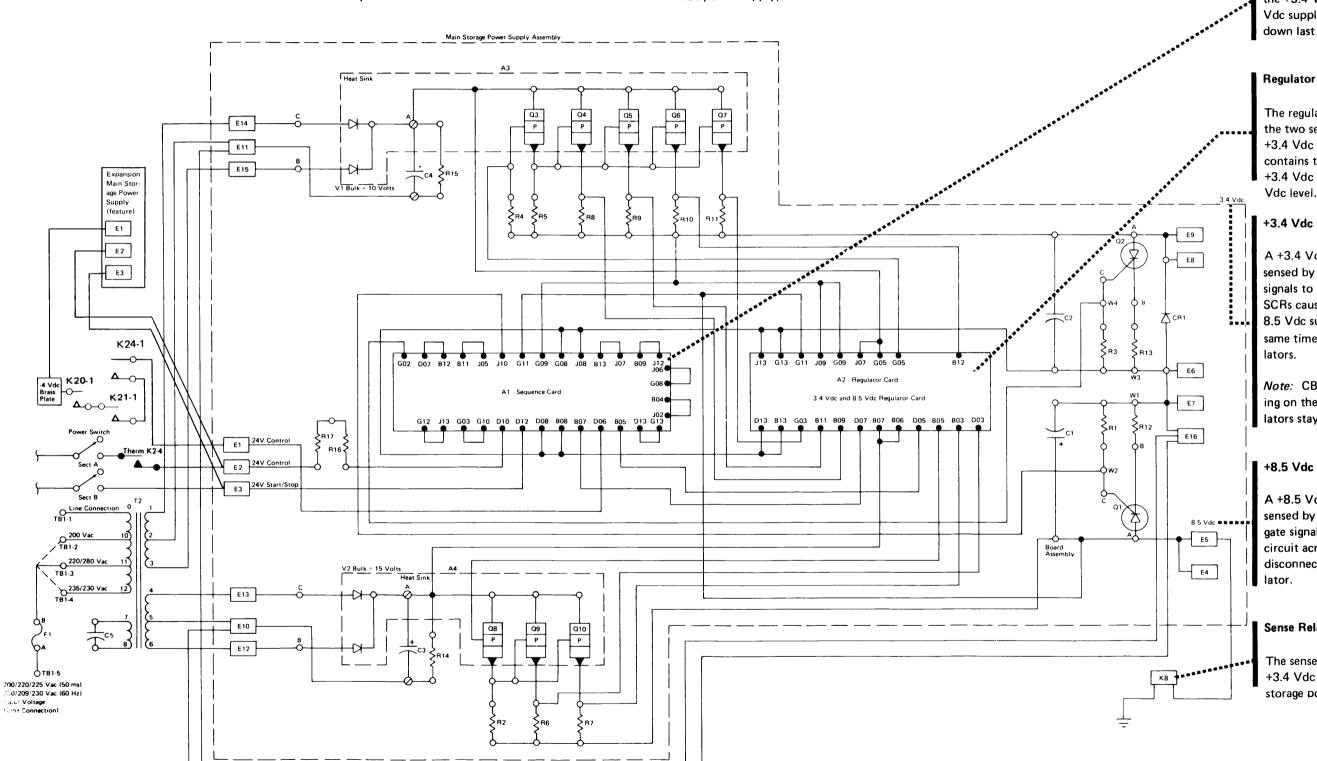

| I-Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-38         |                                                | 0.10                   | I/O CHECK Light (ALD PB121)                                               | 7-7        | MAIN STORAGE POWER SUPPLY                       |              |

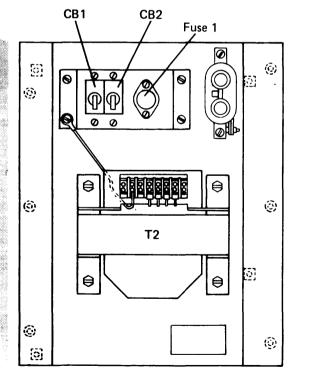

| Move Logical Immediate—MVI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-38         | SYSTEM CONSOLE                                 | 7-1                    | LSR DISPLAY SELECTOR (ALD PC111)                                          | 7-7        | Voltage Adjustments                             |              |

| Compare Logical Immediate—CLI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-38         | OPERATOR CONTROLS                              | 7-1<br>7-1             | CE MODE SELECTOR (ALD PA101)                                              | . ,<br>7-8 | +3.4 Vdc                                        |              |

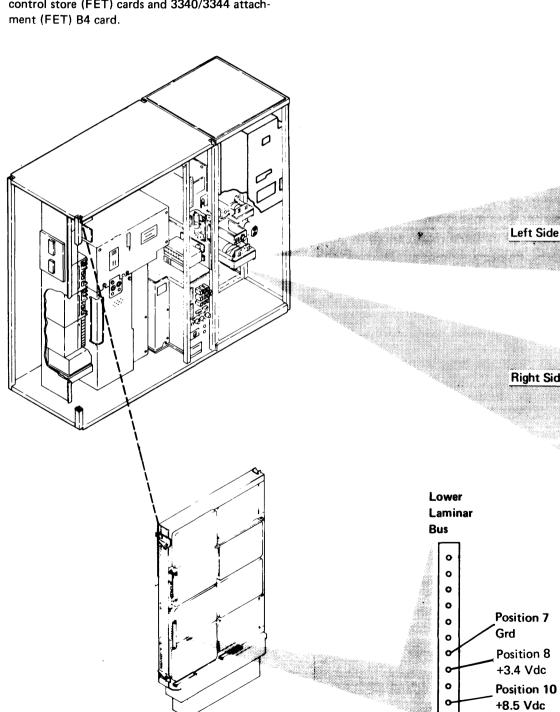

| Move Logical Immediate or Compare Logical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3 30         | The Emergency Power-Off (EPO) Pull Switch (ALD | 7-1                    | TEST                                                                      | 7-8        | +8.5 Vdc                                        |              |

| Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5-39         | YA102)                                         | 7-1                    | PROCESS                                                                   | 7-8<br>7-8 |                                                 | 8-15         |

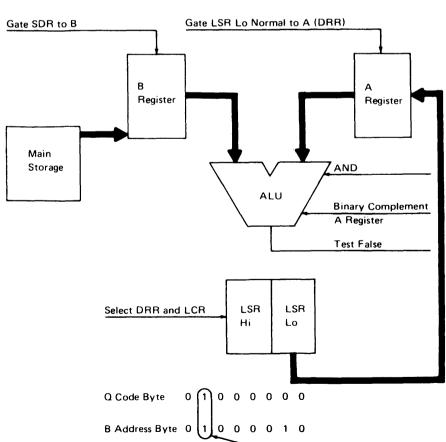

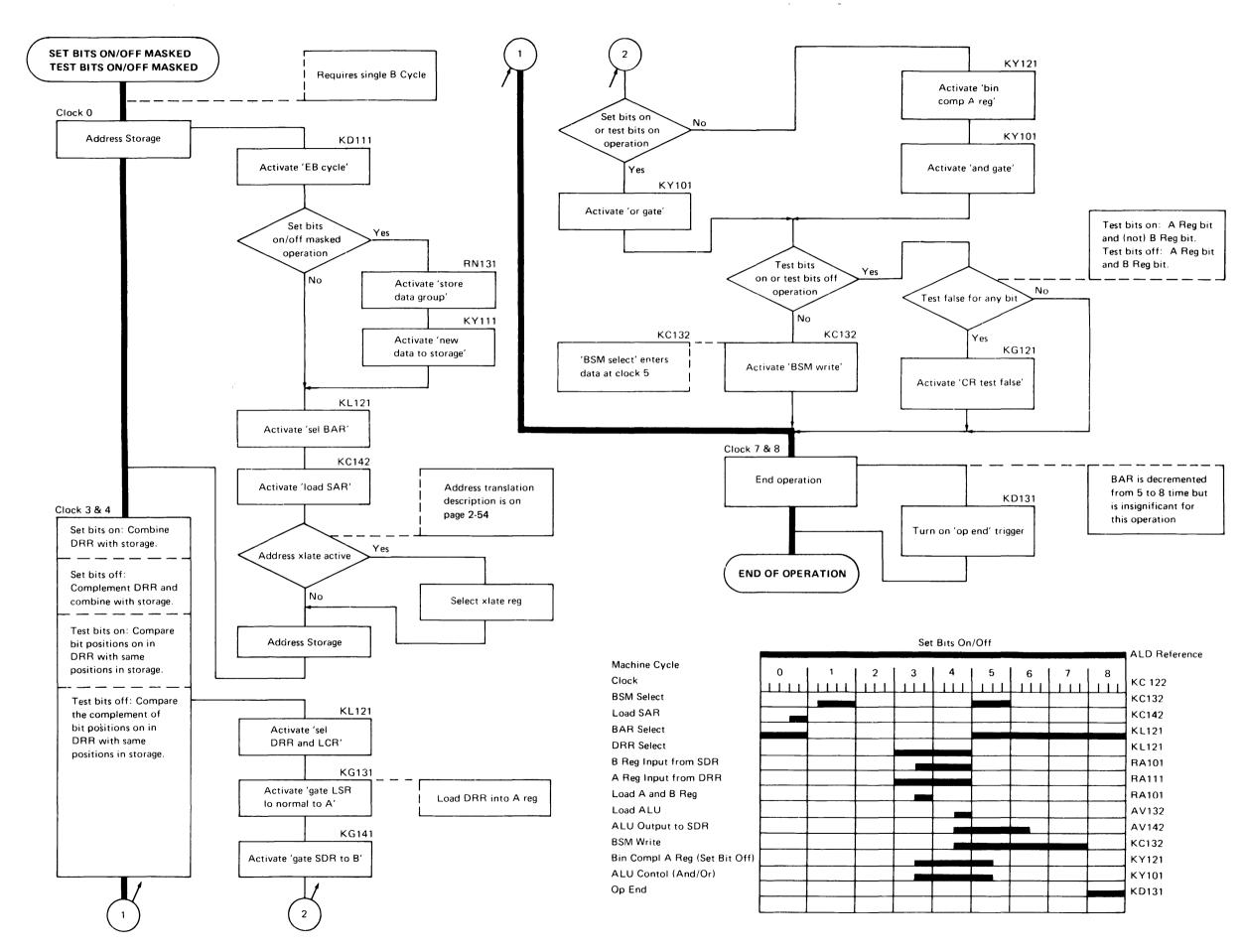

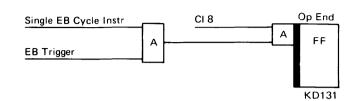

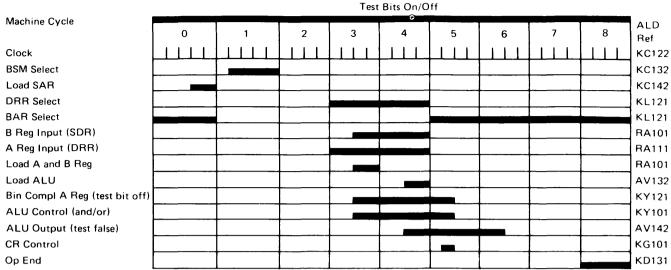

| Set Bits On/Off Masked and Test Bits On/Off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-39         | Usage Meter (ALD YA104)                        | 7-1<br>7-1             | STEP                                                                      | 7-8<br>7-8 | Sequencing                                      |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-42         |                                                | 7-1<br>7-2             | CE Switches                                                               | 7-8<br>7-9 | Overvoltage (OV)/Undervoltage (UV) Portection . | 8-15         |

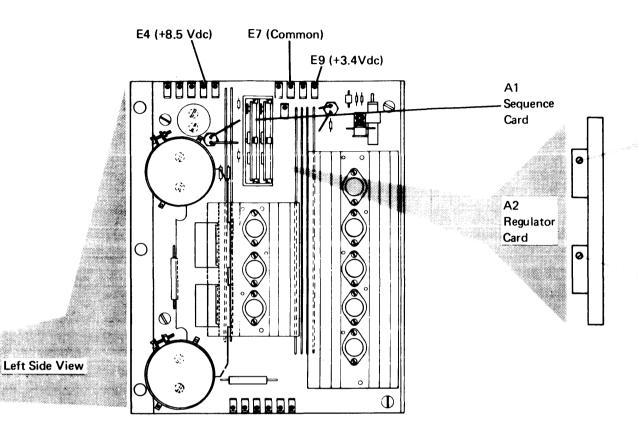

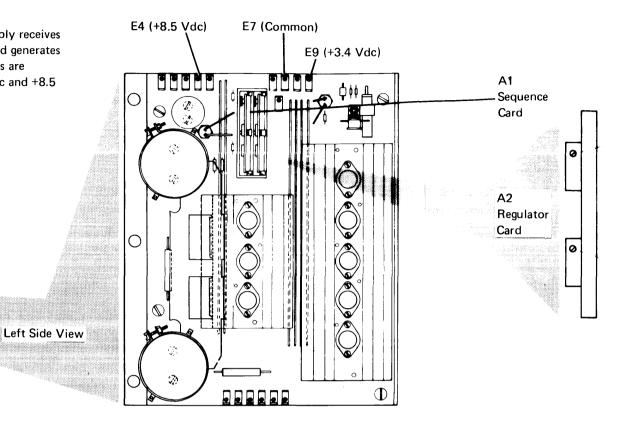

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-42<br>5-42 | File Control Panel                             | 1-2                    |                                                                           | 7-9<br>7-9 | Sequence Card (A1)                              |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-42<br>5-42 |                                                |                        | EXTENDED SAR ADDRESS BITS Switch                                          |            | Regulator Card (A2)                             |              |

| Set Bits Off Masked—SBF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | without 3344 installed (ALD PC101, YD100) .    | 7-2                    | > 64K ADDR BIT Switch (ALD PA101)                                         | 7-9        | +3.4 Vdc                                        |              |

| Test Bits On Masked—TBN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-42         | PROGRAM LOAD SELECTOR Switch                   |                        | SAR/MSAR Display Switch (ALD 'sel MSAR                                    |            | +8.5 Vdc                                        |              |

| Test Bits Off Masked—TBF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-42         | with 3344 installed (ALD PC101, YD100)         | 7-2                    | sw' PA101)                                                                | 7-9        | Sense Relay                                     | 8-15         |

| Set Bits On Masked                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-43         | PROCESSOR CHECK Light (ALD PC111)              | 7-3                    | I/O OVERLAP Switch (ALD PC121)                                            | 7-9        | EXPANSION MAIN STORAGE POWER                    |              |

| Set Bits Off Masked                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-43         | POWER ON/OFF Switch (ALD YA102, PC111) .       | 7-3                    | DISPLAY CHK (Check) BITS Switch (ALD                                      |            | SUPPLY                                          |              |

| Test Bits On Masked                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-43         | START Key (ALD PC111)                          | 7-3                    | PC121)                                                                    | 7-9        | Voltage Adjustments                             | 8-16         |

| Test Bits Off Masked                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-43         | Message Display Unit (ALD PB131)               | 7-3                    | BSCA/LCA LOCAL TEST (ALD HE160)                                           | 7-9        | +3.4 Vdc                                        | 8-16         |

| Store, Load, or Add to Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-46         | I/O ATTENTION Light (ALD PC111)                | 7-3                    | I/O CHECK Switch (ALD PA101)                                              | 7-9        | +8.5 Vdc                                        | 8-16         |

| Store Register-ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-46         | PROGRAM LOAD Key (ALD PC111)                   | 7-3                    | PARITY CHECK Switch (ALD PA101)                                           | 7-9        | Sequencing                                      | 8-17         |

| Load Register-L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-46         | STOP Key/Light (ALD PC111)                     | 7-3                    | STORAGE TEST Switch (ALD PA101)                                           | 7-9        | Overvoltage (OV)/Undervoltage (UV) Protection   | 8-17         |

| Add to Register-A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-46         | CONSOLE DISPLAY                                | 7-4                    | ADDR INCREM (Address Increment) Switch                                    |            | Sequence Card (A1)                              |              |

| Load Address-LA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-50         | INT LEV (Interrupt Level) Light (ALD PB111).   | 7- <b>4</b>            | (ALD PA101)                                                               | 7-9        | Regulator Card (A2)                             |              |