HP 64000 Logic Development System

Emulation with Internal Analysis 68000/68008

#### CERTIFICATION

Hewlett-Packard Company certifies that this product met its published specifications at the time of shipment from the factory. Hewlett-Packard further certifies that its calibration measurements are traceable to the United States National Bureau of Standards, to the extent allowed by the Bureau's calibration facility, and to the calibration facilities of other International Standards Organization members.

#### WARRANTY

This Hewlett-Packard system product is warranted against defects in materials and workmanship for a period of 90 days from date of installation. During the warranty period, HP will, at its option, either repair or replace products which prove to be defective.

Warranty service of this product will be performed at Buyer's facility at no charge within HP service travel areas. Outside HP service travel areas, warranty service will be performed at Buyer's facility only upon HP's prior agreement and Buyer shall pay HP's round trip travel expenses. In all other cases, products must be returned to a service facility designated by HP.

For products returned to HP for warranty service, Buyer shall prepay shipping charges to HP and HP shall pay shipping charges to return the product to Buyer. However, Buyer shall pay all shipping charges, duties, and taxes for products returned to HP from another country.

HP warrants that its software and firmware designated by HP for use with an instrument will execute its programming instructions when properly installed on that instrument. HP does not warrant that the operation of the instrument, or software, or firmware will be uninterrupted or error free.

### **LIMITATION OF WARRANTY**

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by Buyer, Buyer-supplied software or interfacing, unauthorized modification or misuse, operation outside of the environment specifications for the product, or improper site preparation or maintenance.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED. HP SPECIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### **EXCLUSIVE REMEDIES**

THE REMEDIES PROVIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES. HP SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

#### **ASSISTANCE**

Product maintenance agreements and other customer assistance agreements are available for Hewlett-Packard products.

For any assistance, contact your nearest Hewlett-Packard Sales and Service Office.

**BUSINESS REPLY CARD**

FIRST CLASS PERMIT NO. 1303 COLORADO SPRINGS, COLORADO

**POSTAGE WILL BE PAID BY ADDRESSEE**

# HEWLETT-PACKARD Logic Product Support Dept.

Logic Product Support Dept.

Attn: Technical Publications Manager

Centennial Annex - D2

P.O. Box 617

Colorado Springs, Colorado 80901-0617

NO POSTAGE

NECESSARY

IF MAILED

IN THE

UNITED STATES

Your cooperation in completing and returning this form will be greatly appreciated. Thank you.

FOLD HERE

# **READER COMMENT SHEET**

Operating Manual with Service Appendix, Model 64243 Emulation with Internal Analysis 68000/68008 64243-90901, September 1985

Your comments are important to us. Please answer this questionnaire and return it to us. Circle the number that best describes your answer in questions 1 through 7. Thank you.

| 1. The information in this book is completed Doesn't cover enough (what more do you need?) | t <b>e:</b><br>1 | 2               | 3   | 4   | 5 | Covers everything |

|--------------------------------------------------------------------------------------------|------------------|-----------------|-----|-----|---|-------------------|

| 2. The information in this book is accurate Too many errors                                | e:<br>1          | 2               | 3   | 4   | 5 | Exactly right     |

| 3. The information in this book is:  Difficult to find                                     | 1                | 2               | 3   | 4   | 5 | Easy to find      |

| 4. The Index and Table of Contents are u<br>Missing or inadequate                          |                  | <b>ul:</b><br>2 | 3   | 4   | 5 | Helpful           |

| 5. What about the "how-to" procedures a                                                    | nd e             | exa             | mpl | es: |   |                   |

| No help                                                                                    |                  | 2               |     |     | 5 | Very Helpful      |

| Not enough                                                                                 | 1                | 2               | 3   | 4   | 5 | Too many          |

| 6. What about the writing style: Confusing                                                 | 1                | 2               | 3   | 4   | 5 | Clear             |

| 7. What about organization of the book:  Poor order                                        | 1                | 2               | 3   | 4   | 5 | Good order        |

| 8. What about the size of the book:  Too small                                             | 1                | 2               | 3   | 4   | 5 | Too big           |

| Comments:                                                                                  |                  |                 |     |     |   |                   |

|                                                                                            |                  |                 |     |     |   |                   |

| Particular pages with errors?                                                              |                  |                 |     |     |   |                   |

| Job title:Company:                                                                         |                  |                 |     |     |   |                   |

| Address:                                                                                   |                  |                 |     |     |   |                   |

| Nicker 16                                                                                  |                  |                 |     |     |   |                   |

Note: If mailed outside U.S.A., place card in envelope. Use address shown on other side of this card.

**BUSINESS REPLY CARD**

FIRST CLASS PERMIT NO. 1303 COLORADO SPRINGS, COLORADO

**POSTAGE WILL BE PAID BY ADDRESSEE**

# HEWLETT-PACKARD Logic Product Support Dept.

Logic Product Support Dept.

Attn: Technical Publications Manager

Centennial Annex - D2

P.O. Box 617

Colorado Springs, Colorado 80901-0617

NO POSTAGE

NECESSARY

IF MAILED

IN THE

UNITED STATES

Your cooperation in completing and returning this form will be greatly appreciated. Thank you.

FOLD HERE

# **READER COMMENT SHEET**

Operating Manual with Service Appendix, Model 64243 Emulation with Internal Analysis 68000/68008 64243-90901, September 1985

Your comments are important to us. Please answer this questionnaire and return it to us. Circle the number that best describes your answer in questions 1 through 7. Thank you.

| 1. The information in this book is completed Doesn't cover enough (what more do you need?) | t <b>e:</b><br>1 | 2               | 3   | 4   | 5 | Covers everything |

|--------------------------------------------------------------------------------------------|------------------|-----------------|-----|-----|---|-------------------|

| 2. The information in this book is accurate Too many errors                                | e:<br>1          | 2               | 3   | 4   | 5 | Exactly right     |

| 3. The information in this book is:  Difficult to find                                     | 1                | 2               | 3   | 4   | 5 | Easy to find      |

| 4. The Index and Table of Contents are u<br>Missing or inadequate                          |                  | <b>ul:</b><br>2 | 3   | 4   | 5 | Helpful           |

| 5. What about the "how-to" procedures a                                                    | nd e             | exa             | mpl | es: |   |                   |

| No help                                                                                    |                  | 2               |     |     | 5 | Very Helpful      |

| Not enough                                                                                 | 1                | 2               | 3   | 4   | 5 | Too many          |

| 6. What about the writing style: Confusing                                                 | 1                | 2               | 3   | 4   | 5 | Clear             |

| 7. What about organization of the book:  Poor order                                        | 1                | 2               | 3   | 4   | 5 | Good order        |

| 8. What about the size of the book:  Too small                                             | 1                | 2               | 3   | 4   | 5 | Too big           |

| Comments:                                                                                  |                  |                 |     |     |   |                   |

|                                                                                            |                  |                 |     |     |   |                   |

| Particular pages with errors?                                                              |                  |                 |     |     |   |                   |

| Job title:Company:                                                                         |                  |                 |     |     |   |                   |

| Address:                                                                                   |                  |                 |     |     |   |                   |

| Nicker 16                                                                                  |                  |                 |     |     |   |                   |

Note: If mailed outside U.S.A., place card in envelope. Use address shown on other side of this card.

#### SAFETY SUMMARY

The following general safety precautions must be observed during all phases of operation, service, and repair of this instrument. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of the instrument. Hewlett-Packard Company assumes no liability for the customer's failure to comply with these requirements.

#### **GROUND THE INSTRUMENT.**

To minimize shock hazard, the instrument chassis and cabinet must be connected to an electrical ground. The instrument is equipped with a three-conductor ac power cable. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet. The power jack and mating plug of the power cable meet International Electrotechnical Commission (IEC) safety standards.

#### DO NOT OPERATE IN AN EXPLOSIVE ATMOSPHERE.

Do not operate the instrument in the presence of flammable gases or fumes. Operation of any electrical instrument in such an environment constitutes a definite safety hazard.

#### KEEP AWAY FROM LIVE CIRCUITS.

Operating personnel must not remove instrument covers. Component replacement and internal adjustments must be made by qualified maintenance personnel. Do not replace components with the power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

#### DO NOT SERVICE OR ADJUST ALONE.

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

#### DO NOT SUBSTITUTE PARTS OR MODIFY INSTRUMENT.

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification of the instrument. Return the instrument to a Hewlett-Packard Sales and Service Office for service and repair to ensure that safety features are maintained.

#### DANGEROUS PROCEDURE WARNINGS.

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed.

WARNING

Dangerous voltages, capable of causing death, are present in this instrument. Use extreme caution when handling, testing, and adjusting.

#### **SAFETY SYMBOLS**

## General Definitions of Safety Symbols Used on Equipment or in Manuals.

Instruction manual symbol: the product is marked with this symbol when it is necessary for the user to refer to the instruction manual in order to protect against damage to the instrument.

Indicates dangerous voltage (terminals fed from the interior by voltage exceeding 1000 volts must be so marked).

OR

Protective conductor terminal. For protection against electrical shock in case of a fault. Used with field wiring terminals to indicate the terminal which must be connected to ground before operating equipment.

Low-noise or noiseless, clean ground (earth) terminal. Used for a signal common, as well as providing protection against electrical shock in case of a fault. A terminal marked with this symbol must be connected to ground in the manner described in the installation (operating) manual, and before operating the equipment.

Frame or chassis terminal. A connection to the frame (chassis) of the equipment which normally includes all exposed metal structures.

Alternating current (power line).

Direct current (power line).

Alternating or direct current (power line).

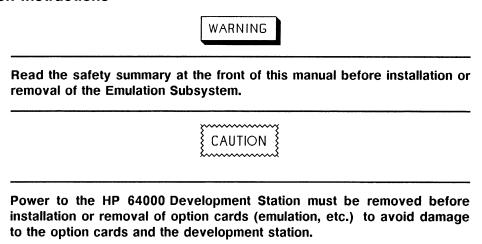

WARNING

The WARNING sign denotes a hazard. It calls attention to a procedure, practice, condition or the like, which, if not correctly performed, could result in injury or death to personnel.

The CAUTION sign denotes a hazard. It calls attention to an operating procedure, practice, condition or the like, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the product.

NOTE:

The NOTE sign denotes important information. It calls attention to procedure, practice, condition or the like, which is essential to highlight.

## **OPERATING MANUAL WITH SERVICE APPENDIX**

# EMULATION WITH INTERNAL ANALYSIS 68000/68008

© COPYRIGHT HEWLETT-PACKARD COMPANY 1985 LOGIC SYSTEMS DIVISION COLORADO SPRINGS, COLORADO, U. S. A.

**ALL RIGHTS RESERVED**

Manual Part No. 64243-90901

E1085

PRINTED: October 1985

#### PRINTING HISTORY

Each new edition of this manual incorporates all material updated since the previous edition. Manual change sheets are issued between editions, allowing you to correct or insert information in the current edition.

The print date changes only when each new edition is published. Minor corrections or additions may be made as the manual is reprinted between editions. Vertical bars in a page margin indicates the location of reprint corrections.

First Edition .......... August, 1985 (64243-90901 E0885)

Second Edition ........ October, 1985 (64243-90901 E1085)

#### **SOFTWARE VERSION NUMBER**

Your HP 64000 software is identified with a version number in the form YY.XX. The version number is printed on a label attached to the software media or media envelope. This manual applies to the following:

Model HP 64243A Version 1.XX Model HP 64244A Version 1.XX

Within the software version number, the digit to the left of the decimal point indicates the product feature set. This manual supports all software versions identified with this same digit.

The digits to the right of the decimal point indicate feature subsets. These feature subsets normally have no affect on the manual. However, if you subscribe to the "Software Material Subscription" (SMS), these subset items are covered in the "Software Response Bulletin" (SRB).

### **REPAIR NUMBERS**

This manual applies to components of the HP 64243 and HP 64244 Emulation Subsystem with the following repair number prefixes:

| Model Number | Current Repair Prefix | Other Repair Numbers |

|--------------|-----------------------|----------------------|

| HP 64243     | 2626A                 | N/A                  |

| HP 64244     | 2626A                 | N/A                  |

# **TABLE OF CONTENTS**

| USING | THIS | MAN | UAL |

|-------|------|-----|-----|

|-------|------|-----|-----|

|      | GENERAL  MANUAL CONTENTS GUIDE                         | χvi |

|------|--------------------------------------------------------|-----|

| Cha  | pter 1: GENERAL INFORMATION                            |     |

|      | OVERVIEW                                               |     |

|      | SAFETY CONSIDERATIONS                                  |     |

|      | GENERAL                                                |     |

|      | WHAT IS AN EMULATION SYSTEM?                           |     |

|      | Physical Description                                   |     |

|      | Emulation Subsystem Hardware Emulation System Software |     |

|      | Emulation System Manual                                |     |

|      | Functional Description                                 |     |

|      | WHAT DOES THE EMULATOR ALLOW YOU TO DO?                |     |

|      | How Are These Tasks Implemented?                       |     |

|      | WILL THE EMULATOR SYSTEM RUN INTERACTIVELY             |     |

|      | WITH OTHER HP 64000 SYSTEM MODULES?                    | 1-7 |

|      | WHAT EFFECT WILL THE EMULATOR HAVE ON YOUR PROGRAM?    |     |

|      | WHAT IS HAPPENING WHILE YOUR PROGRAM IS RUNNING?       | 1-8 |

|      | During Normal Flow of the Program                      | 1-8 |

|      | During Emulation Monitor Program Control               | 1-9 |

|      | WHAT DOES THE EMULATOR DO                              |     |

|      | TO YOUR MICROPROCESSOR SYSTEM?                         |     |

|      | Functional Transparency                                |     |

|      | Timing Transparency                                    |     |

|      | Electrical Transparency                                | -10 |

|      | SOFTWARE MATERIALS SUBSCRIPTION                        |     |

|      | Software Updates                                       |     |

|      | Reference Manual Updates                               |     |

|      | Software Problem Reporting                             |     |

|      | Software Release Bulletins                             |     |

|      | Software Status Bulletins                              |     |

|      | General User Information                               |     |

| Chap | oter 2: INSTALLING HARDWARE AND SOFTWARE               |     |

|      | OVERVIEW                                               | 2-1 |

|      | INTRODUCTION                                           |     |

|      | PRE-INSTALLATION INSPECTION                            | 2-4 |

|     | Required Equipment, Recommended Additional Equipment, |       |

|-----|-------------------------------------------------------|-------|

|     | and Additional Optional Equipment                     | . 2-4 |

|     | INSTALLING EMULATION SYSTEM HARDWARE                  |       |

|     | INTO AN HP 64100 LOGIC DEVELOPMENT STATION            | . 2-6 |

|     | Configuration of the Boards in the Station            |       |

|     | Configuration of the Memory Boards                    |       |

|     | Installation Instructions                             |       |

|     | INSTALLING EMULATION SYSTEM HARDWARE                  | \     |

|     | INTO AN HP 64110 LOGIC DEVELOPMENT STATION            | 2 14  |

|     | Configuration of the Boards in the Station            |       |

|     |                                                       |       |

|     | Configuration of the Memory Boards                    |       |

|     | Installation Instructions                             | 2-1   |

|     | Installing the Emulation Probe Cable                  |       |

|     | Connector into the Target System Socket               |       |

|     | Target System Microprocessor Connector Compatibility  |       |

|     | Installing Into a DIP Socket (DIP)                    |       |

|     | Installing into a Pin Grid Array (PGA) Socket         |       |

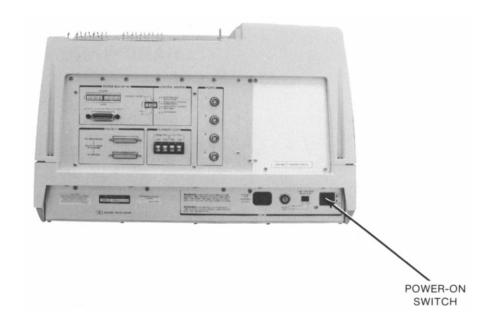

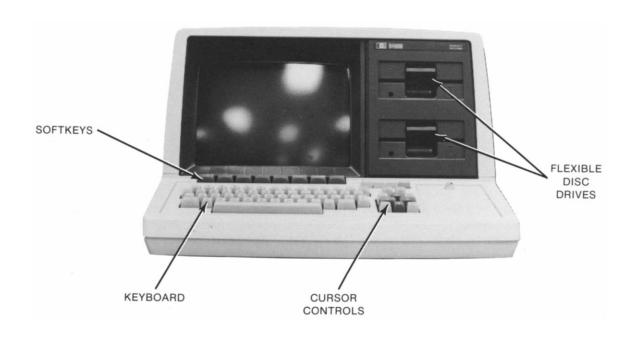

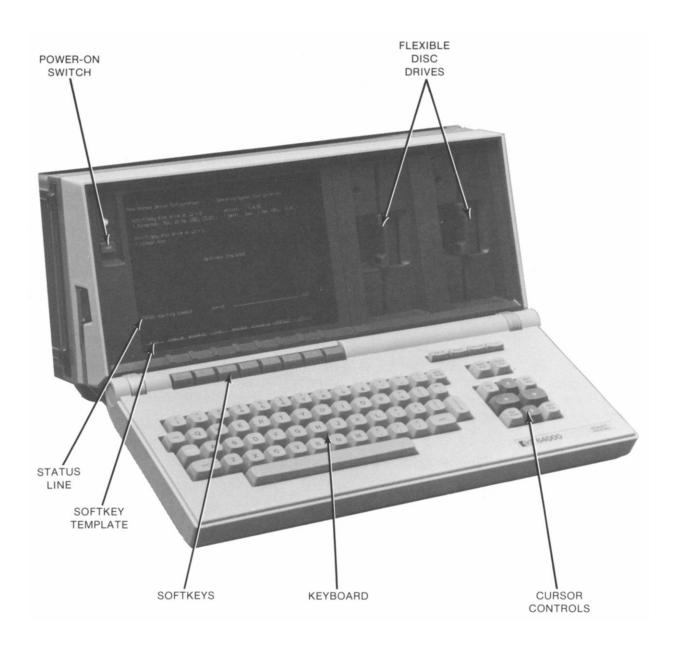

|     | TURNING ON THE DEVELOPMENT STATION                    |       |

|     | LOADING EMULATION SYSTEM SOFTWARE                     |       |

|     | Backing Up Your Software                              | 2-24  |

|     | Loading Software in Clustered Stations Configuration  | 2-24  |

|     | Configuring A Flexible Disc For Stand-Alone Operation | 2-25  |

|     | FORMAT A NEW FLEXIBLE DISC                            | 2-25  |

|     | DEFINE DISC SOFTWARE CONFIGURATIONS                   | 2-26  |

|     | COPY THE MODULES ONTO NEW DISCS                       |       |

|     | REMOVING EMULATION SOFTWARE                           |       |

|     | FROM THE OPERATING SYSTEM                             | 2-29  |

|     | PERFORMING OPERATION VERIFICATION                     |       |

|     | OPERATING THE EMULATION SYSTEM                        |       |

|     | IN STAND-ALONE CONFIGURATION                          | 2 30  |

|     | REMOVING THE EMULATOR CONTROL BOARD                   |       |

|     | REPACKAGING FOR SHIPMENT                              |       |

|     |                                                       |       |

|     | Other Packaging Materials                             | 2-02  |

| Cha | pter 3: GETTING STARTED                               |       |

|     | OVERVIEW                                              | 3_1   |

|     | GENERAL                                               |       |

|     | INTRODUCTION                                          |       |

|     | UNDERSTANDING THE EXAMPLES                            |       |

|     | ASSIGNING YOUR USERID                                 |       |

|     | SINGLE-MODULE SYSTEMS -VS- MULTI-MODULE SYSTEMS       | 0-2   |

|     |                                                       |       |

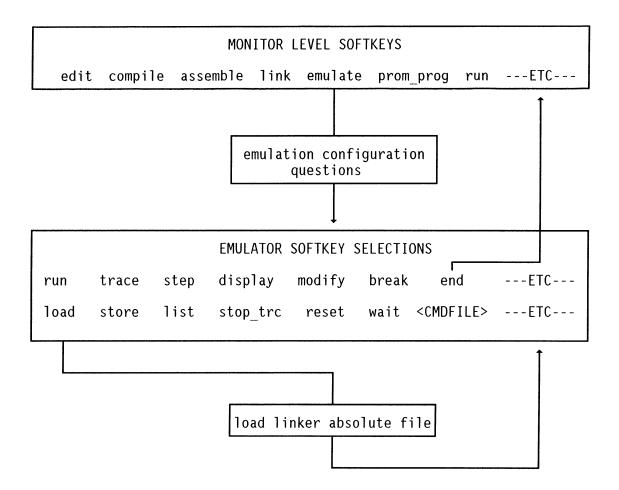

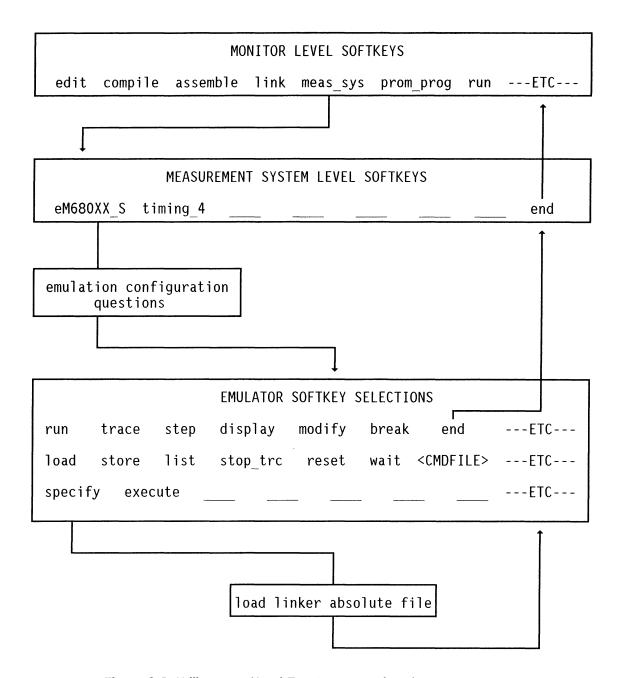

|     | SOFTKEYS                                              |       |

|     | Monitor Level Softkeys                                |       |

|     | Fmulation System Softkeys                             | 3-4   |

|     | YOUR PROGRAM MODULE                                             |                          |

|-----|-----------------------------------------------------------------|--------------------------|

|     | FILES YOU WILL CREATE                                           |                          |

|     | ORGANIZING YOUR PROGRAM MODULES                                 | 3-6                      |

|     | Copying the 680XX Programs to Your Userid                       |                          |

|     | Looking at Your Sample Program                                  | 3-9                      |

|     | INITIATING A SYSTEM "LOG" COMMAND FILE                          | 3-9                      |

|     | ASSEMBLING AND LINKING THE PROGRAM MODULES                      |                          |

|     | Assembling Modules                                              | 3-9                      |

|     | Linking Modules                                                 |                          |

|     | GAINING ACCESS TO THE EMULATION SUBSYSTEM                       |                          |

|     | ANSWERING THE EMULATION CONFIGURATION QUESTIONS                 |                          |

|     | LOADING EMULATION MEMORY                                        |                          |

|     | ENDING THE "LOG" COMMAND FILE                                   |                          |

|     | BUILDING SYSTEM COMMAND FILES                                   |                          |

|     | Logging Commands to a Command File                              |                          |

|     | Typing The Commands Into a Command File                         |                          |

|     | Typing a System Command File                                    |                          |

|     | Typing an Emulation Command File                                |                          |

|     | USING THE EMULATOR                                              |                          |

|     | To See Real-Time Tracing of Processor Activity                  |                          |

|     | To Break into Emulation Monitor and See Registers               |                          |

|     | Stepping                                                        |                          |

|     | USING THE COMMAND FILES                                         | 3-23                     |

| Cha | overview                                                        | 4_1                      |

|     | GENERAL                                                         |                          |

|     | INTRODUCTION                                                    |                          |

|     | USING THE ASSEMBLER                                             |                          |

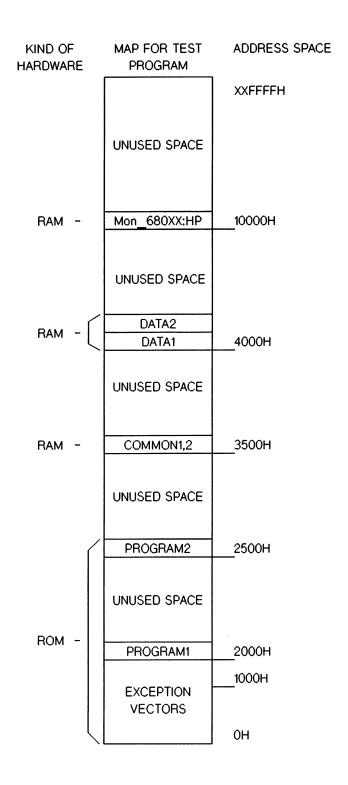

|     | The Relationship of Linker Mapping and Emulation Memory Mapping | · · · · · · -            |

|     | USING THE 680XX EMULATION MONITOR PROGRAM                       | 4-4                      |

|     | Emulation Monitor Memory Requirements (68000)                   | 4-4                      |

|     | Emulation Monitor Memory Requirements (68008)                   |                          |

|     | WHY SO MANY FILES HAVE THE SAME NAME                            |                          |

|     | WHERE TO LOCATE THE MONITOR                                     | 4-12                     |

|     |                                                                 |                          |

| Cha | pter 5: ANSWERING EMULATION CONFIGURATION QUESTIONS             |                          |

|     | GENERAL                                                         | 5-1                      |

|     | INTRODUCTION                                                    | 5-1                      |

|     | ADDRESS CONVENTIONS                                             |                          |

|     | ACCESSING THE CONFIGURATION QUESTIONS                           | 5-2                      |

|     |                                                                 | 0-2                      |

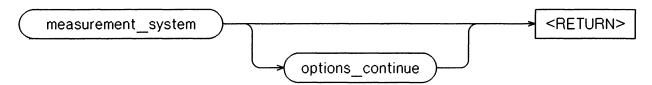

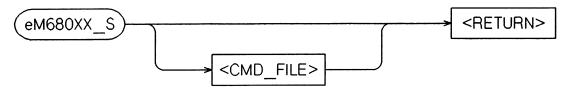

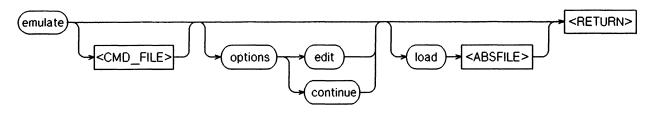

|     | Measurement System/Emulate Command Syntax                       | 5-3                      |

|     | Configuring/Reconfiguring the Emulation Pod                     | 5-3                      |

|     | Configuring/Reconfiguring the Emulation Pod                     | 5-3<br>5-3               |

|     | Configuring/Reconfiguring the Emulation Pod                     | 5-3<br>5-3<br>5-7        |

|     | Configuring/Reconfiguring the Emulation Pod                     | 5-3<br>5-3<br>5-7<br>5-7 |

|      | Selecting Real-Time/Nonreal-Time Runs             |      |

|------|---------------------------------------------------|------|

|      | Selecting/Modifying a Memory Configuration        | 5-9  |

|      | MODIFYING A CURRENT CONFIGURATION                 |      |

|      | SELECTING THE MEMORY CONFIGURATION                |      |

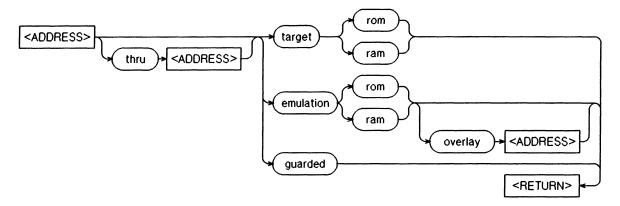

|      | Mapping Memory                                    |      |

|      | Memory Map Definition                             |      |

|      | Emulation Monitor Memory Requirements             | 5-13 |

|      | Display Organization                              | 5-13 |

|      | Entering Memory Blocks                            | 5-15 |

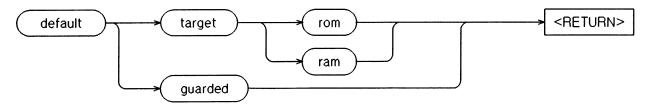

|      | Setting the Default                               | 5-18 |

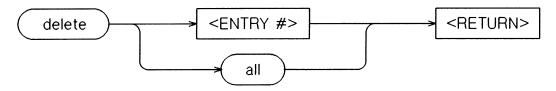

|      | Deleting Blocks                                   |      |

|      | Ending the Mapping Session                        | 5-19 |

|      | Configuring Simulated I/O                         |      |

|      | Configuring the Emulator Pod                      |      |

|      | Interlock emulation memory DTACK with user DTACK? |      |

|      | Enable Bus Error on emulation memory accesses?    |      |

|      | Enable emulator processor interrupts ?            |      |

|      | Enable emulator DMA transfers ?                   |      |

|      | Enable DMA transfers to emulation memory?         |      |

|      | Enable tracing of DMA memory transfers?           | 5-22 |

|      | Enable tracing of DMA tags?                       | 5-23 |

|      | Trap number for software break?                   |      |

|      | Enable emulator use of INT7?                      |      |

|      | Enable Interrupt level 7 sharing ?                |      |

|      | Enable tristate delay on halts?                   | 5-23 |

|      | Configuring for Interactive Measurements          | 5-24 |

|      | Naming Your Emulation Configuration Command File  |      |

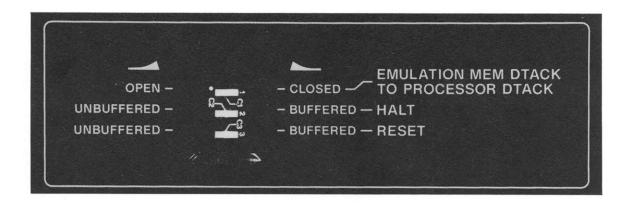

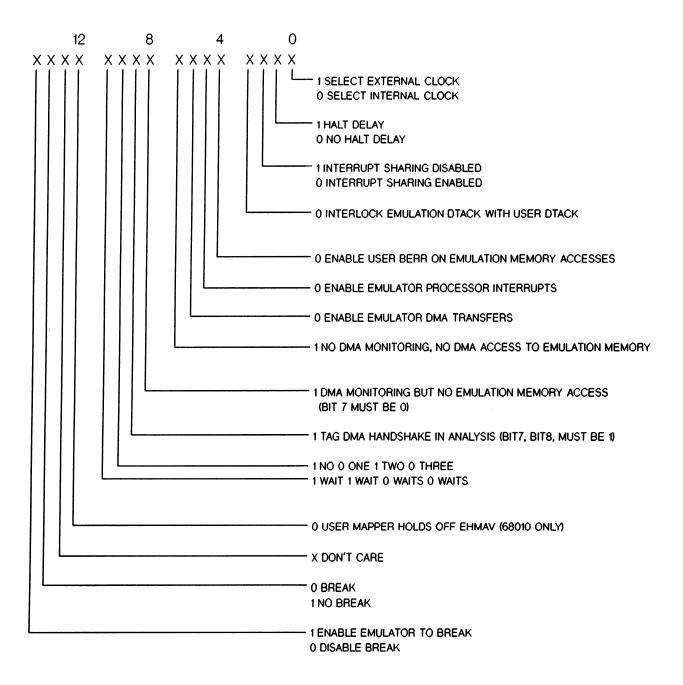

|      | CONFIGURATION SWITCHES                            | 5-27 |

|      |                                                   |      |

|      |                                                   |      |

| Chap | oter 6: USING THE EMULATOREXAMPLES                |      |

|      | OVERVIEW                                          |      |

|      | OVERVIEW                                          |      |

|      | INTRODUCTION                                      |      |

|      | EXECUTION                                         |      |

|      | RUNNING THE PROGRAM                               |      |

|      | PROCESSOR RESET                                   |      |

|      | PROCESSOR STATUS MESSAGES                         |      |

|      | ANALYSIS STATUS INFORMATION                       |      |

|      | Using the HP 64302A Internal Analysis Board       | o-3  |

|      |                                                   |      |

|      | OUT-OF-CIRCUIT EMULATION                          | 0-4  |

|      |                                                   |      |

|      | IN-CIRCUIT EMULATION                              | 6-5  |

|      | Emulation Memory and Target System Memory         | 6-5  |

|      | Guidelines for In-Circuit Emulation               | 6-5  |

|              | BEGINNING AND ENDING EMULATION                       |       |

|--------------|------------------------------------------------------|-------|

|              | EMULATION EXAMPLES                                   | . 6-7 |

|              | Demonstration Configuration                          | . 6-7 |

|              | To Display Registers:                                | . 6-9 |

|              | To Step Registers <#STEPS> From <address>:</address> | 6-10  |

|              | To Display Memory - Blocked Byte:                    |       |

|              | To Display Memory - Mnemonic:                        | 6-12  |

|              | To Display Memory - Absolute Byte:                   |       |

|              | To Display Memory - Real:                            |       |

|              | To Display Memory Blocked Byte Offset:               | 6-15  |

|              | To Modify and Display Memory - Byte:                 |       |

|              | USING ANALYSIS COMMANDS                              |       |

|              | ANALYSIS EXAMPLES                                    |       |

|              | To See Real-time Tracing of Processor Operations     |       |

|              | To Trace After <address>:</address>                  |       |

|              | To Display Trace Absolute:                           |       |

|              | To Display Trace Status Binary:                      |       |

|              | To Display Trace Status Mnemonic:                    | 6 00  |

|              | To display Trace Status Milemonic.                   | 0-23  |

|              |                                                      |       |

| <b>3</b> h a | THE TO COMMENTAND CLIEBERS DV AND CVALTAY            |       |

| JIId         | pter 7: COMMAND SUMMARY AND SYNTAX                   |       |

|              | INTRODUCTION                                         | 7 1   |

|              | OPERATIONAL COMMANDS                                 |       |

|              | Command Line Comment Delimiter                       |       |

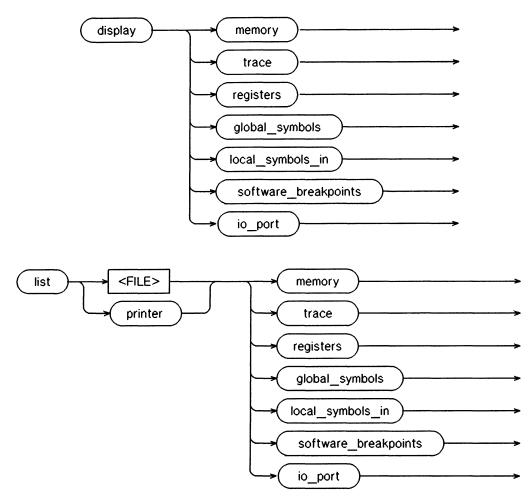

|              | DISPLAY AND LIST COMMANDS                            |       |

|              |                                                      |       |

|              | Display and List Command Options                     |       |

|              | Memory Data                                          |       |

|              | Register Contents                                    |       |

|              | Trace Information                                    |       |

|              | Global and Local Symbols                             |       |

|              | Software Breakpoint Table                            | . 7-6 |

|              | ANALYSIS AND INTERACTIVE COMMANDS                    |       |

|              | USING ANALYSIS COMMANDS                              |       |

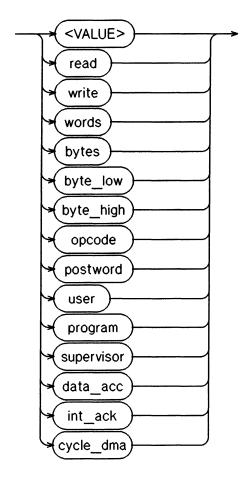

|              | Data Qualification                                   |       |

|              | ANALYSIS MODES                                       |       |

|              | BUS_CYCLE_DATA MODE                                  |       |

|              | EXECUTION_DATA MODE                                  |       |

|              | BREAK COMMAND SYNTAX                                 | 7-16  |

|              | DISPLAY/LIST COMMAND SYNTAX                          |       |

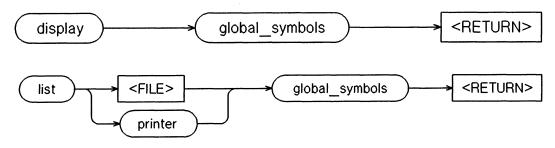

|              | DISPLAY/LIST GLOBAL_SYMBOLS SYNTAX                   | 7-19  |

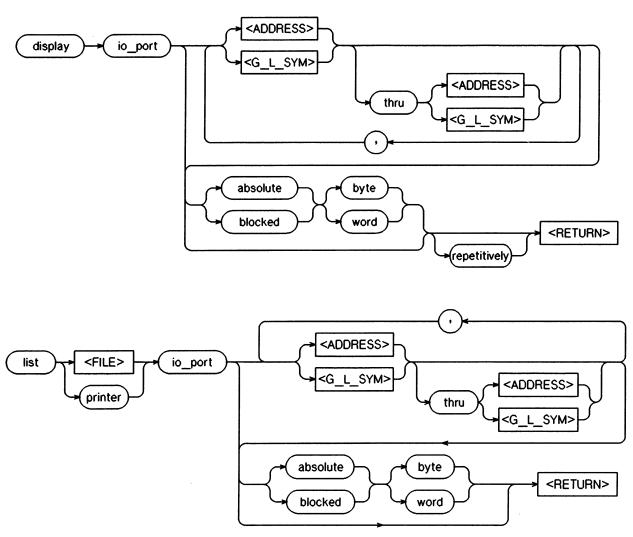

|              | DISPLAY/LIST IO PORT SYNTAX                          |       |

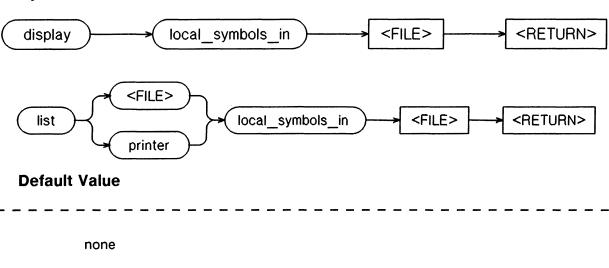

|              | DISPLAY/LIST LOC SYM SYNTAX                          |       |

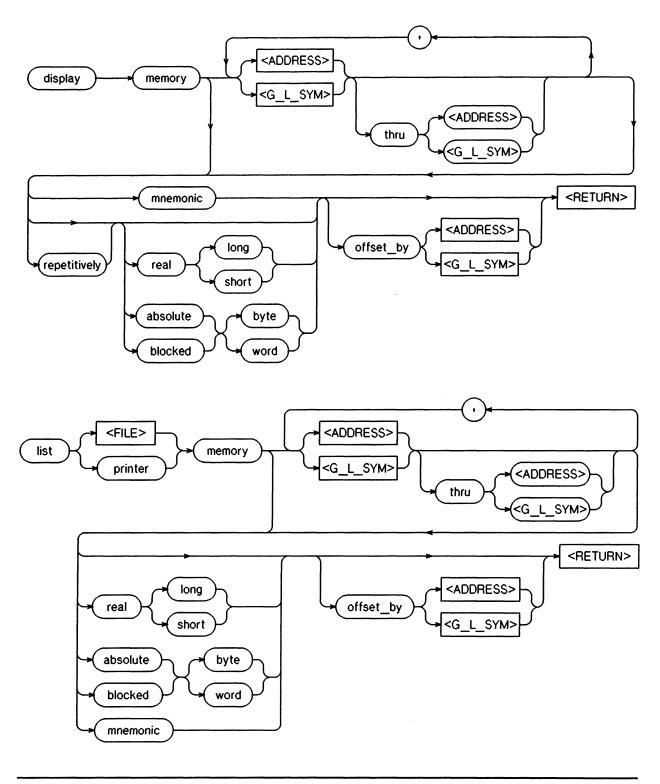

|              | DISPLAY/LIST MEMORY SYNTAX                           |       |

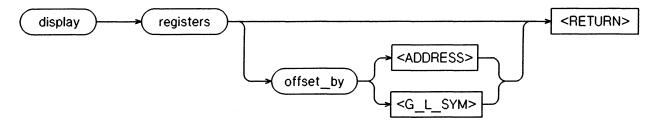

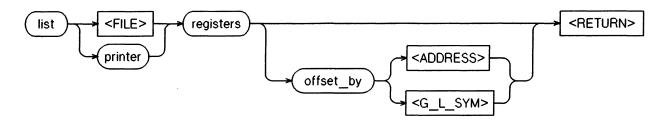

|              | DISPLAY/LIST REGISTERS SYNTAX                        |       |

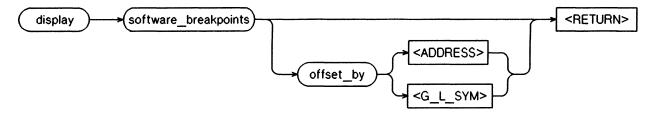

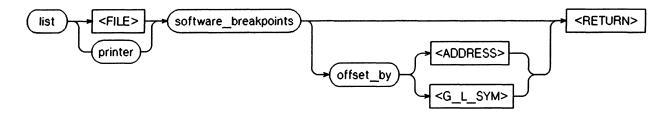

|              | DISPLAY/LIST SOFTWARE BREAKPOINTS SYNTAX             |       |

|              | DISPLAY/LIST TRACE SYNTAX                            |       |

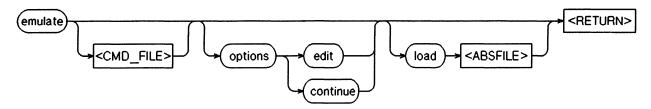

|              | EMULATE SYNTAX                                       |       |

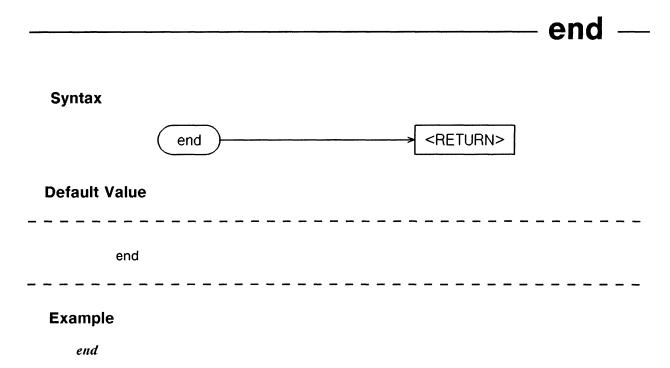

|              | END SYNTAX                                           |       |

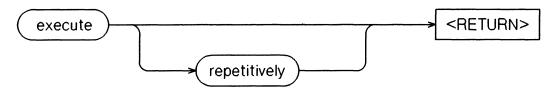

|              | EXECUTE SYNTAX                                       |       |

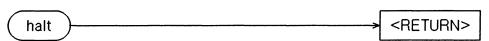

|              | HALT SYNTAX                                          |       |

|              | MALI SINIAA                                          | 7-35  |

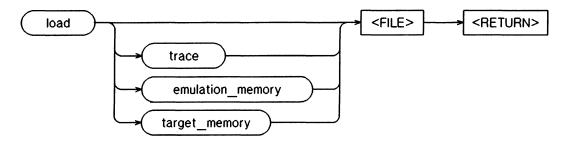

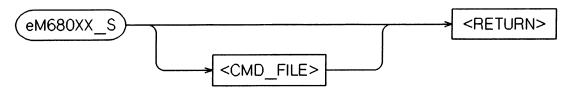

| LOAD SYNTAX                                          | 7-36 |

|------------------------------------------------------|------|

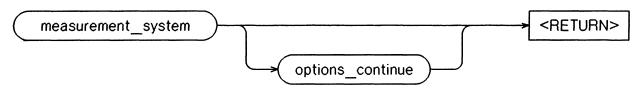

| MEASUREMENT SYSTEM SYNTAX                            |      |

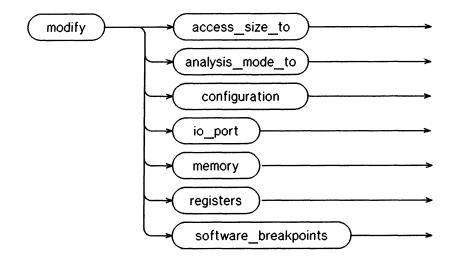

| MODIFY SYNTAX                                        |      |

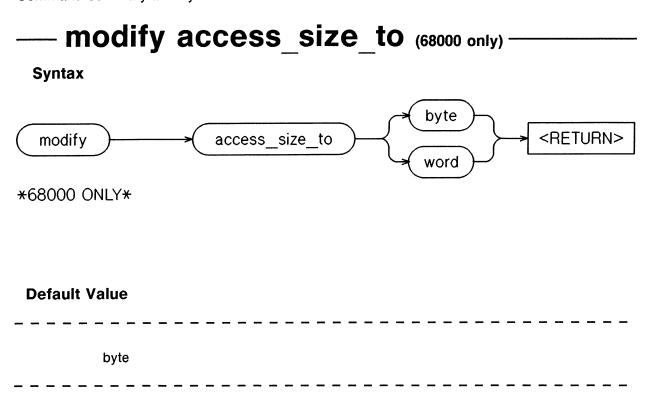

| MODIFY ACCESS SIZE TO SYNTAX                         |      |

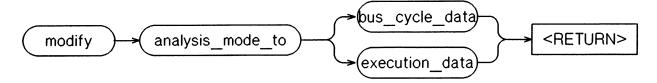

| MODIFY ANALYSIS MODE TO                              |      |

| MODIFY CONFIGURATION SYNTAX                          |      |

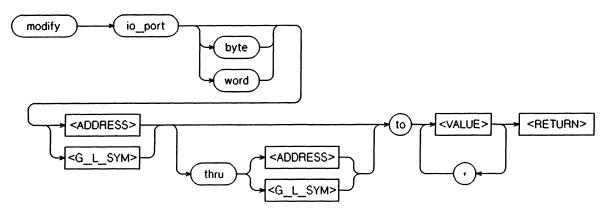

| MODIFY IO PORT SYNTAX                                |      |

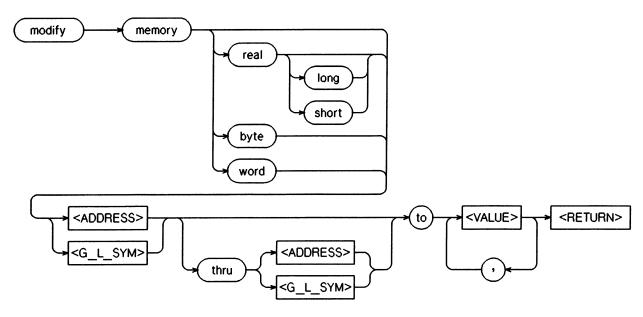

| MODIFY MEMORY SYNTAX                                 |      |

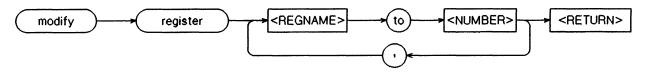

| MODIFY REGISTER SYNTAX                               |      |

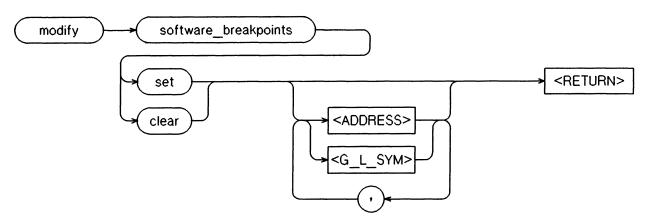

| MODIFY SOFTWARE BREAKPOINTS SYNTAX                   |      |

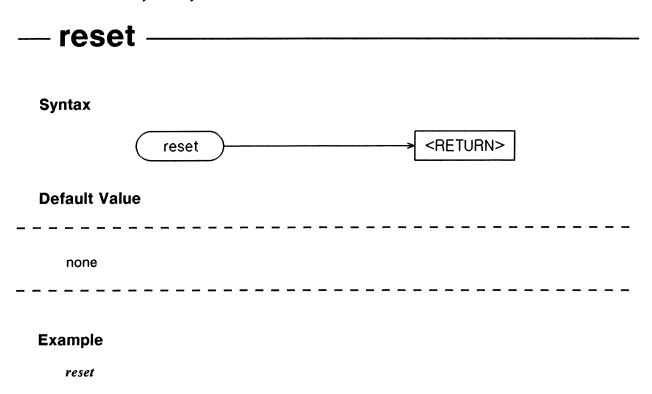

| RESET SYNTAX                                         |      |

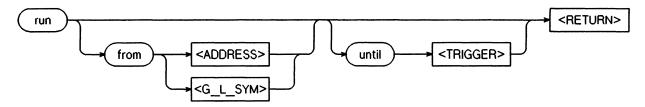

| RUN SYNTAX                                           |      |

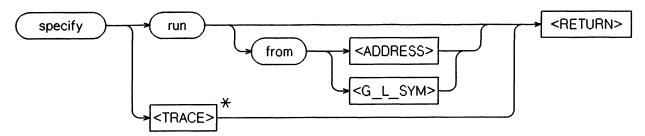

| SPECIFY SYNTAX                                       |      |

| STEP SYNTAX                                          |      |

| STOP TRACE SYNTAX                                    |      |

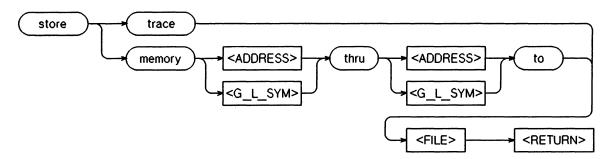

| STORE SYNTAX                                         |      |

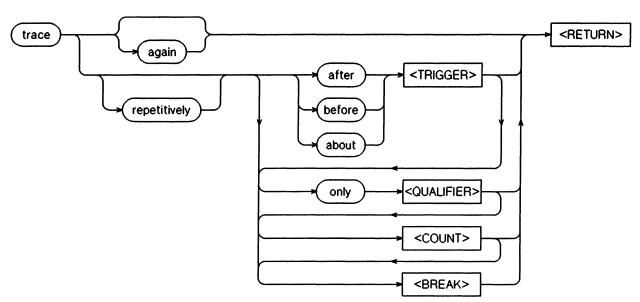

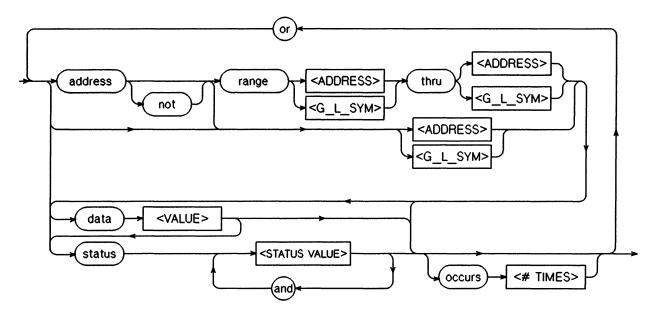

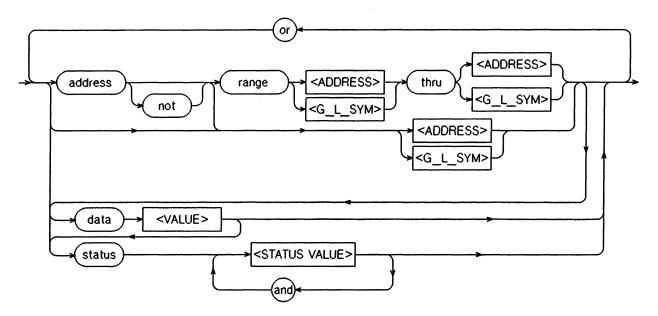

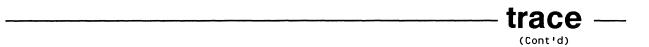

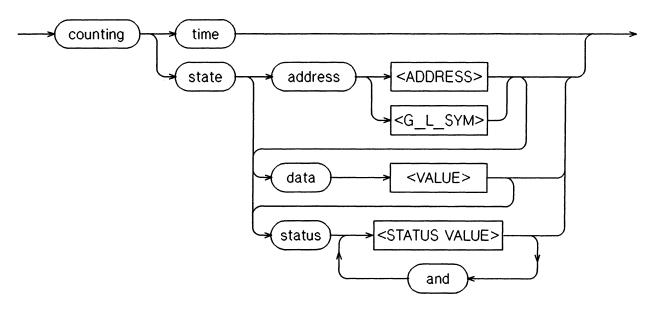

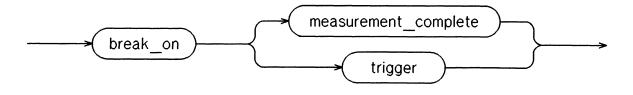

| TRACE SYNTAX                                         |      |

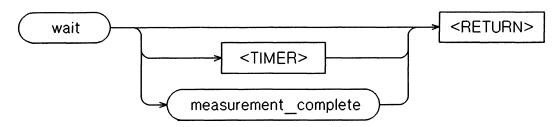

| WAIT SYNTAX                                          |      |

|                                                      |      |

| Chapter 8: THE EMULATION MONITOR PROGRAM             |      |

| Chapter 6. The Emocation monitor incomain            |      |

| OVERVIEW                                             | 8-1  |

| GENERAL                                              | 8-1  |

| INTRODUCTION                                         | 8-1  |

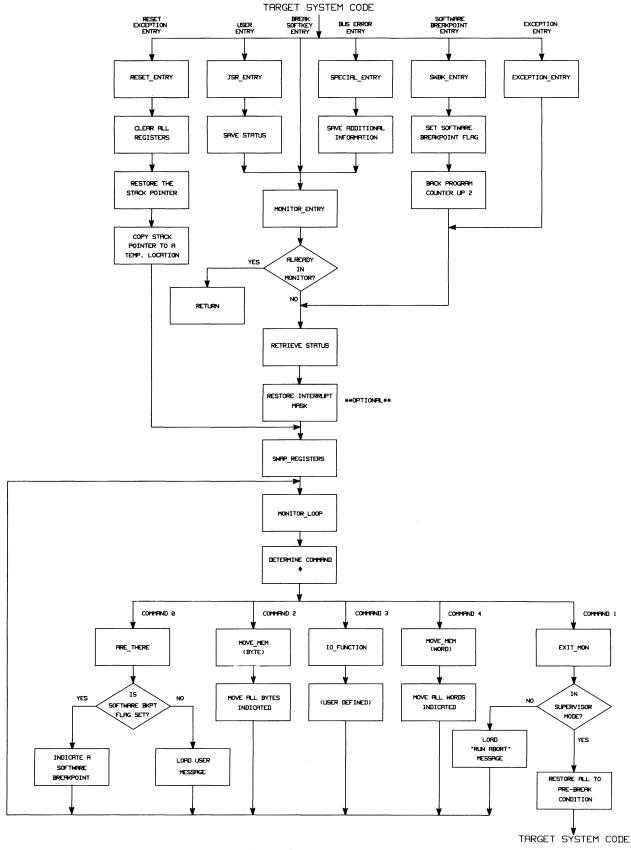

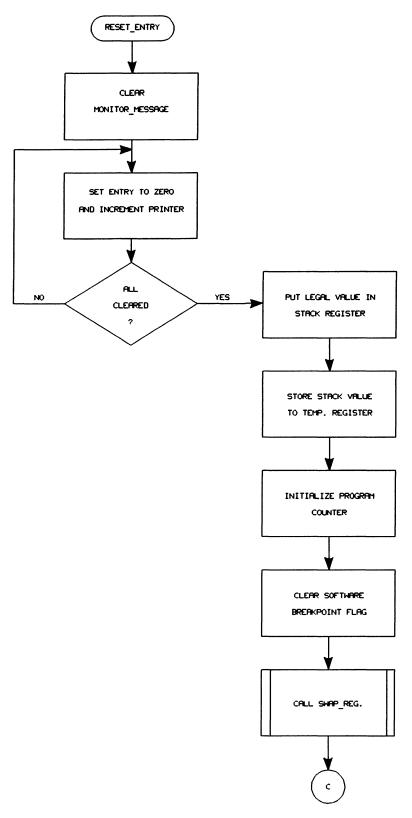

| THE BREAK FUNCTION AND THE EMULATION MONITOR         | 8-2  |

| EMULATION MONITOR                                    | 8-2  |

| MODIFYING THE MONITOR TO USE SOFTWARE BREAKPOINTS    | 8-4  |

| CUSTOMIZING THE EMULATION MONITOR                    | 8-5  |

| Emulation Monitor Memory Requirements (68000)        | 8-8  |

| Emulation Monitor Memory Requirements (68008)        | 8-9  |

| Linking The Emulation Monitor                        |      |

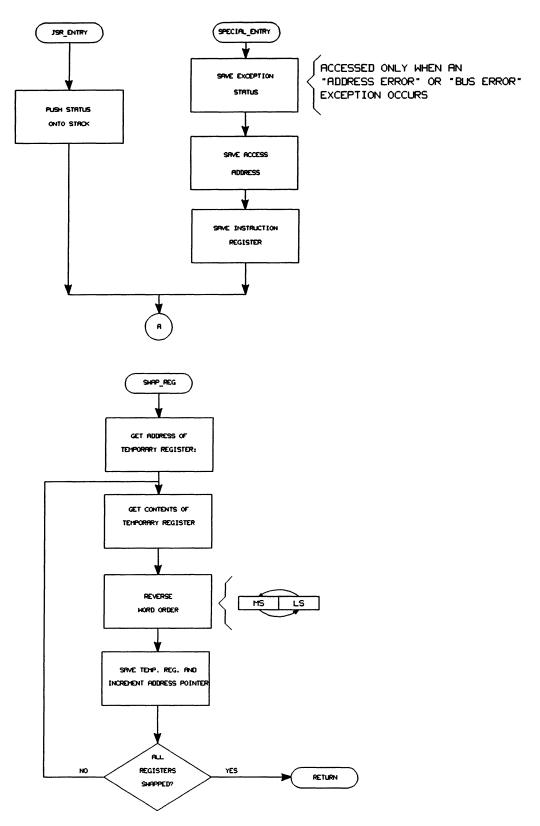

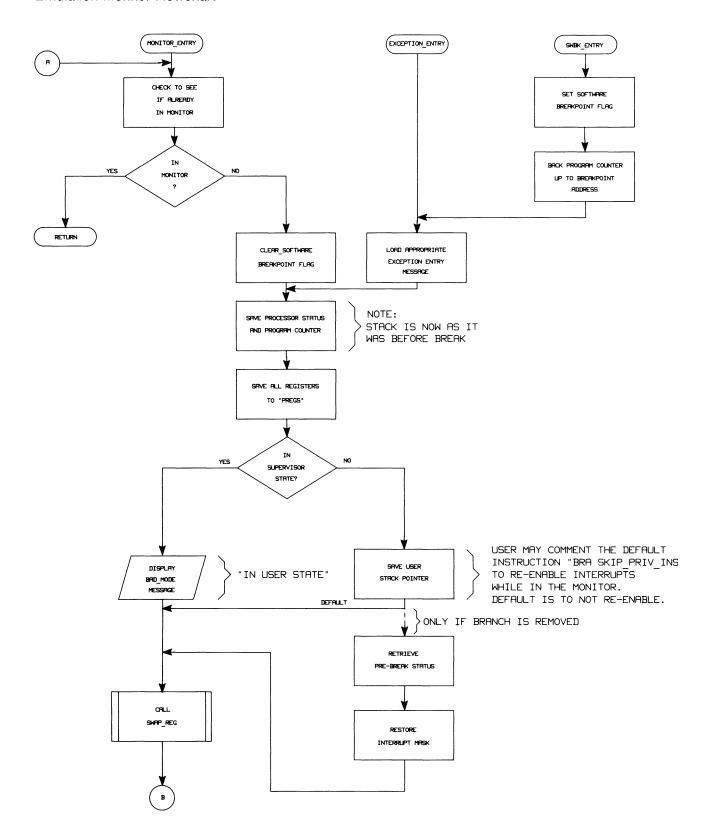

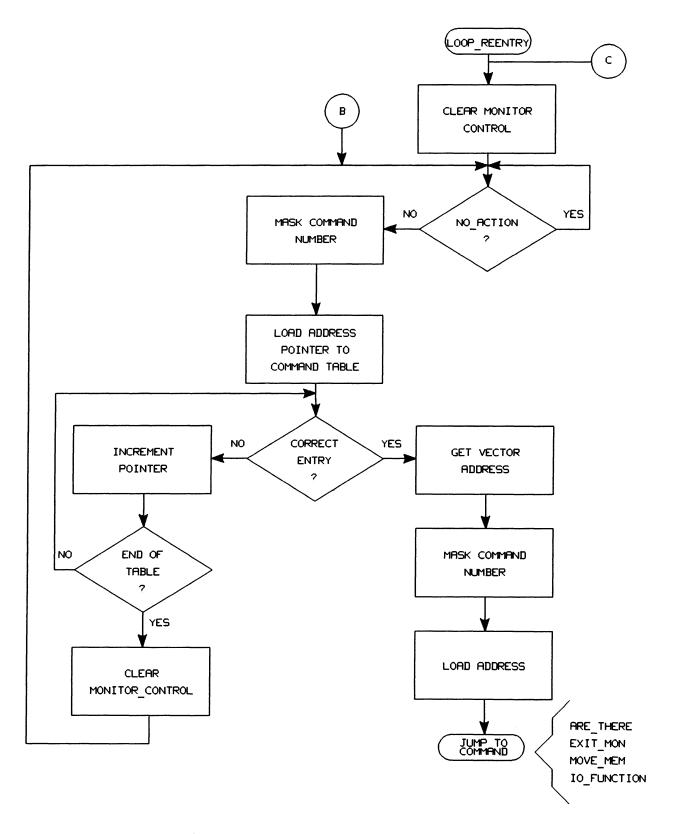

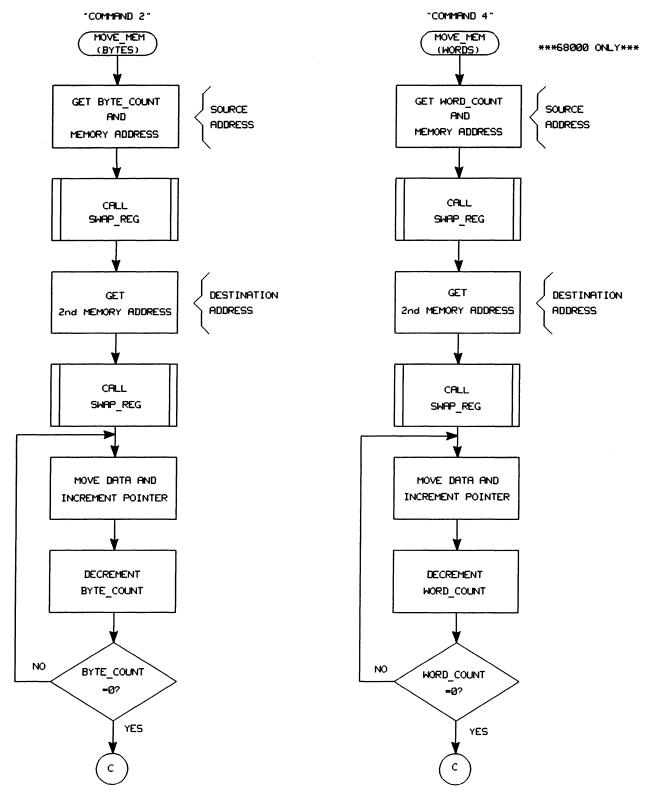

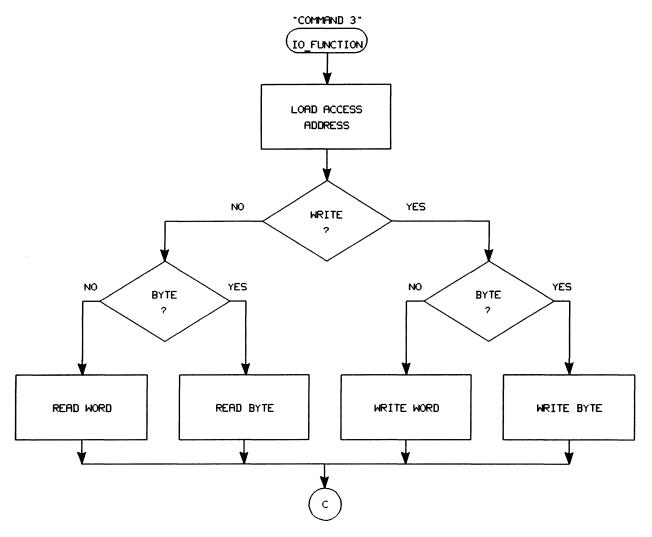

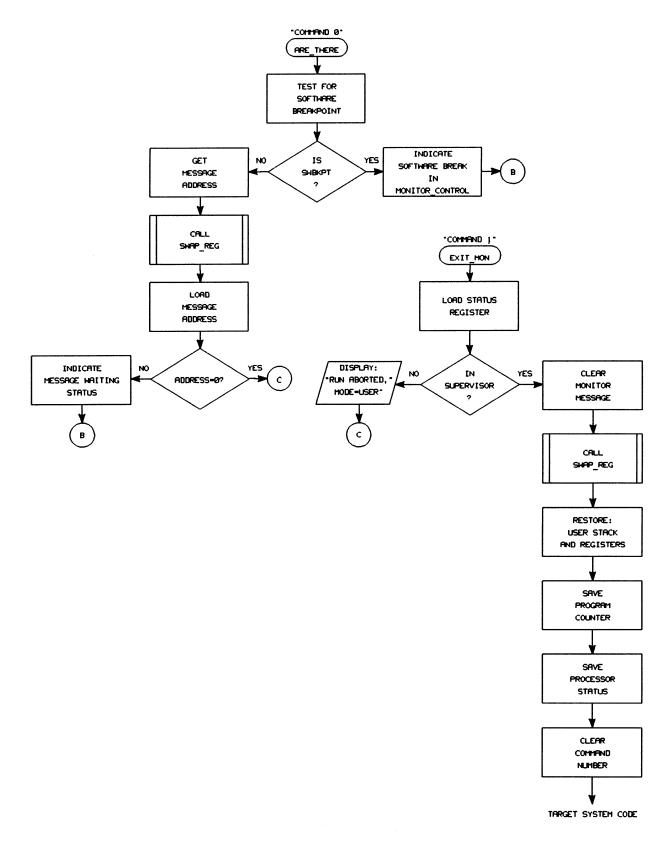

| EMULATION MONITOR FLOWCHART                          | 8-10 |

| EMULATION MONITOR SOURCE PROGRAM                     | 8-10 |

|                                                      |      |

| Chapter 9: EMULATION AND ANALYSIS OPERATIONAL THEORY |      |

|                                                      |      |

| OVERVIEW                                             |      |

| GENERAL                                              |      |

| INTRODUCTION                                         |      |

| EMULATION OVERVIEW                                   |      |

| MULTI-MODULE EMULATION AND ANALYSIS                  |      |

| Plug-in Leads                                        |      |

| EMULATOR OPERATING CONSIDERATIONS                    |      |

| Software Breakpoints                                 |      |

| Using Software Break in Real Time                    | 9-11 |

| Chapter 10: PRINTER SIMULATED I/O                                                                                                                                                                                                                                                                    |                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| OVERVIEW OPENING THE PRINTER FILE WRITING TO THE PRINTER CLOSING THE PRINTER FILE PRINTER EXAMPLE PROGRAM                                                                                                                                                                                            | 10-2<br>10-2<br>10-3                                                         |

| Chapter 11: DISPLAY SIMULATED I/O                                                                                                                                                                                                                                                                    |                                                                              |

| OVERVIEW OPENING THE DISPLAY FILE SCROLLING Roll To/Write Line 18 LINE & COLUMN Selecting The Starting Line/Column Writing From The Starting Line/Column CLOSING THE DISPLAY FILE DISPLAY EXAMPLE PROGRAM PROCEDURE DELAY;                                                                           | 11-2 11-2 11-3 11-3 11-3 11-7                                                |

| Chapter 12: KEYBOARD SIMULATED I/O                                                                                                                                                                                                                                                                   |                                                                              |

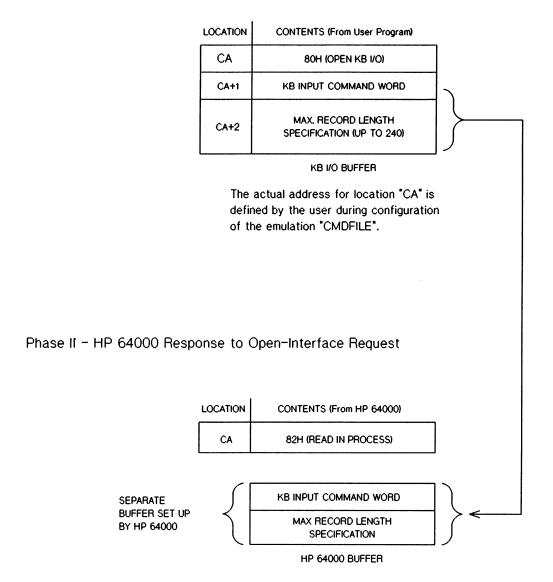

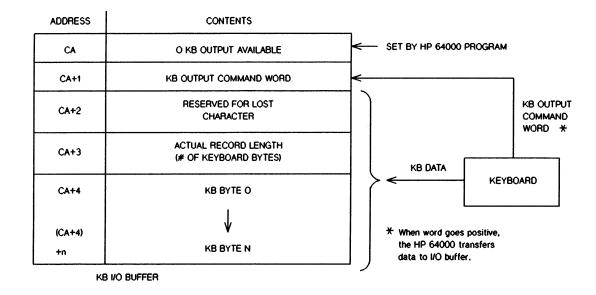

| OVERVIEW OPENING THE KEYBOARD FILE READ IN PROCESS - HP 64000 RESPONSE OUTPUT AVAILABLE -HP 64000 RESPONSE CLOSING THE KEYBOARD FILE                                                                                                                                                                 | 12-2<br>12-2<br>12-3                                                         |

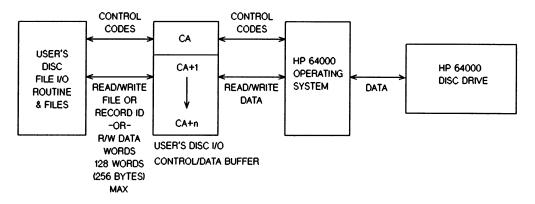

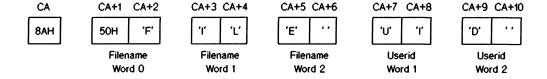

| Chapter 13: DISC FILE SIMULATED I/O                                                                                                                                                                                                                                                                  |                                                                              |

| OVERVIEW CREATING A NEW FILE WRITING A RECORD Writing First Record Writing Additional Records CLOSING THE FILE ACCESSING EXISTING FILES - OPENING THE FILE SELECTING A RECORD Automatic Selection Of Record 1,2,3Etc. Advancing N Records Backup N Records Position To Record N Rewind To Record One | 13-3<br>13-3<br>13-4<br>13-4<br>13-4<br>13-5<br>13-5<br>13-5<br>13-5<br>13-5 |

| 1                                       | READING THE RECORD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-6<br>3-7<br>15                                               |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Chapte                                  | er 14: RS-232 SIMULATED I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                |

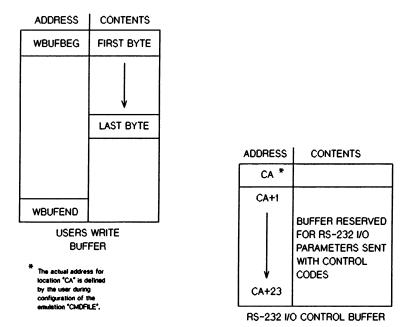

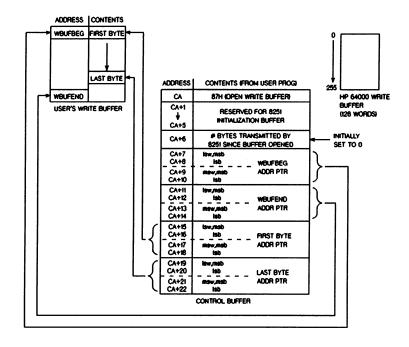

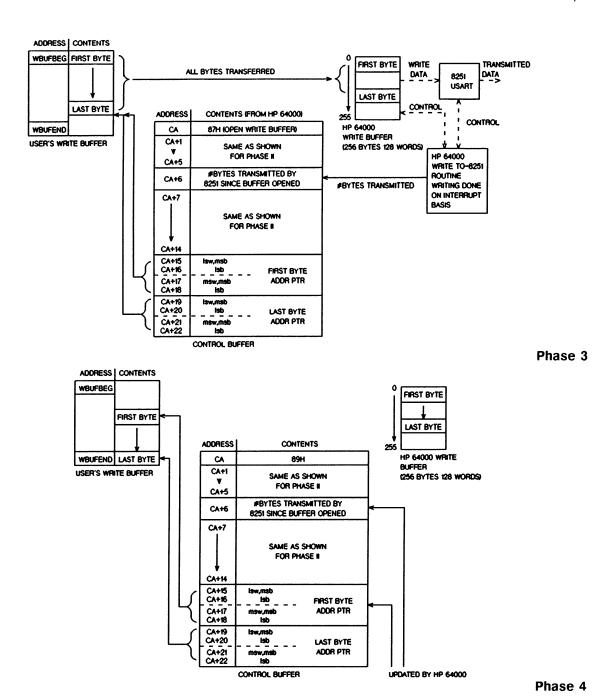

| ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) | DVERVIEW       14         DPENING THE RS-232 FILE       14         NITIALIZING THE 8251 USART       14         Asynchronous Mode       14         Synchronous Mode/Single Sync Character       14         Synchronous Mode/Double Sync Character       14         COMMAND TO 8251 USART       14         WRITING TO THE 8251 USART       14         Writing A Single Byte       14         Using A Buffer To Write Multiple Bytes       14         Write Record       14         Update Write Buffer       14         READING FROM THE 8251 USART       14-         READING FROM THE 8251 USART       14-         READING FROM THE 8251 USART       14-         Using A Buffer To Read Multiple Bytes       14-         Read Record       14-         Update Read Buffer       14-         Closing The Read Buffer       14-         Closing The Read Buffer       14-         Closing THE RS-232 FILE       14-          CLOSING THE RS-232 FILE       14- | -2<br>-3<br>-5<br>-6<br>-7<br>-8<br>-9<br>-9<br>12<br>13<br>17 |

| Appen                                   | dix A: SYNTACTICAL VARIABLE DEFINITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                |

| Appen                                   | dix B: 680XX REGISTER FORMAT AND NAMES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                |

| Appen                                   | dix C: GLOSSARY OF SOFTKEY LABELS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                |

| Appen                                   | dix D: STATUS, ERROR, AND SOFTKEY PROMPT MESSAGES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                |

Appendix E: SIMULATED I/O ERROR CODES

| <b>Appendix</b> | F: | <b>RESTRICTIONS</b> | WHEN | <b>USING</b> | <b>EXECUTION</b> | DATA |

|-----------------|----|---------------------|------|--------------|------------------|------|

|                 |    |                     |      |              | -                | _    |

| EFFECTS OF EXECUTION_DATA MODE                                      | F-2  |

|---------------------------------------------------------------------|------|

| LIST OF ILLUSTRATIONS                                               |      |

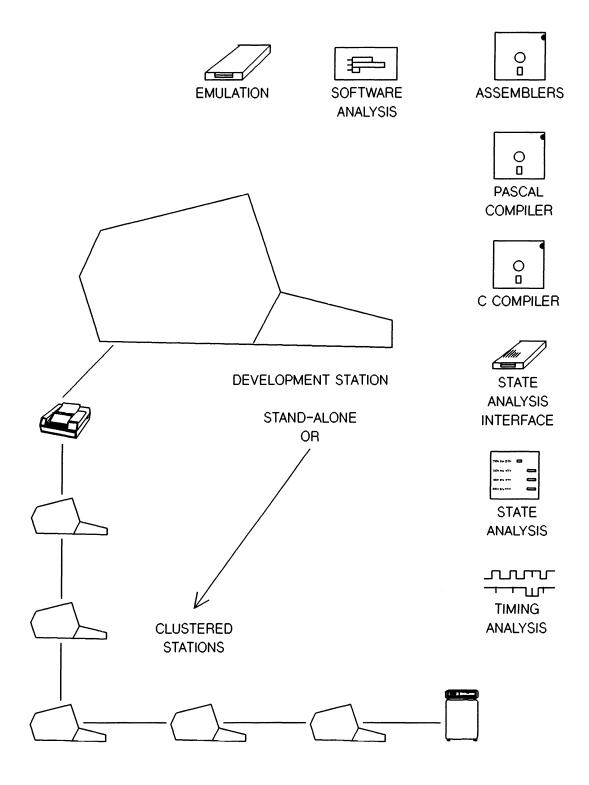

| Figure 1-1. 68000/68008 Emulation Systems                           | 1-C  |

| Figure 1-2. Emulation System Functional Block Diagram               |      |

| Figure 1-3. Development System Tools                                |      |

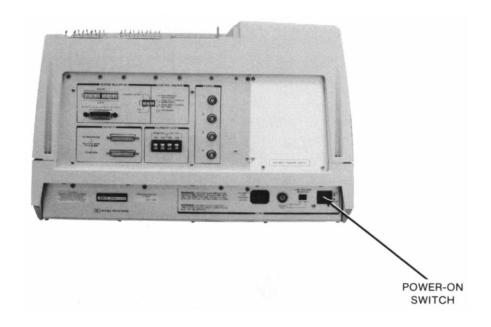

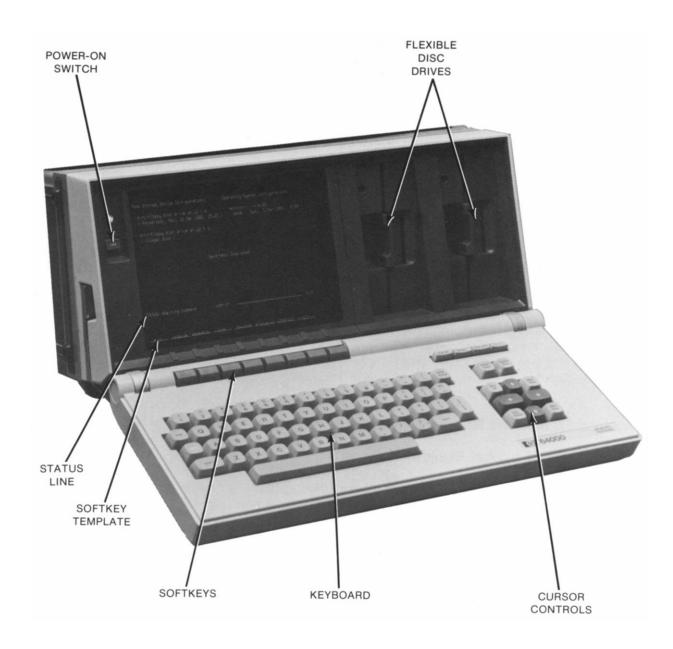

| Figure 2-1. HP 64100 Key Features                                   |      |

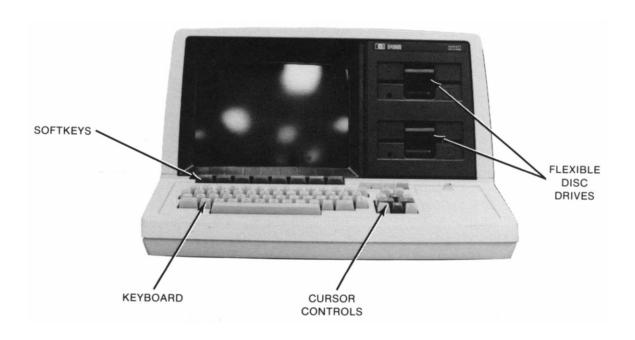

| Figure 2-2. HP 64110 Key Features                                   |      |

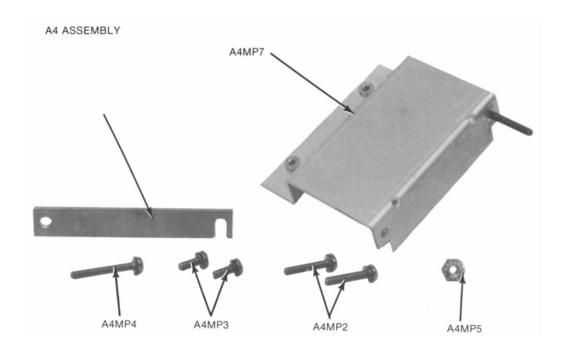

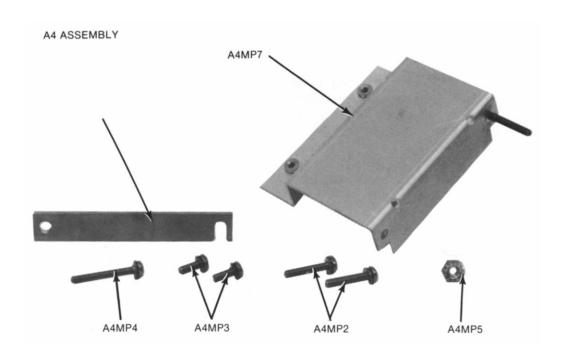

| Figure 2-3. RFI Ground Bracket Assembly Parts                       | 2-10 |

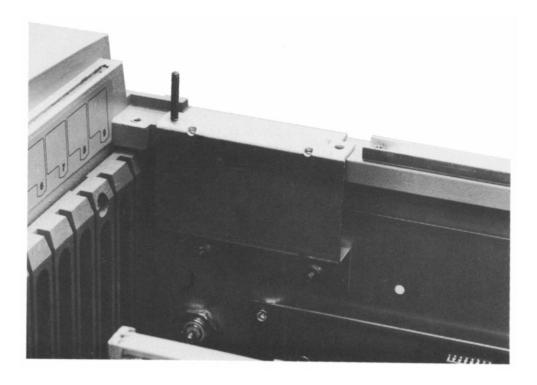

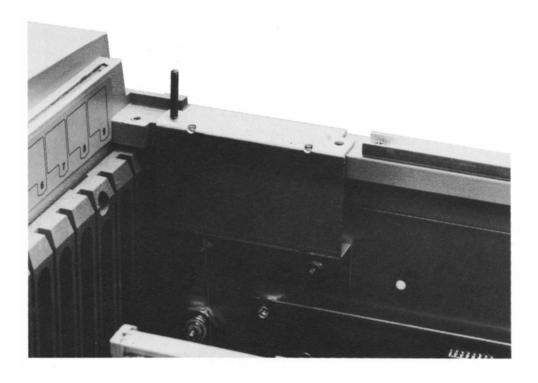

| Figure 2-4. RFI Ground Bracket Installation (HP 64100)              |      |

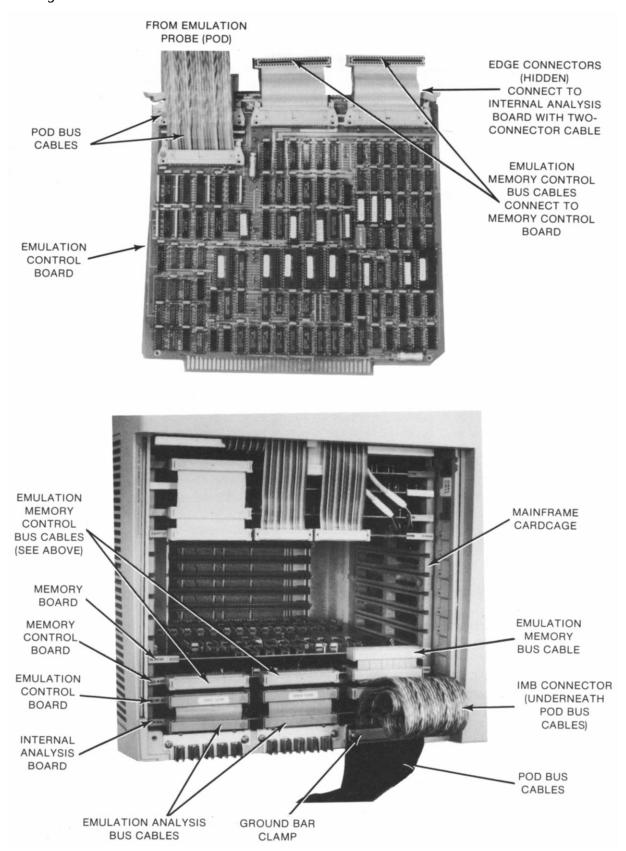

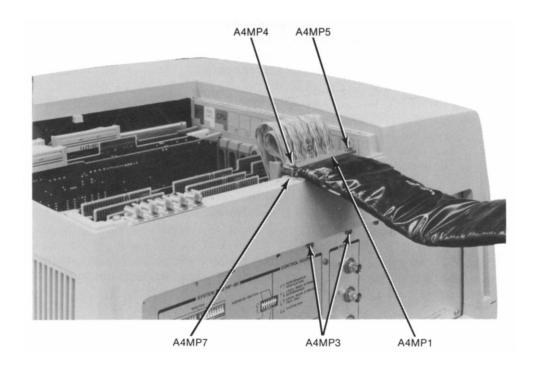

| Figure 2-5. Emulation Control Board Connections                     |      |

| Figure 2-7. HP 64110 Installation Details                           |      |

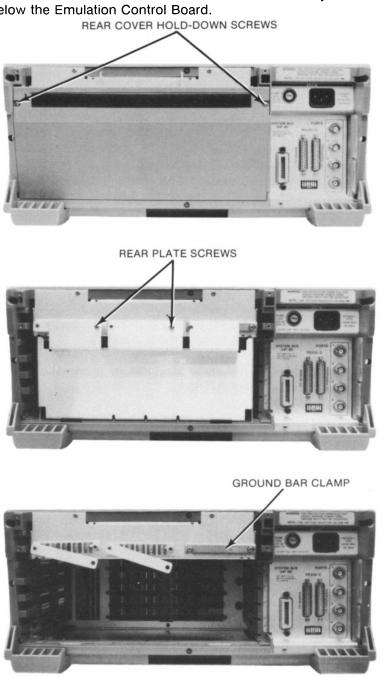

| Figure 2-8. Ground Bar Clamp Installation (HP 64110)                |      |

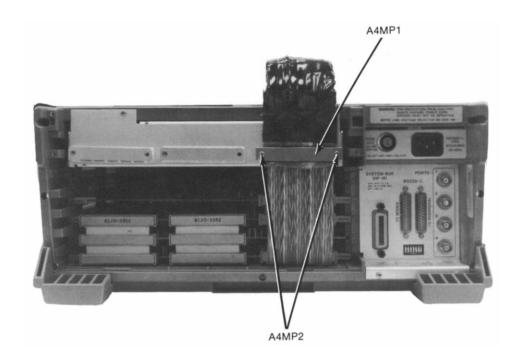

| Figure 2-9. HP 64110 Memory, Emulation, and Intermodule Bus Cabling |      |

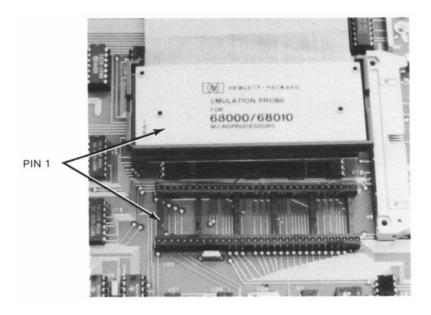

| Figure 2-10. Installing the Emulation Probe Microprocessor          | 2-10 |

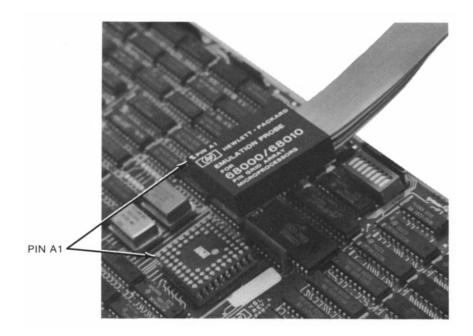

| Figure 2-11. Installing the Emulation Probe Microprocessor          |      |

| Figure 2-12. I/O Bus Configuration Display                          | 2-23 |

| Figure 2-13. Option Test Display                                    |      |

| Figure 3-1. Exception Vector Table (Commented)                      |      |

| Figure 3-2. Exception Vector Table (Un-commented)                   | 3-8  |

| Figure 3-3. Linker Output Listing                                   |      |

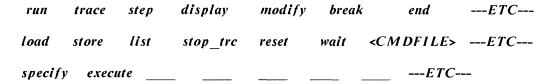

| Figure 3-4. Utility Keys Used For Transportation (from "emulate")   |      |

| Figure 3-5. Utility Keys Used For Transportation (from "meas_sys")  |      |

| Figure 3-6. Trace After 002000H                                     |      |

| Figure 3-7. RUN Emulation Command File Trace 1                      |      |

| Figure 3-8. RUN Emulation Command File Trace 2                      |      |

| Figure 4-1. Example Link Programs                                   |      |

| Figure 4-2A. Mon_680XX Relocatable File - Record #1                 |      |

| Figure 4-2B. Mon_68008 Relocatable File - Record #1                 |      |

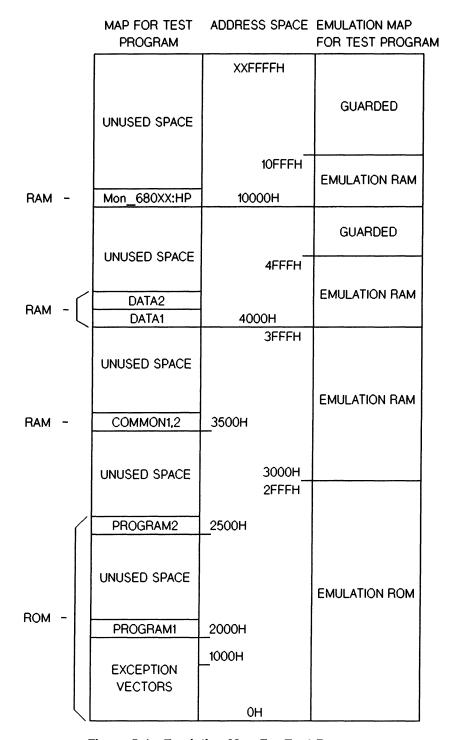

| Figure 4-3. Memory Map For Test                                     |      |

| Figure 4-4. Example Link_Sym Listing                                |      |

| Figure 4-5. Example Memory Map                                      |      |

| Figure 5-1. Emulation Map For Test Program                          |      |

| Figure 5-2. Memory Map Display                                      | 5-14 |

| Figure 5-3. Sample Overlay Mapping #1                               | 5-1/ |

| Figure 5-4. Sample Overlay Mapping #2                               |      |

| Figure 7-1. Memory Contents - Hexadecimal and ASCII                 |      |

| Figure 7-1. Memory Contents - Hexadecimal and ASCII                 |      |

| rigure 7-2. Memory Contents - Milemonic                             | /-5  |

| Figure 7-3. Register Contents                                          | 7-6   |

|------------------------------------------------------------------------|-------|

| Figure 7-4. Trace Memory Display                                       |       |

| Figure 7-5. Bus_Cycle_Data Trace Page 1                                |       |

| Figure 7-6. Bus_Cycle_Data Trace Page 2                                | 7-12  |

| Figure 7-7. Execution Cycle Data Page 1                                |       |

| Figure 7-8. Execution Data Trace Page 2                                |       |

| Figure 8-1. Sample Modified IO_FUNCTION                                |       |

| Figure 8-2A. Mon_68000 Relocatable File - Record #1                    |       |

| Figure 8-2B. Mon_68008 Relocatable File - Record #1                    |       |

| Figure 8-3. Emulation Monitor Flowchart                                |       |

| Figure 9-1. HP 64000 Logic Development System Simplified Block Diagram |       |

| Figure 9-2. Emulation Probe (Pod)                                      |       |

| Figure 9-3. Pod Plug-in Leads                                          |       |

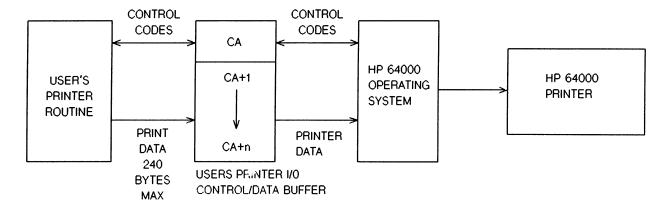

| Figure 10-1. Printer Interface                                         |       |

| Figure 10-2. Program PRINT_SIO                                         |       |

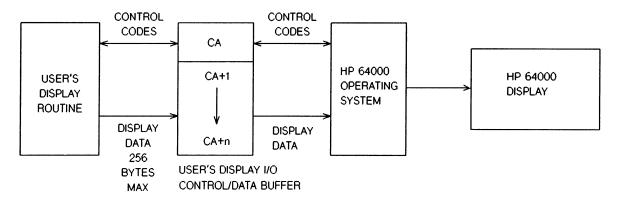

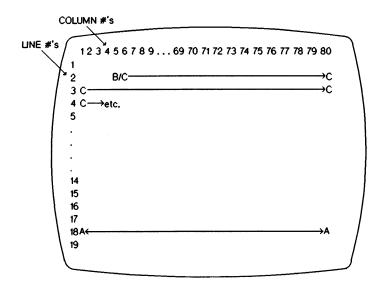

| Figure 11-1. Display Interface Diagram                                 |       |

| Figure 11-2. Display Techniques                                        | 11-4  |

| Figure 11-3 Display/ Keyboard Simulated I/O Program                    |       |

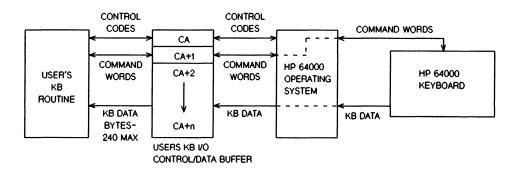

| Figure 12-1. Keyboard Interface Diagram                                |       |

| Figure 12-2. Keyboard Interface Sequence                               |       |

| Figure 13-1. Disc Drive Interface Diagram                              |       |

| Figure 13-2. Program Disc_1                                            |       |

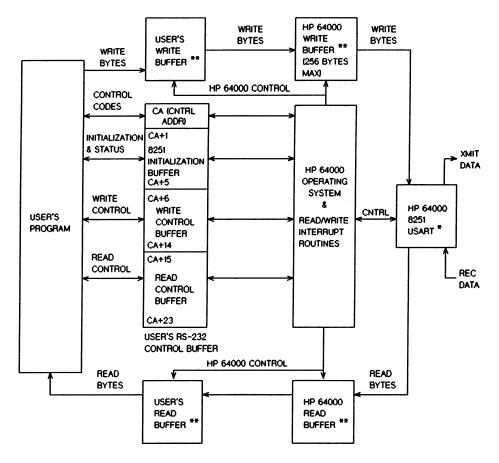

| Figure 14-1. RS-232 Interface Diagram                                  |       |

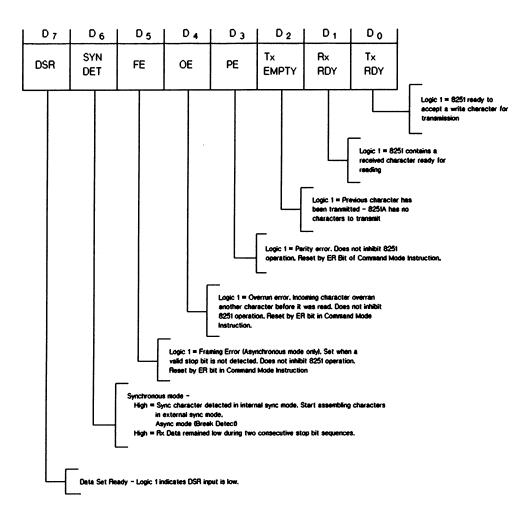

| Figure 14-2. 8251 Initialization Formats                               |       |

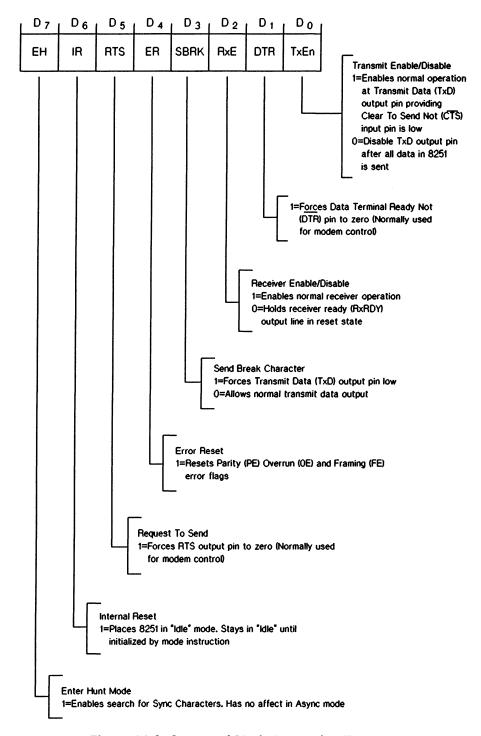

| Figure 14-3. Command Mode Instruction Format                           |       |

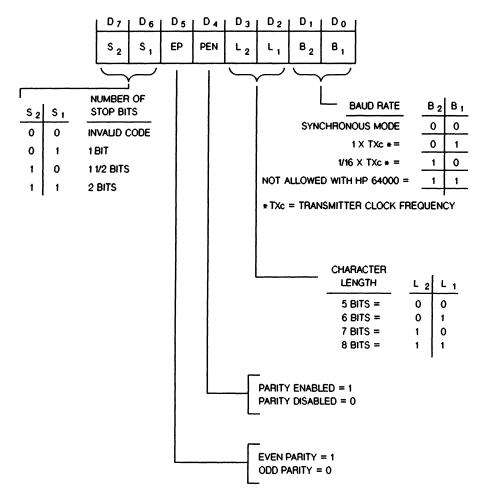

| Figure 14-4. Asynchronous Mode Instruction Format                      |       |

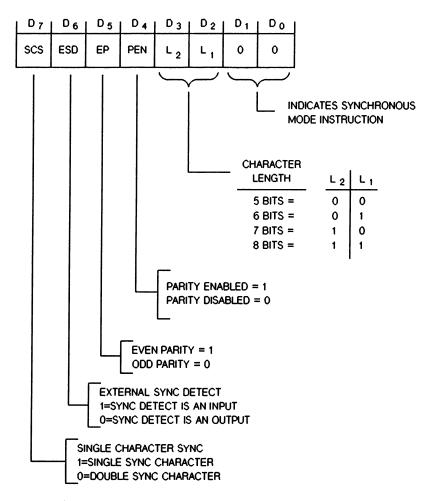

| Figure 14-5. Synchronous Mode Instruction Format                       |       |

| Figure 14-5. 8231 Status Word Format                                   |       |

| Figure 14-7. Writing RS-232 Record Interface Sequence                  |       |

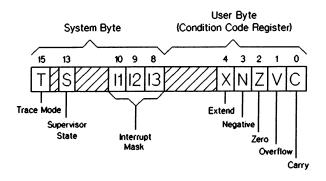

| Figure B-1. Status Register Format                                     |       |

| Figure F-1. Status Register Format                                     |       |

| rigule 1-1. Example One Word Branch-Around Code                        | Г-2   |

| LIST OF TABLES                                                         |       |

| LIST OF TABLES                                                         |       |

| Table 2-1. RFI Ground Bracket Assembly Parts List                      | 2-9   |

| Table 5-1. Number of Mapper Blocks vs. Available Memory                |       |

| Table 6-1. 680XX Status Definition                                     |       |

| Table 6-2. Softkey Labels and Mnemonic Status Definitions              | 6-4   |

| Table 7-1. "And" Function Results                                      | 7-8   |

| Table 10-1. Printer Control Codes                                      | 10-4  |

| Table 11-1. Display Control Codes                                      |       |

| Table 12-1. Keyboard Control Codes                                     | 12-4  |

| Table 12-2. Command Word Codes                                         | 12-6  |

| Table 13-1. Disc File Type Numbers and Names                           | 13-2  |

| Table 13-2. Disc File Control Codes                                    | 13-8  |

| Table 14-1, RS-232 Control Codes                                       | 14-18 |

| Table | D-1. | Status Messages                                 | D-1 |

|-------|------|-------------------------------------------------|-----|

|       |      | Error Messages                                  |     |

| Table | D-3. | Softkey Prompt Messages                         | D-5 |

| Table | E-1. | Simulated I/O Error Codes - General Definitions | E-1 |

## NOTICE

CONDUCTIVE FOAM OR PLASTIC OVER EMULATOR PINS MAY CAUSE ERRATIC OPERATION.

The emulator and preprocessor user assembly pins are covered at the time of shipment with either a conductive foam wafer or a conductive plastic pin protector. This is done for two reasons: 1) to protect the user interface circuitry within the emulator or preprocessor from electro-static discharge (ESD), 2) to protect the delicate gold plated pins of the probe assembly from damage due to impact.

Both the foam and plastic protection devices are conductive. This may cause erratic performance of the emulation or analysis system during operation, and also during option\_test performance verification. Therefore, it is recommended that the foam or plastic device be removed before using the emulation or analysis system or before running option test performance verification.

When not using the emulator or preprocessor, the foam or plastic assembly should be replaced to retain protection for the probe pins and protection from ESD.

## **USING THIS MANUAL**

#### **GENERAL**

This manual includes both operating instructions for the emulator and reference material. The reference material is gathered in the final chapters: Command Summary and Syntax, The Emulator Monitor Program, Emulation and Analysis Operational Theory, Simulated I/O, and the seven Appendices.

If you have never used a HP 64000 series Emulator, you will want to take special note of Chapter 3, Chapter 4, Chapter 5, and Chapter 6. The tutorial information in Chapter 3 is most effective as a training tool if you sit down at a HP 64000 development station, and, following the manual's instructions, enter and step through each of the examples provided.

If you are an experienced (HP 64000) emulator user, you will want to take special note of Chapter 6 and Chapter 7 which include information specific to the 68000/68008 emulator.

#### MANUAL CONTENTS GUIDE

Several guides are provided to help you find the information you need:

- A table of contents precedes the body of the manual.

- The first page of each chapter lists the topics that are covered in that chapter. Each chapter is dedicated to a single purpose.

- An index concludes the manual.

The 68000/68008 Emulator/Analyzer Manual is divided into thirteen chapters, defined as follows:

Chapter 1 introduces basic emulator concepts and provides a general overview of an emulation system.

Chapter 2 is the installation information. This chapter describes, in detail, how to install the emulation system in your HP 64100 and HP 64110. Also included is information on how to configure the system for "stand-alone" operation.

Chapter 3 is a tutorial. This chapter walks you through the emulation process and explains, in general terms, some of the more basic emulation features.

Chapter 4 is a review of the assembling and linking processes which are necessary before emulation can begin.

Chapter 5 explains each of the emulation configuration questions and explains the options available to answer the questions. Chapter 6 explains how to enter and exit the emulation program, provides guidelines for various modes of emulation, provides information on the 68000/68008 processor, and concludes with emulation examples.

Emulator/Analyzer 68000/68008 Using This Manual

Chapter 6 explains how to enter and exit the emulation program, provides guidelines for various modes of emulation, provides information on the 68000/68008 processor, and concludes with emulation examples.

Chapter 7 provides a functional description of the emulation system commands and the syntax for using them.

Chapter 8 provides a detailed description of the emulation monitor program provided with your emulation system software.

Chapter 9 provides the emulation and analysis operational theory.

Chapters 10 through 14 describe the simulated I/O feature of the HP 64000 Logic Development System.

### UNDERSTANDING THE EXAMPLES USED IN THIS MANUAL

The examples provided throughout this manual use the following structure:

PRESS (or press) edit MODULE RETURN).

PRESS or press-- means you should enter a command by selecting the softkeys and/or typing in any file names or other variables which are not provided in the softkey selections.

edit -- softkeys will appear in italics. Usually you will not be prompted to use the ---ETC--- softkey to search for the appropriate softkey template.

MODULE -- this is the name of a file which you must type in. Softkeys are not provided for this type of selection since it is variable. However, a softkey prompt such as, <FILE> will appear as a softkey selection.

(RETURN) -- this indicates that the RETURN key, located on the keyboard, should be pressed.

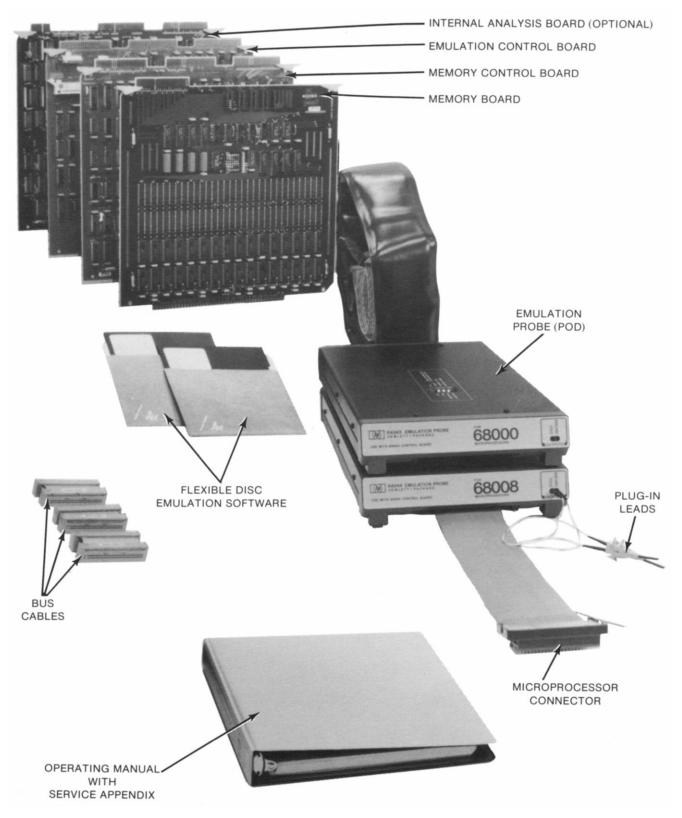

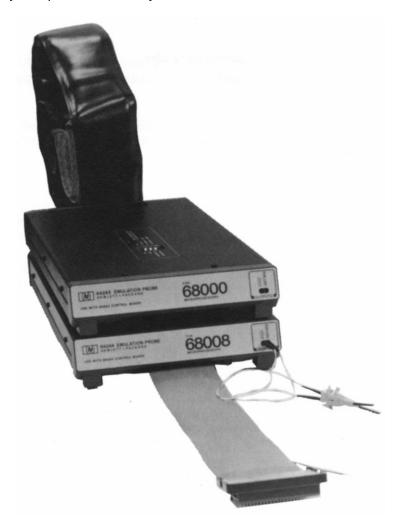

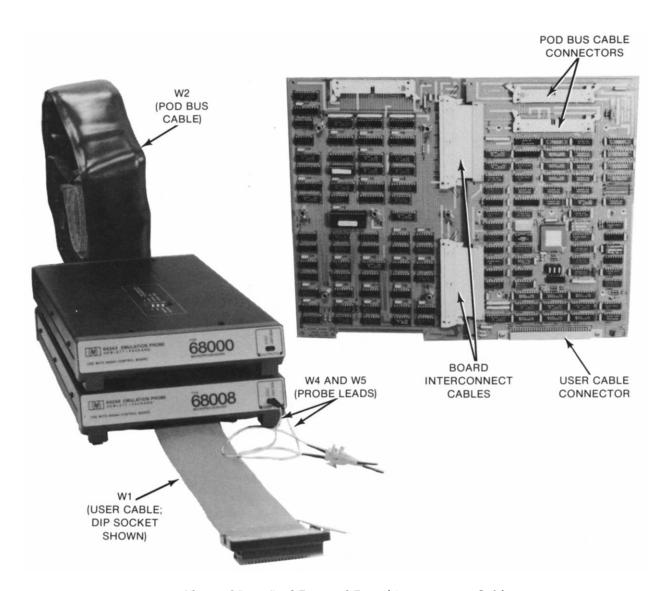

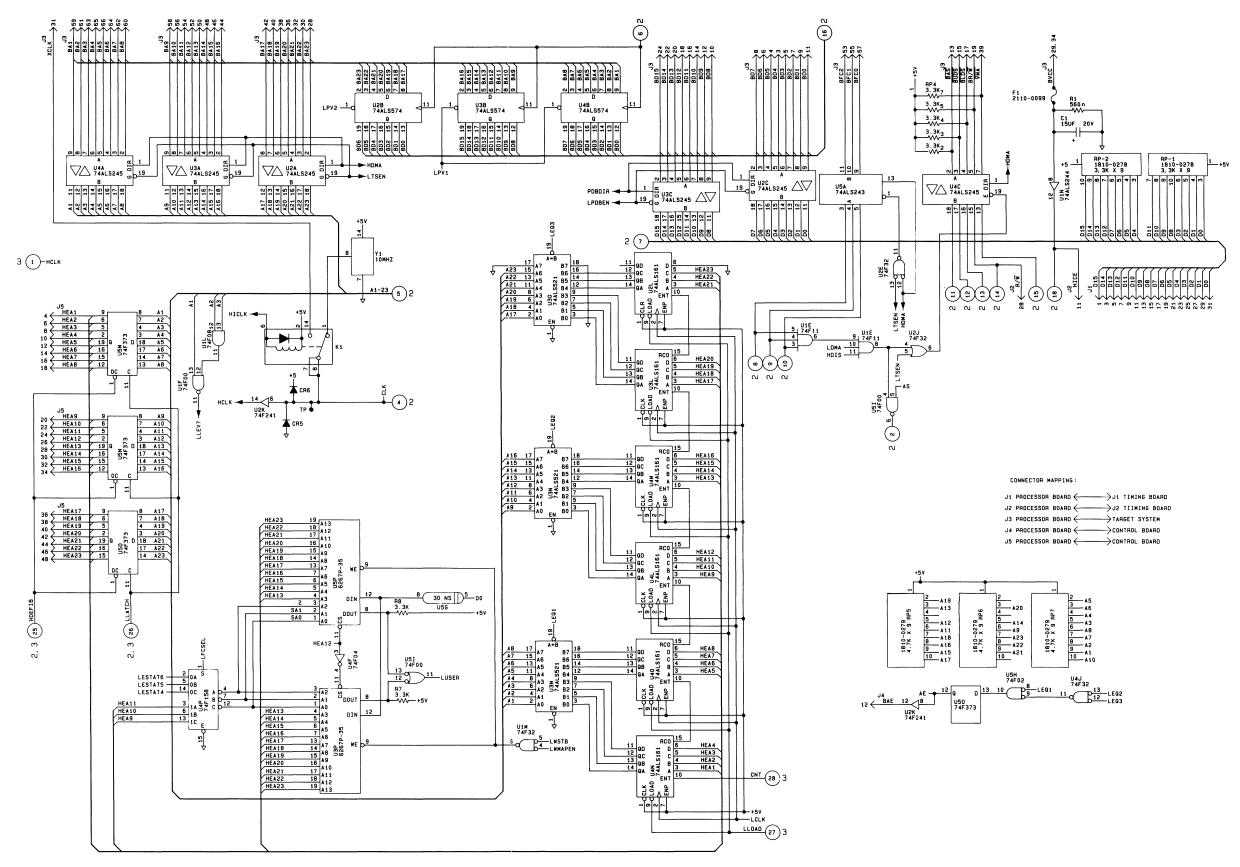

Figure 1-1. 68000/68008 Emulation Systems

# Chapter 1

## **GENERAL INFORMATION**

#### **OVERVIEW**

This chapter will answer these questions:

- What is an emulation system?

- What does an emulator allow you to do?

- Will the emulator system run interactively with other HP 64000 system modules?

- Will using an emulator have an effect on your program?

- What is happening while your program is running?

- · What does the emulator do to your microprocessor system?

- What is your role in the emulation process?

- What can Software Materials Subscription do for you?

#### SAFETY CONSIDERATIONS

This product is a Safety Class 1 instrument (provided with a protective earth terminal) and meets safety standards IEC 348. Review the instrument and this manual for safety markings and instructions before operating the instrument.

### **GENERAL**

In this chapter, whenever 680XX is mentioned (even as part of a filename) both the 68000 and the 68008 are assumed unless there are differences between the two processors. In that case, the differences will be noted. When the name 680XX appears in any program listings, just insert the appropriate name of your processor.

#### WHAT IS AN EMULATION SYSTEM?

#### **Physical Description**

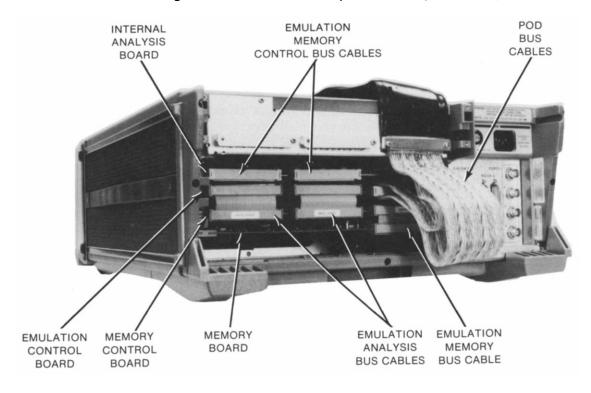

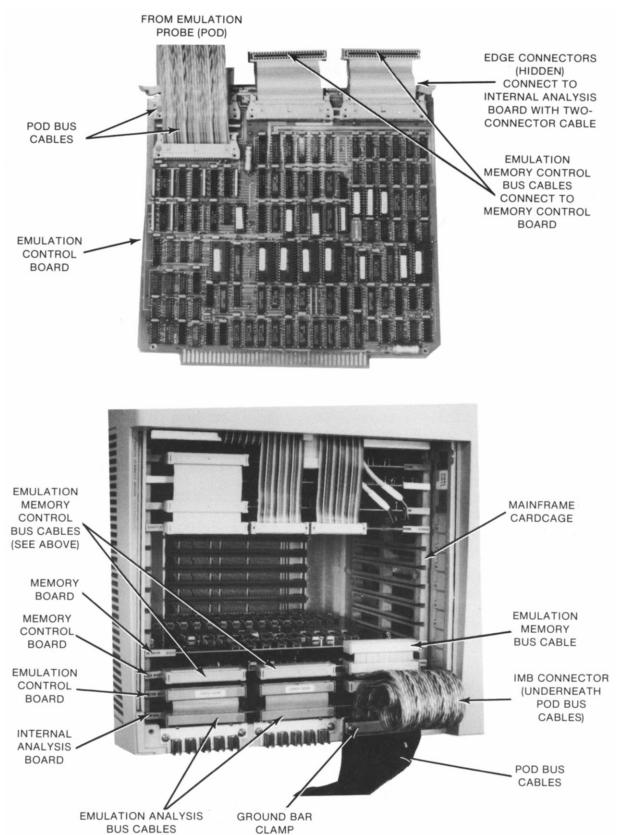

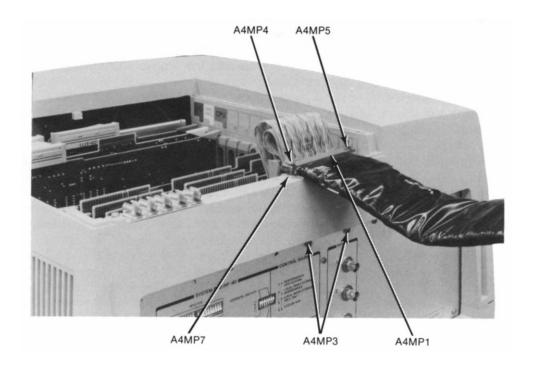

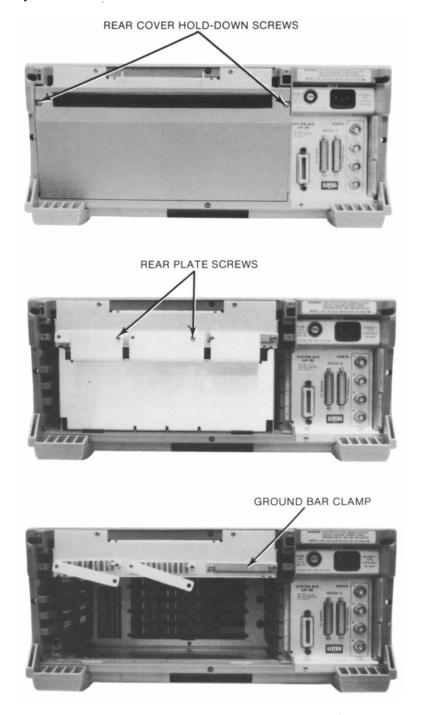

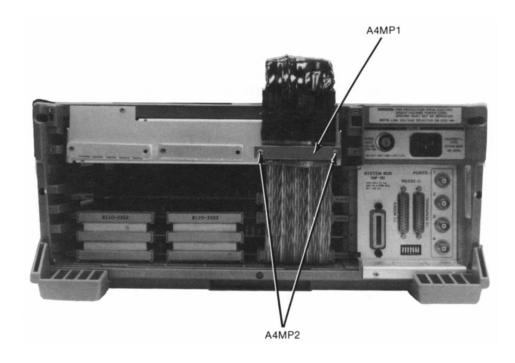

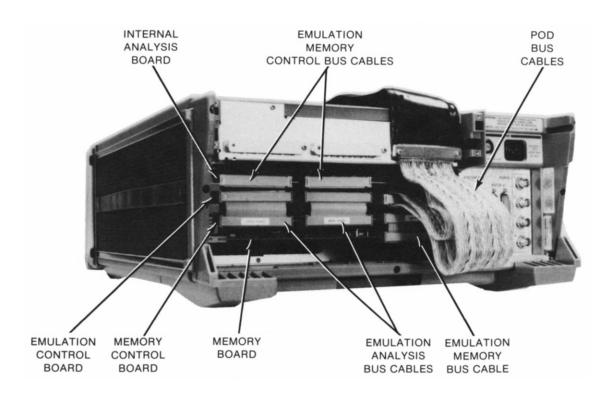

The emulation system is a separate functional module within the HP 64000 development station structure. The operator controls the emulation system via the station keyboard and display. The emulation system consists of four hardware modules plus the flexible disc emulation software package and technical manuals. The four hardware modules are:

- Emulation Subsystem

- Emulation Memory Subsystem

- Internal Analyzer

- Emulation/Memory/Analysis Bus Cable(s)

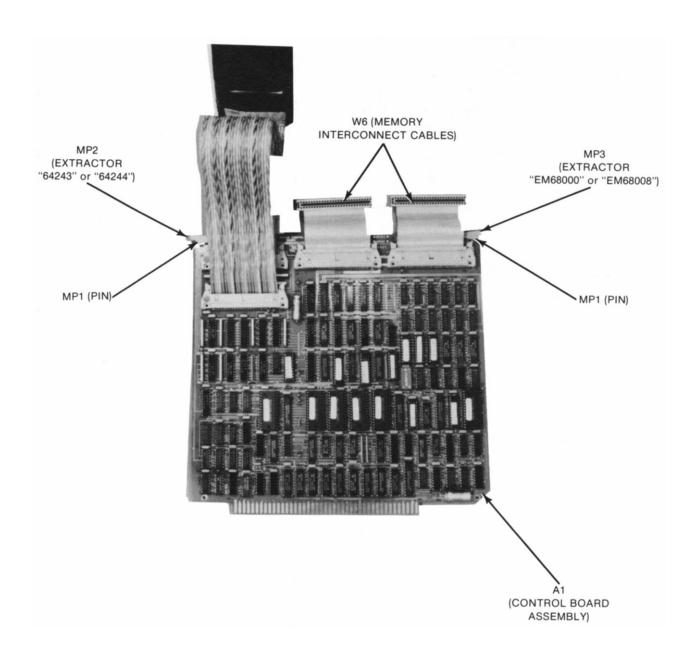

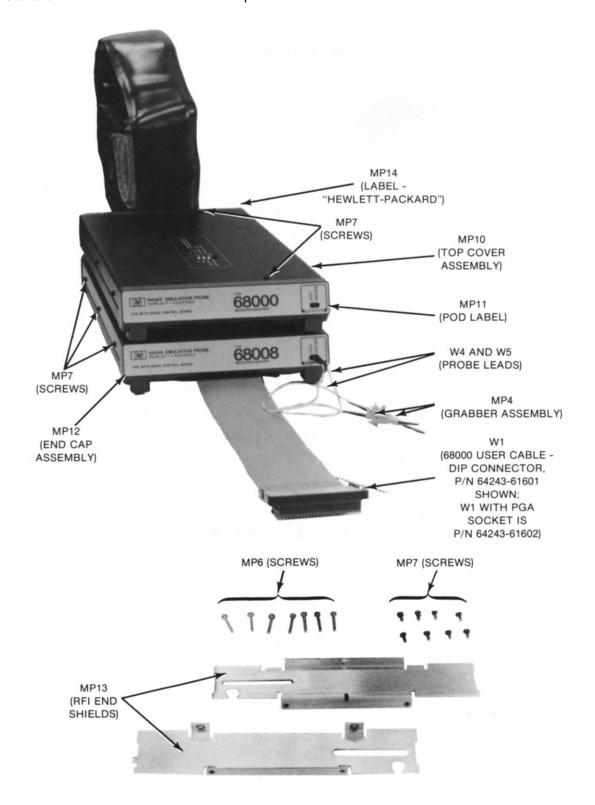

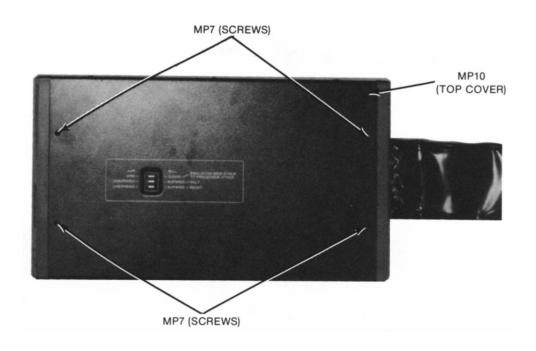

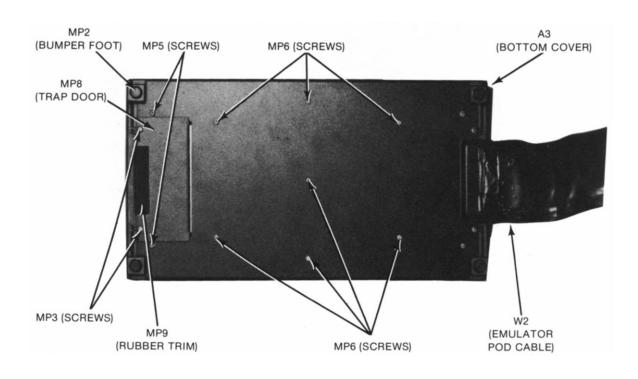

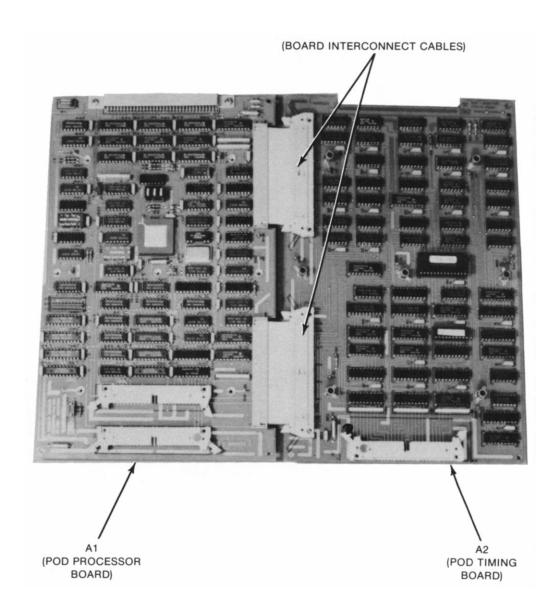

The emulation system hardware listed above consists of circuit boards which are installed in the development station card cage, the emulation probe (pod) which is connected by cabling to the development station, and bus cables to connect the boards. These parts, along with the software and technical manuals required, are shown in figure 1-1 and are listed below.

#### **Emulation Subsystem Hardware**

(1) Emulator Probe (Pod)/Control Board HP 64243 (68000) or HP 64244 (68008)

#### **Emulation Memory Subsystem Hardware**

- (1) Emulation Memory Control Board HP 64155A

- (1) Memory (Static RAM) Board(s) HP 64152/153/154A or HP 64161/162/163A

#### Internal Analyzer

To perform the internal analysis functions described in this manual you must also have the following option:

(1) Wide Internal Analysis Board HP 64302A

#### NOTE

The entire emulation system may be used in conjunction with "external" analysis and timing systems for more sophisticated measurements. External analysis and timing systems are available as plug-in options for the HP 64000 system. See your local HP Sales & Service office for more details on the external analysis systems.

#### **Emulation/Memory/Analysis Bus Cable(s)**

(3) Bus Cable(s)

## **Emulation System Software**

(2) Flexible Disc Emulation System Software (HP 64243-120XX) (68000) or (HP 64244-120XX) (68008)

#### **Emulation System Manual**

(1) 68000/68008 Emulation with Internal Analyzer Operating Manual with Service Appendix HP 64243-90901

## **Accessory Software Required**

In order to assemble/compile and link your program modules you will need to have the following software:

- (1) Flexible disc containing 68000/08/10 Assembler/Linker HP 64845AF

- (3) Flexible disc containing 68000/08/10 Pascal Compiler HP 64815AF

- (2) Flexible disc containing 68000/08/10 C Compiler HP 64819AF

## **Functional Description**

The goal of the emulator is to look just like the microprocessor which will eventually control your system, as seen by your target system hardware. At the same time it must be capable of giving you complete and immediate insight into the clock-by-clock operation of the system. The function, signal quality, signal timing, loading, drive capacity, and other factors at the plug-in connector should be indistinguishable from the same factors that would be present if the actual processor were being used. This characteristic is referred to as transparency, which is discussed later in this chapter under the heading entitled "What Does The Emulator Do To Your Microprocessor System?"

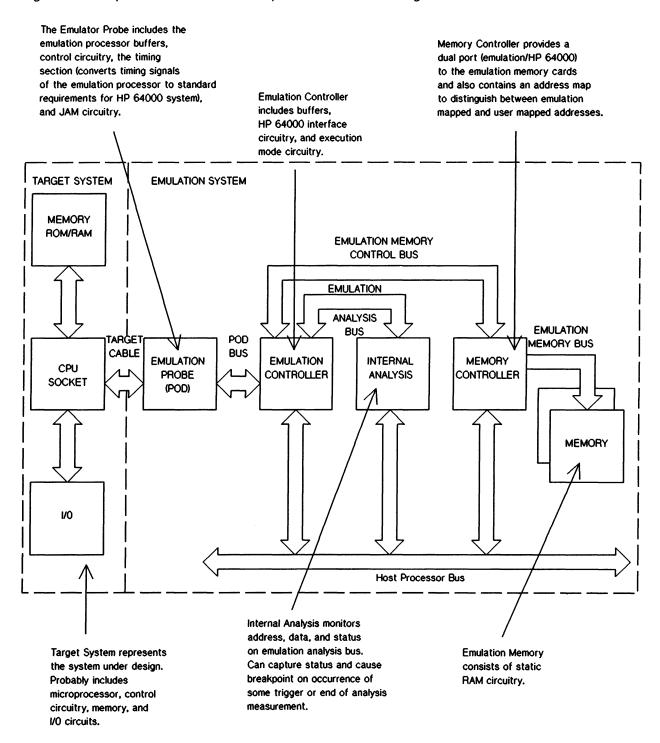

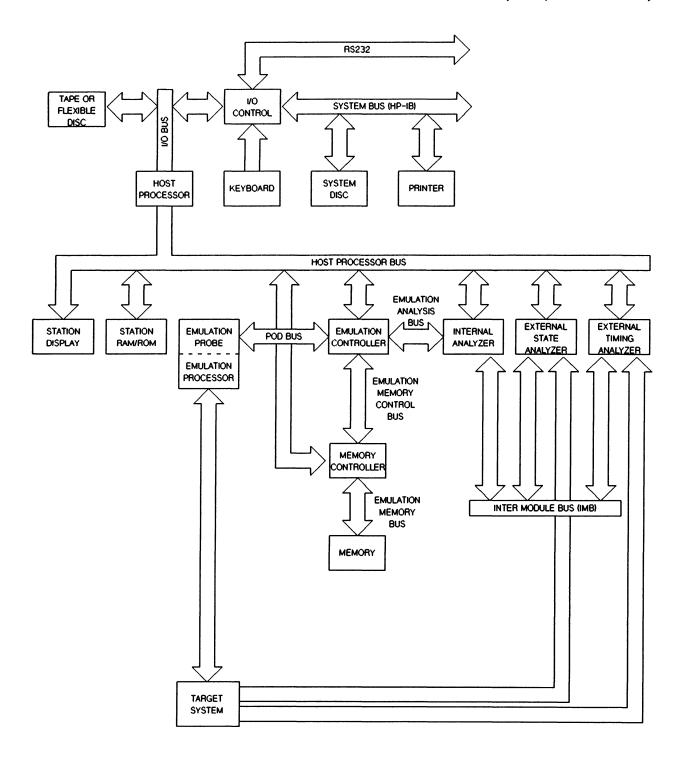

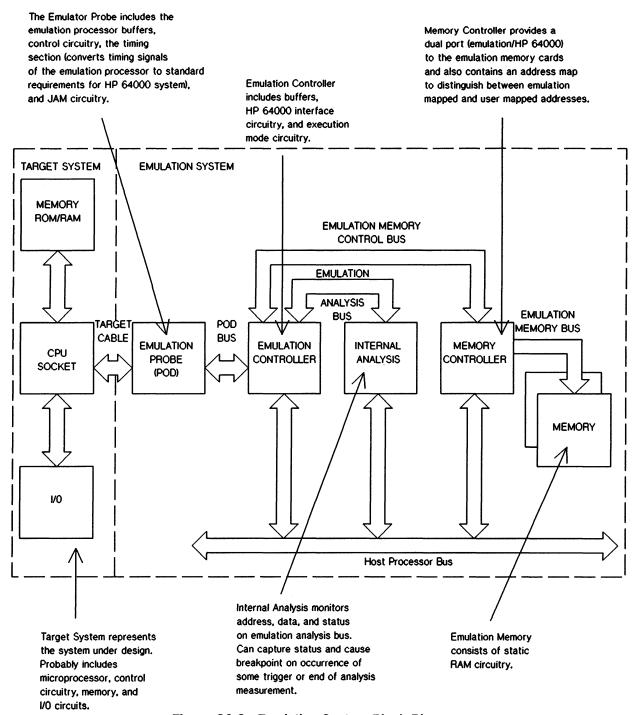

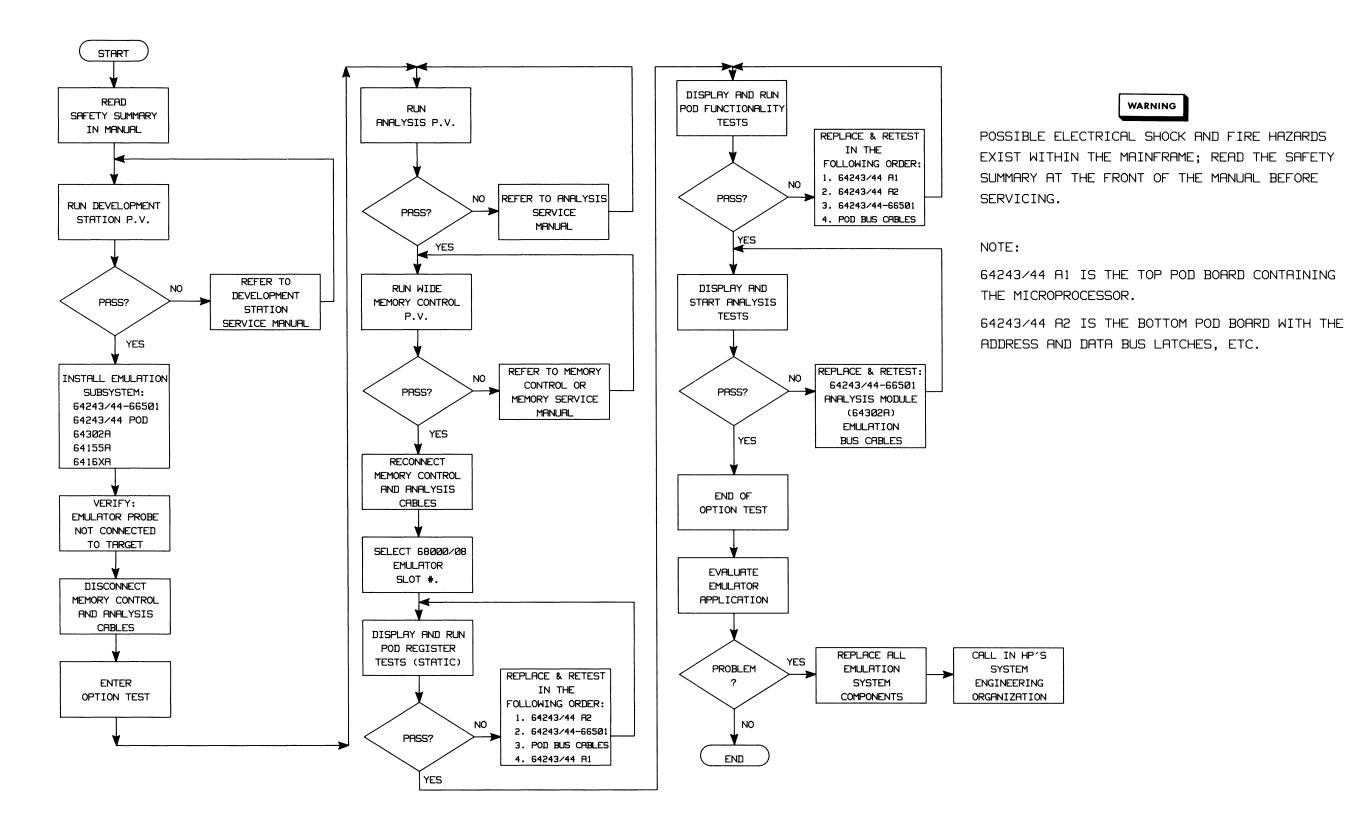

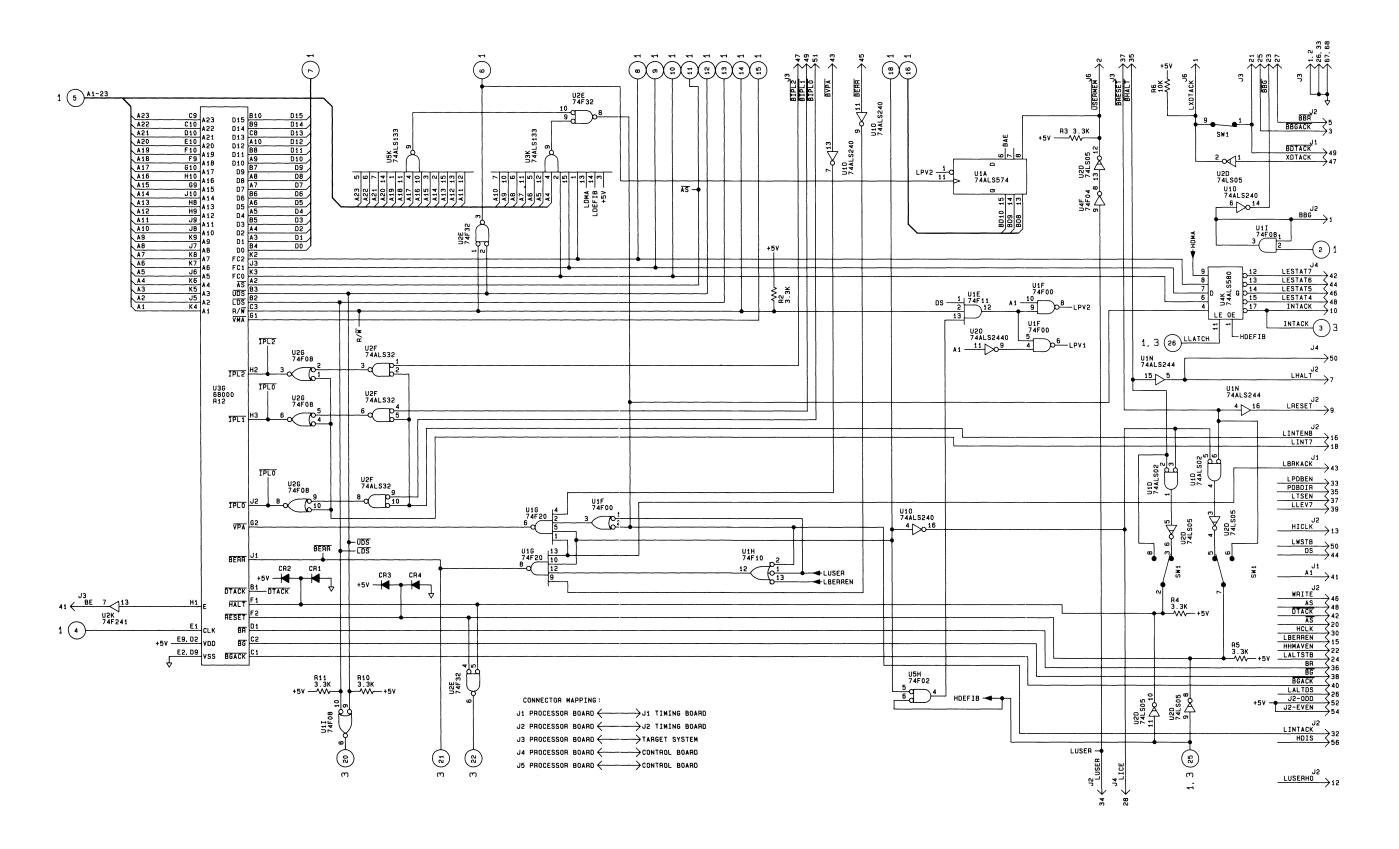

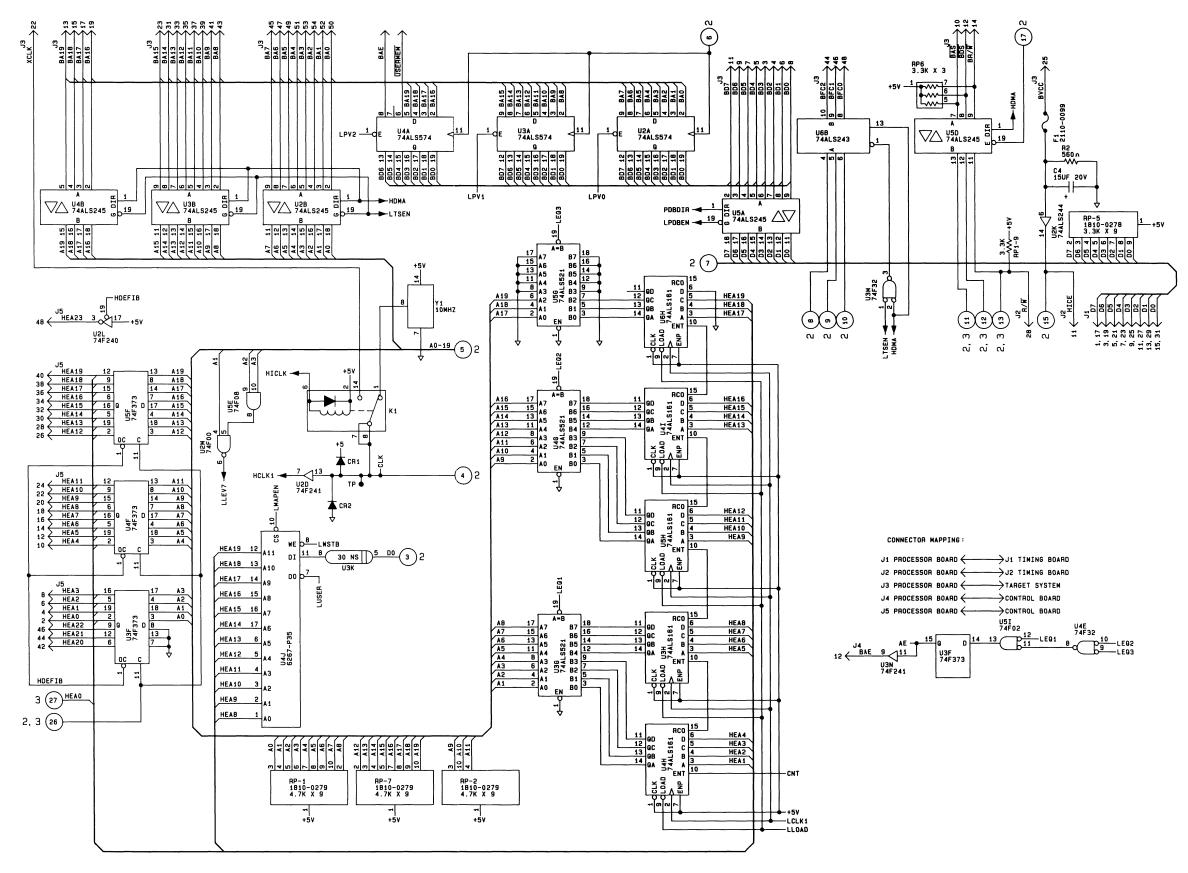

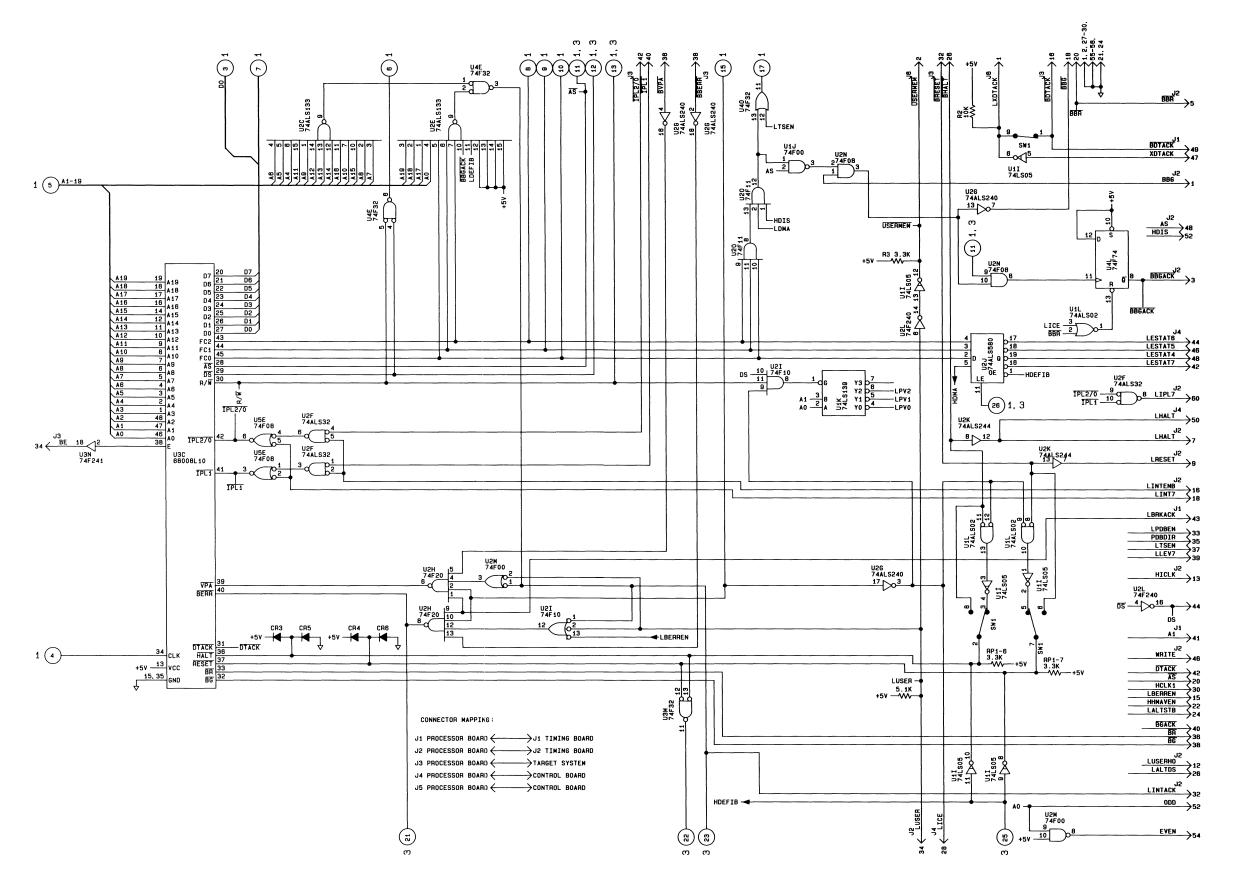

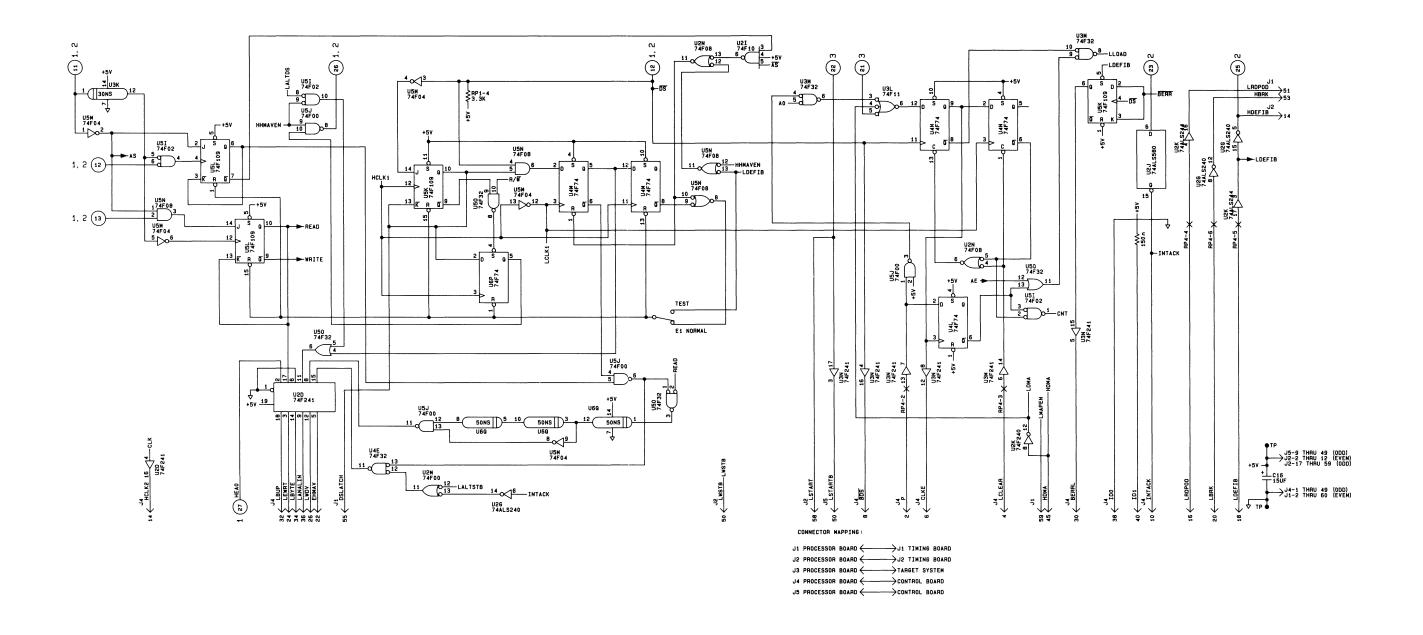

The emulation system and its components, functionally illustrated in figure 1-2, are described briefly in the following paragraphs. A further, in-depth description, is given in Chapter 8, "Emulation and Analysis Operational Theory".

Interaction between the HP 64000 editor, the assembler/linker, and the emulator run-time environment is so easy that error producing programming practices, such as code patching, are unnecessary.

An important feature is that the emulation and analysis functions can operate independently of the HP 64000 operating system. That is, once the emulation and analysis equipment has been configured and set into operation, the equipment can operate without interaction from the operating system.

After your (target system) hardware is developed, the emulator can be used in-circuit, alone, or with other products to debug your target system hardware and to integrate the program modules with your target system hardware.

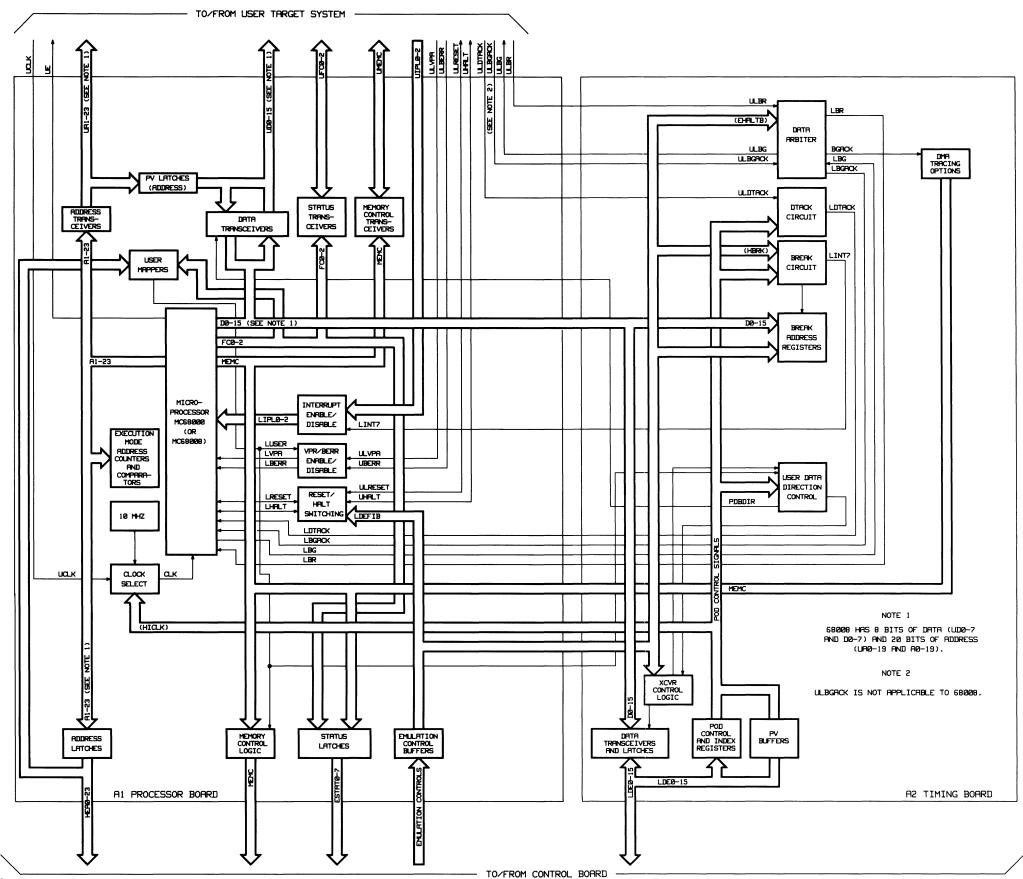

Emulation is accomplished by a two-processor system. The host microprocessor, located in the development station, is used by the HP 64000 operating system. The emulation processor, located in the emulation pod, is used to emulate your target system processor. Since the host and emulation processors do not share the operating system resources, the HP 64000 can easily be adapted to support different target systems by changing the emulation processor.

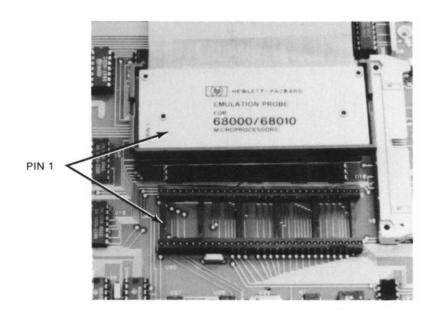

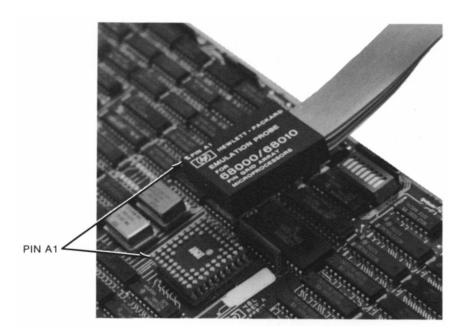

The emulator allows you to replace the 680XX processor in your target system with a device which performs like the 680XX, but which is easily controlled by you from the development station. This is done through the emulation pod and microprocessor connector which are part of the cable extending from the emulation control board. The pod contains the processor that drives your target system. The microprocessor connector is plugged into your target system processor socket. (Your target system processor must be removed to accommodate the connector.)

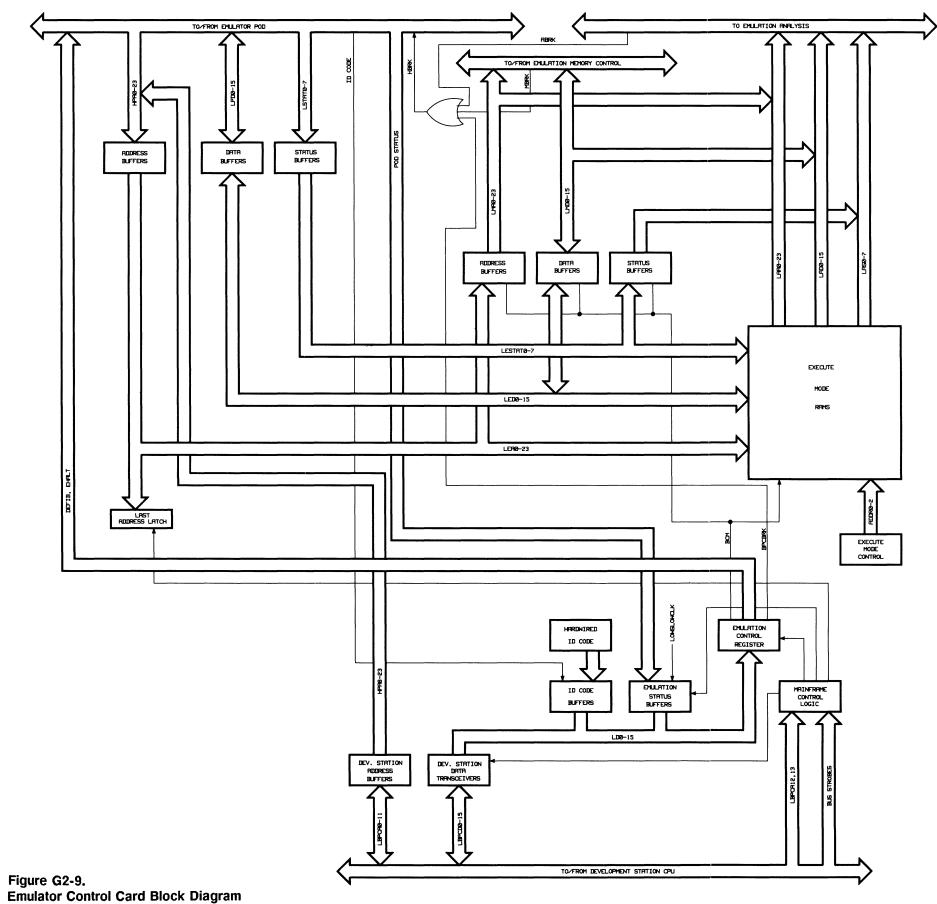

The emulator allows you to access and modify internal processor registers, and locations or blocks of memory. In addition, you can access code instruction-by-instruction. The emulation control board controls the interaction between the HP 64000 operating system software and the emulation

hardware. This board is the major interface between the emulation pod and the memory/analysis buses. The HP 64000 host processor can control the emulation processor "reset" and the bus activity stopping functions directly through this board. However, the two main functions of the control board are: to convert unique pod timing signals to compatible memory and analysis bus signals and to provide a channel to the pod for hardware configuration.

Figure 1-2. Emulation System Functional Block Diagram

The emulation system includes emulation memory implemented in static RAM. Emulation memory can be used in place of you target system ROM or RAM. Thus, program modules which will ultimately reside in your target system ROM may be developed and thoroughly tested, then permanently stored in ROM. The memory requirements of the emulation system are satisfied by the Static RAM Board(s). Each static RAM board has the capacity to hold a maximum of 128K words of random access memory. Options to these memory boards are available in which only a fourth or half of the board is loaded. These options are discussed in appendix H2 in the paragraph entitled "Configuration of the Memory Boards". Emulation memory may be configured to exist at any location in the memory address space of the emulation processor.

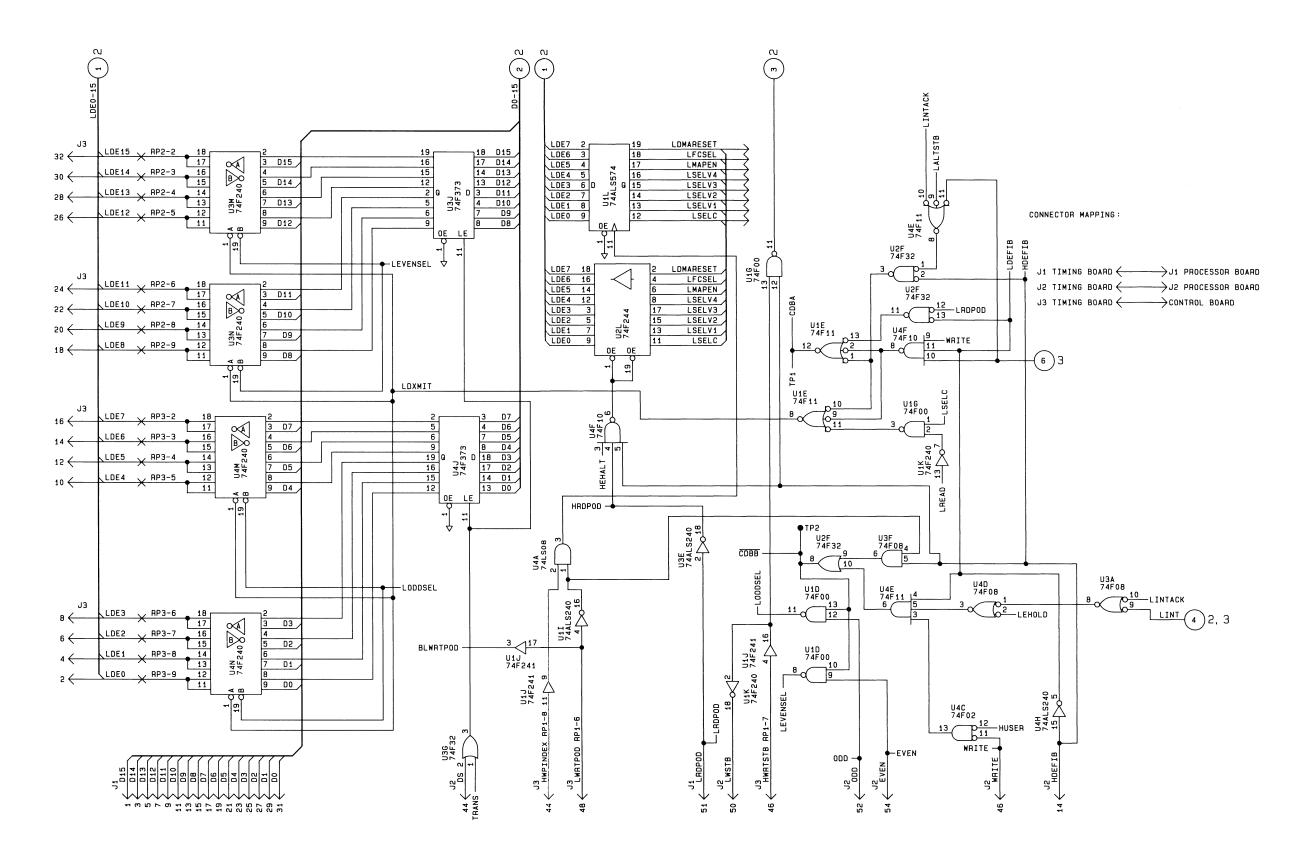

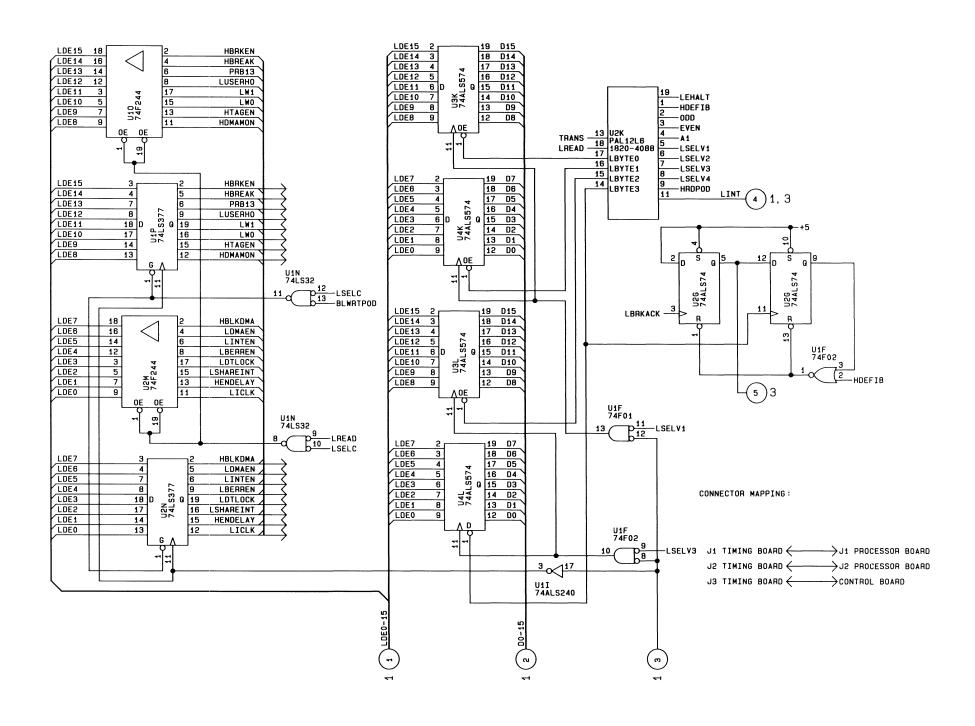

Emulation/user memory is controlled by the memory control board. The memory control board monitors the emulation memory bus to determine the type of memory that is to be accessed, (i.e., emulation memory or user memory). The memory control board is the major interface point from emulation memory to the HP 64000 operating system. The host processor communicates with the emulation processor by transferring data to and from emulation memory. Data transfer is accomplished through the memory controller board into the static RAM boards. In addition to providing an access port for the host processor into emulation memory, the memory controller contains a hardware mapper that is programmed to map the emulation processor memory address space into emulation/user/quarded and RAM/ROM memory spaces.

The emulator may be used for software development before your target system hardware is finished for out-of-circuit emulation. Program modules may be run by the emulator, and trace measurements may be made by the emulation system internal analysis board. The internal analysis board is the equivalent of a logic analyzer. It accepts your trigger specifications, then monitors the emulation analysis bus to determine if the specified event has occurred. When the event occurs, the analysis board makes a trace of 256 states of program execution and stores them in a trace memory. Trace data is available to the HP 64000 and is displayed on the development station screen. The analysis board is required for hardware breakpoints and for 'run\_until' action.

#### WHAT DOES THE EMULATOR ALLOW YOU TO DO?

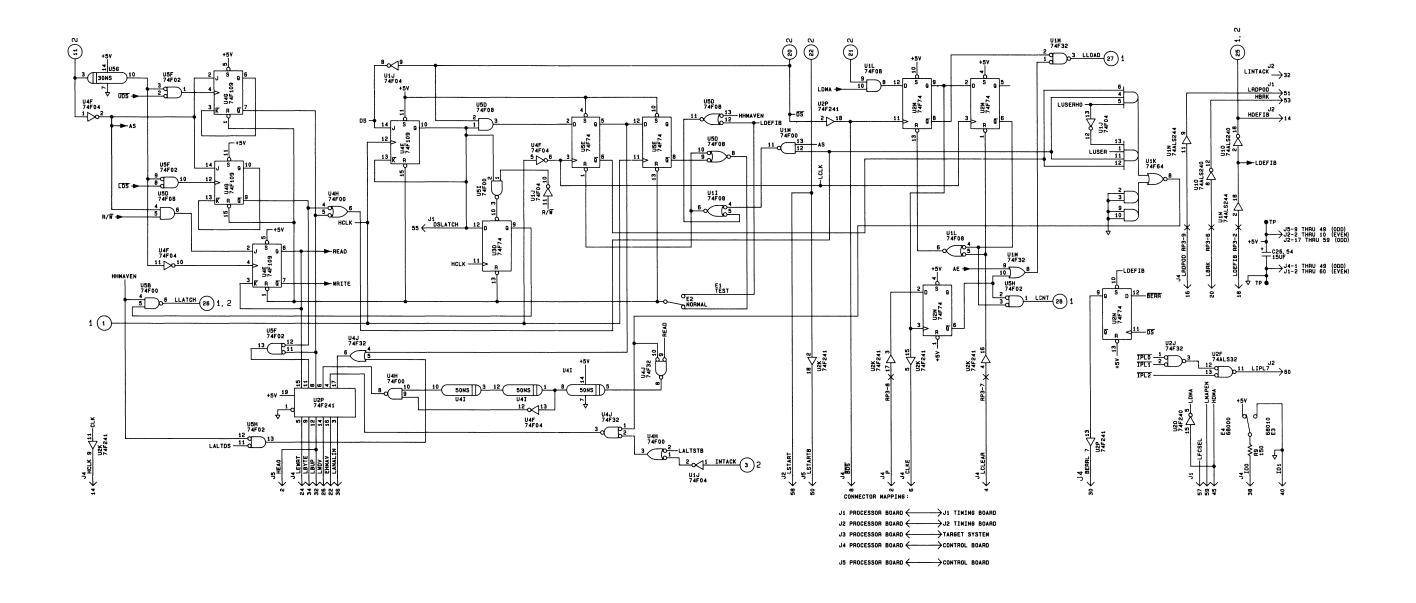

An emulator is just one of the tools available in a complete development system (see figure 1-3). The tasks facilitated by an emulator are software debug, hardware debug, and hardware and software integration.

## **How Are These Tasks Implemented?**

These tasks are implemented via the basic emulator features:

- Program Loading and Execution.

Your code developed on the HP 64000 using the editor, compilers, assembler, and linker can be loaded into memory by means of the emulator.

- Run/Stop Controls.

- Memory Display/Modification.

You can display locations or blocks of memory and modify any that can be changed.

Figure 1-3. Development System Tools

I/O Ports Display/Modification.

You can display I/O port address locations and values, and modify the values.

- · Global and Local Symbols Display.

- Internal Resource Display/Modification.

Allows you to display internal resources of the processor, such as registers, and to modify them, if desired.

Analysis (with optional internal analyzer board).

Allows you real time observation and display of activity on the emulation processor bus.

Program Stepping.

Allows you to execute code instruction-by-instruction, gaining access to the internal machine states between instructions.

Resource Mapping.

Allows you to map memory to emulation processor address space.

· Memory Characterization.

You can assign emulation memory ROM or RAM. You can test "ROM" code without using ROM hardware.

Breakpoint Generation.

You can transfer program execution to a monitor routine with the occurrence of a particular machine state or range of states.

· Clock Source Selection.

Provides internal clock generation, which can be used in lieu of your target system clock.

# WILL THE EMULATOR SYSTEM RUN INTERACTIVELY WITH OTHER HP 64000 SYSTEM MODULES?

The HP 64000 system allows the use of emulation and analysis features in an interactive manner between an emulator and another module; a module that could be another emulator or a state or timing analyzer. Interaction allows the integration of development work on multi-processor designs, or more elaborate and detailed analysis of a design, or both.

In particular, the capabilities that are supported include: simultaneous initiation of multiple measurements, using the results of one measurement to control another, and coordinating execution of a program with the initiation of a measurement.

#### WHAT EFFECT WILL THE EMULATOR HAVE ON YOUR PROGRAM?

The effect which the emulator will have on your program will depend upon the emulator operation which you select for execution at a particular time. The emulator will never permanently alter your program, but it may effect the execution of your program.

Depending upon the emulator operation selected for execution, the emulator will be operating in one of two modes: real-time or nonreal-time. "Real-time" in this case is not based on whether wait states are inserted; instead real-time refers to the continuous execution of your target system program without interference from the development system (except as instructed by you - and then, only for specific operations).

Interference occurs when a break to the emulation monitor program is initiated either by you or automatically. The emulation monitor is a program which allows you access to the internal registers and memory of the 680XX processor.

Whenever the emulator is running under control of the emulation monitor program it is no longer executing your program in real time. The emulation monitor program is described in more detail in later paragraphs in this section.

Features that cannot be performed in real-time mode without breaking into the emulation monitor program are the following:

Memory Accesses--display, list, load, modify, and store.

Register Accesses--display, list, and modify.

Symbol Accesses--display and list. For local symbols these commands will cause the present values to be displayed/listed for symbols in emulation memory. For symbols in target memory, present values are displayed as "\*\*\*\*".

The above features can be accessed while the emulator is configured for real-time mode by causing a break to the emulation monitor. This happens when you press the *break* softkey and the (RETURN) key, or when you attempt to access guarded memory, or when you create an analysis break condition, such as "trace break\_on meas\_comp" or "trace break\_on trigger".

Basically, features that can be performed in real-time mode are listed below. A more detailed explanation of these features is given in chapter 4.

run, some display, some modify, specify, execute,

trace, step, break, load trace, stop\_trace

#### WHAT IS HAPPENING WHILE YOUR PROGRAM IS RUNNING?

#### **During Normal Flow of the Program**

During the normal flow of your program, the emulation processor in the emulation pod generates address information for each cycle. One function of this hardware differentiates your target system and emulation resources based on the address. If the pod identifies a target system resource with