Publication No. 7380 May, 1978

# NOTICE

The material in this manual is for information purposes only and is subject to change without notice.

Floating Point Systems, Inc. assumes no responsibility for any errors which may appear in this publication.

### PROPRIETARY INFORMATION

This document contains proprietary information and is supplied for identification, maintenance, engineering evaluation or inspection purposes only and shall not be duplicated or disclosed without written permission of FLOATING POINT SYSTEMS, INC.

By accepting this document the recipient agrees to make every effort to prevent unauthorized use of this information.

Copyright © 1978 by Floating Point Systems, Inc. Beaverton, Oregon 97005

All rights reserved. No part of this publication may be reproduced in any form or by any means without permission in writing from the publisher.

Printed in USA

98 11 į 2-€ 3-€ 3-6 5--, 5 01-0 3-10 2-11 £1-13 3-13 Serverbor, Oregon 97005 21-5 3-15 es is publication

y any means

of the publisher.

# CONTENTS

|                                                                                                                                  |                                                                                                                                                                                                                                                                            | Daga                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| CHAPTER 1                                                                                                                        | INTRODUCTION                                                                                                                                                                                                                                                               | Page                                                                                                |

| 1.1<br>1.2<br>1.3<br>1.4<br>1.4.1                                                                                                | PURPOSE SCOPE GENERAL DESCRIPTION PHYSICAL DESCRIPTION Processor                                                                                                                                                                                                           | 1-1<br>1-1<br>1-2<br>1-5<br>1-5                                                                     |

| CHAPTER 2                                                                                                                        | SITE PLANNING AND PREPARATION                                                                                                                                                                                                                                              |                                                                                                     |

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.3<br>2.4                                                                              | INTRODUCTION PHYSICAL REQUIREMENTS Processor Power Panel Control Panel ELECTRICAL REQUIREMENTS ENVIRONMENTAL REQUIREMENTS                                                                                                                                                  | 2-1<br>2-1<br>2-1<br>2-2<br>2-3<br>2-4<br>2-5                                                       |

| CHAPTER 3                                                                                                                        | INSTALLATION AND CHECKOUT                                                                                                                                                                                                                                                  | •                                                                                                   |

| 3.1<br>3.2<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.5<br>3.5.1<br>3.5.2<br>3.6<br>3.6.1 | INTRODUCTION  ACCEPTANCE OF DELIVERY  UNPACKING  Outer Carton Inner Carton Verification  RACK INSTALLATION Rack Slides Power Panel Mounting the Processor Control Panel  SYSTEM INTERCONNECTION Power Panel to Control Panel Power Panel to Processor  START-UP Line Power | 3-1<br>3-1<br>3-1<br>3-2<br>3-2<br>3-3<br>3-5<br>3-8<br>3-9<br>3-10<br>3-10<br>3-11<br>3-13<br>3-13 |

| 3.6.2<br>3.6.3                                                                                                                   | Line Power  DC Power Supplies  Final Installation                                                                                                                                                                                                                          | 3-13<br>3-14<br>3-15                                                                                |

|                                                                                                                                                                                                                         |     |                                                                                                                                                                                                                                                                                                       | Page                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER                                                                                                                                                                                                                 | 4   | CHECKOUT AND TEST                                                                                                                                                                                                                                                                                     |                                                                                                                                               |

| 4.1.<br>4.2<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4                                                                                                                                                                         |     | INTRODUCTION HOST SYSTEM AP DIAGNOSTICS APTEST APPATH APARTH FIFFT                                                                                                                                                                                                                                    | 4-1<br>4-1<br>4-1<br>4-2<br>4-2<br>4-2<br>4-2                                                                                                 |

| CHAPTER                                                                                                                                                                                                                 | 5   | THEORY OF OPERATION                                                                                                                                                                                                                                                                                   |                                                                                                                                               |

| 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.3<br>5.3<br>5.3.1<br>5.3.2<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4<br>5.4.5<br>5.4.6<br>5.4.6<br>5.4.7<br>5.5.5<br>1.5.5<br>2.2<br>2.3<br>2.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3 |     | INTRODUCTION SYSTEM OVERVIEW Functional Units Data Paths Examples of Data Flow MEMORY Data Pad Main Data Table Memory ARITHMETIC Floating-Point Numbers Arithmetic Data Format Floating-Point Addition Floating-Point Multiplication FADD Hardware FMUL Hardware CONTROL Program Source Address S-PAD | 5-1<br>5-1<br>5-3<br>5-11<br>5-20<br>5-22<br>5-22<br>5-31<br>5-39<br>5-47<br>5-52<br>5-65<br>5-65<br>5-65<br>5-118<br>5-118<br>5-118<br>5-123 |

| CHAPTER                                                                                                                                                                                                                 | 6   | INTERFACES                                                                                                                                                                                                                                                                                            |                                                                                                                                               |

| 6. 2. 2<br>6. 2. 2<br>6. 2. 2<br>6. 2. 2<br>6. 3<br>6. 3. 4<br>6. 3. 4                                                                                                                                                  | .4. | INTRODUCTION GENERAL-PURPOSE INTERFACE Programmed I/O Direct Memory Access AP SPECIAL-PURPOSE (INTERNAL) INTERFACE Programming Considerations                                                                                                                                                         | 6-1<br>6-1<br>6-3<br>6-7<br>6-15<br>6-15                                                                                                      |

6-9

- -- 0

# ILLUSTRATIONS

| Figure No                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Page                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-2<br>1-3                                                                                                                                              | The Processor Typical AP-CT Configuration Power Panel Control Panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1-7<br>1-8<br>1-9<br>1-10                                                                                                                                                                                    |

| 3 <b>-</b> 2                                                                                                                                            | Rack Mounting Detail (Untapped)<br>Rack Mounting Detail (Tapped)<br>Bus Bar Bolting Detail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-6<br>3-7<br>3-12                                                                                                                                                                                           |

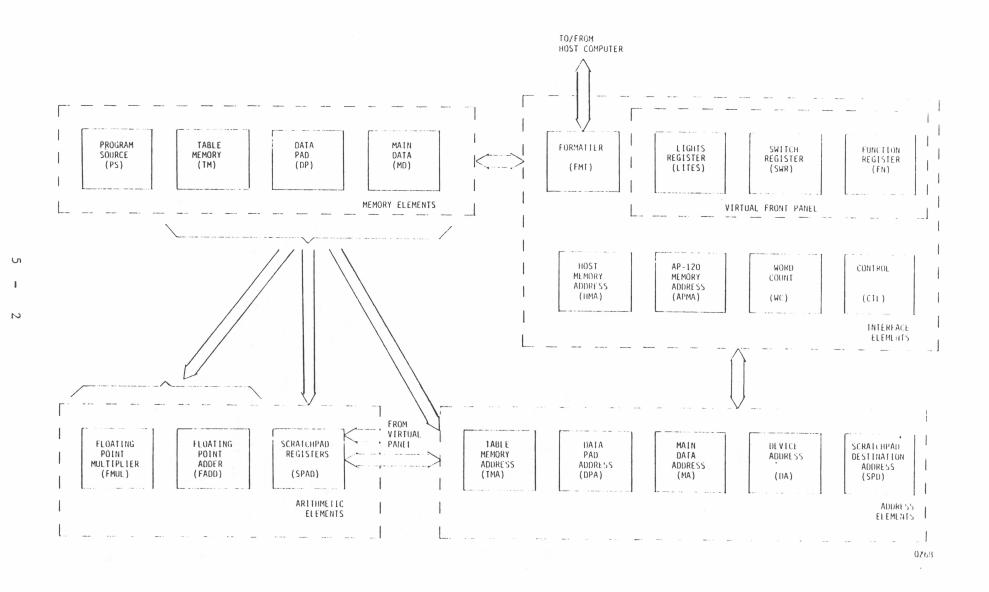

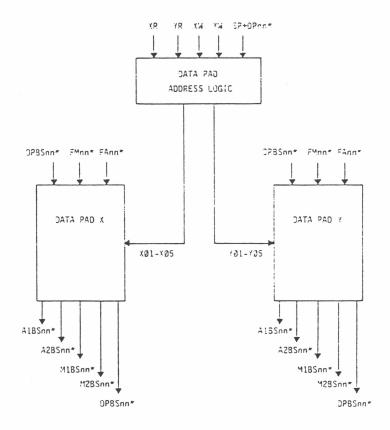

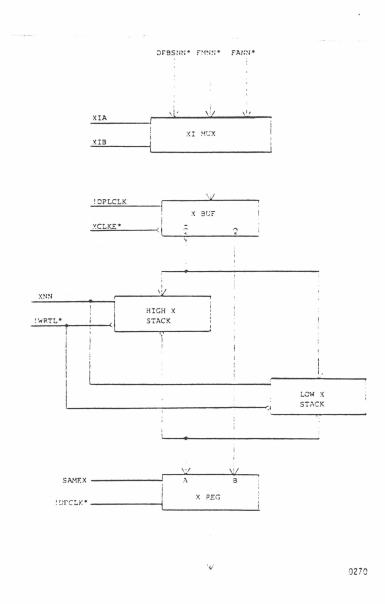

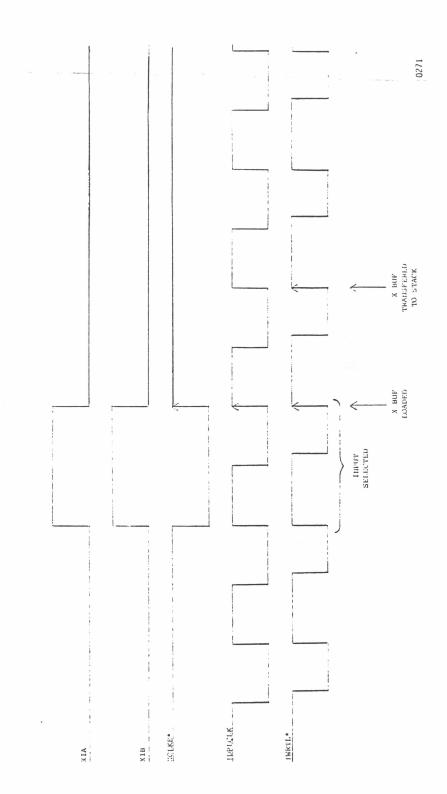

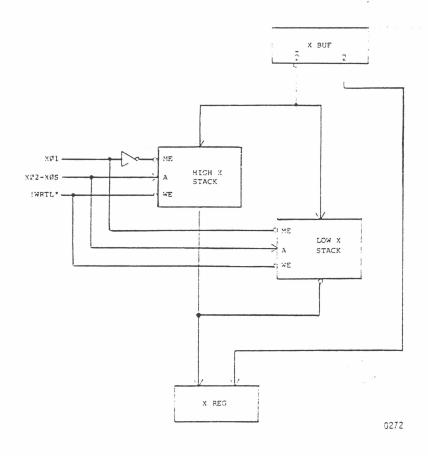

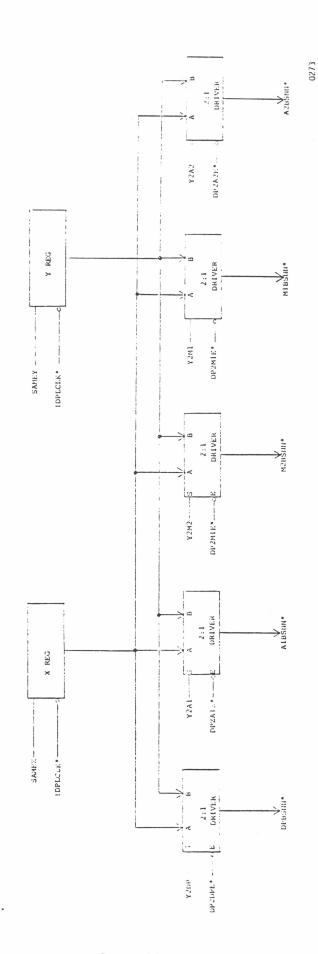

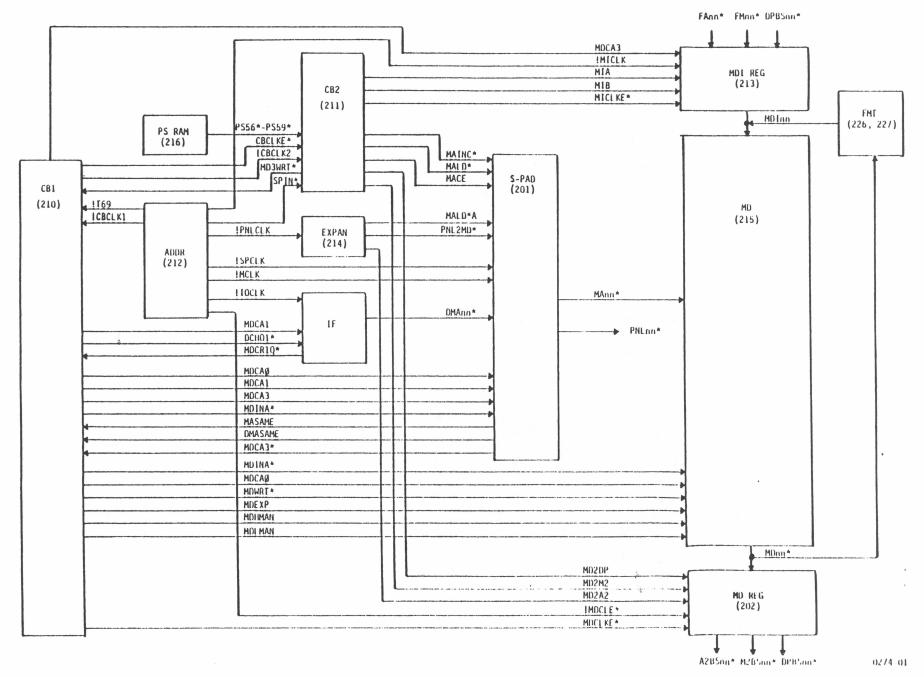

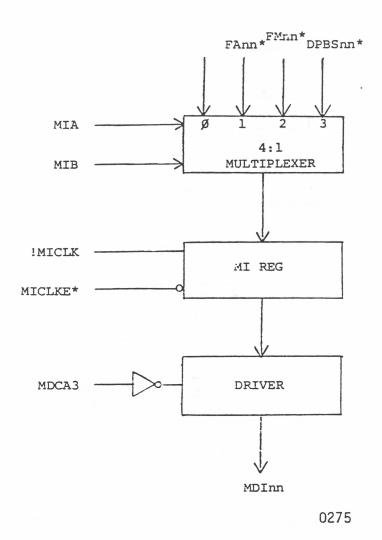

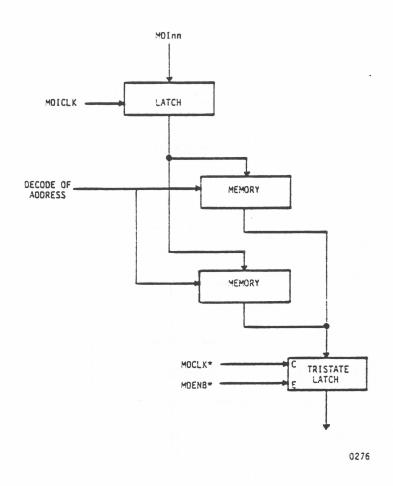

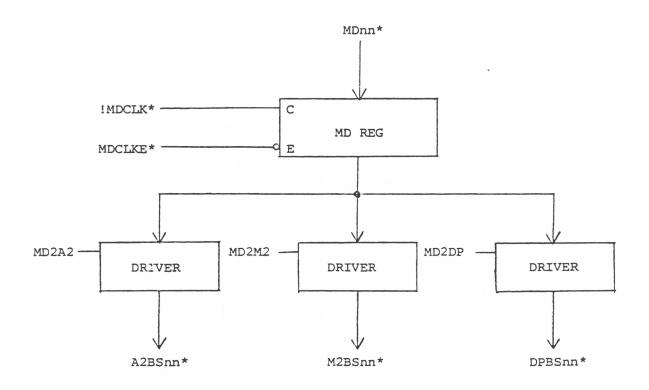

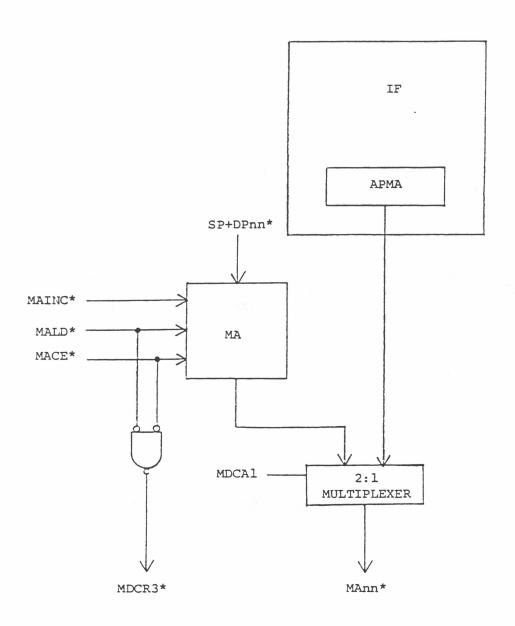

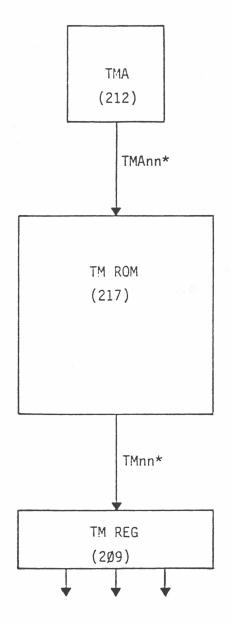

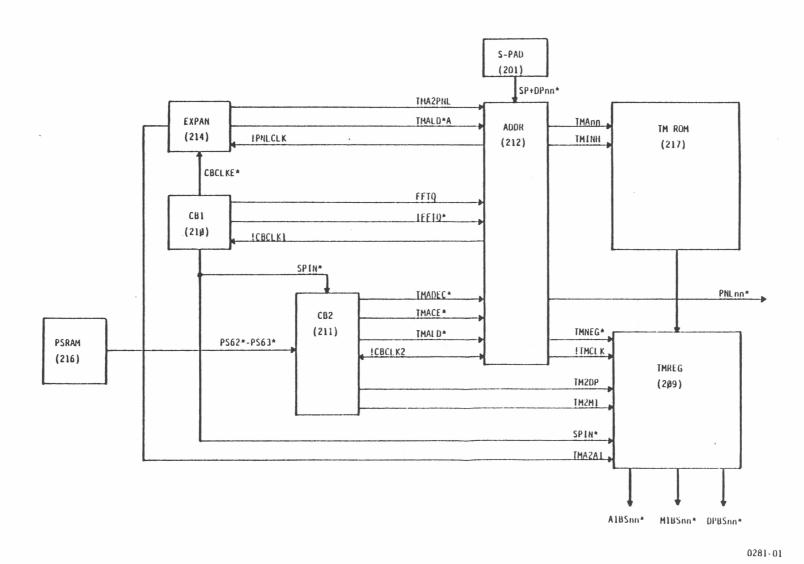

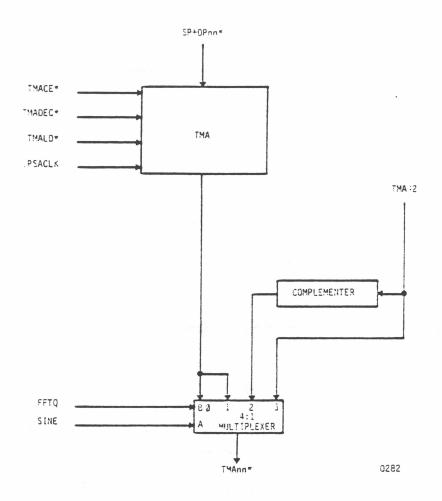

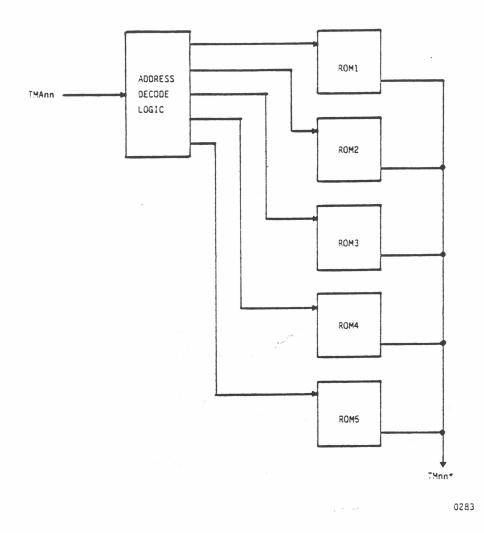

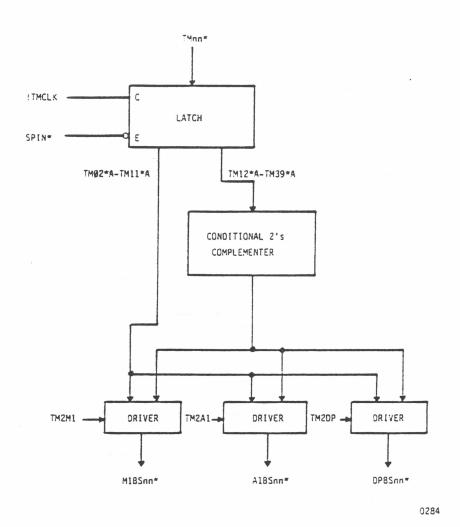

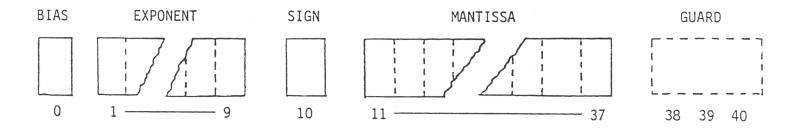

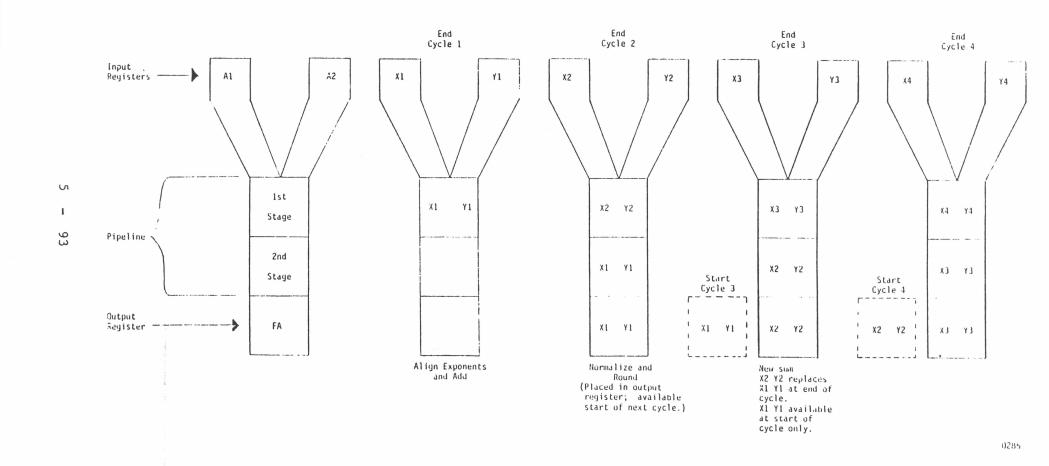

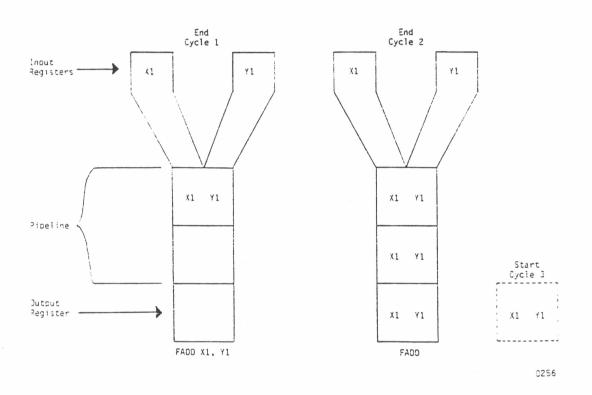

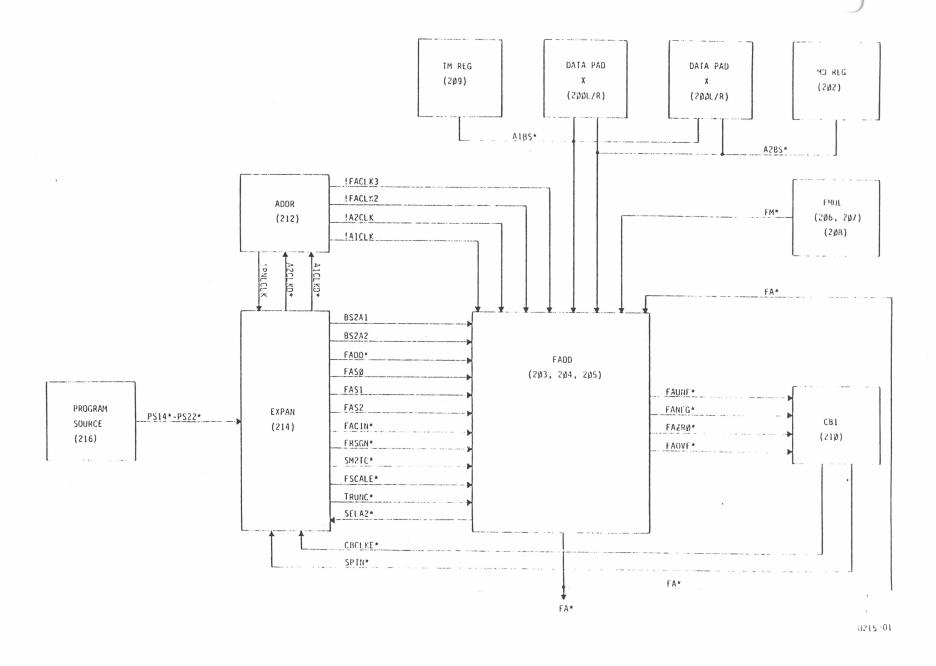

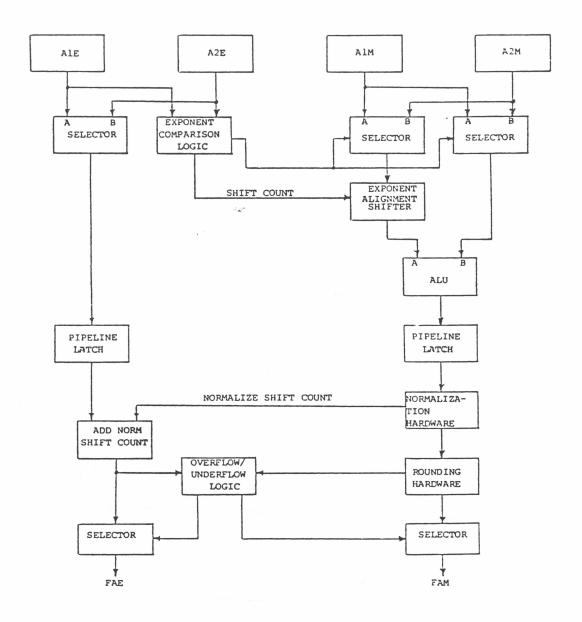

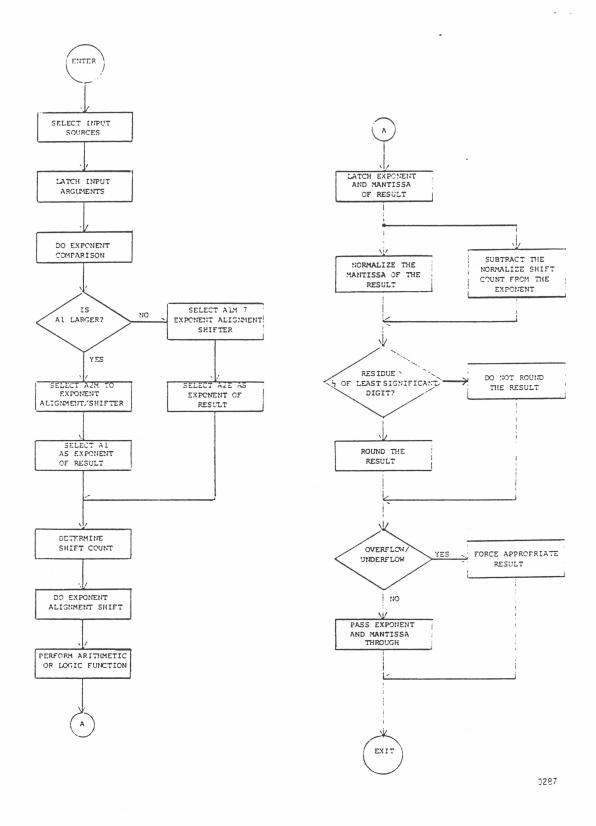

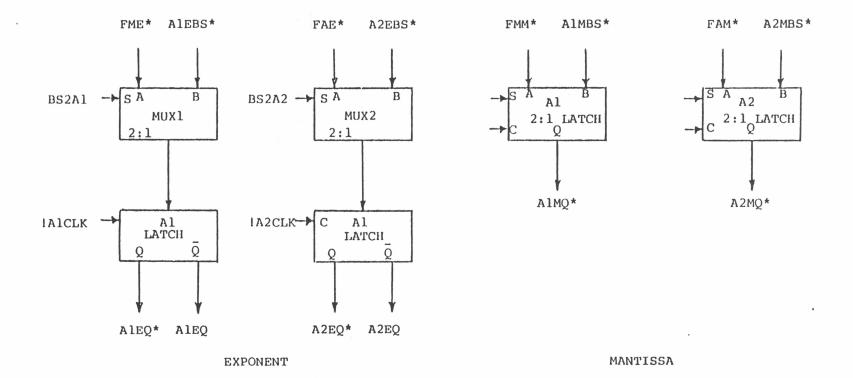

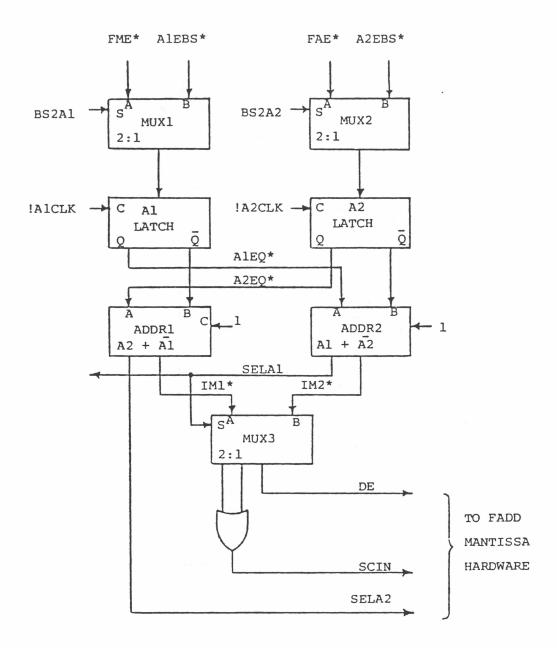

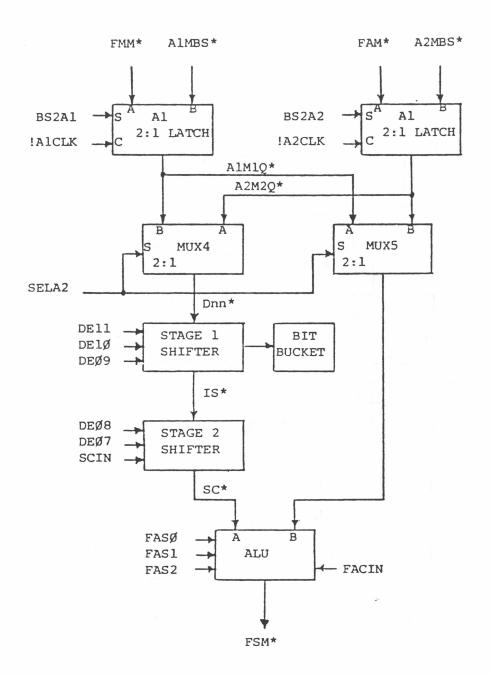

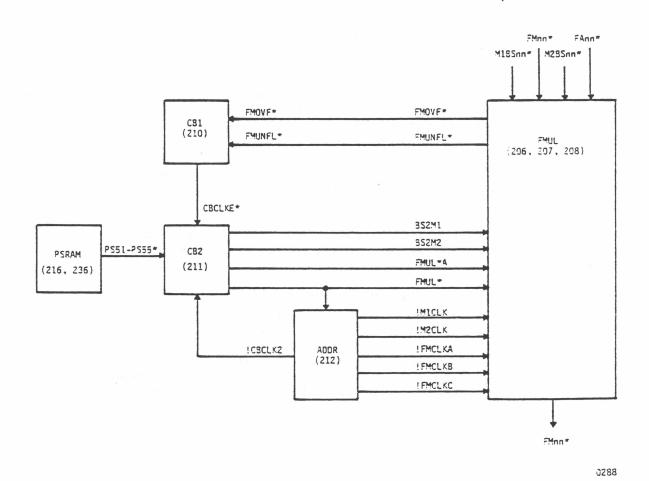

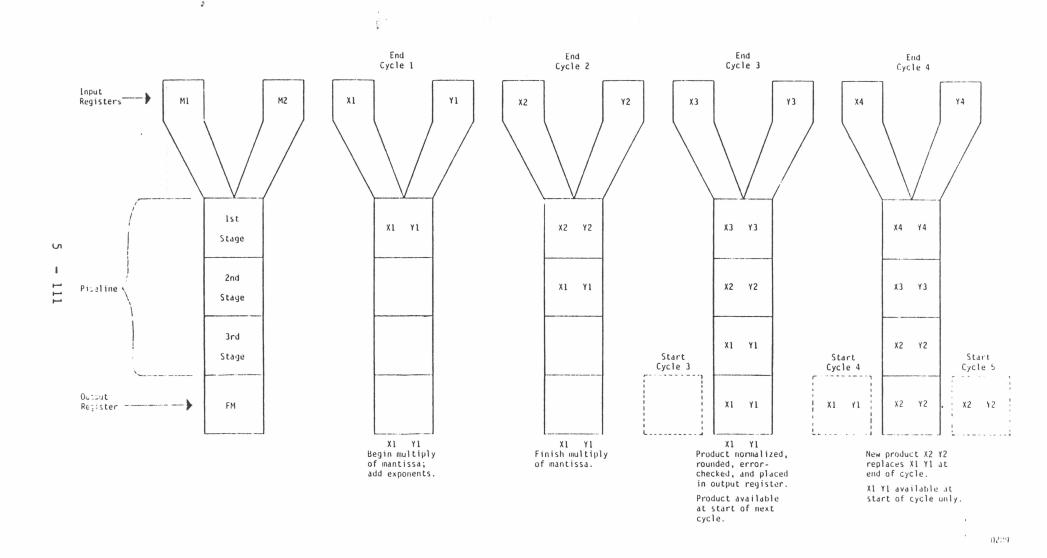

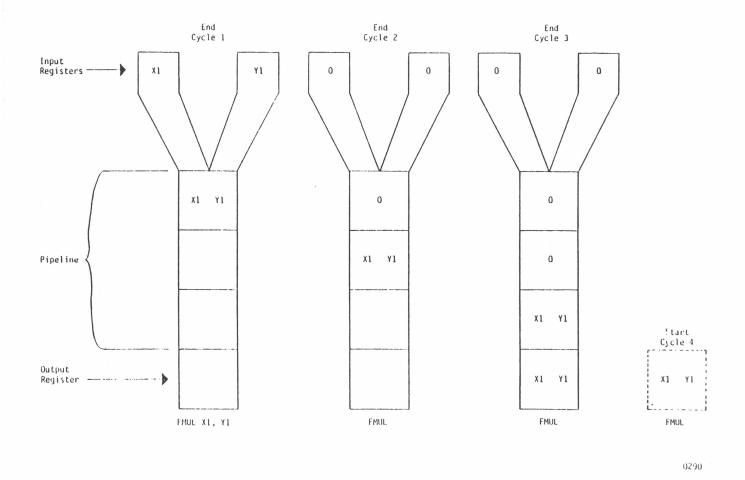

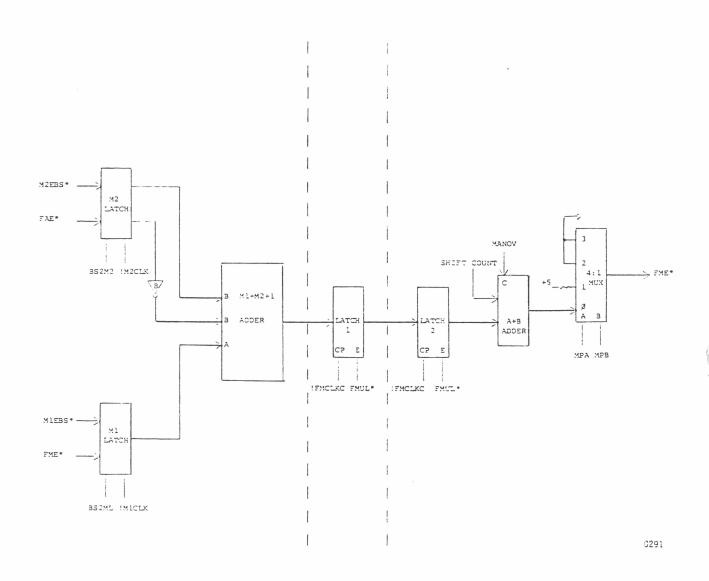

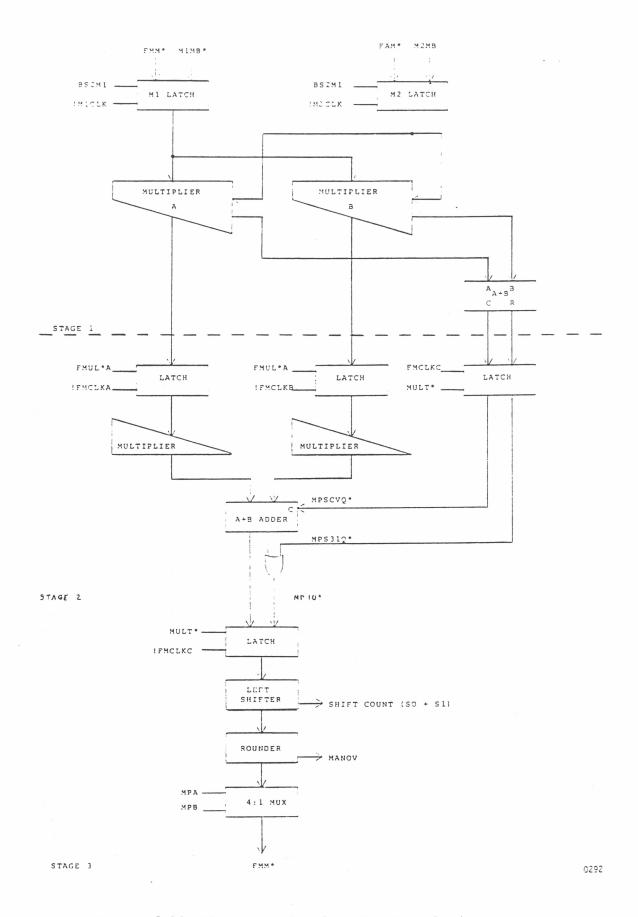

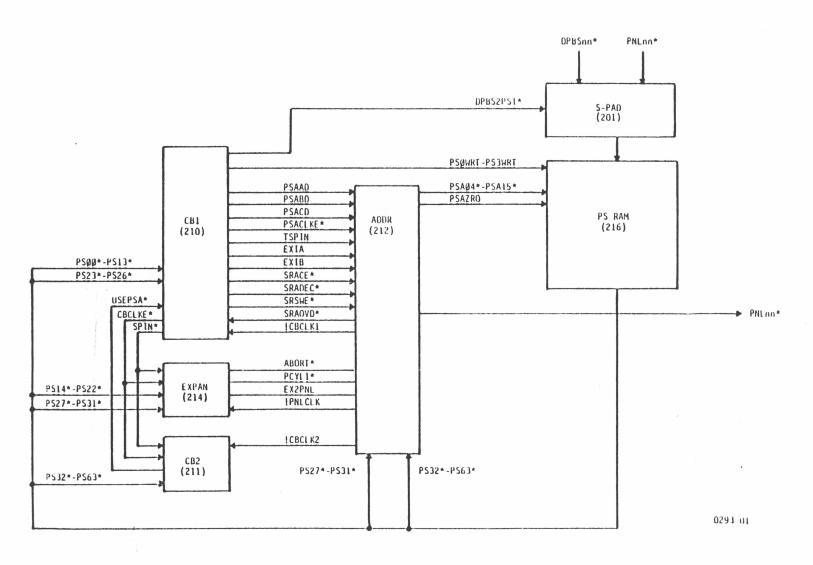

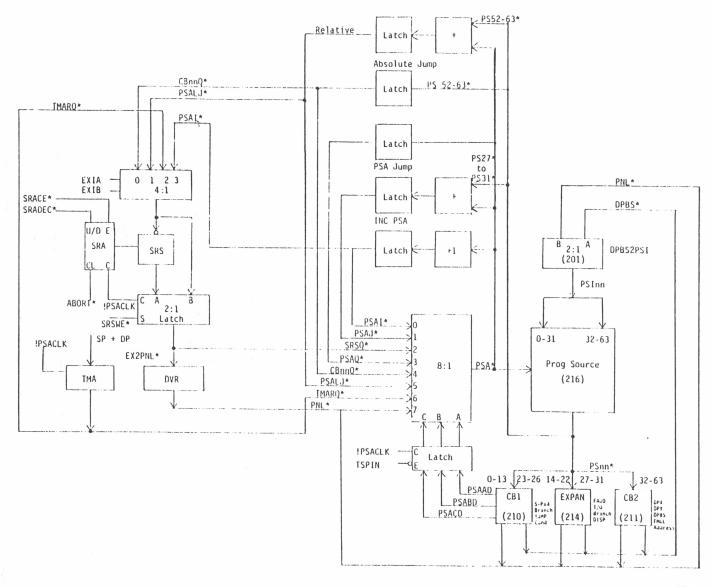

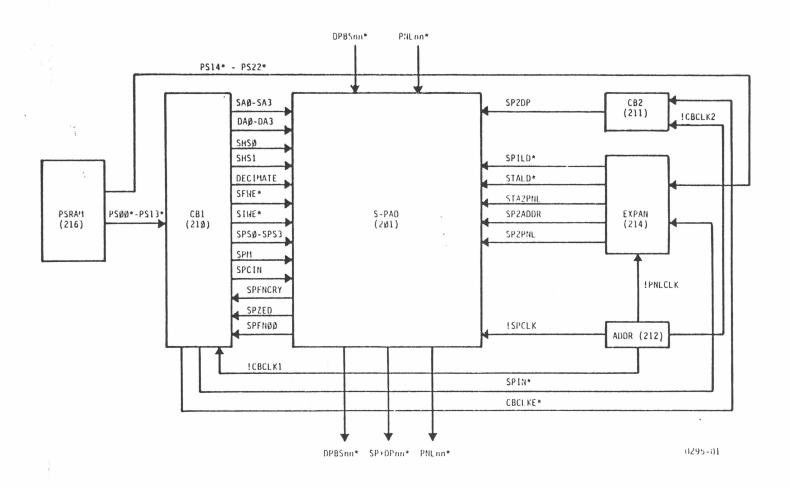

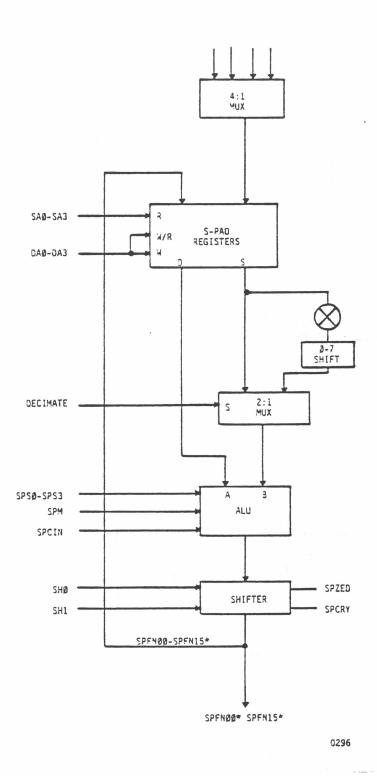

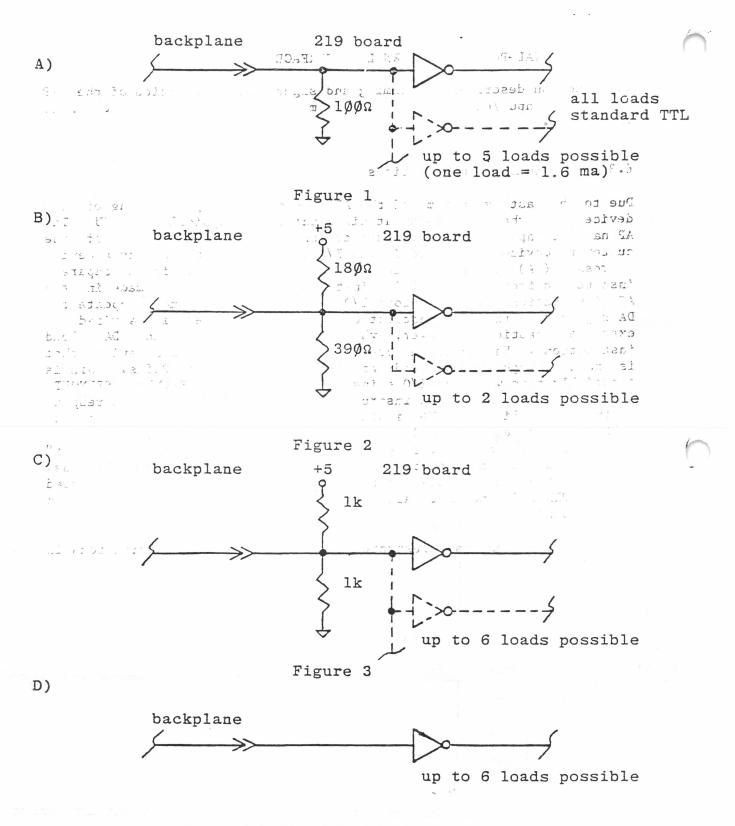

| 5-2 5-3 5-4 5-5 5-6 5-7 5-8 5-9 5-10 5-11 5-12 5-13 5-14 5-15 5-16 5-17 5-18 5-19 5-20 5-21 5-22 5-23 5-24 5-25 5-26 5-27 5-28 5-29 5-30 5-31 5-32 5-33 | AP - Simplified Block Diagram Block Diagram of DPX Timing Diagram of Writing DPX Detail Showing Stack Address Data Pad Output Logic Main Data System Interconnection Block Diagram MI Reg Block Diagram Main Data Memory Element Block Diagram Main Data Register Block Diagram Memory Address Simplified Block Diagram Table Memory System Block Diagram Table Memory ROM Interconnection Block Diagram Table Memory ROM Block Diagram Table Memory ROM Block Diagram Table Memory Register Block Diagram Table Memory Register Block Diagram Internal Floating-Point Format Adder (FADD) Pipeline Operation Pushing Values Through the Adder (FADD) Interconnection Block Diagram FADD Hardware Block Diagram Flow Chart AP Floating Adder Logic Floating Adder Input Latches Input Latches and Exponent Comparison Logic Exponent Alignment Logic Floating Multiplier Interconnection Block Diagram Multiplier (FMUL) Pipeline Operation Pushing Values Through the Multiplier (FMUL) Floating Multiplier Exponent Logic Floating Multiplier Exponent Logic Floating Multiplier Exponent Logic Floating Multiplier Mantissa Logic AP Block Diagram Program Source Address Logic S-PAD Interconnection Block Diagram Program Source Address Logic S-PAD Interconnection Block Diagram | 5-26<br>5-26<br>5-27<br>5-28<br>5-29<br>5-30<br>5-36<br>5-35<br>5-42<br>5-43<br>5-45<br>5-45<br>5-45<br>5-45<br>5-46<br>5-65<br>5-93<br>5-101<br>5-102<br>5-101<br>5-112<br>5-125<br>5-125<br>5-125<br>5-125 |

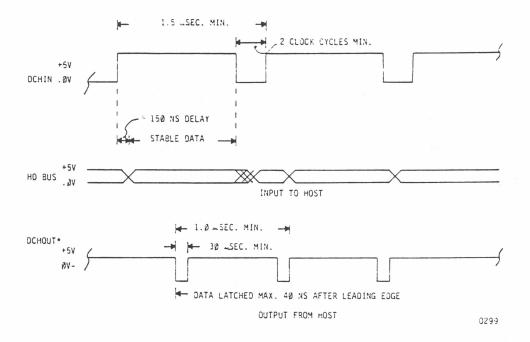

|                                                                                                                                                         | Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6 <b>-</b> 9                                                                                                                                                                                                 |

# TABLES

| Table                                                       | No. Title                                                                                                                                                                                                                                                                                                                         | Page                                                         |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| 1-1                                                         | Related Publications                                                                                                                                                                                                                                                                                                              | 1-1                                                          |

| 2-1                                                         | Electrical Specification Summary .                                                                                                                                                                                                                                                                                                | 2-4                                                          |

| 3-1<br>3-2                                                  | Hardware Shipment Checklist AP Mounting Hardware                                                                                                                                                                                                                                                                                  | 3 <b>-</b> 3<br>3 <b>-</b> 4                                 |

| 5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6<br>5-7<br>5-8<br>5-9 | Table Memory Addressing 4-Bit, 2's Complement, Binary Number System Range of Exponent Values Adding a 512 Bias Examples of Decimal Floating-Point Numbers Examples of AP Internal Floating-Point Numbers Table of Rules for Booth's Algorithm Table of Rules of 3-Bit Booth's Algorithm Octal Decode of the FADD and FADD1 Fields | 5-40<br>5-61<br>5-64<br>5-66<br>5-66<br>5-86<br>5-91<br>5-96 |

| 5-10<br>6-1<br>6-2<br>6-3<br>6-4                            | Octal Decode of the Al and A2 Fields  Controller to AP Signals  AP to Controller Signals  Host Data Bus                                                                                                                                                                                                                           | 5-96<br>6-10<br>6-11<br>6-12                                 |

### CHAPTER 1

### INTRODUCTION

#### 1.1 PURPOSE

The purpose of this manual is to provide the information necessary to understand, install, use and maintain the AP-CT. The array processor is a pipelined, parallel processor which can be interfaced to any one of a variety of host computers to provide a powerful, cost-effective processor for high-density, high-speed computation. Throughout the remainder of this manual, the AP-CT is referred to as the "AP".

### 1.2 SCOPE

This manual provides hardware information related to the AP. The manual first covers site planning and installation so that the AP can be properly installed and started up. The next section covers the check-out and test procedures that are used to verify proper AP operation. The bulk of the manual contains detailed theory of operation for the AP. This theory is written to the functional and schematic diagram level as an aid in understanding the AP hardware.

This manual is limited to discussions of the AP hardware. Additional information on the AP, such as software descriptions or interface descriptions, is available in the related manuals listed in Table 1-1 below. Any of these manuals can be ordered from Floating Point Systems, P.O. Box 23489, Portland, Oregon 97223.

Table 1-1 Related Publications

| Manual                                                             | Number                               |

|--------------------------------------------------------------------|--------------------------------------|

| Processor Handbook Programmer's Reference Manual Parts One and Two | 7259 <b>–</b> 02<br>7319             |

| APDBUG Manual AP Diagnostic Software                               | 7364 <b>-</b> 01<br>7284 <b>-</b> 02 |

| Manual AP Math Library Parts One and Two                           | 7288-03                              |

### 1.3 GENERAL DESCRIPTION

The AP is a pipelined, parallel processor. This processor contains two floating-point pipelined arithmetic elements, multiple memories and multiple buses. This structure greatly reduces the time required for processing information because it allows various system elements to handle tasks in parallel rather than sequentially.

The array processor may be functionally divided into five main units: memory, arithmetic, address, interface and control. Each of these five units is briefly described below:

## Memory

The AP contains four main memory elements that, because of the multiple bus structure, operate independently. Thus, simultaneous operation of the memories is possible. These four memories are:

\* program source

- stores the 64-bit microencoded instruction word

\* table memory

- stores frequently-used constants such as sines and cosines

\* data pad

- fast access memory composed of two elements (X and Y), each of which may be considered 32 individual accumulators

\* main data

extstyle ext

Arithmetic The AP contains three arithmetic elements, two of which are specifically designed for floating-point operations. These elements are:

ria de-

\* floating-point adder (FADD)

- a 2-stage, pipelined adder that performs arithmetic and logic operations. Because a new input may be entered into the pipeline stream every cycle, a new add can be started every 225ns although it takes 450ns to perform an add.

cha ex-

The results from the adder are normalized, rounded and error-checked.

er di che G a chacifa to Garc di the T

- \* floating-point multiplier (FMUL)

- a 3-stage, pipelined multiplier. Although it requires three cyles to complete the multiplication (675ns), the pipeline method permits a new multiply operation to be started every 225ns.

Multiplier results are normalized, rounded and error-checked.

- \* scratchpad ALU (SPAD)

- an ALU and sixteen 16-bit registers used to perform integer arithmetic and overhead functions in parallel with FADD and FMUL operation. Such overhead functions include: loop counting address indexing and control functions required by the program.

### Address

The AP contains five registers used for addressing the system's memories, peripherals and scratchpad (SPAD) registers. These five registers are:

- \* table memory address register

- serves as a pointer to the location containing the desired constant in table memory.

- register

- \* data pad address contains an address that is combined with an index value in the instruction word to access a specific location in the data pad memory.

- \* memory address register

- serves as a pointer to the desired location in main data memory.

- \* device address register

- contains the address of the external device to be used with the AP.

- \* scratchpad destination

- contains the address of the scratchpad register that is to receive the output of the scratchpad ALU.

Interface

The AP contains a number of interface elements. Three of these elements are registers that make up a "simulated" or "virtual" front panel. The five remaining elements are used when performing DMA transfers between AP and the host computer. The interface elements are:

- \* switch register

- used by the host to load data and/or addresses into the AP. This register is similar to a normal computer switch register except that information is loaded or read under computer control, rather than entered by means of front panel switches.

- \* lights register

- simulates front panel lights in order to display the contents of internal AP registers.

- \* function register

- provides the remaining front panel controls required by a computer such as stop, start, deposit, examine, step, continue, etc.

- \* formatter

- converts the input word to the 38-bit floating-point format required by the AP and vice versa. Typically, the formatter supports four different formats, as determined by the host computer.

- \* host memory address register

- serves as a pointer to host computer memory locations involved in DMA transfers. This register always operates in either autoincrement or auto-decrement mode.

of 12 Figure Lessor Li2-1/4 Lessor Lessor Lessor Lessor Lessor Lessor Lessor

- \* array processor memory address register

- serves as a pointer to the AP main data memory locations involved in DMA transfers. This register always operates in either auto-increment or autodecrement mode.

- \* word count register

- keeps track of the number of words transferred during a DMA operation.

- \* control register

- used for control and status information when performing DMA transfers.

Control

The AP contains a number of control elements that ensure the processor operates properly. Such control elements include clocking circuits, status registers, control gating, etc. It is important to remember that the AP is a synchronous processor and therefore, control elements are extremely important.

Although programming information is not included in this manual, it should be noted that the AP uses a 64-bit instruction word and a 38-bit floating-point data word. The data word consists of a 10-bit exponent and a 28-bit mantissa. For more information on instruction and data word formats, refer to the AP Processor Handbook.

### 1.4 PHYSICAL DESCRIPTION

This section provides a detailed description of the physical characteristics of the three equipment groups that comprise the AP. The three equipment groups are physically separate pieces of hardware (each with a separate serial number tag) and will subsequently be called the processor, the power panel, and the control panel.

### 1.4.1 Processor

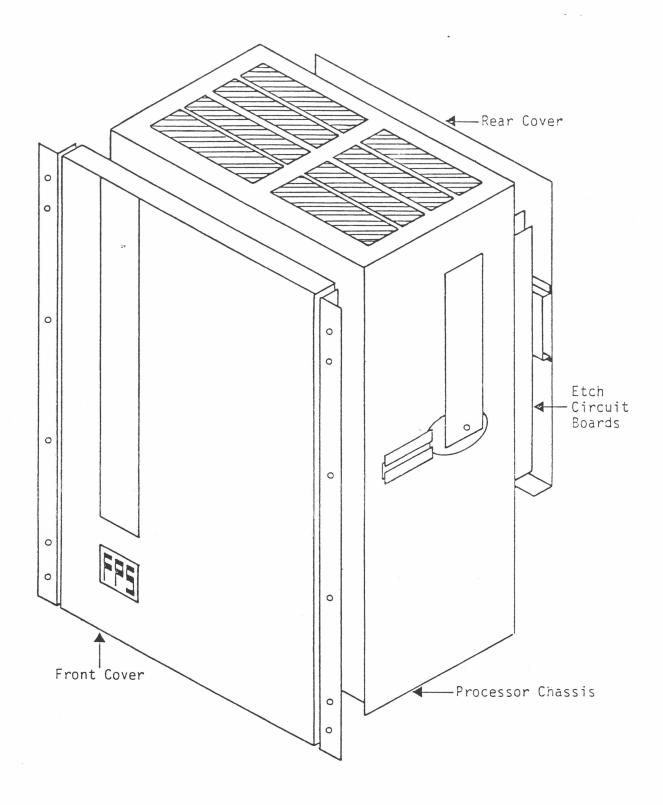

The processor consists of a 31-slot card cage assembly, a minimum of 22 etch circuit boards (ECB), a front cover and a rear cover. (See Figure 1-1.) Assembled (ECB, front and rear covers in place), the processor is physically 62.23 cm. (24-1/2 inches) high, 31.12 cm. (12-1/4 inches) deep, and 44.78 cm. (17-5/8 inches) wide. The AP is designed to mount in a standard 48.78 cm. (19- inch) EIA. Thus, the width measurement incorporates the distance the rack slides extend from the card cage chassis. Figure 1-2 illustrates a typical AP configuration.

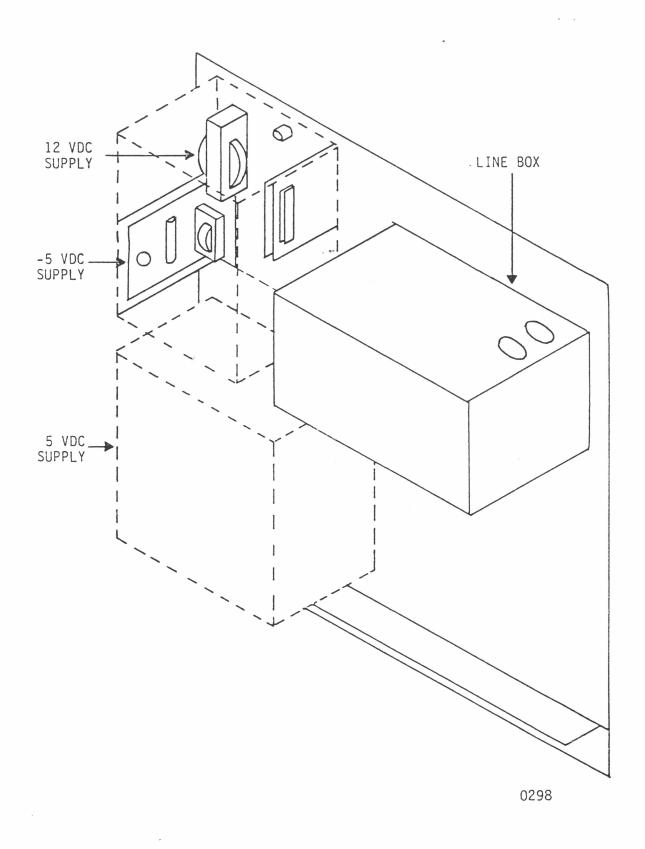

### 1.4.1.1 Power Panel

One 5V/120A or 150A DC power supply, a +12V/3A DC power supply, and a -5V/3A DC power supply are to be mounted on the power panel. A line box is already mounted. Figure 1-3 is a visual presentation of the power panel. The line box houses a terminal board, a power relay, and the line filters. When assembled, the power panel is 52.70 cm. (20-3/4 inches) high, 48.18 cm. (18-31/32 inches) wide, and 15.56 cm. (6-1/8 inches) deep. The power panel specifies the line voltage to be used.

The power panel, like the processor, is designed to be mounted in a 48.26 cm. (19-inch) EIA rack. The standard installation has the power panel occupying the back of the rack immediately behind the processor. The power panel mounts directly on the rack. This panel is also hinged to allow access to the power supplies for maintenance without removal of the power panel from the rack.

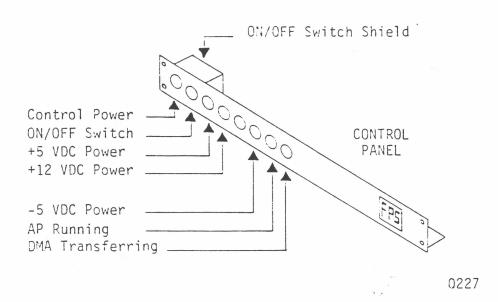

### 1.4.1.2 Control Panel

The control panel consists of the power ON/OFF switch, the power status indicators, and the processor status indicators. See Figure 1-4. Physically, the control panel is  $4.29~\rm cm$ .  $(1-11/16~\rm inches)$  high  $(4.45~\rm cm$ .  $[1-3/4~\rm inch]$  rack increment),  $48.18~\rm cm$ .  $(18-31/32~\rm inches)$  wide, and  $4.45~\rm cm$ .  $(1-3/4~\rm inches)$  deep. This subassembly is also designed to be rack-mounted and may be mounted at the front of the rack (with the processor) or at the rear of the rack (with the power panel). It should be noted that the control panel voltage must match the power panel voltage as noted on the serial number tag.

0181

Figure 1-1 The Processor

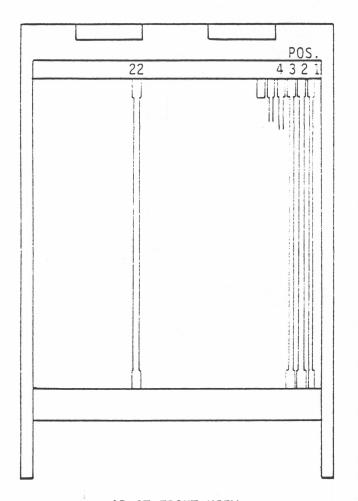

| POS.                                                                                                                             | BOARD                                                                                                                                                   | TYPE                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23-31 | 263<br>227<br>226<br>215<br>216<br>201<br>212<br>214<br>210<br>211<br>202<br>217<br>209<br>213<br>200<br>203<br>204<br>205<br>206<br>207<br>208<br>NULL | PDP INTERFACE  FORMATTER  MAIN DATA PROGRAM SOURCE SCRATCH PAD TM ADDRESS REGISTERS INST. & FRONT PANEL REG. DEST. ADDRESS REGISTERS DATA PAD ADDR. REGISTER DATA MEMORY OUT. REGISTER TM ROM TM OUTPUT REGISTER DATA MEMORY IN. REGISTER DATA PAD RIGHT DATA PAD LEFT  FLOATING POINT ADDER  FLOATING POINT MULTIPLIER |

AP-CT FRONT VIEW

0297

Figure 1-2 AP-CT Configuration

Figure 1-3 Power Panel

Figure 1-4 Control Panel

### CHAPTER 2

### SITE PLANNING AND PREPARATION

### 2.1 INTRODUCTION

This section provides a summary of the equipment characteristics of the AP essential for pre-installation site planning and preparation.

### 2.2 PHYSICAL REQUIREMENTS

The physical requirements that must be considered for installation are the space to be occupied, ventilation, and the system connections that are required. The AP is designed to be rack-mounted in a standard 48.26 cm. (19-inch) EIA rack with a rack depth of between 50.80 and 63.50 cm. (20 and 25 inches). Floating Point Systems recommends that the user allow 76.20 cm. (30 inches) of free vertical rack space for vertical installation of the AP. FPS recommends that the user allow 36.83 cm. (14-1/2 inches) of free vertical rack space for installation of an AP modified for horizontal installation.

### 2.2.1 Processor

The AP physically requires 62.23 cm. (24-1/2 inches) or vertical rack space when mounted vertically; it requires 36.83 cm. (14-1/2 inches) when mounted horizontally. It will be mounted in the forward portion of the rack on rack slides. A minimum of an additional 4.45 cm. (1-3/4 inches) above the processor (in the vertical plane) are necessary for proper air circulation when the AP is mounted vertically. This can be be occupied by the control panel, blank panels, or other equipment which does not fully occupy the space adjacent to the AP.

Five position, tilt-type rack slides are used on the processor to allow access to the backplane, etch circuit boards, fans, and connectors during installation and maintenance. The rack slides and hardware (nuts, bolts, etc.) are included for mounting in racks from 50.80 to 63.50 cm. (20 to 25 inches) deep.

The processor must interface to the host processor via an interface cable. This interface cabling is, in most cases, supplied by Floating Point Systems. It is necessary that the processor be physically located in a place that will allow the interface cabling to connect from the host processor to the AP. Because the processor is mounted on rack slides, it is recommended that an extra 63.50 cm. (25 inches) of slack be left in this cabling to allow the processor to operate in its fully-extended position. As examples of typical interface cabling lengths, the Nova/Eclipse interface cabling provided by FPS is 3 m., 4.80 cm. (10 feet) and the Unibus cable for the PDP-11 series is 1 m., 52.40 cm. (five feet) in length.

### 2.2.2 Power Panel

The power panel mounts directly on the rack immediately behind the processor assembly. As specified in Section 1.2.3.3, the power panel requires 52.70 cm. (20-3/4 inches) of free vertical rack space in the rear of the rack. If the rack is less than 50.80 cm. (20 inches) deep, it is possible that there will not be enough clearance between the processor and the power panel to allow the power panel to be mounted immediately behind the processor. Consideration must also be given for the interconnection of the power panel to the processor, to the control panel, and to the electrical service.

Between the power panel and the processor, there are three interconnecting cables: the four separate +5 VDC cables 5 VDC, the control, the +12 VDC and the -5 VDC, and the AC fan voltage. The +5 VDC cabling provided is 1 m., 42.24 cm. (56 inches) in length and connects from the +5 VDC/150A power supply on the power panel to the front of the processor. The +12 VDC and the -5 VDC cabling is 1 m., 6.68 cm. (42 inches) long and connects to the rear of the processor. It should be noted that the processor is also capable of sliding forward 50.80 cm. (20 inches) on its rack slides. Thus, the physical layout of the power panel with respect to the processor must leave enough slack in the cabling to allow for this 50.80 cm. (20 inches) of travel. See FPS Schematic #680-2150-102 for an interconnection block diagram.

There are two cables from the control panel going to the power panel. One cable is 1 m., 6.68 cm. (42 inches) long, lights the control power indicator and connects the ON/OFF switch. The other is 1 m., 6.68 cm. (42 inches) long for the DC supply and function indicators.

The cord provided to connect the power panel to the electrical service is 1 m., 82.88 cm. (six feet) in length. The cable orginates at the line box on the power panel and utilizes a standard three-prong plug to connect to the service.

## 2.2.3 Control Panel

The two primary physical considerations in the placement of the control panel are its physical size and its cabling requirement. The control panel is to be mounted directly on the rack and requires a 4.45 cm. (1-3/4 inch) rack increment. Mounting hardware is included. The control panel may be either mounted in the front or the rear of the rack. Further, it may be mounted above or below the processor or power panel. When front mounted, the control panel assures free-air for one end of the processor and the status of the AP is visible. Rear mounting minimizes total rack space and reduces the chances of accidentally switching the AP power off.

There are two cables at the control panel. One contains the power and processor status. The other contains the ON/OFF control voltage. The physical requirements for the ON/OFF control cabling are defined in Section 2.2.2. The power and processor status cabling originates at the processor and routes by the power panel, terminating at the control panel, and is 1 m., 6.68 cm. (42 inches) in length. The ON/OFF control cabling originates at the control panel and terminates at the line box on the power panel.

### 2.3 ELECTRICAL REQUIREMENTS

The AP can be supplied in three different power configurations as specified in Table 2-1. The total power required for the AP system is approximately 1200 watts (the actual power required is configuration-dependent), and a low impedance service is advised. FPS strongly recommends that the AP be given its own electrical service and the service should be rated for 20 amperes (or 10 amperes for 220V or 240V applications) in order to provide a low impedance source. This low impedance source is critical for proper operation of the peak rectifying supplies used.

Table 2-1 Electrical Specification Summary

| Voltage | Range   | Minimum<br>Line<br>Voltage | Frequency |     | Fu<br>Line | Control |

|---------|---------|----------------------------|-----------|-----|------------|---------|

| (VRMS)  | (VRMS)  | (P-P)                      | (Hz)      | (A) |            |         |

| 115     | 100-125 | 280                        | 50-60     | 20  | 15         | 250ma   |

| 230     | 200-240 | 560                        | 50-60     | 10  | 10         | 1       |

If the customer specifies the 115V power option, the AP will come with a 1 m., 82.88 cm. (six-foot) power cord with a U.S. standard three-wire (with ground) male cord cap. For 220V applications inside the U.S., a 15A U.S. standard 220V male cord cap is supplied on the 1 m., 82.88 cm. (six-foot) power cord. For European applications, a 15A male IEC cord cap is supplied on the 1 m., 82.88 cm. (six-foot) power cord.

### 2.4 ENVIRONMENTAL REQUIREMENTS

Temperature, humidity, vibration, and dust are the four environmental factors that should be considered prior to the installation of the AP.

FPS specifies the AP to operate in environments of 10 degrees C to 40 degrees C. This temperature specification should be derated one degree C per 2500 feet (762 m) above sea level for 60 Hz operation and 5 degrees C for 50 Hz operation. This temperature specification (10 degree C to 40 degree C) is at a relative humidity of 0 percent to 90 percent. If the user's environment has the possibility of varying outside of this temperature/humidity specifications, some type of environmental conditioning is recommended.

With respect to vibration, typical data processing environments suitable for commercial computers are adequate for the AP. The AP, as shipped, is equipped with an air filter that filters the dirt particles out of the incoming cooling air. This air filter allows the AP to be installed in most environments. If an extremely dirty environment is encountered, it may be necessary to clean the filter daily (or more often) or provide an alternate means of air filtering such as an electrostatic air cleaner in proximity to the AP.

### CHAPTER 3

#### INSTALLATION AND CHECKOUT

### 3.1 INTRODUCTION

This section provides the user with the information necessary to accept delivery, unpack, install, connect, and start up the AP.

### 3.2 ACCEPTANCE OF DELIVERY

The acceptance of delivery of the AP, unless otherwise negotiated, occurs at the factory. For insurance purposes, however, the shipping carton that contains the AP should be carefully examined for apparent damage prior to signing the carrier's receipt of delivery. If there is damage to the packing carton, this should be noted on the shipping receipt prior to signing.

### 3.3 UNPACKING

All of the AP hardware and one complete set (more if ordered) of the hardware documentation are shipped in a single carton. Note, however, that documentation will not be shipped until FPS receives a completed non-disclosure form from the customer stating that documentation will be used only for maintenance purposes. The shipping carton weighs approximately 67.95 kilograms (150 pounds) and is 83.82 cm. (33 inches) long, 68.58 cm. (27 inches) wide, and 68.58 cm. (27 inches) high. The AP hardware inside this carton is separately boxed to ensure against damage during shipment. The packaging cartons and packing materials should be saved in case it is necessary to reship the equipment.

#### 3.3.1 Outer Carton

Prior to opening the container, the packing slip affixed to the exterior of the carton should be removed and placed in a secure location. This packing slip is on the top of the carton and will be used to verify that no shortages exist in the shipment.

After removing the packing slip, the top of the packing carton should be opened, the documents removed and placed with the packing slip, and the upper shock pad (rectangular white plastic foam liner) removed. It is also possible that the I/O adapter (not used on all units) or the host-to-AP interconnect cable, if provided by FPS, or both, should be removed at this point. If so, its presence will be obvious; if not, it is packed elsewhere. The documentation will be checked later to ensure a complete shipment.

### 3.3.2 Inner Cartons

Open the inner carton and remove the two equipment packages and the bubble-packed control panel. Remove the smaller package first. larger of the two equipment packages contains the processor, and smaller, the power panel. Open the processor package, slide the processor out, and remove the plastic bag from around the processor. If the host-to-AP interconnect cable or the I/O adapter was to be provided by FPS and was not found above (see Section 3.3.1), it will be found in the processor package. Remove the processor, host-to-AP interconnect, and the I/O adapter to a secure area. Place the plastic bag and the packing material into the package. Open the power panel package and slide out the power panel and rack slides. Remove the rack slide box from the packing strips around the power panel. The power panel should then be placed with the processor in a secure area. Unwrap the bubble-pack from around the control panel and unbox the rack slides. Place the packing strips and bubble-pack inside the empty power panel package. Replace both the processor package and the power panel package in the inner carton. Replace the upper shock pad and close the outer carton.

### 3.3.3 Verification

After unpacking, both the hardware and the documentation should be checked to ensure that a complete shipment was made. The packing slip should be checked to see that all the specified items arrived in the packing carton. The packing slip reflects the shipment of the equipment as specified in the customers purchase order. It should be noted that if the purchase order specifies such things as the interface, the size of main data, or the size of program source, that these are etch circuit boards that are internal to the AP chassis and have been installed in the processor at the factory prior to shipment.

With the documentation package is a sheet of paper titled "AP Check List for Documentation". The actual documentation received should be checked piece-by-piece against this sheet to ascertain the presence of all specified documentation. If shortages do exist, these should be noted by name as specified on the checklist and FPS should be notified immediately.

At the shipping-dock level, verification of hardware shipment should be limited to the major functional units as specified in Table 3-1. The processor, the power panel, and the control panel each have a serial number tag affixed to them. Located at the end of the serial number is a letter ("A" for the processor, "B" for the power panel, and "C" for the control panel) added to help identify these subassemblies. The presence of the three subassemblies should be verified.

Table 3-1 Hardware Shipment Checklist

|   |                     | <br>    |        |

|---|---------------------|---------|--------|

| 1 | Functional unit     | Present | Absent |

| 1 | Processor           |         |        |

| 1 | Power Panel         |         |        |

| 1 | Control Panel       |         |        |

|   | Rack Slides         |         |        |

| 1 | Host-to-AP Cable(s) | 277     |        |

|   | I/O Adapter*        |         |        |

| 1 | Extender Card**     |         |        |

|   |                     |         |        |

<sup>\*</sup> Not necessary on some Host CPU's

The presence of the rack slides, the host-to-AP interconnect cable (if supplied by FPS), and the extender card (this is sent with the first AP supplied) should be verified. Again, if shortages exist, these should be recorded and FPS should be notifed immediately.

The power panel and the control panel should be checked to verify that they operate on the same AC input power, and that this is the power option ordered. The three power options available are specified in Table 2-1. The serial number tag on the power panel and the control panel have a section labeled "volts". These should be checked to ensure that they both specify the same voltages, and that this voltge option is the one that was ordered.

## 3.4 RACK INSTALLATION

The rack installation of the AP follows a logical sequence. After checking the area, set aside for the AP installation to make sure it is clear and free of obstruction. The first step is to locate and mount the rack slides. Next, the power panel is located and mounted on the back of the rack. Then, the processor is inserted into the rack on its rack slides. Finally, the control panel is located and mounted. Table 3-2 gives a detailed list of the mounting hardware supplied by FPS.

<sup>\*\*</sup> This will be supplied with first unit only.

Table 3-2 AP Mounting Hardware

- (1) Set Rackslides.

- (2) 12 OHS, 12 CW, 12 Captive Nuts (10-32 x 3/4) for Processor.

- (3) 20 BHS, 16 FHS, 20 LW, 50 FW, 4 nuts, 4 Nut Plates

- (10-32) for Rackslides. 4 BHS, 4 FW, 4 LW, 4 Captive Nuts (10-32 x 1/2) for Power Panel, bottom.

- (5) 4 OHS, 4 CW, 4 Captive Nuts (10-32 x 3/4) for Power Panel, top.

(6) 4 OHS, 4 CW, 4 Captive Nuts (10-32 x 3/4) for County Panel

- Control Panel.

- 2 BHS, 4 FW, 4 LW, 2 nuts w/LW (10-32 x 1/2) for Power Cables.

|                     | $10-32 \times 1/2$<br>Bills | 10-32 x 3/8<br>BIIS | 10-32 X 1/2<br>FIIS | 10-32 x 3/4<br>OIIS | Lock Washers<br>#10 | Cup Washers<br>#10 | Flat Washers<br>#10 | 10-32 Nut<br>w/Lock Washer | Nut Plate<br>10-32 | Captive Nut<br>10-32 |

|---------------------|-----------------------------|---------------------|---------------------|---------------------|---------------------|--------------------|---------------------|----------------------------|--------------------|----------------------|

| Processor           |                             |                     |                     | 12                  |                     | 12                 |                     | 1                          |                    | 12                   |

| Rackslides          |                             | 20                  | 16                  |                     | 20                  |                    | 50                  | 4                          | 4                  | -50                  |

| Power Panel, Bottom | 4                           |                     |                     |                     | 4                   |                    | 4                   |                            | / 5 = 1            | 4                    |

| Power Panel, Top    | 7.5                         | 1-22                |                     | 4                   |                     | 4                  |                     |                            |                    | 4                    |

| Control Panel       |                             |                     |                     | 4                   |                     | 4                  | 575                 |                            |                    | 4                    |

| DC Power Cables     | 2                           |                     |                     |                     | 4                   |                    | 4                   | 2                          |                    |                      |

| TOTAL               | 6                           | 20                  | 16                  | 20                  | 28                  | 20                 | 58                  | 6                          | 4                  | 24                   |

| w/Loss Allowance    | 7                           | 22                  | 17                  | 22                  | 30                  | 22                 | 60                  | 7                          | 5                  | 26                   |

BHS = Binding Head Screw

OHS = Oval Head Screw

FHS = Flat Head Screw

LW = Lock Washer FW '= Flat Washer

CW = Cup Washer

0229

### 3.4.1 Rack Slides

Prior to locating the rack slides in the rack, the 76.20 cm. (30 inches) of free vertical rack space into which the AP will be installed should be visually checked to ensure that there is nothing else occupying this space. The distance from the front to the rear of the rack mounts should be checked to ensure that this distance is greater than 50.80 cm. (20 inches) and less than 63.50 cm. (25 inches).

The first step in mounting the rack slides is to determine the uppermost limit of the 76.20 vertical centimeters (30 inches) of rack space set aside for the AP installation. (This point should be between two 1.27 cm. [1/2 inch] spaced holes.) This will be the reference point from which further measurements will be made. reference point measure down 4.45 cm. (1-3/4 inches) (one rack increment) and mark this spot (note that this  $4.45 \text{ cm} \cdot [1-3/4 \text{ inches}]$ space may be occupied by a unit above, if the bottom of the unit permits free air passage to the rear of the rack, and if the control panel is to be mounted elsewhere.) This now becomes the theoretical top edge of the processor. (Again this should be between two holes that are 1.27 cm. [1/2 inch] apart.) Measure down 31.12 cm. inches) (7 rack intervals) and mark this spot. This now is the center line for the rack slides and should be between two holes that are spaced 1.27 cm. (1/2 inch) apart.

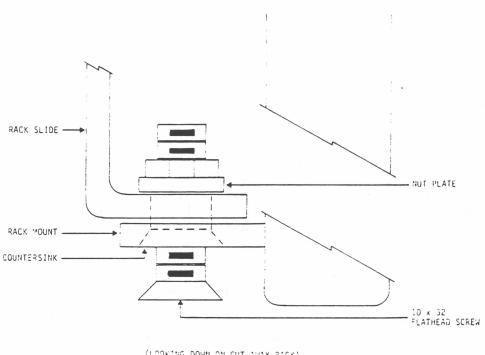

There are generally two types of mounts in the standard 48.26 cm. (19-inch) EIA rack. In one, the mounting holes are tapped and in the other they are not. If the rack you have is one that has tapped mounting holes, skip the next paragraph. If your rack mounting holes are not tapped, it will be neccessary for you to countersink the second hole above and the second hole below the center line of the rack slides. This is necessary to allow the front panel of the processor to mount flush in the rack. FPS provides all the necessary bolts, nuts, nut plates and washers for installation of the AP.

After countersinking these two holes in the front of the rack on both the left and right sides, mount the rack slide on the rack using flat-head 10-32 screws and nut plates. See Figure 3-1 for a diagram showing the positioning of the various parts. After mounting the rack slides to the front of the rack, position the rack slide extensions in place and determine the two holes on each side to be used for mounting the rack slide in the rear of the rack. Now that these have been determined, countersink these four holes (two on on each side) as was done in the front of the rack. Now, bolt the rack slide extensions on the rack using the flat-head 10-32 screws and nut plates in the same manner as was used in the front of the rack. Then, using the 10-32binding head screws, lockwashers, and nuts (four sets required) bolt the rack slides to the rack slide extensions. Then SECURELY tighten all rack slide and rack slide extension bolts.

BACK OF RACK

(LOOKING DOWN ON CUT-AWAY RACK)

0233

Figure 3-1 Rack Mounting Detail (Untapped)

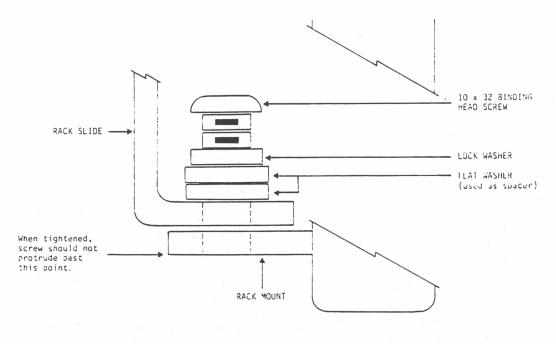

If mounting the AP in a rack that has tapped mounting holes, the measurements determining the center line of the rack slides should have been made (as specified above) prior to this time. The rack slide will mount on the rack. Use the two holes above and two holes below this center line. The 10-32x3/8 binding head screws and flat washers are provided to mount the rack slide. In order for the front panel of the processor to mount flush in the rack, it is necessary that the 10-32screws not protrude past the edge of the mounting flange. Install the rack slides as shown in Figure 3-2 using the required number of flat washers to ensure that the screws do not protrude.

FRONT OF RACK

(LOOKING DOWN ON CUT-AWAY RACK)

0231

Figure 3-2 Rack Mounting Detail (Tapped)

After installing both the left and right rack slides to the front of the rack, the holes used to mount the rack slide extensions should be determined by positioning the rack slide extension at the end of the rack slide and marking the appropriate four holes. The rack slide extension should then be mounted to the rear of the rack in a similar fashion as the rack slides ensuring that the 10-32 binding head screws do not protrude. The latter is necessary to allow the power panel to mount properly. Now, using the 10-32 binding head screws, lock washers, and nuts (four sets required) bolt the rack slides to the rack slide extensions. Then SECURELY tighten all rack slide and rack slide extension bolts.

### 3.4.2 Power Panel

After the rack slides have been mounted, the power panel should be located and mounted in the rear of the rack. (Note that the correct orientation of the power panel is with the piano hinge at the bottom of the rack.) From the center line of the rack slide (between two holes spaced 1.27 cm. [1/2 inch] apart) measure up 22.86 cm. (nine inches) and mark this hole. This should be done on both sides prior to attempting the installation of the power panel. This is the hole in which the upper screw of the power panel will be placed.

After locating the two upper holes in the rack, assemble two 10-32 oval head screws (provided by FPS) and cup washers to be used to mount the power panel. The power panel will be installed by lifting the power panel into position on the rack and placing the two screws into the holes which were located above. These two screws will then support the weight of the panel while the rest of the screws are placed through the panel into the rack.

After asembling the two 10-32 screws with cup washers and determining the holes in the rack to be used, the upper hole on the left and right of the power panel should be aligned with the holes in the rack. screw assembly is inserted through the upper hole in the power panel, and screwed into the rack mount. This should be done for both the left and right sides. Insert the other two 10-32 oval headed screws with cup washers into the rack through the middle holes in the power panel. (These may require the clip-type speed nuts if the rack is untapped.) These should not be mounted securely, but only temporarily. Now, using the four 10-32 binding head screws, flat washers and lock washers, bolt the power panel hinge, lower section to the rack mount. The power panel should now be aligned in the rack in such a way as to allow it to be folded down on its hinge far enough to allow access to each of the equipment groups mounted on the panel. This is done by pivoting the panel down and adjusting the hinge in the rack until the panel can be pivoted out the back of the rack. After finishing this, all the screws should be replaced.

### 3.4.3 Mounting the Processor

Prior to mounting the processor in the rack, the portion of the rack slide assembly on the processor should be adjusted. First, set the rack slide tilt mechanism arms to the horizontal position. The angle between these extended arms and the rear face of the processor should be 90 degrees. This can be simply checked by laying the edge of the extender board on the rack slide arm and visually checking to see if this is square with respect to the rear cover of the processor. If not, the nut behind the large screw in the middle of the tilt mechanism should be loosened and the arm repositioned until a 90-degree angle is achieved. Repositioning the arm is accomplished by turning the large screw mentioned above. The nut should then be re-tightened. Both tilt mechanisms (left and right) should be checked and adjusted if necessary.

Preferably with two people, set the processor on the floor in front of the rack with the front panel forward. Lift the processor and insert the arms into the slide slots of the rack slides. Slide the processor into the rack until it stops. Now grasp the outer portion of the slides and, while pulling forward slightly, press the release buttons and slide the processor into the rack. The mounting ears should now be flush in the rack. If the processor does not slide freely into the rack (it binds) or the mounting ears do not fit flush in the rack, further adjustment of the rack slide hardware in the rack will be necessary to allow the processor to slide into the rack without First, the mounting of the rack slide hardware in the rack binding. should be adjusted relative to the rack to allow the processor to slide in the rack without binding. Then, if necessary, the rack slide tilt mechanism should be re-adjusted until the front panel fits flush with the rack. Then from the rear of the rack, visually verify that there is at least two inches of clearance between the line box (on the power panel) and the rear cover of the processor.

# 3.4.4 Control Panel

If the control panel is to be mounted in the front of the rack, it will mount immediately above (or below) the processor. If your rack has untapped mounting holes, it will be necessary for you to use four #10 clip-type speed nuts to mount the control panel. If the processor and power panel have been mounted according to instructions, then above and below both the processor and power panel will be rack holes spaced 3.18 cm. (1-1/4 inches) apart, ready to receive the control panel.

In order to attach the connector to the control panel (Section 3.5.1) it will be necessary to gain access to the rear of the control panel. Therefore, it is recommended that it be mounted temporarily at this time, or connect the cable to the connector now. Four 10-32 oval head screws with cup washers and inserts will be used to mount the control panel. Now, locate the control panel in the position chosen and install the screws through the slots in the panel into the rack. Now adjust the position of the control panel to provide a 19 cm. (1/16th of an inch) clearance between the edge of the control panel and either the processor or the power panel. This is necessary to allow the processor or power panel to move without hindrance.

### 3.5 SYSTEM INTERCONNECTION

The AP has several connections which must be properly made prior to powering up the system. There are sub-system interconnections, a Host-to-AP interconnection, and an electrical service connection. FPS Schematic #680-2150-102 shows the necessary connections.

### 3.5.1 Power Panel to Control Panel

Prior to connecting any of the cabling, the serial number tag on the power panel should be checked to ensure that the power panel received is of the voltage option specified, and that this voltage is compatible with the service voltage supplied to the AP. The fuses and labels (mounted on the line box) should be checked to verify that they are of the proper value as specified in Table 2-1. The control panel serial number tag should then be checked to make sure that its voltage is compatible with the power panel.

While the control panel is out of the rack, feed the nine-pin D sub-miniature female connector P9 through the space left by the removal of the control panel. This connector is labeled P9 on the cable clamp and has six #22 wires coming into it. Now connect plug P9 to socket J9 on the control panel and secure it with the locking screws. After making this connection, take P3 and its cable (originating from the control panel) and drop it through the space in the rack left by the removal of the control panel. Then the control panel should be re-installed as per Section 3.4.4 and the screws tightened. Again make sure that the control panel has .19 cm. (1/16th of an inch) clearance between itself and either the processor or the power panel. Now, from the back of the rack connect P3 (the jones plug) to socket J3 on the line box. Note that if the control panel is mounted above the processor, the two above-mentioned cable runs should be dressed in such a way that they will not hang near the processor's fan filters.

## 3.5.2 Power Panel to Processor

To prepare for the power panel hookup:

- 1) Slide out the processor.

- 2) Remove the AP retaining screws.

- 3) Lift off the front panel.

- 4) Slide the processor forward until the rack slides lock.

### CAUTION

Once the front panel is removed, the user must be careful not to damage the wire-wrap pins on the mother board.

The power supplies for the AP-CT are user-supplied. These are a +5V, a -5V, and a +12V supply, as shown on FPS Schematic #680-2150-102. The line box is FPS-supplied. To connect these supplies:

- Connect socket Jll on the I/O bracket at the bottom rear of the processor to the line box, as shown in FPS Schematic #680-2150-102. (From the front of the rack, socket Jll is on the left side of the processor near the fans.)

- 2) Connect socket Jl, which is located just to the right of socket Jll, to the power supplies, also as shown in FPS Schematic #680-2150-102.

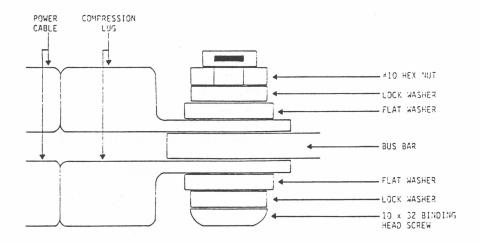

- 3) Connect the four processor cables found on the lower part of the mother board to the +5VDC/150A or 120A power supply on the power panel. Note that the two cables marked red on the ends are for connection to the positive terminal; the two solid black cables are for connection to the negative terminal. Place one cable lug on each side of the appropriate bus-bar and secure it with a 10/32 binding head screw, lock washer, flat washer, and nut. Place a lock washer and a flat washer between the screw head and the first lug. Insert assembly through the bus-bar. Then place the second lug, flat washer and lock washer over

the appropriate bus-bar. Secure it in place by placing a lock washer between the 10/32 binding head screw mounting bracket and fastening it with a hex nut. Figure 3-3 shows how the cables are bolted to the bus-bar. After all cables are connected, tighten them securely and check to see that the positive (+) is not shorted or close to the negative (-) at this connection.

After the power supplies are connected, the host-to-AP cable is connected to the AP. Due to the number of different types of cabling configurations possible, it is impossible to give specific instructions for this operation. However, general guidelines follow.

The host-to-AP cabling connects, on the AP end, to the sockets on the I/O bracket. In most cases, these are keyed to prevent incorrect insertion of the cable. However, if they are not, straightforward markings on the I/O bracket are given (both a connector number and a pin number as a reference). This cabling is connected to the AP and not connected to the host until after the voltage levels are checked on the AP, as specified in Section 3.6. Further details and directions for the host-to-AP connection are contained in Section 3.6.3.

0233

Figure 3-3 Bus Bar Bolting Detail

### 3.6 START-UP

The start-up includes checking the line voltage; applying power to the AP; checking the +5 VDC, -5 VDC, and -12 VDC; checking the fans; and re-installing the power panel (returning it to an upright position in the rack).

#### 3.6.1 Line Power

Before plugging in the AP, the line voltage to be used should be checked with a meter to ensure that it falls within the minimum and maximum range specified in the voltage (RMS) column of Table 2-1. The line voltage should also be checked with an oscilloscope to make sure the line voltage is not less than 280 volts peak-to-peak for the 115 VRMS option, 535 volts peak-to-peak for the 208 VRMS option, and 560 volts peak-to-peak for the 230 VRMS option. While checking the line voltage with an oscilloscope, the wave form should be checked to verify that it is really sinusoidal. If the peaks appear flattened, or the peak-to-peak value drops below 280/560 volts when the AP is turned on, then it is possible that a lower impedance power service will be necessary for proper AP operation. (This peak-to-peak value check is detailed in Section 3.6.2. Also, see Table 2.1.)

Place the ON/OFF switch on the control panel in the "OFF" (switch down) position and plug in the power cord. The processor should then be tilted back to its upright position to allow access to the mother board. The four heavy cables on the mother board at the bottom of the processor are the +5 VDC and 5 VDC return. The +5 VDC is the uppermost terminal (above the return terminal). A meter which is accurate to a tenth of a volt should be placed on the mother board between the +5 VDC and common. This will be used to monitor the +5 VDC as the power is applied to the unit. Now turn the ON/OFF switch to the "ON" position while watching the meter monitoring the +5 VDC. The fans should come on, the +5 VDC should read slightly over +5 volts, and the supply indicators on the control panel should be lit. If problems occur, the system should be immediately powered down and the line cord unplugged.

## 3.6.2 DC Power Supplies

After it is possible to power up the AP, the DC voltage supplies should be checked to verify that they are properly adjusted. Again, an accurate voltmeter that can give a tenth of a volt resolution should be used for this verification. The voltmeter should currently be attached to the +5 VDC (from Section 3.6.1) on the mother board and this voltage should be 5.15 + 0.05 volts when the ON/OFF switch is in the ON position. If this voltage does not fall within this specified range, it will be necessary to adjust it.

The -5 volts should then be checked. Directly to the left of the left +5 VDC and down slightly on the mother board, is a rectangle labeled -5V. The positive lead of the meter should be placed on the AP common (the common of the meter is currently on AP common) and the common of the meter touched to any of the wirewrap pins protruding from the -5V rectangle. This should read +5.00 + 0.05 volts. If this voltage does not fall within this specification it should be adjusted until it does.

Next, the +12 volt supply should be checked to verify that it reads +12.00 + 0.05 volts. The common of the meter should be returned to the common on the AP mother board. After assuring that the meter is to the proper scale, the other probe should be placed on one of the wirewrap pins protruding from the 12V rectangle. This rectangle is in the middle at the top of of the mother board. If the voltage does not meet the above specification, it should be adjusted.

Now that the voltage levels are properly set, visually check to verify that the indicators on the control panel labeled "control power", "+5 power", "+12 power", and "-5 power" are lit. Also, visually check to ensure that all eight fans are operating. With the oscilloscope again placed across the line voltage (Section 3.6.1), toggle the ON/OFF switch between ON and OFF while monitoring the waveform on the oscilloscope. The line voltage on the scope should not vary more than 35 volts peak-to-peak as the system is switched. If it does, consideration should be given to installing a low impedance line source (see Section 2.3). You may prefer to use a differential oscilloscope input, so the oscilloscope ground can be on the power line safety ground, and the oscilloscope inputs on the power true (Remember, there is a significant voltage drop on both power lines). Hopefully, there will be at least 10 percent more than 280/560 volts peak-to-peak line voltage under load, in order to allow for occasional low input line voltage.

## 3.6.3 Final Installation

After powering down the AP and the host system, the host-to-AP cabling should be connected to the host in the appropriate manner. Due to the number of different types of cabling configurations (these are host-dependent), only general guidelines will be given. In some cases, such as the PDP-11, this connection requires as little as plugging a connector into a socket on the host. In others, such as the Nova, this requires the insertion of an etch circuit (or wirewrap) card into a slot in the host chassis, and then cabling from this I/O adapter to the AP.

The power panel should then be pivoted back into the rack, the screws replaced and tightened securely. The front panel should then be mounted on the processor with the four screws. Then slide the processor into the rack and secure it with 12 oval headed screws, cup washers, and inserts. Note that if your rack has untapped mounting holes, 12 clip-type speed nuts are supplied.

3 - 15

#### CHAPTER 4

### CHECKOUT AND TEST

### 4.1 INTRODUCTION

After the AP has been installed into the users system, the system should be checked to verify that the integration of the AP has not caused interactive-type system problems. Then the diagnostic software provided by FPS should be used to verify the operation of the host-to-AP interface and the AP system.

### 4.2 HOST SYSTEM

After the power panel and the processor have been installed in the rack, the host system should be turned on. Then the AP should be turned on by placing the ON/OFF switch in the ON position. The user's system should then be checked to verify that the host processor and all peripheral devices function properly. First, the host should be checked to verify that it is able to operate. This can be done by operating some simple program like a bootstrap loader and seeing that it executes properly. Then each peripheral on the system (disk, teletype, terminal, tape drive, etc.) should be checked to see that it functions properly. The diagnostic programs supplied with each of these devices will adequately verify their operation.

### 4.3 AP DIAGNOSTICS

FPS supplies a diagnostic software package with each AP. This software package consists of four separate test programs. Certain hardware options supplied by FPS, at the customer's request, necessitate the addition of one or more diagnostic programs. If this is the case for your AP, the necessary information will be supplied by FPS on an individual basis. The general diagnostic programs supplied by FPS are called APTEST, APPATH, APARTH, and FIFFT. These four programs not only verify the AP system operation, but are also used in isolating and correcting system deficiencies. This manual will give the user enough information to verify the AP system. If a further description of these programs and their input commands is necessary, FPS Manual #7284 AP Diagnostic Software Manuals should be consulted.

4 - 1

For verifying the operation of the AP, the four diagnostic programs should be run for a short period of time. APTEST should be run first, then APPATH, then APARTH, and then FIFFT. For verification, all four programs use the same input command string. The method of running the test will be to load the test to be run into the host (if the program does not autostart); start the program from the teletype (or terminal); input the command characters RWE; and then input a carriage return. The program will, after a short period of time (this short period of time varies with the different tests, but should not exceed five minutes), return a status character to the teletype (or terminal) indicating proper system action. If an error is detected, the program will inform the user by printing the error message out on the teletype in the appropriate format (defined by FPS Manual #7284).

### 4.3.1 APTEST

APTEST tests the ability of the host to load and read the various AP registers and memory elements accessible to it through the virtual front panel. APTEST also verifies the DMA-to-DMA transfer capabilities of the system and provides a simple test of the AP formatter. A "T" is typed on the teletype as status to indicate four error-free passes through the program. This test uses random patterns to test the memory elements of the AP and should be run for one hour to verify the system.

### 4.3.2 APPATH

APPATH runs the processor of the AP. Its main function is to verify the various data paths internal to the AP. This test should be run for ten minutes. A "P" is displayed to indicate that the program is running and that the AP is running error-free.

#### 4.3.3 APARTH

APARTH runs the arithmetic elements of the AP on strings of randomly-selected numbers verifying the operation of these arithmetic elements. The program returns an "A" status to indicate error-free operation. This test should be run for one hour.

### 4.3.4 FIFFT

FIFFT does forward and inverse Fast Fourier Transforms (FFT) on two different sets of data. First, the program uses data sets with only one non-zero value (an impulse). Then the program uses a randomly-selected data set. After the impulse test is done, the program types "END OF IMPULSE TEST" and then automatically proceeds to compute FFT's on random data. The program then types a "F" as status verifying error-free operation. This test should be run for one hour.

#### CHAPTER 5

### THEORY OF OPERATION

### 5.1 INTRODUCTION

This chapter provides the detailed theory of operation for the AP and is divided into four major sections: system overview, memory, arithmetic and control.

The system overview (paragraph 5.2) presents a functional system description by delineating the major functional elements, the various data paths, and the flow of data between the AP and the host computer.