ACOLO LA COLO LA COLO

The attached pages update: (1) edition A-09-00016-01-A and Update Notices A-09-00058-01-A, A-09-00066-01-A, A-09-00091-01-A, A-09-00177-01-A, and A-09-00228-01-A or (2) edition A-09-00016-01-B and Update Notices A-09-00066-01-A, A-09-00091-01-A, A-09-00177-01-A, and A-09-00228-01-A of the Workstation Hardware Manual.

Insert these pages according to the collating instructions on the inside of this cover

Updated pages are indicated by a date at the bottom of the page.

Throughout this Update Notice, change bars in the margins indicate technical additions and changes. Asterisks indicate deletions. Editorial changes are not identified. All changes will be incorporated into the next editions of this manual

Insert this page after the title page of your manual to provide a record of this Update Notice.

Copyright © 1983 by Convergent Technologies, Inc

#### COLLATING INSTRUCTIONS

#### VOLUME 1: Sections 1 - 9

| Delete       | Replace with |

|--------------|--------------|

| iii to xi    | iii to xi    |

| 1-3, 1-4     | 1-3, 1-4     |

| 1-9          | 1-9, 1-10    |

| 2-25, 2-26   | 2-25, 2-26   |

| 2-109, 2-110 | 2-109, 2-110 |

| 9-5, 9-6     | 9-5, 9-6     |

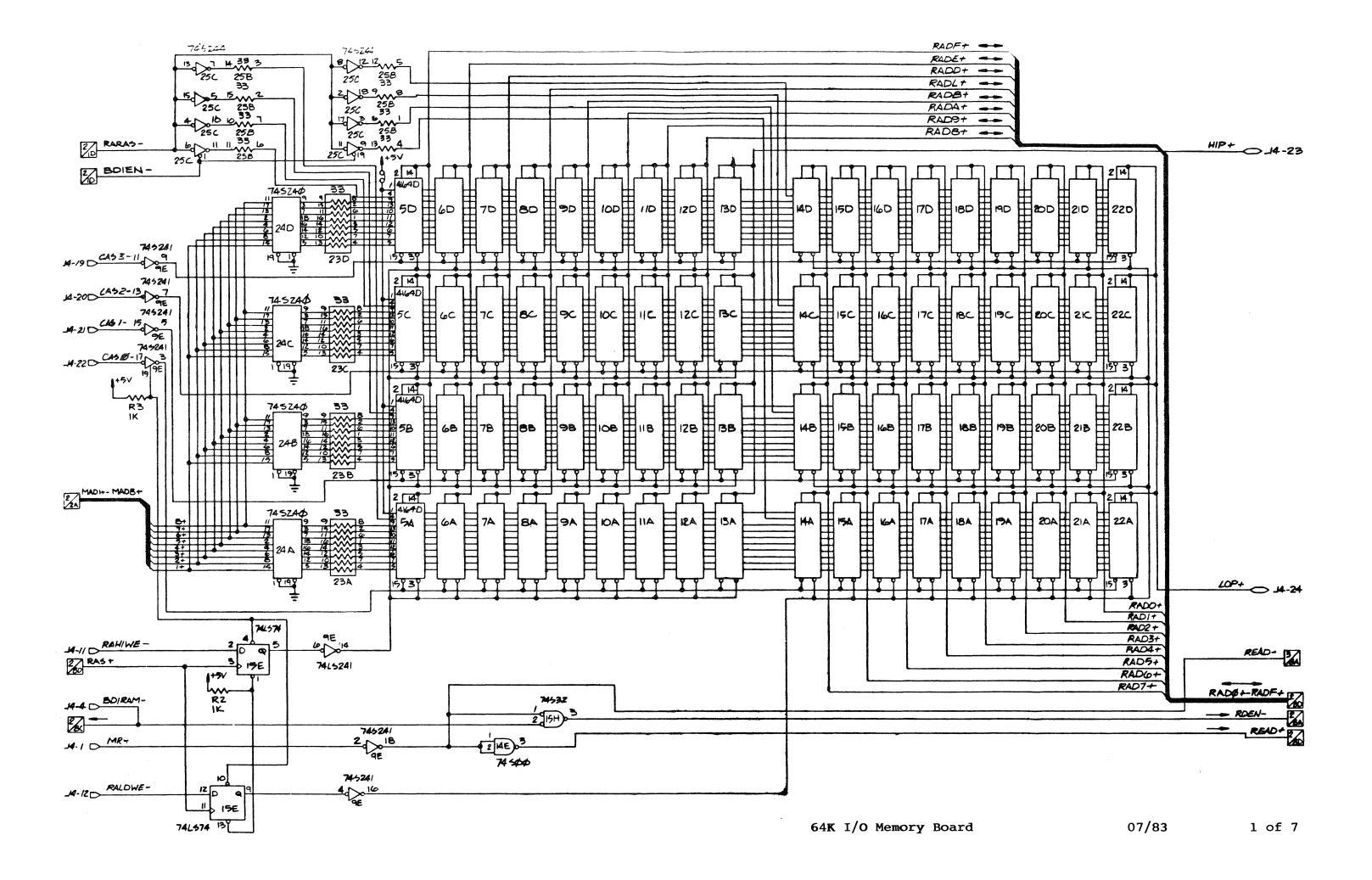

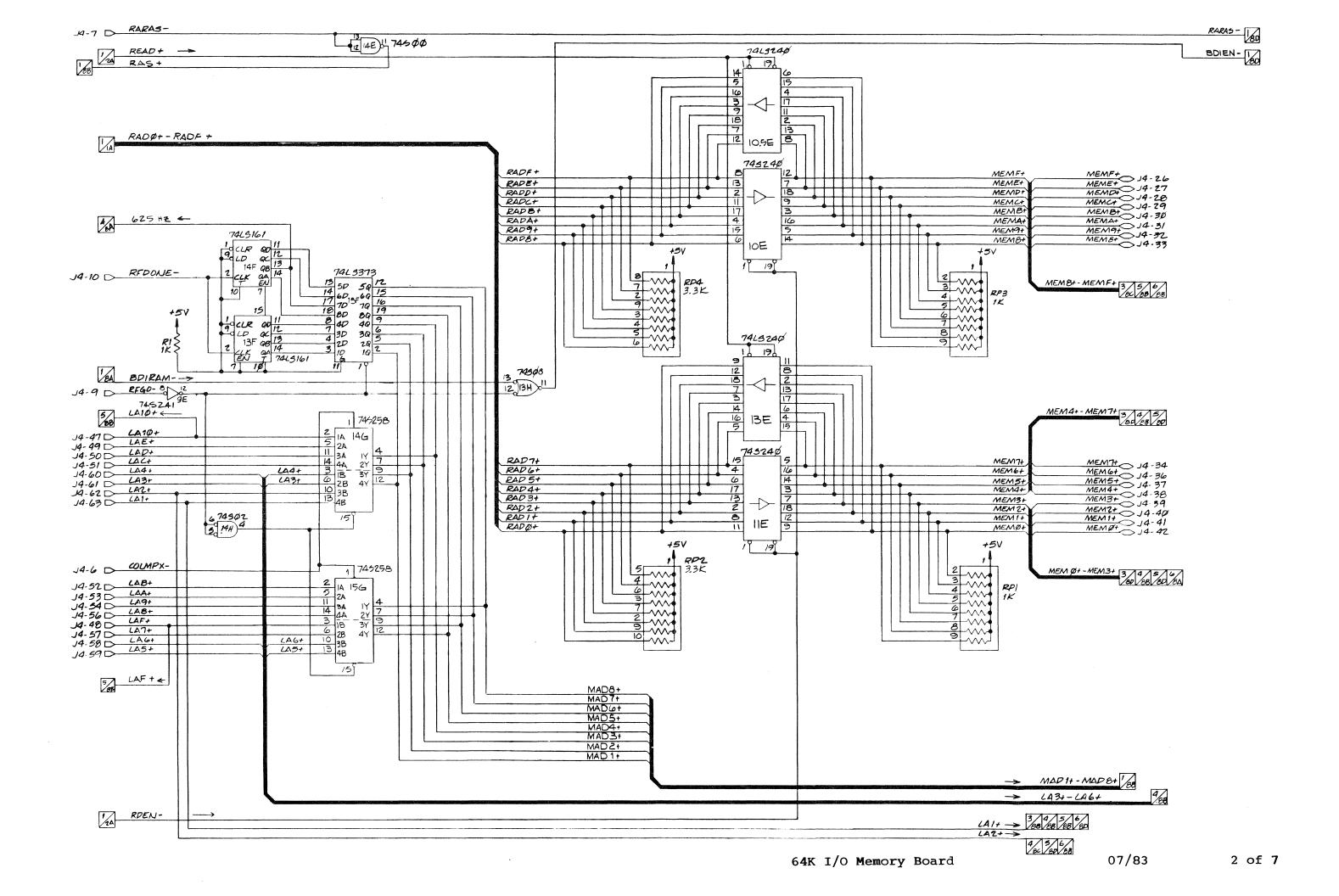

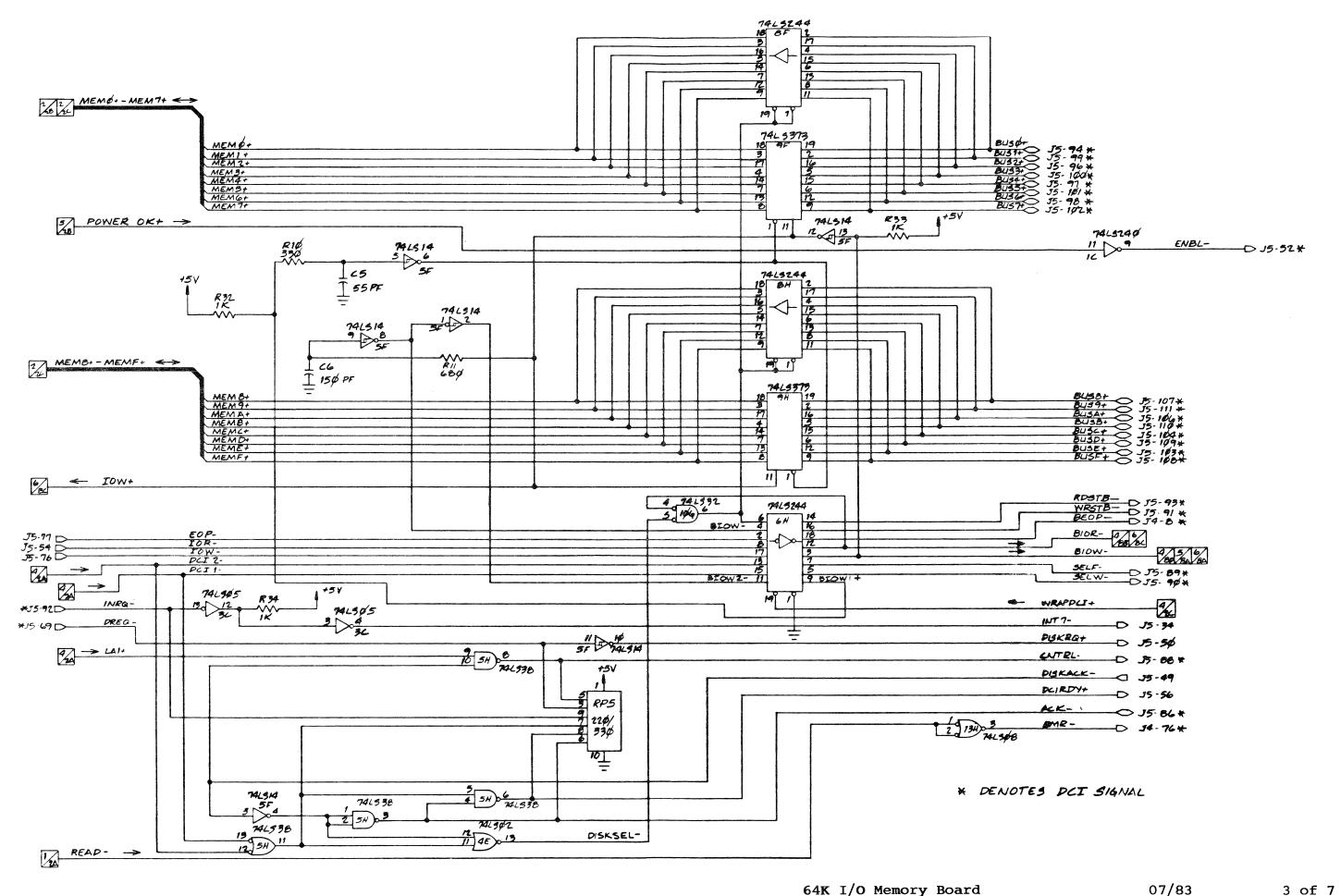

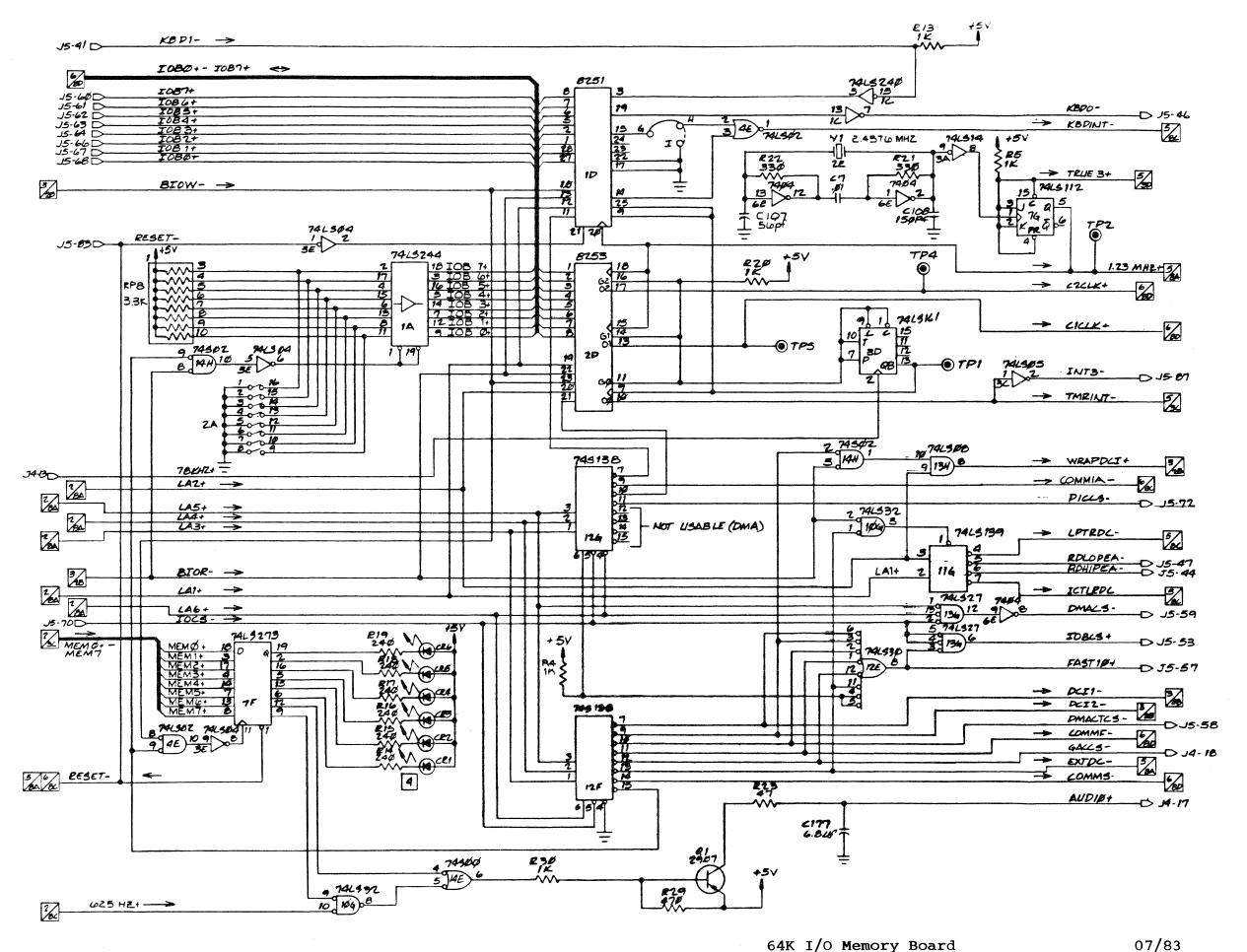

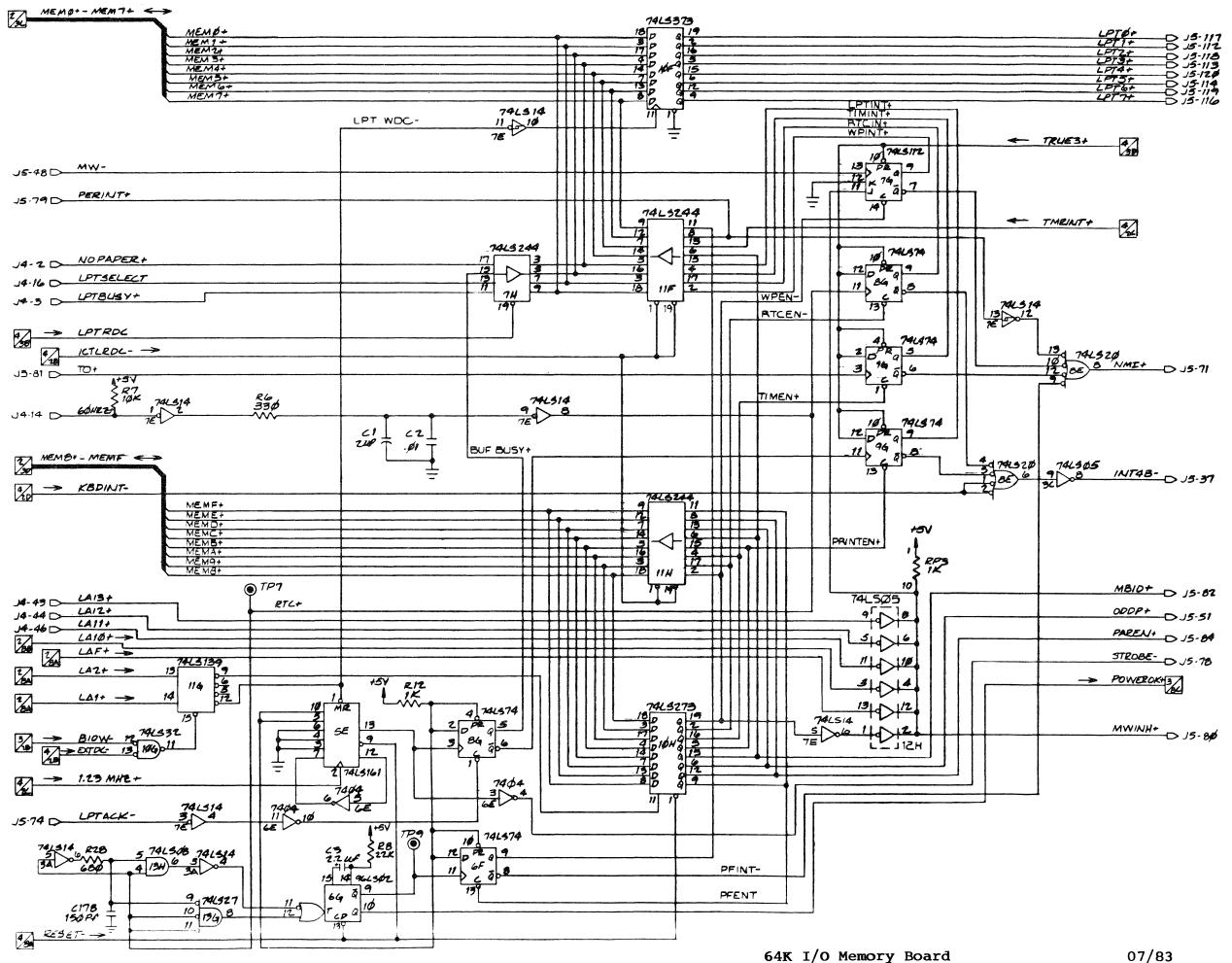

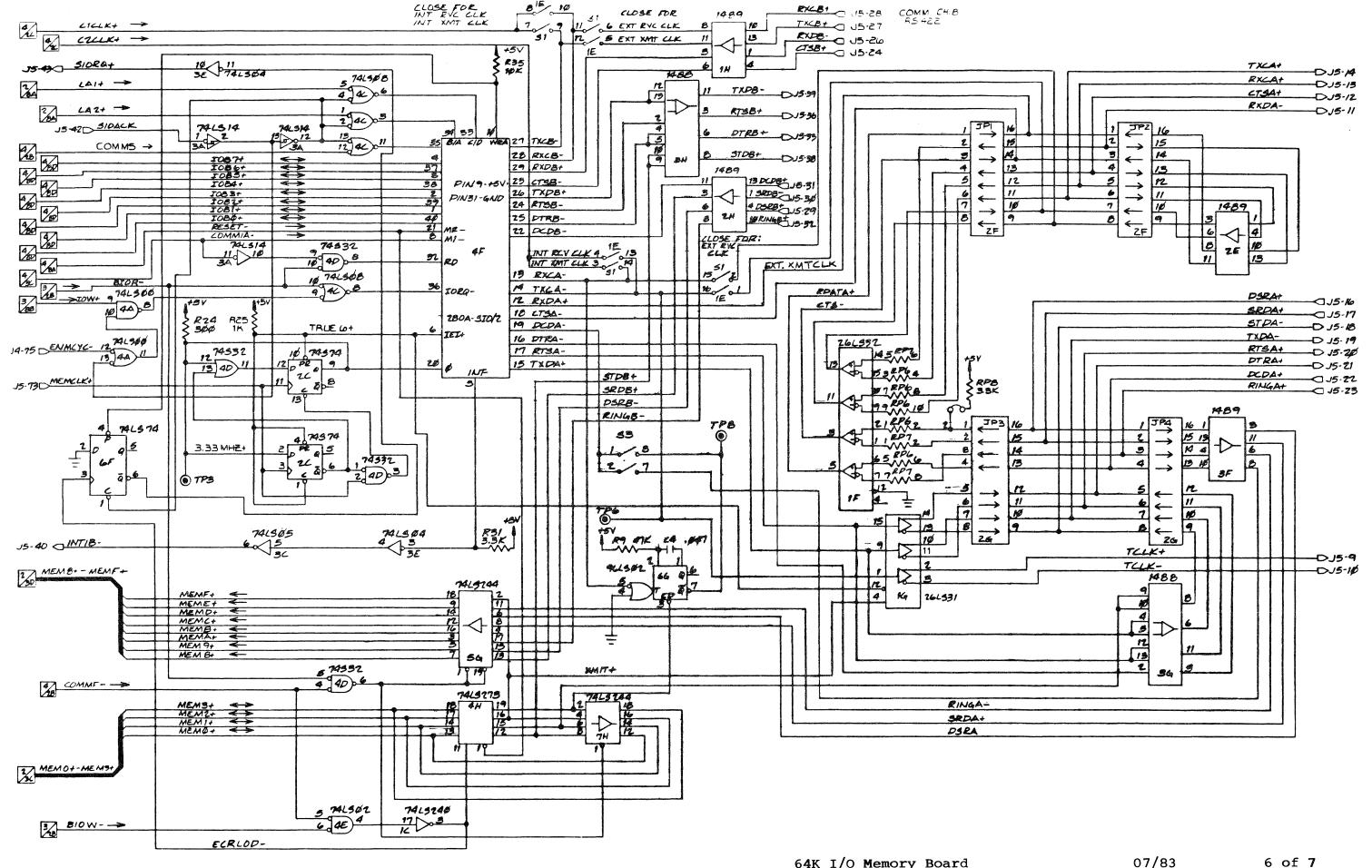

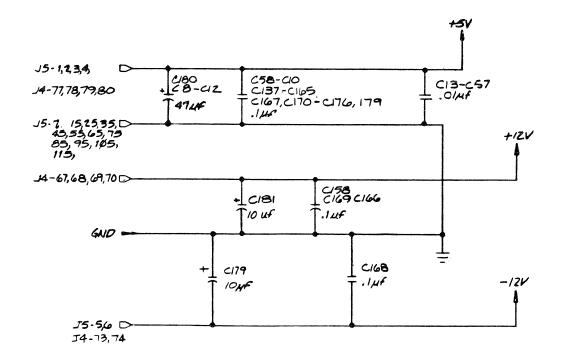

Place the <u>seven foldout pages</u> (schematic) of the 64K I/O-Memory board at the end of Section 5. (Do not delete the existing schematics.)

# VOLUME 2: Sections 10 - 14 Glossary Appendixes A - G

| Delete          |              | Replace with               |

|-----------------|--------------|----------------------------|

| iii to vi       |              | iii to vi                  |

| D-1, D-2<br>D-7 | (Appendix C) | D-1, D-2, D-2.1            |

| E-1             | (Appendix D) | E-i to E-iii, E-l to E-101 |

| F-1             | (Appendix E) | F-i, F-ii, F-1 to F-72     |

#### DESCRIPTION OF CHANGES

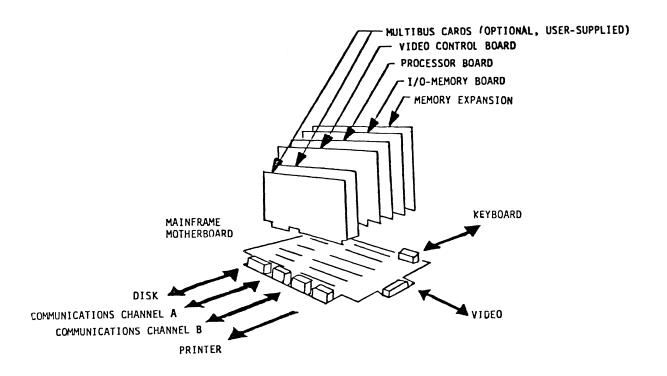

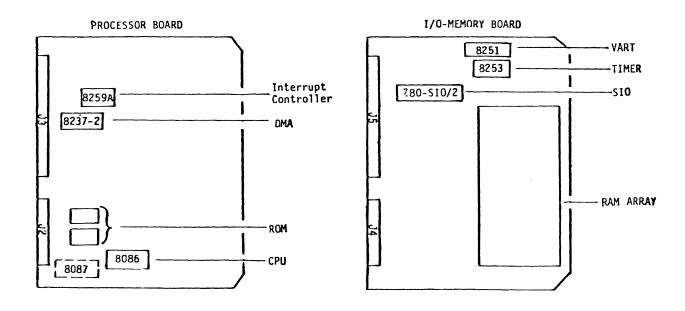

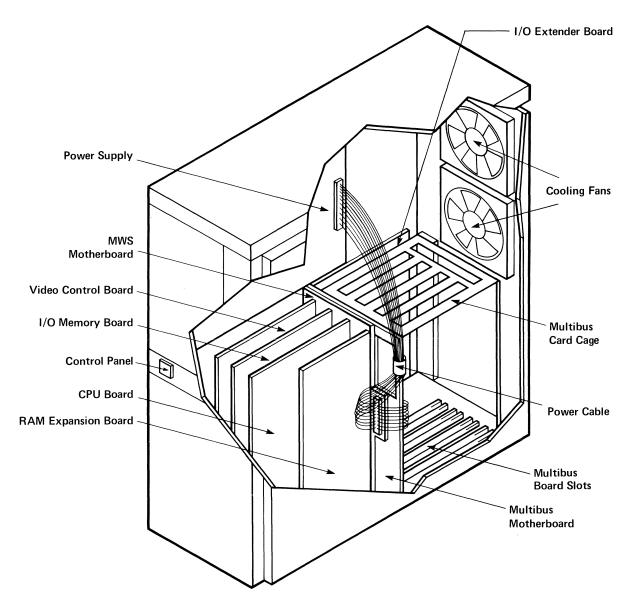

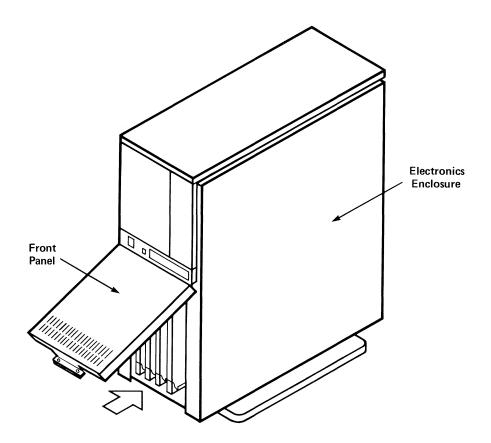

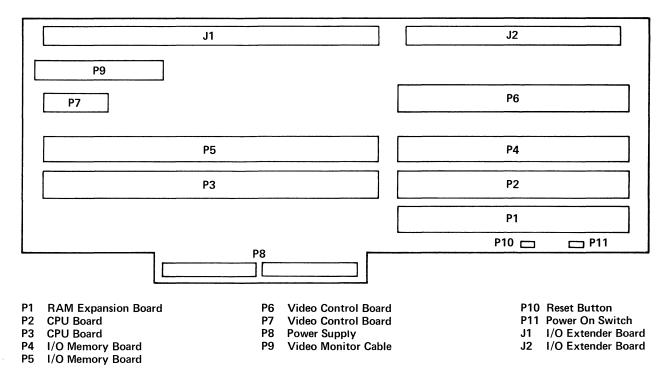

Revisions include changes in Chapter 2 and Appendix C for the 64K I/O Memory board. Other revisions include a minor change to Chapter 9 and revised Figures 1-1, 1-4, and 12-2.

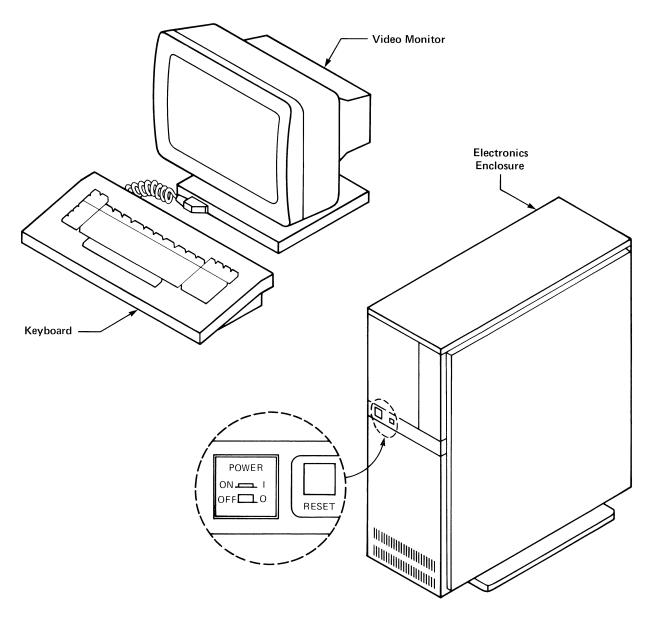

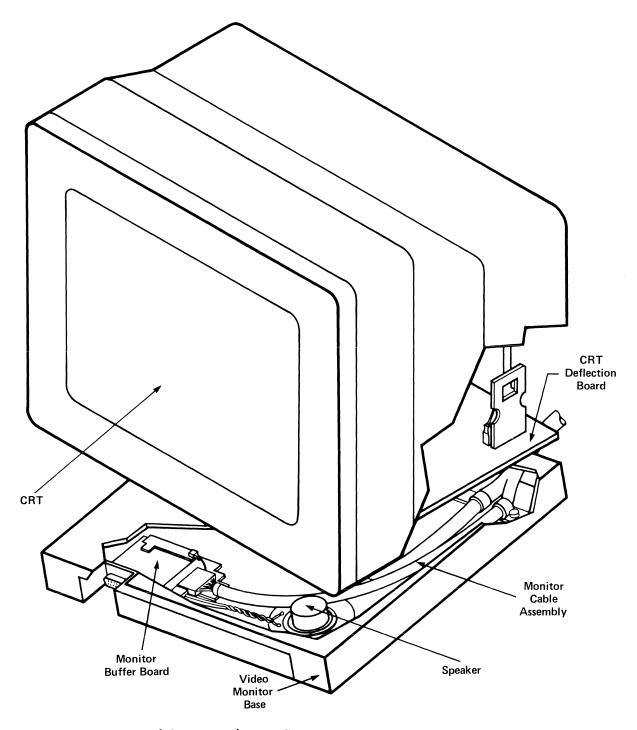

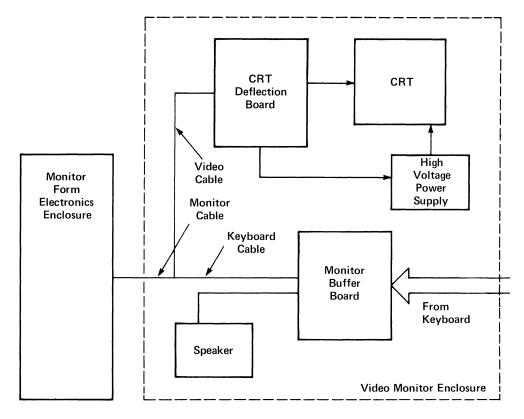

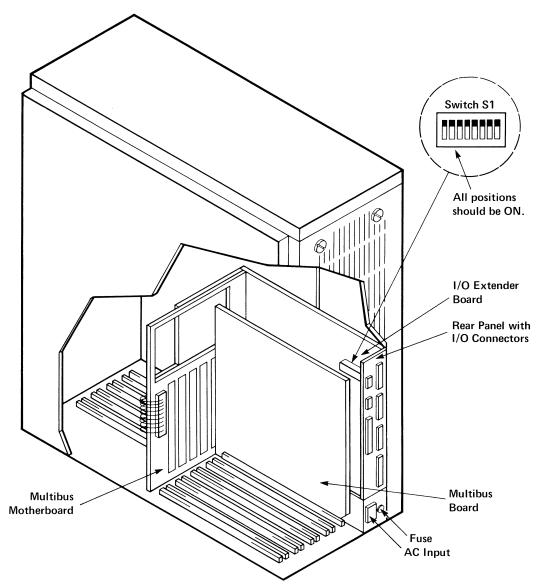

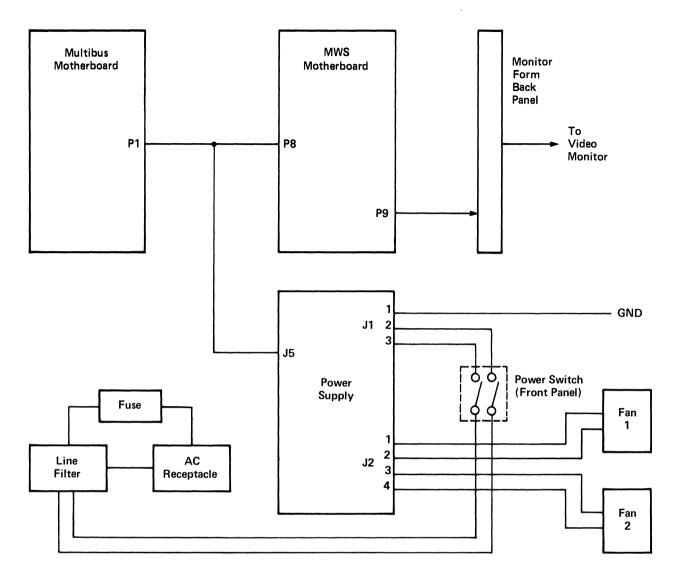

Appendix D contains a description of the monitor form of the IWS workstation and includes information about custom Multibus applications.

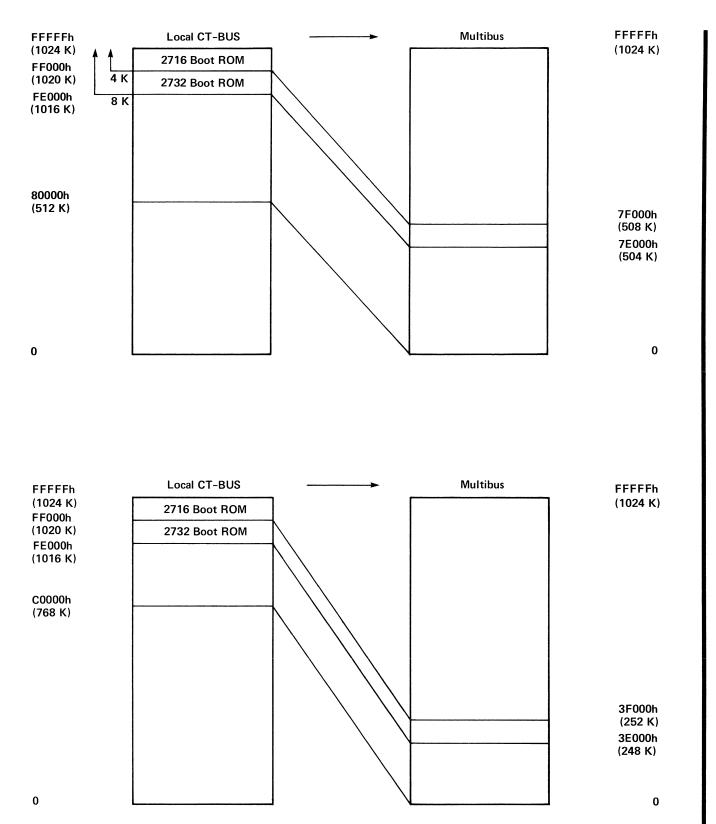

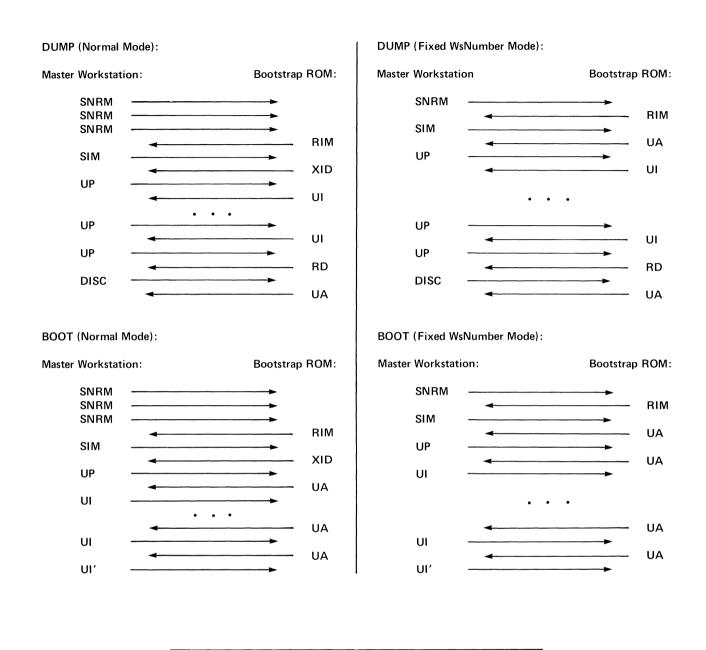

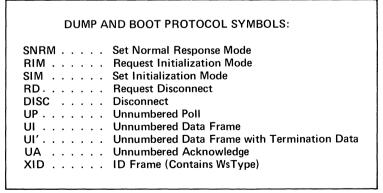

Appendix E contains a detailed software description of the four bootstrap ROMs available for the IWS workstation.

## CONTENTS: Volume 1

| GUI | DE TO TECHNICAL DOCUMENTATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | xiii                                                                                                         |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Pre | face                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | XX                                                                                                           |

| 1.  | System Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                              |

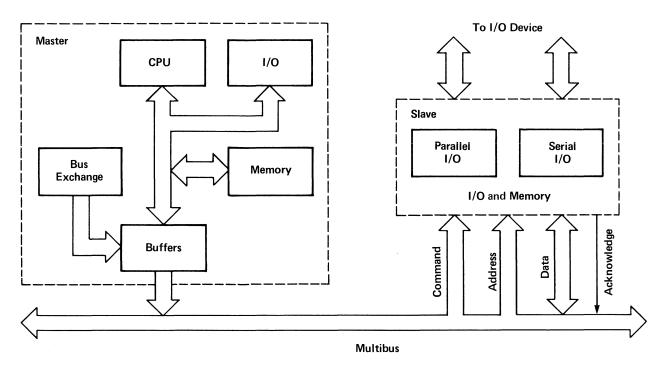

|     | Overview The mainframe Memory Input/output Multibus interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-1<br>1-2<br>1-5<br>1-8                                                                                     |

| 2.  | Functions and Interfaces (Processor and I/O-Memory Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | s)                                                                                                           |

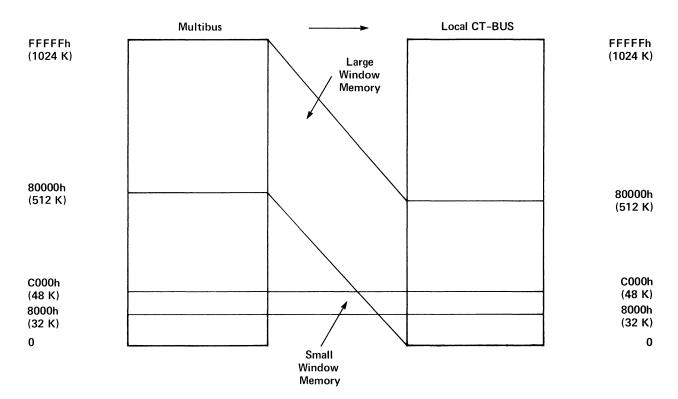

|     | Dual bus organization.  Local and multibus separation.  Local J/O bus interface.  Local I/O bus interface.  Multibus interface.  Multibus master access.  Multibus slave access.  Multibus slave access.  Priorities.  Bus timeout.  The 8086 and 8087 processors  The 8086 CPU.  The 8087 numeric data processor  Software interface.  8086 CPU.  8087 NDP.  Memory interface.  Address space.  ROM memory.  Multibus/Local-bus memory mapping.  Software interface.  Parity error register (PER)  I/O and control interfaces.  I/O peripheral devices and channels  I/O circuits and registers.  DMA Control.  Intervupt Control.  Keyboard Control and LEDs.  Interval Timer.  I/O-Memory Board LEDs and Audio.  Communications Control.  I/O Control Register (IOCR).  Parity Error Register (PER) | 2-1<br>2-2<br>2-6<br>2-7<br>2-7<br>2-8<br>2-1<br>2-1<br>2-1<br>2-1<br>2-1<br>2-1<br>2-1<br>2-2<br>2-2<br>2-2 |

| Printer Status Register (PSR)              | 2-33  |

|--------------------------------------------|-------|

| Screen Attribute Register (SAR)            | 2-33  |

| Floppy Disk Control (FDC)                  | 2-33  |

| Winchester Disk Control (WDC)              | 2-33  |

| Software interface                         | 2-34  |

| DMA Transfers                              | 2-35  |

| General operating characteristics          | 2-35  |

| Channel uses                               | 2-37  |

| Multibus Access                            | 2-38  |

| Communications                             | 2-38  |

| Disk                                       | 2-40  |

| Video Refresh                              | 2-40  |

| Bus exchange                               | 2-42  |

| Address generation                         | 2-43  |

| Communication and Video Addresses          | 2-43  |

| Disk Addresses                             | 2-43  |

| Software interface                         | 2-47  |

| 8237-2 DMA controller                      | 2-47  |

| DMA extended address register (EAR)        | 2-53  |

| Interrupts                                 | 2-55  |

| Non-maskable interrupts                    | 2-55  |

| Power Failure                              | 2-58  |

| Parity Error                               | 2-58  |

| Memory Write-protection                    | 2-58  |

| Bus Timeout                                | 2-59  |

| Maskable interrupts                        | 2-59  |

| Communications (Level 1)                   | 2-59  |

| Internal Timer (Level 3)                   | 2-59  |

| Printer Keyboard, realtime clock and       | 2-39  |

| 8087 Level 4                               | 2-59  |

| Disks (Level 7)                            | 2-59  |

| Software interface                         | 2-60  |

| 8259A interrupt controller                 | 2-61  |

| I/O control register (IOCR)                | 2-70  |

| 8253 interval timer                        | 2-75  |

| Multibus interface                         |       |

|                                            | 2-80  |

| Signal lines                               | 2-80  |

| Form factor                                | 2-80  |

| Transfers across the interface             | 2-80  |

| Modes of operation                         | 2-84  |

| Bus priority resolution                    | 2-84  |

| Interrupts                                 | 2-85  |

| Communications interface                   | 2-88  |

| Channels                                   | 2-88  |

| Transfer control                           | 2-88  |

| Switch-selectable clocks                   | 2-91  |

| Extended control register                  | 2-91  |

| Software interface                         | 2-92  |

| Z-80A serial I/O (SIO) controller          | 2-92  |

| SIO extended control register (ECR)        | 2-97  |

| SIO interrupt acknowledge register (IAR)   | 2-100 |

| Keyboard interface                         | 2-102 |

| Keyboard/mainframe communication functions | 2-102 |

|    | Data formats  Software interface          | 2-104<br>2-104 |

|----|-------------------------------------------|----------------|

|    | Printer interface Software interface      | 2-111          |

|    | Utilities  Programmable LEDs and audio    | 2-113          |

|    | Hardwired LEDs                            | 2-115          |

|    | Power supply                              | 2-115          |

| _  |                                           | 2-116          |

| 3. | Mainframe Motherboard                     |                |

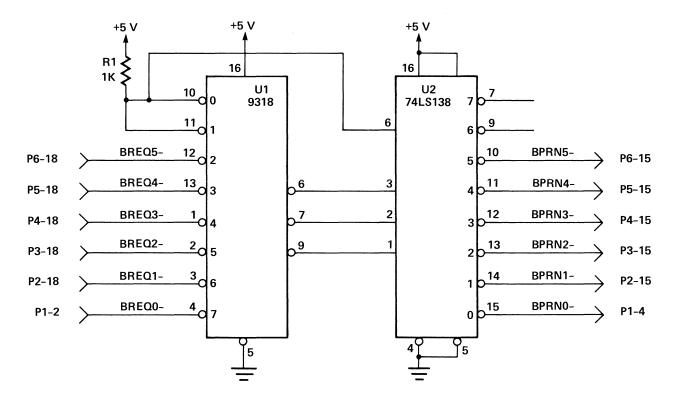

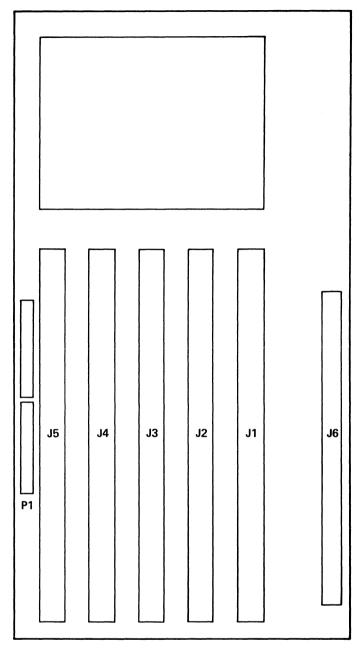

|    | Multibus priority resolution logic        | 3-1<br>3-2     |

|    | References                                | 3-3            |

|    | Edge-connector pin list                   | 3-3            |

|    | Jumpers                                   | 3–3            |

| 4. | Processor Board                           |                |

|    | Overview                                  | 4-1            |

|    | Operation by logic block                  | 4-1            |

|    | The dual bus architecture                 | 4-3<br>4-4     |

|    | Control of the local bus drivers          | 4-4<br>4-6     |

|    | Bus timeouts                              | 4-8            |

|    | The 8086 microprocessor                   | 4-8            |

|    | The 8087                                  | 4-11           |

|    | The RAM controller                        | 4-11           |

|    | Memory read cycles                        | 4-12           |

|    | Memory write                              | 4-13           |

|    | Column address strobe                     | 4-13           |

|    | Parity logic                              | 4-14           |

|    | Parity writing                            | 4-14           |

|    | Parity reading and checking               | 4-14           |

|    | Interrupt control logic                   | 4-15<br>4-18   |

|    | Multibus slave READY generation           | 4-10           |

|    | Non-Multibus READY generation             | 4-21           |

|    | Multibus interface                        | 4-23           |

|    | Multibus master mode                      | 4-23           |

|    | 8289 Multibus handshake                   | 4-23           |

|    | Acquiring multibus                        | 4-24           |

|    | Multibus master mode operation            | 4-26           |

|    | during master mode                        | 4-27           |

|    | LOCK access to Multibus                   | 4-28           |

|    | Slave mode                                | 4-29           |

|    | Multibus slave transfer acknowledge logic | 4-31           |

|    | Root PROMe                                | 1 21           |

| DC characteristics. References Edge-connector pin list. Connector J2. Connector J3. Jumpers. Switches. The memory addressing decode PROM. LED indicators. Test points. I/O-Port addresses vs. functions. Device pin functions. 8086 HMOS microproocessor. 8284 Clock driver. 8289 Bus arbiter. 8288 Bus controller. 8259A Interrupt controller. 8259A Interrupt controller. 8259A Interrupt controller. 8260 Address decode. The RAM array. Disk control interface (DCI). I/O address decode. The I/O control register (IOCR). Control bits of the IOCR. Speaker LESs and switches. Programmable timer. Keyboard interface. Line printer interface. Real time clocks. Power fail detect. Write protection. Communications. Non-DMA transfers between 8086 and the SIO. Programming the ECR. Multidrop driver control. Multidrop driver control. Multidrop receiver clock detect. Baud rate clock source selection. Channel B level changers. AC characteristics. DC characteristics. DC characteristics. References. Edge-connector jin list. Connector J4. Connector J5 Jumpers.                                                                           |    | ac characteristics                | 4-33  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----------------------------------|-------|

| Edge-connector pin list. Connector J2. Connector J3. Jumpers. Switches. The memory addressing decode PROM. LED indicators. Test points. I/O-Port addresses vs. functions. Device pin functions. 8086 HMOS microprocessor. 8284 Clock driver. 8288 Bus arbiter. 8288 Bus controller. 8237-2 DMA controller. 8259A Interrupt controller. 8259A Interrupt controller.  5. I/O Memory Board  Overview. Operation by logic block. The RAM array. Disk control interface (DCI) I/O address decode. The I/O control register (IOCR) Control bits of the IOCR. Status bits of the IOCR. Speaker LESs and switches. Programmable timer. Keyboard interface. Line printer interface. Real time clocks. Power fail detect. Write protection. Communications. Non-DMA transfers between 8086 and the SIO. DMA transfers between memory and the SIO. DRA transfers between memory and the SIO. Programming the ECR. Multidrop driver control Multidrop driver control Multidrop receiver clock detect. Baud rate clock source selection Channel B level changers. AC characteristics DC characteristics References. Edge-connector pin list. Connector J4. Connector J5. |    | DC characteristics                | 4-42  |

| Connector J2. Connector J3. Jumpers. Switches. The memory addressing decode PROM. LED indicators. Test points. I/O-Port addresses vs. functions. Device pin functions.  8086 HMOS microproccessor. 8284 Clock driver. 8289 Bus arbiter. 8289 Bus arbiter. 8237-2 DMA controller. 8259A Interrupt controller. 8259A Interrupt controller.  Operation by logic block. The RAM array. Disk control interface (DCI) I/O address decode. The I/O control register (IOCR) Control bits of the IOCR. Speaker LESs and switches. Programmable timer. Keyboard interface. Line printer interface. Real time clocks. Power fail detect. Write protection. Communications. Non-DMA transfers between 8086 and the SIO. DMA transfers between memory and the SIO. Programming the ECR. Multidrop driver control Multidrop receiver clock detect. Baud rate clock source selection Channel B level changers. AC characteristics. DC characteristics References. Edge-connector pin list. Connector J4. Connector J5.                                                                                                                                                     |    |                                   | 4-44  |

| Connector J3. Jumpers. Switches. The memory addressing decode PROM. LED indicators. Test points. I/O-Port addresses vs. functions. Device pin functions. 8086 HMOS microprocessor. 8284 Clock driver. 8288 Bus controller. 8237-2 DMA controller. 8259A Interrupt controller. 8259A Interrupt controller.  5. I/O Memory Board  Overview. Operation by logic block. The RAM array. Disk control interface (DCI) I/O address decode. The I/O control register (IOCR). Control bits of the IOCR. Speaker LESs and switches. Programmable timer. Keyboard interface. Line printer interface. Real time clocks. Power fail detect. Write protection. Communications. Non-DMA transfers between 8086 and the SIO. DMA transfers between memory and the SIO. Programming the ECR. Multidrop driver control Multidrop driver control Multidrop receiver clock detect. Baud rate clocks source selection Channel B level changers AC characteristics. DC characteristics DC characteristics Edge-connector pin list Connector J4. Connector J5.                                                                                                                     |    |                                   | 4-44  |

| Jumpers Switches. The memory addressing decode PROM. LED indicators. Test points. I/O-Port addresses vs. functions. Device pin functions.  8086 HMOS microproccessor 8284 Clock driver. 8289 Bus arbiter. 8237-2 DMA controller. 8237-2 DMA controller. 8259A Interrupt controller.  Operation by logic block. The RAM array. Disk control interface (DCI) I/O address decode. The I/O control register (IOCR) Control bits of the IOCR. Speaker LESs and switches. Programmable timer Keyboard interface. Line printer interface. Real time clocks. Power fail detect. Write protection. Communications Non-DMA transfers between memory and the SIO. Programming the ECR. Multidrop driver control Multidrop receiver clock detect. Baud rate clock source selection. Channel B level changers. AC characteristics. References. Edge-connector pin list. Connector J4. Connector J5.                                                                                                                                                                                                                                                                      |    |                                   | 4-44  |

| Switches. The memory addressing decode PROM. LED indicators. Test points. I/O-Port addresses vs. functions. Device pin functions.  8086 HMOS microprocessor 8284 Clock driver. 8289 Bus arbiter. 8288 Bus controller 8237-2 DMA controller. 8259A Interrupt controller. 8259A Interrupt controller.  5. I/O Memory Board  Overview. Operation by logic block. The RAM array. Disk control interface (DCI) I/O address decode. The I/O control register (IOCR) Control bits of the IOCR. Status bits of the IOCR. Speaker LESs and switches Programmable timer. Keyboard interface. Line printer interface. Real time clocks. Power fail detect. Write protection. Communications. Non-DMA transfers between 8086 and the SIO. DMA transfers between memory and the SIO. Programming the ECR. Multidrop driver control Multidrop receiver clock detect. Baud rate clock source selection Channel B level changers. AC characteristics. DC characteristics. References. Edge-connector pin list Connector J4. Connector J5.                                                                                                                                   |    | Connector J3                      | 4-45  |

| The memory addressing decode PROM.  LED indicators. Test points.  I/O-Port addresses vs. functions.  Device pin functions.  8086 HMOS microproccessor  8284 Clock driver.  8289 Bus arbiter.  8287-2 DMA controller.  8237-2 DMA controller.  8259A Interrupt controller.  9259A Interrupt controller.  5. I/O Memory Board  Overview.  Operation by logic block.  The RAM array.  Disk control interface (DCI).  I/o address decode.  The I/O control register (IOCR).  Control bits of the IOCR.  Status bits of the IOCR.  Speaker LESs and switches.  Programmable timer.  Keyboard interface.  Line printer interface.  Real time clocks.  Power fail detect.  Write protection.  Communications.  Non-DMA transfers between 8086 and the SIO.  DMA transfers between memory and the SIO.  Programming the ECR.  Multidrop driver control.  Multidrop receiver clock detect.  Baud rate clock source selection.  Channel B level changers.  AC characteristics.  DC characteristics.  Edge-connector Ji.                                                                                                                                               |    |                                   | 4-48  |

| Test points. I/O-Port addresses vs. functions. Device pin functions.  8086 HMOS microproocessor 8284 Clock driver. 8289 Bus arbiter. 8288 Bus controller. 8237-2 DMA controller. 8259A Interrupt controller. 8259A Interrupt controller.  5. I/O Memory Board  Overview. Operation by logic block. The RAM array. Disk control interface (DCI) I/O address decode. The I/O control register (IOCR). Control bits of the IOCR. Speaker LESs and switches. Programmable timer. Keyboard interface. Line printer interface. Real time clocks. Power fail detect. Write protection. Communications. Non-DMA transfers between 8086 and the SIO. Programming the ECR. Multidrop driver control. Multidrop receiver clock detect. Baud rate clock source selection. Channel B level changers. Channel B level changers. Characteristics. DC characteristics. Edge-connector Ji.                                                                                                                                                                                                                                                                                   |    | Switches                          | 4-48  |

| Test points.  I/O-Port addresses vs. functions  Device pin functions.  8086 HMOS microprocessor.  8284 Clock driver.  8289 Bus arbiter.  8288 Bus controller.  8237-2 DMA controller.  8259A Interrupt controller.  8259A Interrupt controller.  5. I/O Memory Board  Overview.  Operation by logic block.  The RAM array.  Disk control interface (DCI)  I/O address decode.  The I/O control register (IOCR)  Control bits of the IOCR.  Status bits of the IOCR.  Speaker LESs and switches.  Programmable timer.  Keyboard interface.  Line printer interface.  Real time clocks.  Power fail detect.  Write protection.  Communications.  Non-DMA transfers between 8086 and the SIO.  DMA transfers between memory and the SIO.  Programming the ECR.  Multidrop driver control.  Multidrop receiver clock detect.  Baud rate clock source selection.  Channel B level changers.  AC characteristics.  DC characteristics.  DC characteristics.  References.  Edge-connector pin list.  Connector J4.  Connector J5.                                                                                                                                  |    | The memory addressing decode PROM | 4-48  |

| I/O-Port addresses vs. functions.  Device pin functions.  8086 HMOS microprocessor.  8284 Clock driver.  8288 Bus arbiter.  8288 Bus controller.  8237-2 DMA controller.  8259A Interrupt controller.  8259A Interrupt controller.  70 Memory Board  Overview.  Operation by logic block.  The RAM array.  Disk control interface (DCI).  I/O address decode.  The I/O control register (IOCR).  Control bits of the IOCR.  Speaker LESs and switches.  Programmable timer.  Keyboard interface.  Line printer interface.  Real time clocks.  Power fail detect.  Write protection.  Communications.  Non-DMA transfers between 8086 and the SIO.  DMA transfers between memory and the SIO.  Programming the ECR.  Multidrop driver control.  Multidrop receiver clock detect.  Baud rate clock source selection.  Channel B level changers.  AC characteristics.  DC characteristics.  DC characteristics.  Edge-connector pin list.  Connector J4.  Connector J5.                                                                                                                                                                                        |    | LED indicators                    | 4-49  |

| Device pin functions.  8086 HMOS microproocessor.  8284 Clock driver.  8289 Bus arbiter.  8238 Bus controller.  8237-2 DMA controller.  8259A Interrupt controller.  5. I/O Memory Board  Overview.  Operation by logic block.  The RAM array.  Disk control interface (DCI).  I/O address decode.  The I/O control register (IOCR).  Control bits of the IOCR.  Status bits of the IOCR.  Speaker LESs and switches.  Programmable timer.  Keyboard interface.  Line printer interface.  Real time clocks.  Power fail detect.  Write protection.  Communications.  Non-DMA transfers between 8086 and the SIO.  DMA transfers between memory and the SIO.  Programming the ECR.  Multidrop driver control.  Multidrop driver control.  Multidrop receiver clock detect.  Baud rate clock source selection.  Channel B level changers.  Channel B level changers.  AC characteristics.  DC characteristics.  DC characteristics.  Edge-connector pin list.  Connector J4.  Connector J5.                                                                                                                                                                   |    | Test points                       | 4-49  |

| Device pin functions.  8086 HMOS microproocessor.  8284 Clock driver.  8289 Bus arbiter.  8238 Bus controller.  8237-2 DMA controller.  8259A Interrupt controller.  5. I/O Memory Board  Overview.  Operation by logic block.  The RAM array.  Disk control interface (DCI).  I/O address decode.  The I/O control register (IOCR).  Control bits of the IOCR.  Status bits of the IOCR.  Speaker LESs and switches.  Programmable timer.  Keyboard interface.  Line printer interface.  Real time clocks.  Power fail detect.  Write protection.  Communications.  Non-DMA transfers between 8086 and the SIO.  DMA transfers between memory and the SIO.  Programming the ECR.  Multidrop driver control.  Multidrop driver control.  Multidrop receiver clock detect.  Baud rate clock source selection.  Channel B level changers.  Channel B level changers.  AC characteristics.  DC characteristics.  DC characteristics.  Edge-connector pin list.  Connector J4.  Connector J5.                                                                                                                                                                   |    | I/O-Port addresses vs. functions  | 4-49  |

| 8086 HMOS microproocessor 8284 Clock driver. 8289 Bus arbiter. 8288 Bus controller. 8237-2 DMA controller 8259A Interrupt controller 8259A Interrupt controller  5. I/O Memory Board  Overview. Operation by logic block. The RAM array. Disk control interface (DCI) I/O address decode. The I/O control register (IOCR) Control bits of the IOCR. Status bits of the IOCR. Speaker LESs and switches. Programmable timer. Keyboard interface. Line printer interface. Real time clocks. Power fail detect. Write protection. Communications. Non-DMA transfers between 8086 and the SIO. Programming the ECR. Multidrop driver control. Multidrop receiver clock detect. Baud rate clock source selection Channel B level changers. Channel B level changers. AC characteristics. DC characteristics. References. Edge-connector pin list. Connector J4. Connector J5.                                                                                                                                                                                                                                                                                    |    |                                   | 4-50  |

| 8284 Clock driver. 8289 Bus arbiter. 8237-2 DMA controller. 8237-2 DMA controller. 8259A Interrupt controller.  8259A Interrupt controller.  5. I/O Memory Board  Overview. Operation by logic block. The RAM array. Disk control interface (DCI). I/O address decode. The I/O control register (IOCR). Control bits of the IOCR. Status bits of the IOCR. Speaker LESs and switches. Programmable timer. Keyboard interface. Line printer interface. Real time clocks. Power fail detect. Write protection. Communications. Non-DMA transfers between 8086 and the SIO. DMA transfers between memory and the SIO. Programming the ECR. Multidrop driver control. Multidrop driver control. Multidrop receiver clock detect. Baud rate clock source selection. Channel B level changers. AC characteristics. DC characteristics. References. Edge-connector pin list. Connector J4. Connector J5.                                                                                                                                                                                                                                                           |    |                                   | 4-50  |

| 8289 Bus arbiter. 8288 Bus controller. 8237-2 DMA controller. 8259A Interrupt controller.  5. I/O Memory Board  Overview. Operation by logic block. The RAM array. Disk control interface (DCI). I/O address decode. The I/O control register (IOCR). Control bits of the IOCR. Status bits of the IOCR. Speaker LESs and switches. Programmable timer. Keyboard interface. Line printer interface. Real time clocks. Power fail detect. Write protection. Communications. Non-DMA transfers between 8086 and the SIO. Programming the ECR. Multidrop driver control. Multidrop driver control. Multidrop receiver clock detect. Baud rate clock source selection. Channel B level changers. Channel B level changers. AC characteristics. DC characteristics. References. Edge-connector pin list. Connector J4. Connector J4.                                                                                                                                                                                                                                                                                                                             |    |                                   | 4-57  |

| 8288 Bus controller. 8237-2 DMA controller. 8259A Interrupt controller.  5. I/O Memory Board  Overview. Operation by logic block. The RAM array. Disk control interface (DCI). I/O address decode. The I/O control register (IOCR). Control bits of the IOCR. Status bits of the IOCR. Speaker LESs and switches. Programmable timer. Keyboard interface. Line printer interface. Real time clocks. Power fail detect. Write protection. Communications. Non-DMA transfers between 8086 and the SIO. DMA transfers between memory and the SIO. Programming the ECR. Multidrop driver control. Multidrop receiver clock detect. Baud rate clock source selection. Channel B level changers. AC characteristics. DC characteristics. References. Edge-connector pin list. Connector J4. Connector J5.                                                                                                                                                                                                                                                                                                                                                         |    |                                   | 4-62  |

| 8237-2 DMA controller. 8259A Interrupt controller.  5. I/O Memory Board  Overview. Operation by logic block. The RAM array. Disk control interface (DCI) I/O address decode. The I/O control register (IOCR) Control bits of the IOCR. Status bits of the IOCR. Speaker LESs and switches. Programmable timer. Keyboard interface. Line printer interface. Real time clocks. Power fail detect. Write protection. Communications. Non-DMA transfers between 8086 and the SIO. Programming the ECR. Multidrop driver control. Multidrop receiver clock detect. Baud rate clock source selection. Channel B level changers. AC characteristics. DC characteristics. References. Edge-connector pin list. Connector J4. Connector J5.                                                                                                                                                                                                                                                                                                                                                                                                                          |    |                                   | 4-68  |

| 8259A Interrupt controller.  5. I/O Memory Board  Overview. Operation by logic block. The RAM array. Disk control interface (DCI). I/O address decode. The I/O control register (IOCR). Control bits of the IOCR. Status bits of the IOCR. Speaker LESs and switches. Programmable timer Keyboard interface. Line printer interface. Real time clocks. Power fail detect. Write protection. Communications. Non-DMA transfers between 8086 and the SIO. Programming the ECR. Multidrop driver control. Multidrop receiver clock detect. Baud rate clock source selection. Channel B level changers. AC characteristics. DC characteristics. References. Edge-connector pin list. Connector J4. Connector J5.                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |                                   | 4-72  |

| Overview. Operation by logic block. The RAM array. Disk control interface (DCI). I/O address decode. The I/O control register (IOCR). Control bits of the IOCR. Status bits of the IOCR. Speaker LESs and switches. Programmable timer. Keyboard interface. Line printer interface. Real time clocks. Power fail detect. Write protection. Communications. Non-DMA transfers between 8086 and the SIO. DMA transfers between memory and the SIO. Programming the ECR. Multidrop driver control. Multidrop receiver clock detect. Baud rate clock source selection. Channel B level changers. AC characteristics. DC characteristics. References. Edge-connector pin list Connector J4. Connector J5.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |                                   | 4-79  |

| Overview. Operation by logic block. The RAM array. Disk control interface (DCI)  I/O address decode. The I/O control register (IOCR) Control bits of the IOCR. Status bits of the IOCR. Speaker LESs and switches. Programmable timer. Keyboard interface. Line printer interface. Real time clocks. Power fail detect. Write protection. Communications. Non-DMA transfers between 8086 and the SIO. Programming the ECR. Multidrop driver control. Multidrop driver clock detect. Baud rate clock source selection. Channel B level changers. AC characteristics. DC characteristics. References. Edge-connector pin list Connector J4. Connector J5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | O23311 Interrupt controller       | 4 1 2 |

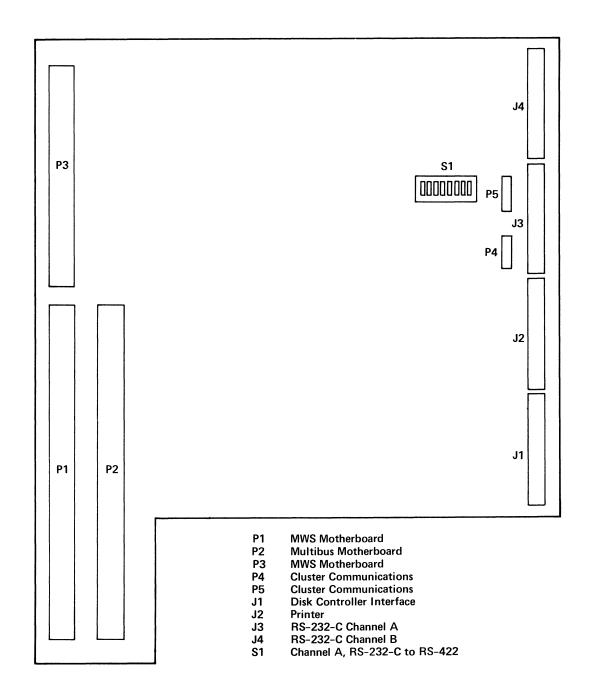

| Operation by logic block.  The RAM array.  Disk control interface (DCI).  I/O address decode.  The I/O control register (IOCR).  Control bits of the IOCR.  Status bits of the IOCR.  Speaker LESs and switches.  Programmable timer.  Keyboard interface.  Line printer interface.  Real time clocks.  Power fail detect.  Write protection.  Communications.  Non-DMA transfers between 8086 and the SIO.  DMA transfers between memory and the SIO.  Programming the ECR.  Multidrop driver control.  Multidrop receiver clock detect.  Baud rate clock source selection.  Channel B level changers.  Channel B level changers.  AC characteristics.  BC characteristics.  References.  Edge-connector pin list.  Connector J4.  Connector J5.                                                                                                                                                                                                                                                                                                                                                                                                           | 5. | I/O Memory Board                  |       |

| The RAM array.  Disk control interface (DCI)  I/O address decode.  The I/O control register (IOCR).  Control bits of the IOCR.  Status bits of the IOCR.  Speaker LESs and switches.  Programmable timer.  Keyboard interface.  Line printer interface.  Real time clocks.  Power fail detect.  Write protection.  Communications.  Non-DMA transfers between 8086 and the SIO.  DMA transfers between memory and the SIO.  Programming the ECR.  Multidrop driver control.  Multidrop receiver clock detect.  Baud rate clock source selection.  Channel B level changers.  Channel B level changers.  AC characteristics.  DC characteristics.  References.  Edge-connector pin list.  Connector J4.  Connector J5.                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | Overview                          | 5-1   |

| Disk control interface (DCI)  I/O address decode  The I/O control register (IOCR) Control bits of the IOCR. Status bits of the IOCR.  Speaker LESs and switches.  Programmable timer  Keyboard interface.  Line printer interface.  Real time clocks.  Power fail detect  Write protection  Communications  Non-DMA transfers between 8086 and the SIO.  DMA transfers between memory and the SIO.  Programming the ECR.  Multidrop driver control.  Multidrop receiver clock detect.  Baud rate clock source selection.  Channel B level changers.  Channel B level changers.  AC characteristics.  DC characteristics.  References.  Edge-connector pin list.  Connector J4.  Connector J5.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | Operation by logic block          | 5-1   |

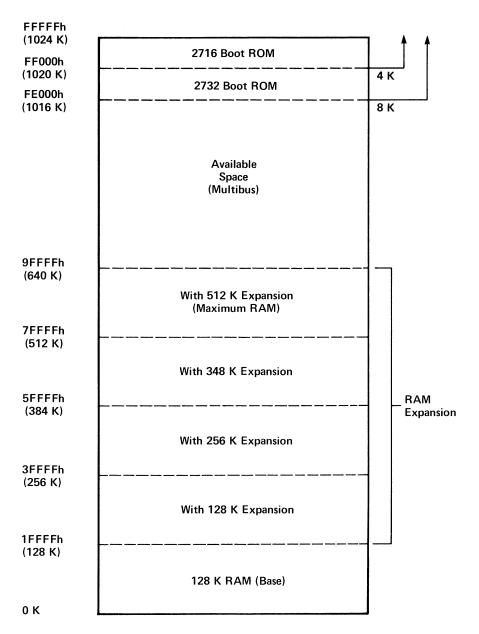

| I/O address decode. The I/O control register (IOCR). Control bits of the IOCR. Status bits of the IOCR. Speaker LESs and switches. Programmable timer. Keyboard interface. Line printer interface. Real time clocks. Power fail detect. Write protection. Communications. Non-DMA transfers between 8086 and the SIO. Programming the ECR. Multidrop driver control. Multidrop receiver clock detect. Baud rate clock source selection. Channel B level changers. AC characteristics. DC characteristics. References. Edge-connector pin list. Connector J4. Connector J5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | The RAM array                     | 5-3   |

| The I/O control register (IOCR) Control bits of the IOCR. Status bits of the IOCR. Speaker LESs and switches. Programmable timer. Keyboard interface. Line printer interface. Real time clocks. Power fail detect. Write protection. Communications. Non-DMA transfers between 8086 and the SIO. Programming the ECR. Multidrop driver control. Multidrop receiver clock detect. Baud rate clock source selection. Channel B level changers. Channel B level changers. AC characteristics. DC characteristics. References. Edge-connector pin list. Connector J4. Connector J5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | Disk control interface (DCI)      | 5-5   |

| Control bits of the IOCR.  Status bits of the IOCR.  Speaker LESs and switches.  Programmable timer.  Keyboard interface.  Line printer interface.  Real time clocks.  Power fail detect.  Write protection.  Communications.  Non-DMA transfers between 8086 and the SIO.  DMA transfers between memory and the SIO.  Programming the ECR.  Multidrop driver control.  Multidrop driver control.  Multidrop receiver clock detect.  Baud rate clock source selection.  Channel B level changers.  Channel B level changers.  AC characteristics.  DC characteristics.  Edge-connector pin list.  Connector J4.  Connector J5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    | I/O address decode                | 5-7   |

| Control bits of the IOCR.  Status bits of the IOCR.  Speaker LESs and switches.  Programmable timer.  Keyboard interface.  Line printer interface.  Real time clocks.  Power fail detect.  Write protection.  Communications.  Non-DMA transfers between 8086 and the SIO.  DMA transfers between memory and the SIO.  Programming the ECR.  Multidrop driver control.  Multidrop driver control.  Multidrop receiver clock detect.  Baud rate clock source selection.  Channel B level changers.  Channel B level changers.  AC characteristics.  DC characteristics.  Edge-connector pin list.  Connector J4.  Connector J5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    | The I/O control register (IOCR)   | 5-8   |

| Status bits of the IOCR.  Speaker LESs and switches. Programmable timer. Keyboard interface. Line printer interface. Real time clocks. Power fail detect. Write protection. Communications. Non-DMA transfers between 8086 and the SIO. DMA transfers between memory and the SIO. Programming the ECR. Multidrop driver control. Multidrop receiver clock detect. Baud rate clock source selection. Channel B level changers. Channel B level changers. AC characteristics. BC characteristics. References. Edge-connector pin list. Connector J4. Connector J5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | Control bits of the IOCR          | 5-9   |

| Programmable timer  Keyboard interface.  Line printer interface.  Real time clocks.  Power fail detect.  Write protection.  Communications.  Non-DMA transfers between 8086 and the SIO.  DMA transfers between memory and the SIO.  Programming the ECR.  Multidrop driver control.  Multidrop receiver clock detect.  Baud rate clock source selection.  Channel B level changers.  Channel B level changers.  AC characteristics.  DC characteristics.  References.  Edge-connector pin list.  Connector J4.  Connector J5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |                                   | 5-10  |

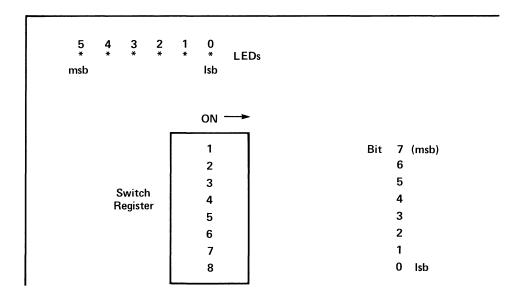

| Programmable timer  Keyboard interface.  Line printer interface.  Real time clocks.  Power fail detect.  Write protection.  Communications.  Non-DMA transfers between 8086 and the SIO.  DMA transfers between memory and the SIO.  Programming the ECR.  Multidrop driver control.  Multidrop receiver clock detect.  Baud rate clock source selection.  Channel B level changers.  Channel B level changers.  AC characteristics.  DC characteristics.  References.  Edge-connector pin list.  Connector J4.  Connector J5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    | Speaker LESs and switches         | 5-11  |

| Keyboard interface. Line printer interface. Real time clocks. Power fail detect. Write protection. Communications.  Non-DMA transfers between 8086 and the SIO. DMA transfers between memory and the SIO. Programming the ECR. Multidrop driver control. Multidrop receiver clock detect. Baud rate clock source selection. Channel B level changers. Channel B level changers. AC characteristics. DC characteristics. References. Edge-connector pin list. Connector J4. Connector J5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |                                   | 5-11  |

| Line printer interface. Real time clocks. Power fail detect. Write protection. Communications.  Non-DMA transfers between 8086 and the SIO. DMA transfers between memory and the SIO. Programming the ECR. Multidrop driver control. Multidrop receiver clock detect. Baud rate clock source selection. Channel B level changers. Channel B level changers. AC characteristics. DC characteristics. References. Edge-connector pin list. Connector J4. Connector J5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |                                   | 5-12  |

| Real time clocks.  Power fail detect.  Write protection.  Communications.  Non-DMA transfers between 8086 and the SIO.  DMA transfers between memory and the SIO.  Programming the ECR.  Multidrop driver control.  Multidrop receiver clock detect.  Baud rate clock source selection.  Channel B level changers.  Channel B level changers.  AC characteristics.  DC characteristics.  References.  Edge-connector pin list.  Connector J4.  Connector J5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |                                   | 5-12  |

| Power fail detect. Write protection. Communications  Non-DMA transfers between 8086 and the SIO.  DMA transfers between memory and the SIO.  Programming the ECR.  Multidrop driver control.  Multidrop receiver clock detect.  Baud rate clock source selection.  Channel B level changers.  Channel B level changers.  AC characteristics.  DC characteristics.  References.  Edge-connector pin list.  Connector J4.  Connector J5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |                                   | 5-13  |

| Write protection  Communications  Non-DMA transfers between 8086 and the SIO  DMA transfers between memory and the SIO  Programming the ECR  Multidrop driver control  Multidrop receiver clock detect  Baud rate clock source selection  Channel B level changers  Channel B level changers  AC characteristics  DC characteristics  References  Edge-connector pin list  Connector J4  Connector J5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |                                   | 5-13  |

| Communications  Non-DMA transfers between 8086 and the SIO  DMA transfers between memory and the SIO  Programming the ECR  Multidrop driver control  Multidrop receiver clock detect  Baud rate clock source selection  Channel B level changers  Channel B level changers  AC characteristics  DC characteristics  References  Edge-connector pin list  Connector J4  Connector J5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |                                   | 5-13  |

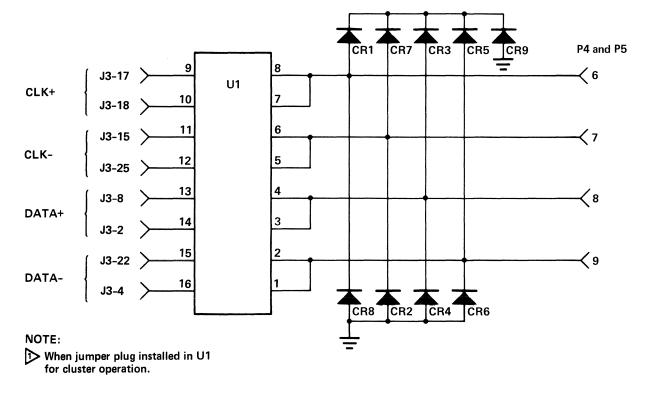

| Non-DMA transfers between 8086 and the SIO  DMA transfers between memory and the SIO  Programming the ECR  Multidrop driver control  Multidrop receiver clock detect  Baud rate clock source selection  Channel B level changers  Channel B level changers  AC characteristics  DC characteristics  References  Edge-connector pin list  Connector J4  Connector J5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |                                   | 5-14  |

| DMA transfers between memory and the SIO  Programming the ECR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |                                   | 5-14  |

| Programming the ECR.  Multidrop driver control.  Multidrop receiver clock detect.  Baud rate clock source selection.  Channel B level changers.  Channel B level changers.  AC characteristics.  DC characteristics.  References.  Edge-connector pin list.  Connector J4.  Connector J5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |                                   | 5-15  |

| Multidrop driver control  Multidrop receiver clock detect  Baud rate clock source selection  Channel B level changers  Channel B level changers  AC characteristics  DC characteristics  References  Edge-connector pin list  Connector J4  Connector J5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |                                   | 5-15  |

| Multidrop receiver clock detect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |                                   | 5-16  |

| Baud rate clock source selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |                                   | 5-16  |

| Channel B level changers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |                                   | 5-16  |

| Channel B level changers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |                                   | 5-18  |

| AC characteristics  DC characteristics  References  Edge-connector pin list  Connector J4  Connector J5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |                                   | 5-18  |

| DC characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |                                   |       |

| References  Edge-connector pin list  Connector J4  Connector J5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |                                   | 5-19  |

| Edge-connector pin list                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |                                   | 5-30  |

| Connector J4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |                                   | 5-32  |

| Connector J5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |                                   | 5-32  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |                                   | 5-32  |

| Jumpers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |                                   | 5-33  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | Jumpers                           | 5-36  |

|    | Switches  Programmable LED and audio  Test points  I/O Port addresses and functions  Device pin functions  8251A USART  8253 programmable timer  Z80A SIO/2                                                                                                                                                                                      | 5-36<br>5-37<br>5-37<br>5-38<br>5-39<br>5-46<br>5-49                                            |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| 6. | RAM Expansion Board                                                                                                                                                                                                                                                                                                                              |                                                                                                 |