INTEGRATED CIRCUITS SERIES

# MOS DIGITAL INTEGRATED CIRCUITS

GENERAL MOTORS CORPORATION MILWAUKEE, WISCONSIN 53201

## MOS DIGITAL INTEGRATED CIRCUITS

a programed instructional text

(c) General Motors Corporation, 1972

programed by:

EUGENE DEWEESE

### TABLE OF CONTENTS

|                                   | NO.         |

|-----------------------------------|-------------|

| INTRODUCTION                      | 1           |

| MOSFET CONSTRUCTION AND OPERATION | 6           |

| REVIEW                            | 35          |

| MOSFET SYMBOLS                    | 37          |

| REVIEW                            | 46          |

| MOSFET CIRCUITS                   | 48          |

| REVIEW                            | 69          |

| MOSFET CIRCUITS (Continued)       | 71          |

| REVIEW                            | 92          |

| COMPLEMENTARY MOS                 | 94          |

| REVIEW                            | 115         |

| MOSFET STRUCTURES                 | 117         |

| REVIEW                            | 136         |

| SWITCHING SPEED                   | 138         |

| REVIEW                            | 160         |

| N-CHANNEL MOSFET'S                | 162         |

| REVIEW                            | 169         |

| TESTS                             | PAGE<br>NO. |

| SAMPLE TEST                       | 152         |

| SAMPLE TEST ANSWERS               | 159         |

| EXAMINATION                       | 161         |

### HOW TO USE THIS TEXT

This is a programed text. Unlike a conventional text, it is divided into numbered sections called frames. In most cases, each frame represents a single concept or unit of information. As in all programed texts, the student must actively participate in the program to obtain full benefit.

To enable the student to participate, the majority of frames contain one or more questions. The answer to each question is shaded and always appears in the beginning of the following frame.

There are two basic types of questions used in this text. The first is used with "lecture" frames; i.e., frames which present complete units of information or concepts. This type of question simply tests your comprehension of the material presented in that frame.

The other type of question is used with frames in which the information or concept is intentionally left incomplete. In these frames, which are in the majority in this text, the student is required to use whatever information he is given (either in the text of the frame or in the accompanying illustration) to answer the question. The answer to the question, then, completes the concept or unit of information presented in the frame.

When you have completed the text, do the sample test at the end of the text. Correct the sample test using the answer sheet provided at the end of the test. If your score is 80 or higher and you are satisfied with your comprehension of the material presented in the text, complete the examination (bound into the text following the sample test) and submit it for correction.

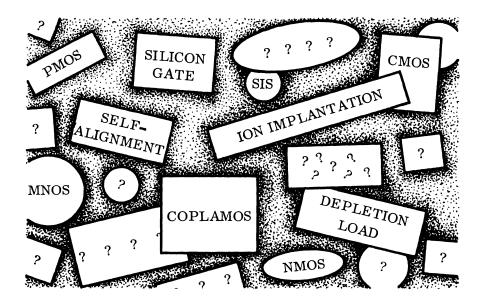

### INTRODUCTION

Metal-Oxide-Semiconductor (MOS) technology is one of the fastest changing fields in electronics. New techniques are being experimented with or put into production almost daily. It would be impossible to publish a book covering all the latest techniques and devices; it would be out of date by the time it was in print. The purpose of this text, therefore, is to explain the basics of MOS and to provide the background knowledge necessary for an understanding of state-of-the-art discussions and articles. In this way it is similar to the Bipolar Digital Integrated Circuits text. When you finish this text, you will not be an MOS expert, but you will at least have a good idea of what MOS is all about, and articles describing the latest MOS devices and techniques should make sense to you.

### STUDENT PREREQUISITES

Before starting this text, you should be able to:

- 1. Identify the components in a cross-sectional drawing of a bipolar integrated circuit.

- 2. Define diffusion, epitaxial growth, and deposition as they apply to integrated circuits.

- 3. Identify schematic drawings and state characteristics of the different types of bipolar digital integrated circuits such as DTL and TTL.

- 4. Given the polarity of the applied voltage and the type of current carriers (holes or electrons), determine the direction the current carriers will flow.

- 5. Identify the logic function or functions represented by a given switching diagram or truth table.

- 6. Describe the results of forward or reverse biasing a P-N junction.

### STUDENT LEARNING OBJECTIVES

Upon completion of this text, you will be able to:

- 1. Identify schematics, state characteristics, and explain operation of inverters, NAND gates, and NOR gates of each of the following types:

- A. PMOS with enhancement MOSFET's used as loads

- B. PMOS with depletion MOSFET's used as loads

- C. CMOS

- 2. Given either a schematic symbol or a cross-sectional drawing of the physical construction, identify each of the four basic types of MOSFET and, given the polarity of the applied voltage, identify the source and drain.

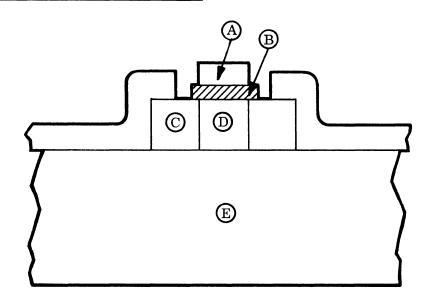

- 3. State characteristics, identify cross-sectional drawings, and identify steps in the construction of each of the following:

- A. MNOS

- B. MOSFET's using self-aligning metal gates

- C. MOSFET's using self-aligning silicon gates

- D. SIS

- E. Coplamos

- 4. Define and/or identify the effects of the following:

- A. Threshold voltage

- B. Pinch-off voltage

- C. Field threshold

- D. Threshold adjustment

- E. Ion implantation

- F. Self-alignment

- G. Gate capacitance

- H. Parasitic capacitance

- I. Parasitic current

- J. Polysilicon

- K. IGFET

- L. Work function

- M. Passivation

### INTRODUCTION

| (1) | In any discussion of MOS devices or technological | gy, the first thing to do is establish a |

|-----|---------------------------------------------------|------------------------------------------|

|     | few definitions and then clarify the definition   | s. As you probably know, MOS is the      |

|     | acronym for M                                     | O                                        |

|     | S                                                 |                                          |

### (2) Metal Oxide Semiconductor

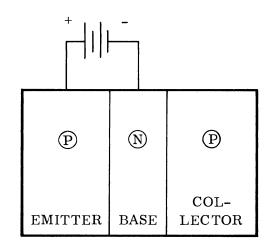

This sounds as if it refers to the materials from which MOS devices are made, and, in a way, this is true — but not completely. Notice, for instance, that a bipolar transistor is actually constructed of metal, oxide, and semiconductor materials. In a bipolar transistor, however, the "active" parts are all made of doped sections of the semiconductor. The oxide is simply an insulator, and the metal is used only for connections to other components. In MOS, as we will see shortly, metal and oxide are integral parts of the transistor. A device made of metal, oxide, and semiconductor materials, then, would be considered \_\_\_\_\_\_\_\_ (only MOS/only bipolar/either bipolar or MOS).

### (3) either bipolar or MOS

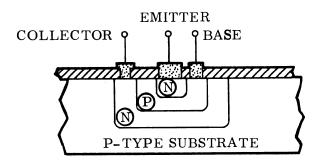

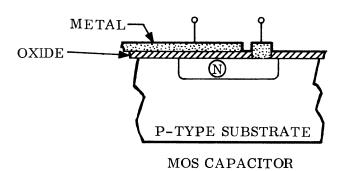

For example, the transistor in the previous frame was bipolar. The capacitor shown here would be considered MOS because one plate is metal, the other is semiconductor, and the dielectric is oxide.

Even this definition, however, can be misleading. The first MOS devices were strictly metal-oxide-semiconductor devices; but, since that time, other materials have been used in addition to or in place of the original three. For example, nitride is sometimes used in place of oxide. Even so, the general term MOS is still applied to these devices. Some of the other materials and their functions will be discussed later.

(1)

**(2)**

BIPOLAR TRANSISTOR

(3)

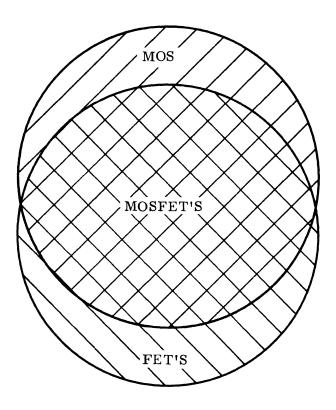

- (4) The other important acronym in this text is FET, which stands for Field Effect Transistor. A FET is simply a transistor which is controlled not by biasing a P-N junction but by the electric field generated by an applied voltage. How this field effect works will be explained shortly, but first there are a couple of general statements that should be made about MOS and FET's.

- 1. Most but not all MOS devices are FET's. (There are, for instance, the MOS capacitors mentioned above.)

- 2. Most but not all FET's are MOS. (There are also junction FET's JFET's which, while utilizing a voltage field effect for control, do not utilize metal, oxide, or any direct substitute as integral parts of their construction.)

| It would seem lo | ogical, then, | to refer to | an MOS | device | which is | also : | an 1 | FET | as |

|------------------|---------------|-------------|--------|--------|----------|--------|------|-----|----|

| a/an             |               |             | _      |        |          |        |      |     |    |

### (5) MOSFET

MOSFET's — MOS Field Effect Transistors — are what we will be covering in this text. There is one more acronym to be introduced first, however: IGFET. The FET part still stands for Field Effect Transistor; the IG stands for Insulated Gate. All you need to remember at this point is that IGFET and MOSFET can, for our purposes, be used interchangeably. The reason for this will become clear as we get into the construction and operation of MOSFET's.

| Which of the | following | terms aı | re synonyı | mous? | MOS, | FET, | MOSFET, | JFET, |

|--------------|-----------|----------|------------|-------|------|------|---------|-------|

| IGFET        |           |          |            |       |      |      |         |       |

- (4) (5)

### MOSFET CONSTRUCTION AND OPERATION

| (6) MOSFET a | and IGFET | 7 |

|--------------|-----------|---|

|--------------|-----------|---|

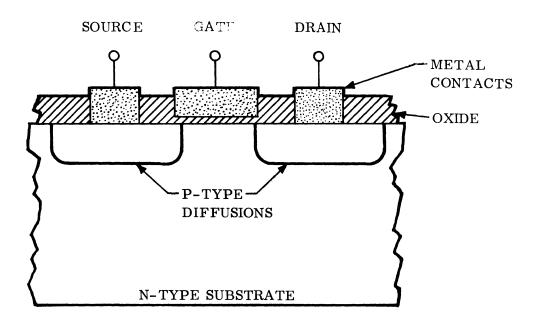

There are four basic types of MOSFET. We will start with the type that first came into general use and still accounts for a large percentage of all MOSFET's being manufactured. All four types are similar in principle so that, once this first type is understood, the other three can be explained by comparing them with this first type.

| Notice first that the MOSFET, like the bipolar transistor, has three elements.  | In  |

|---------------------------------------------------------------------------------|-----|

| the bipolar transistor, these elements were the emitter, base, and collector. I | 'n  |

| the MOSFET, the three elements are the                                          | _ , |

| , and                                                                           |     |

|                                                                                 |     |

(7) source, gate, and drain

In a general sense, the source is comparable to the emitter of a bipolar transistor, the gate to the base, and the drain to the collector. Similarly, the MOSFET can be compared to a vacuum tube, with the source corresponding to the cathode, the gate to the grid, and the drain to the plate. In fact, as we will see shortly, the similarity between MOSFET's and tubes is greater in some ways than the similarity between MOSFET's and bipolar transistors.

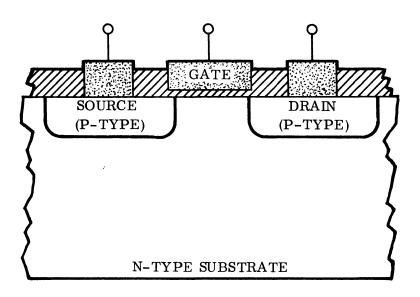

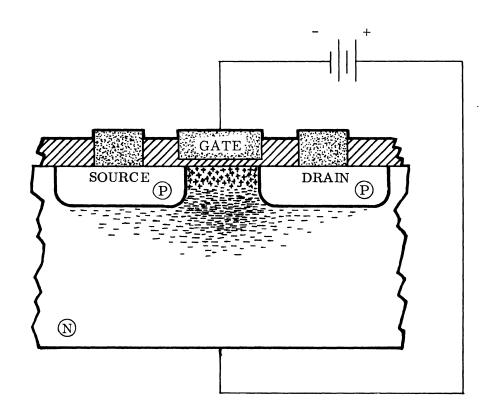

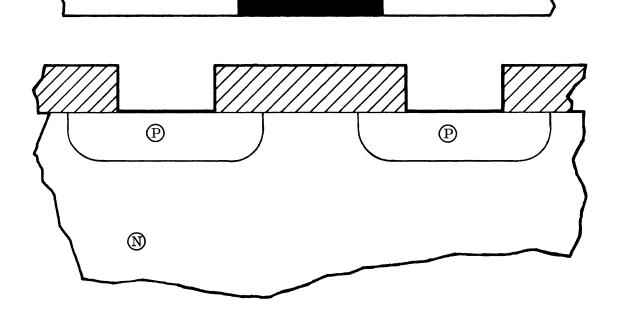

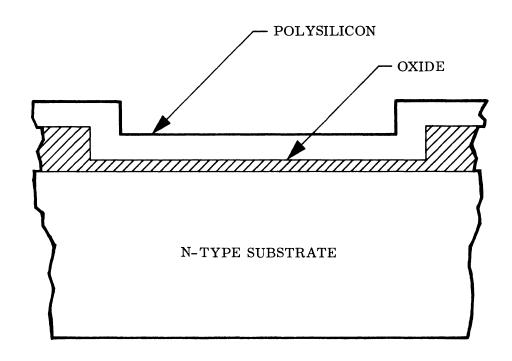

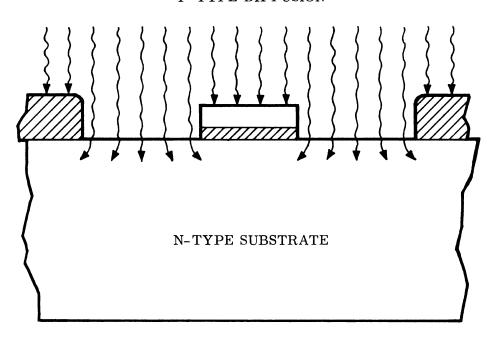

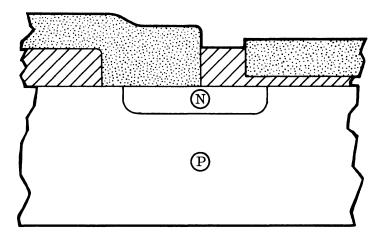

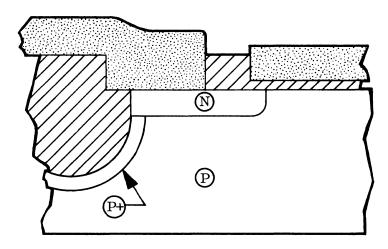

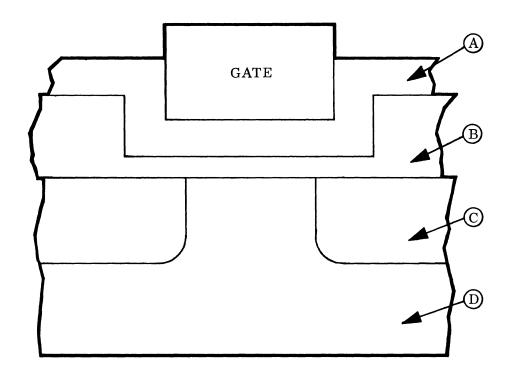

(8) The two diffused areas themselves are the source and drain. The metal contacts are simply that — contacts used to connect the drain and source to other circuits. Internally, the only path between the source and drain is through the substrate material. As indicated, the substrate in this type of MOSFET is N-type and the source and drain are both P-type. Regardless of the polarity of voltage applied between the source and drain, then, the resistance of the source-to-drain path would always be \_\_\_\_\_ (high/low) because one of the P-N junctions would always be \_\_\_\_\_ (forward/reverse) biased.

| (9)  | high                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

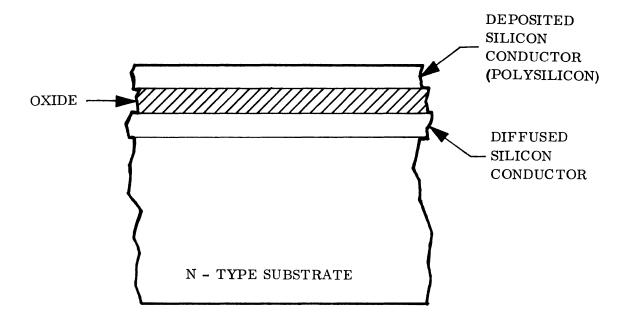

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | reverse                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | The same could be said of the emitter-to-collector path of a bipolar transistor. If this were a bipolar transistor, it could be turned on by applying a negative voltage to the substrate (or "base"). This would forward bias the transistor and allow a heavy current flow as long as the drain was positive with respect to the source. In the MOSFET, this (can also/can not) be done because the gate is (connected to/insulated from) the substrate. |

| (10) | oun not                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | insulated from                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | Notice that we said "gate" rather than "gate contact". This is because the metal itself is the gate. It is not simply a contact as is the case for the source and drain contacts. Thus, as was stated earlier, the FET is constructed of metal, oxide, and semiconductor and is therefore an MOS device. The fact that the gate is insulated from the substrate, as well as from the source and drain, is the reason the MOSFET is also known as a/an FET. |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| (11) | Insulaced Gate (4G)                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | Notice, however, that the oxide separating the gate from the substrate is (thinner/thicker) than the rest of the oxide.                                                                                                                                                                                                                                                                                                                                    |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

- (9) (10) (11)

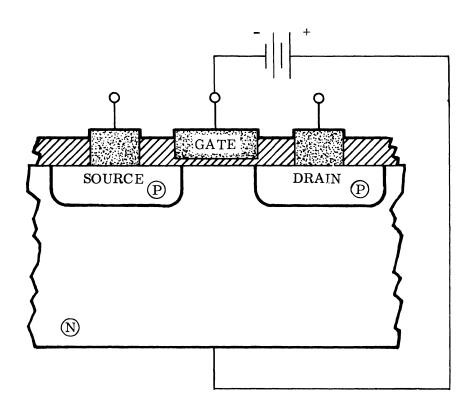

### (12) thinner

The oxide beneath the gate is made as thin as possible so that the field generated by the voltage applied to the gate will have as great an effect as possible on the substrate directly beneath the oxide. To see what this effect will be, we will apply a negative voltage to the gate as shown. Notice that the voltage is applied between the gate and the substrate. As a result of this gate voltage, the gate \_\_\_\_\_\_ (will/will not) draw current.

### (13) will not

(12) (13)

| (14) | electrons                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

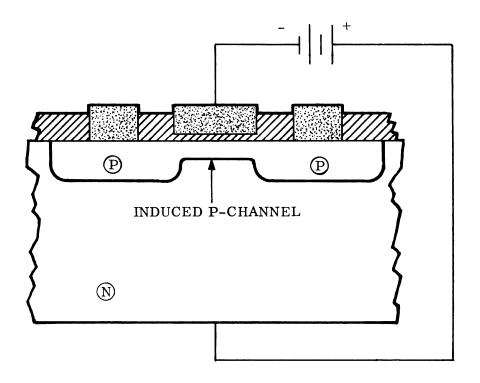

|      | holes                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | Since the substrate is N-type material, there are more free electrons than holes. How many more depends on how heavily it is doped. Even so, a sufficiently negative voltage applied to the gate will attract enough holes to make the MOSFET look like this. As indicated in the illustration, a "channel" is formed. The negative gate voltage, in effect, transforms a small part of the substrate into (N-type/P-type) material.                     |

| (15) | 72. truno.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| (15) | P-type $-$                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | As a result, the P-type material in the source is connected to the P-type material in the drain by the induced channel of P-type material in the substrate. With a negative voltage applied to the gate, then, the source-to-drain path has                                                                                                                                                                                                              |

| (16) | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | lower                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | Loosely speaking, we can say that the gate voltage at which this channel of P-type material — or simply the "P-channel" — appears is called the threshold voltage. (This definition will be modified and tightened later.) At first, when the gate voltage is equal to the threshold voltage, the channel is very thin. As the gate voltage is made more negative, the channel becomes thicker and the source-to-drain resistance (increases/decreases). |

- (14) (15) (16)

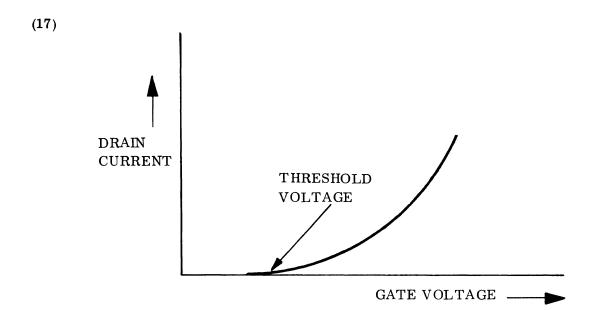

| (17) | decreases |

|------|-----------|

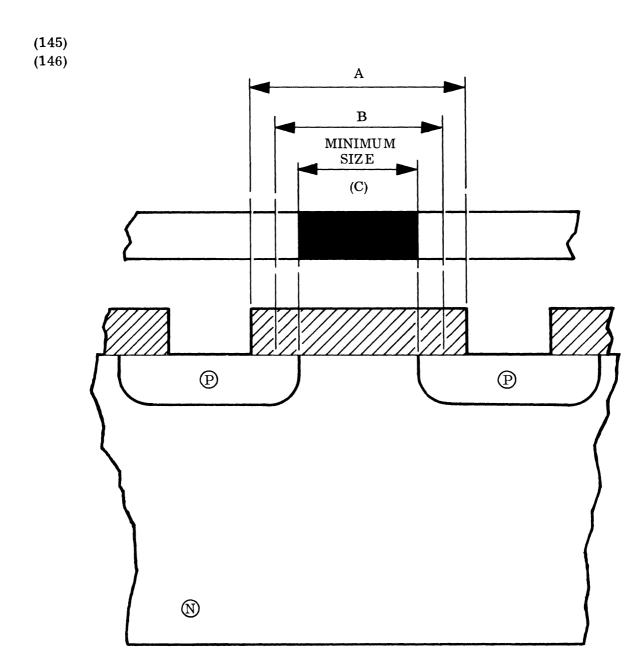

|------|-----------|

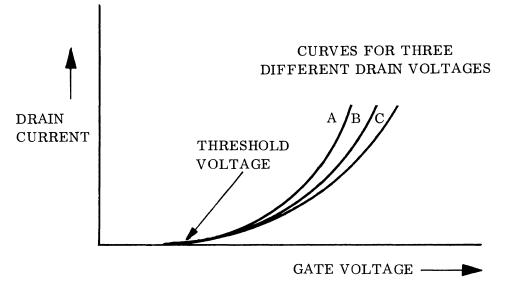

One way of looking at this effect is shown in the illustration. As you can see, there is no point at which the drain current can be said to start abruptly. It is a gradual process. For convenience, the threshold voltage is often defined as the gate voltage at which 10 microamperes of drain current flows. Based on this definition, you would expect the threshold voltage to be (somewhat dependent on/totally independent of) the drain voltage.

### (18) somewhat dependent on

The dependence, however, is quite slight. For our purposes we can say that the threshold voltage is essentially constant. As indicated in the illustration, the drain voltage has a greater effect on the slope of the curve than on the threshold voltage itself. Which of the three curves shown would represent the highest drain voltage? \_\_\_\_\_\_ The lowest? \_\_\_\_\_\_

(18)

### (19) A (highest)

C (lowest)

In some ways, then, our MOSFET is similar to a bipolar transistor. There are some important differences, however. One of the more obvious differences, which has been touched on already, is that, because of the oxide gate insulation, the current drawn by the gate will be essentially zero \_\_\_\_\_\_\_ (at all times/only when the MOSFET is turned on/only when the MOSFET is turned off).

### (20) at all times

The gate acts like a small capacitor and, except for leakage, draws current only while being charged. In a bipolar transistor, on the other hand, the base draws a fairly high current whenever the transistor is turned on.

Another difference can be seen if we take a closer look at the source-to-drain path and compare it to the emitter-to-collector path of a bipolar transistor. When a bipolar transistor is turned on, the two junctions are, in effect, forward biased as far as the collector current is concerned. Even so, the P-N junctions still exist, and there is a certain voltage drop developed across these junctions no matter how forward biased they are (short of total breakdown, of course). Since there are no P-N junctions in the turned-on MOSFET, there are no corresponding voltage drops developed. The only voltage drop is a result of the resistance of the semiconductor material itself.

Assuming adequate gate and base voltages are available, which device could be made to exhibit the lower apparent resistance in a given circuit?

(19) (20)

### (21) A MOSFET

This does not mean that MOSFET's always have lower voltage drops than do bipolar transistors. It only means that, given sufficient gate voltage and the proper circuit, MOSFET's are capable of lower voltage drops than bipolar transistors, simply because MOSFET's, when turned on, do not have P-N junction voltage drops to contend with.

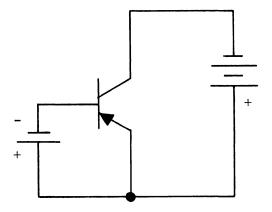

Still another difference between MOSFET's and bipolar transistors has to do with the direction of current flow. Current through a turned-on bipolar transistor would flow in only one direction. In the PNP transistor shown here, for instance, a heavy collector current would be flowing. But if the collector voltage were reversed, there would be no collector current. From what you have seen of the MOSFET so far, you would expect current to flow through the induced channel \_\_\_\_\_\_\_ (only in one direction/equally well in either direction).

### (22) equally well in either direction

Since there are no P-N junctions to be forward or reverse biased, current can flow in either direction as long as the gate is sufficiently negative to induce the P-channel between the source and drain. The polarity of the source and drain voltage would make no difference. Thus, you could say that MOSFET's are theoretically symmetrical, meaning that the drain and source are functionally interchangeable. (An explanation of how to tell which is the source and which is the drain is coming up shortly in the section on MOSFET symbology.)

(21)

(22)

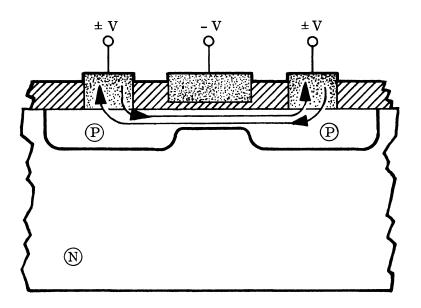

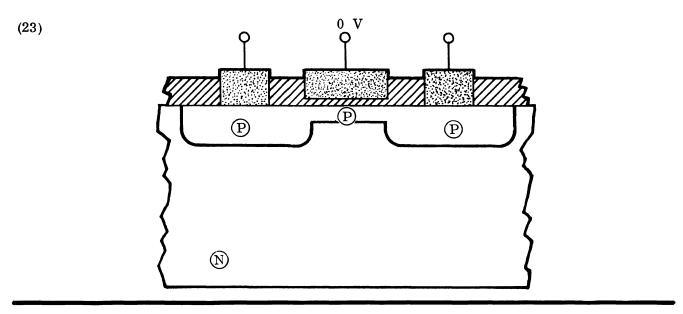

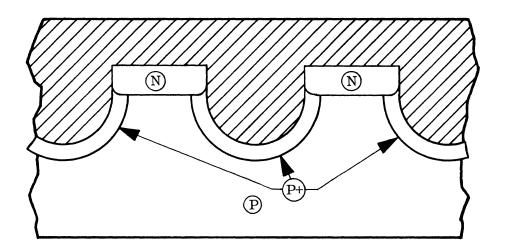

| (23) | has we said at the start, the MOSFET we have been discussing is only one of four basic types. A second type is shown here. This MOSFET is identical to the previous type except that there is a channel of P-type material built into the substrate between the source and drain. With no voltage applied to the gate, the source-to-drain path would present a (high/low) resistance.                                                                                          |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

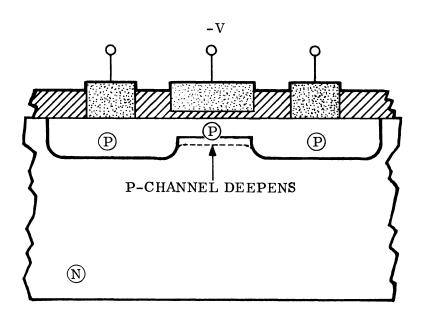

| (24) | low                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | In other words, this type of MOSFET would be turned on when no gate voltage is applied. Now, what happens if we apply a negative voltage to the gate, as we did to the first type of MOSFET? The negative gate voltage will, as before, repel the electrons and attract the holes in the substrate. As a result, the concentration of holes in the P-channel, as well as the depth of the P-channel, will increase, and the resistance of the channel will (increase/decrease). |

| (25) | decrease                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

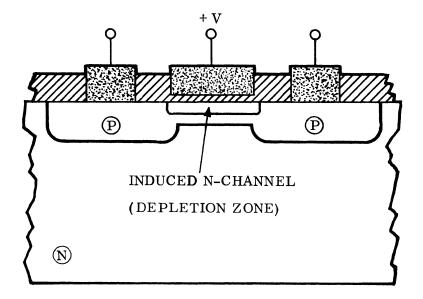

|      | Suppose, however, that a positive voltage is applied to the gate. A positive voltage would repel the holes and attract the electrons. It would cause a channel of material to form within the built-in channel of P-type material.                                                                                                                                                                                                                                              |

(24) (25)

| (26) | N-type |

|------|--------|

|------|--------|

The current, of course, cannot pass through the N-type material since, in order to do so, it would have to pass through two P-N junctions, one of which would always be reverse biased, regardless of the way current was flowing. The induced channel of N-type material within the P-channel is called a "depletion zone." This is because the majority carriers, the holes, have been depleted. The current through the P-channel would be cut off when the depletion zone \_\_\_\_\_\_ (first formed/filled the built-in P-channel/reached the bottom of the substrate).

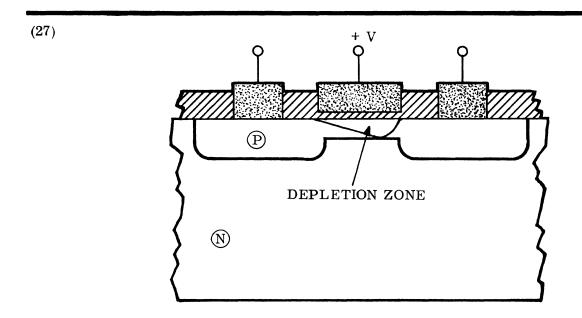

### (27) filled the built-in P-channel

The term actually used is "pinched off," rather than "cut off." The reason for this can be seen in the illustration. As you can see, the depletion zone does not expand evenly and literally pinches off the P-channel at some point. (This is at least partly the result of the source and drain voltages.)

You would expect the gate voltage at which this condition is reached to be called the \_\_\_\_\_\_ voltage.

(26)

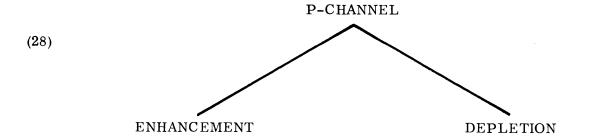

| <b>(2</b> 8) | pinch-off                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | Current flow in both of the MOSFET's we have discussed so far has been through a channel of P-type material. Logically enough, they are called P-channel MOSFET's They can be further identified as either enhancement type or depletion type, depending on whether the channel is induced or built in. The MOSFET with the built-in channel would be a/an type, while the MOSFET in which a channel must be induced would be a/an type. |

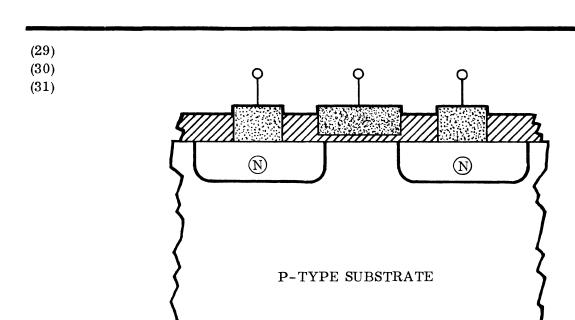

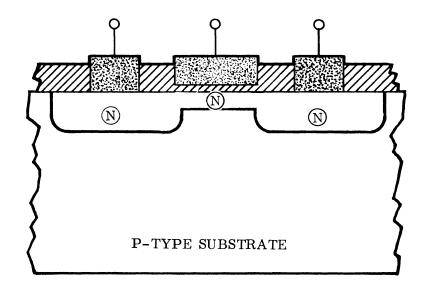

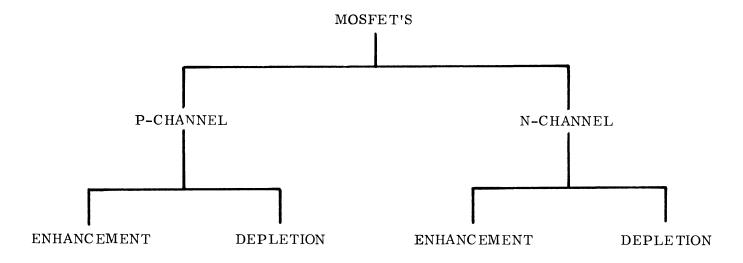

| (29)         | depletion (built-in channel)                                                                                                                                                                                                                                                                                                                                                                                                             |

|              | enhancement (induced channel)                                                                                                                                                                                                                                                                                                                                                                                                            |

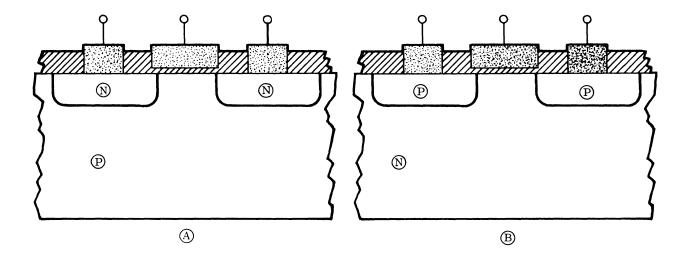

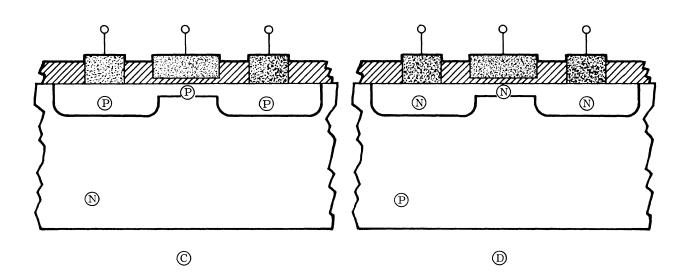

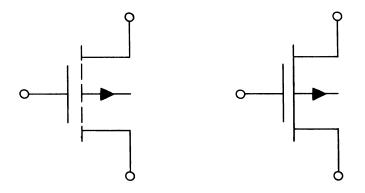

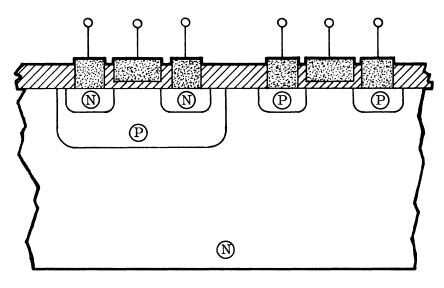

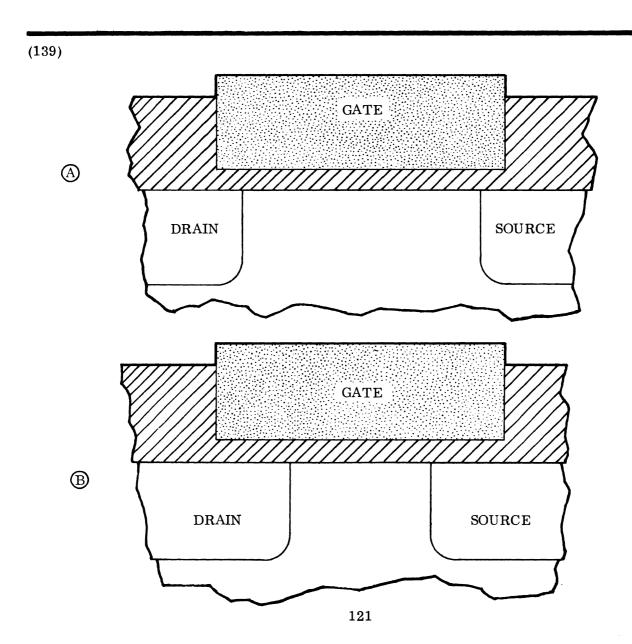

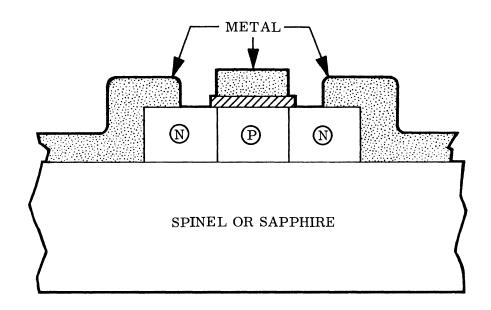

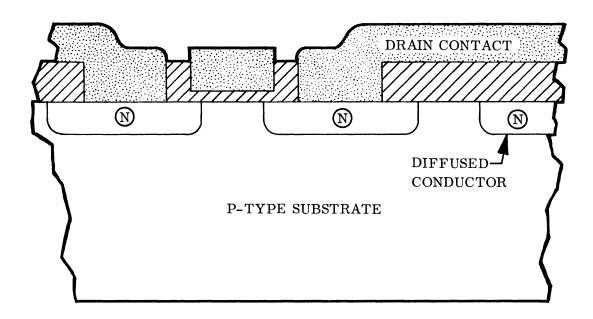

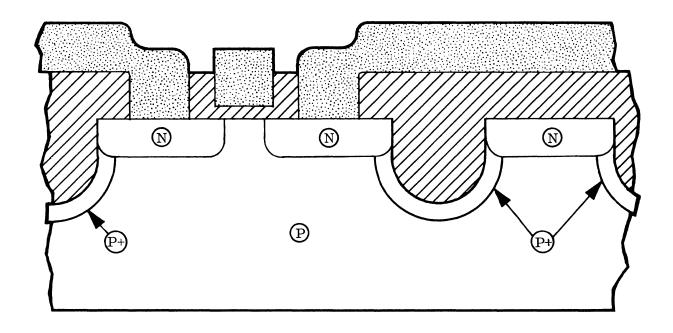

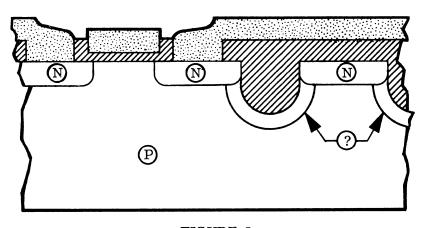

|              | The other two major types of MOSFET's are shown here. In these, the substrate is made of P-type material, and the source and drain are made of N-type. You would expect these MOSFET's to both be calledchannel.                                                                                                                                                                                                                         |

| (30)         | N                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|              | As the P-channel MOSFET's were further identified as enhancement and depletion types, so are the N-channel MOSFET's. The upper MOSFET in the illustration is a/an type, while the lower is a/an type.                                                                                                                                                                                                                                    |

| (0.1)        |                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| (31)         | enpaacement (ribben).                                                                                                                                                                                                                                                                                                                                                                                                                    |

|              | depletion (lower)                                                                                                                                                                                                                                                                                                                                                                                                                        |

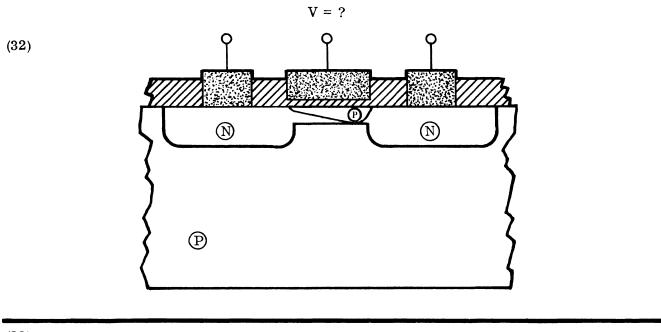

|              | We'll start with the enhancement type. To produce the N-channel necessary to turn                                                                                                                                                                                                                                                                                                                                                        |

### (32) positive

A positive gate voltage would attract the necessary electrons to the gate area of the substrate. Similarly, an N-channel depletion MOSFET would require a \_\_\_\_\_\_ (positive/negative) voltage to produce a depletion zone and pinch off the built-in N-channel.

### (33) negative

As far as basic operation goes, then, the N-channel and P-channel MOSFET's are quite similar, differing primarily in the polarity of the required gate voltages. One other difference worth noting at this time has to do with the type of current carriers utilized. As has been indicated, the P-channel current carriers are holes, and the N-channel current carriers are electrons. Electrons are inherently better current carriers than holes, simply because electrons are able to move around more easily. Electrons are said to have a higher mobility, roughly twice that of holes. For the same size channel and the same drain-to-source voltage, an N-channel MOSFET would have \_\_\_\_\_\_ (twice/half/the same) source-to-drain current as would a P-channel MOSFET.

### (34) twice

The easier the current carriers are to move, the greater the current for a given voltage. This, of course, would be an advantage for N-channel MOSFET's. It is, however, only one difference among many. Each of the four types has certain advantages and disadvantages, either in terms of performance and size or in terms of cost and manufacturing difficulty, and no single type presently has a clearcut advantage over all other types. A number of the advantages and disadvantages of each type will be discussed later.

(33)

(34)

## (35) REVIEW

|    | Α,         | Normally(on/off)                                           |

|----|------------|------------------------------------------------------------|

|    |            | Turned(on/off) by a(positive/negative) gate voltage        |

|    | В.         |                                                            |

|    |            | Normally(on/off)                                           |

|    |            | Turned(on/off) by a(positive/negative) gate voltage        |

|    | <b>C</b> . |                                                            |

|    |            | Normally(on/off)                                           |

|    |            | Turned(on/off) by a(positive/negative) gate voltage        |

|    | D.,        |                                                            |

|    |            | Normally(on/off)                                           |

|    |            | Turned(on/off) by a (positive/negative) gate voltage       |

| 2. | The        | e gate current in these MOSFET's will be essentially zero  |

|    | Α.         | only when they are turned off                              |

|    | В.         | only when they are turned on                               |

|    | C.         | at all times                                               |

|    | D.         | only when the gate is negative                             |

|    | E.         | only when the gate is positive                             |

| 3. | Whe        | en any of these MOSFET's is turned on, current can flow    |

|    | A.         | only when the source is positive with respect to the drain |

|    | В.         | only when the drain is positive with respect to the source |

|    | C.         | regardless of the source and drain polarities              |

(35)

| (35) | ( c        | (continued)                                                                                   |  |  |  |  |  |  |

|------|------------|-----------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|      | 4.         | Another acronym which can be used interchangeably with MOSFET is  It stands for               |  |  |  |  |  |  |

|      | 5.         | For two channels of the same size, a/an(N-channel/P-channel would present a lower resistance. |  |  |  |  |  |  |

|      | 6.         | Current through a turned-on MOSFET would have to pass through $\_$ $(0/1/2)$ P-N junctions.   |  |  |  |  |  |  |

| (36) | RE         | VIEW ANSWERS                                                                                  |  |  |  |  |  |  |

|      | 1.         | A. N-channel enhancement off on, positive                                                     |  |  |  |  |  |  |

|      |            | B. P-channel enhancement off on, negative                                                     |  |  |  |  |  |  |

|      |            | C. P-channel depletion on off, positive                                                       |  |  |  |  |  |  |

|      |            | D. N-channel depletion on off, negative                                                       |  |  |  |  |  |  |

|      | 2.         | C. at all times                                                                               |  |  |  |  |  |  |

|      | 3.         | C. regardless of the source and drain polarities                                              |  |  |  |  |  |  |

|      | <u>4</u> , | IGFET Insulated Gata FET                                                                      |  |  |  |  |  |  |

|      | 5,         | N-channel                                                                                     |  |  |  |  |  |  |

|      | 6.         | 0                                                                                             |  |  |  |  |  |  |

(35) (36)

# MOSFET SYMBOLS

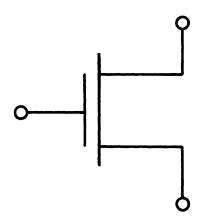

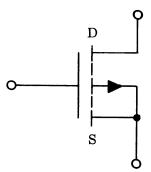

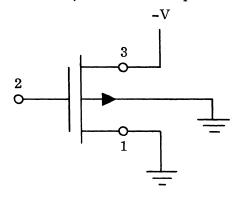

| (37)        | There has as yet been no industry-wide standardization of MOSFET symbols.  A "general" symbol, often used to represent any of the four types we have discussed, is shown here. Notice that, unlike any of the symbols for bipolar transistors, one of the three elements is not physically connected to the others. This "unconnected" element would be the (source/gate/drain).                                                                                                                                                                                                                                                                                                         |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <del></del> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| (38)        | gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             | Remember that this separation, or insulation, between the gate and the rest of the MOSFET is one of the major differences between bipolar transistors and MOSFET's. The other two connections, of course, are the source and drain, and the line connecting them (parallel to the gate) represents the channel. When the symbol stands alone as it does here, there is no way of telling which is the drain and which is the source. The only way to distinguish the source from the drain is by looking at the circuit the MOSFET is in. First, though, we need a definition of the terms source and drain. From the names themselves, you would expect current to flow from the to the |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

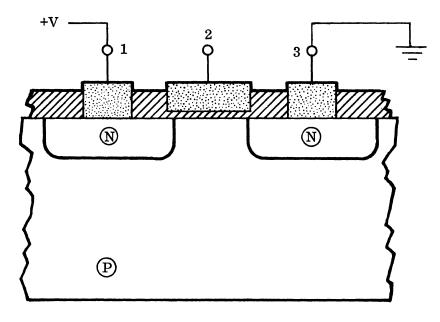

| (39)        | source to the drain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|             | Next, we have to define current flow as it applies to MOSFET's. If only electrons were involved, it would be simple. Current would flow from negative to positive. In MOSFET's, however, holes are current carriers as often as electrons, and they flow from positive to negative. Thus, both the polarity of the applied voltage and the type of current carriers must be taken into account. In a P-channel MOSFET, current flow would be from (positive/negative to In an N-channel MOSFET, current flow would be from to                                                                                                                                                            |

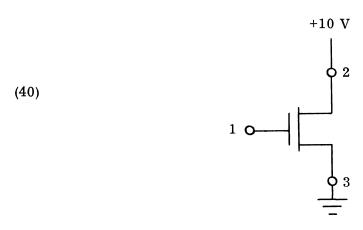

| (40) | positive to negative (P-channel)                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|      | negative to positive (N-channel)                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

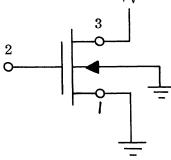

| ·    | In a MOSFET, then, the source is defined as the terminal at which the current carriers, whether they are holes or electrons, originate. If the MOSFET shown here was N-channel, terminal (2/3) would be the source. If it was a P-channel, terminal would be the source.                                                                                                                              |  |  |  |  |  |  |

|      |                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| (41) | 3 (N-channel)                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|      | 2 (P-channel)                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|      | Thus, you can't tell the source from the drain unless you know what type of MOSFET it is. In addition, unless you know whether it is a depletion or enhancement type, you won't be able to tell what any given gate voltage will do to it. It would therefore seem to be a good idea to use a symbol which allows you to distinguish among the four types of MOSFET's.                                |  |  |  |  |  |  |

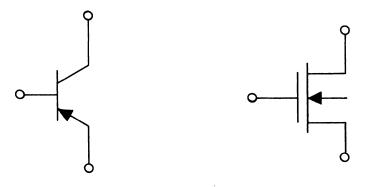

|      | First, let's borrow something from bipolar symbology: an arrowhead. It is used here as a symbol for the substrate. In bipolar symbology, the arrowhead always pointed toward the N-type material. Thus the bipolar transistor shown here would be a PNP. Applying the same logic to the MOSFET symbol, the arrowhead pointing toward the channel means that this is a/an(P-channel/N-channel) MOSFET. |  |  |  |  |  |  |

| (42) | Nobaunel                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|      | Similarly, the symbol shown here, with the arrowhead pointing away from the channel and into the substrate would represent a/anMOSFET.                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

(42)

| (43) | P-channel |

|------|-----------|

|------|-----------|

The direction of the arrowhead, then, distinguishes between N-channel and P-channel, but what about enhancement and depletion types? The answer is shown here. The symbol on the right is the same P-channel MOSFET we saw in the last frame. The symbol on the left is another P-channel symbol, but notice that the channel in this one is represented by a broken line, indicating the channel is \_\_\_\_\_\_\_ (conducting/not conducting).

# (44) not conducting

If we assume that the symbols represent a "neutral state," i.e., no gate voltage applied, then the symbol with the broken line for the channel would represent a/an\_\_\_\_\_\_ (depletion/enhancement) MOSFET.

#### (45) ephancement

With no gate voltage, an enhancement MOSFET is shut off; the channel is open. Therefore it is represented by a broken line. On the other hand, a depletion type MOSFET with no gate voltage is turned on. The built-in channel provides a current path, and it is therefore represented by a solid line.

Going back to an earlier discussion for a moment, recall that the voltage which turns on a MOSFET is the voltage between the gate and the substrate. This means that we must have a way of indicating what the substrate is connected to. The simplest way of doing this is to use the arrowhead, as shown here. This drawing indicates that the substrate is tied to the \_\_\_\_\_\_.

(45)

| ( | 46 | ) | sc | u | r | c | $\epsilon$ |

|---|----|---|----|---|---|---|------------|

|   |    |   |    |   |   |   |            |

For the present we will show all substrates connected in this way. In reality, the substrates are, more often than not, grounded, but the explanations of MOSFET operation that we will be going through shortly are more easily understood if we assume the substrate is connected to the source. The reason for this will, hopefully, become clear by the time the explanations are completed.

### **REVIEW**

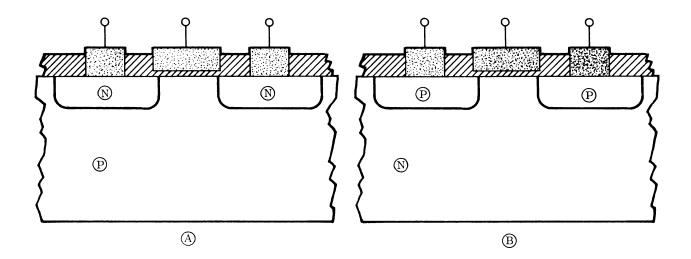

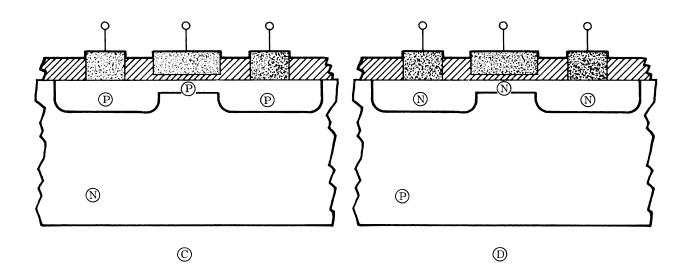

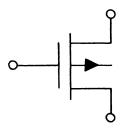

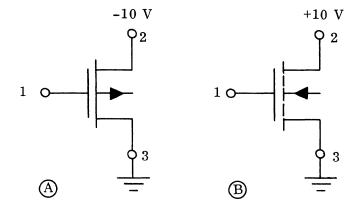

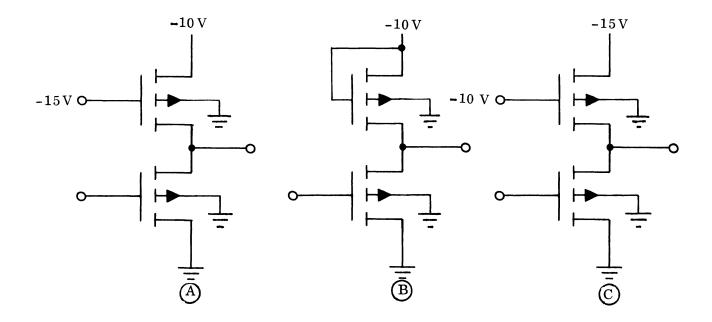

|      | 1. | Identify each of the four MOSFET's in the illustration (P-channel, N-channel, enhancement, depletion). In each case, indicate which terminal is the source when the MOSFET is connected as shown. |

|------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |    | ASource terminal                                                                                                                                                                                  |

|      |    | В                                                                                                                                                                                                 |

|      |    | Source terminal                                                                                                                                                                                   |

|      |    | Source terminal                                                                                                                                                                                   |

|      |    | D                                                                                                                                                                                                 |

|      |    | Source terminal                                                                                                                                                                                   |

|      | 2. | The substrate in MOSFET A is (P-type/N-type) material.                                                                                                                                            |

|      | 3. | With no gate voltage, MOSFET A would be turned(on/off). It would be turned(on/off) by a (positive/negative) gate voltage.                                                                         |

| (47) | RE | /IEW ANSWERS                                                                                                                                                                                      |

|      | 1. | A. P-channel depletion 3                                                                                                                                                                          |

|      |    | B. N-channel enbancement<br>3                                                                                                                                                                     |

|      |    | C. N-channel depletion                                                                                                                                                                            |

|      |    | D. P-channel enhancement 2                                                                                                                                                                        |

|      | 2. | N-type                                                                                                                                                                                            |

3. on (no gate voltage), off by positive gate voltage

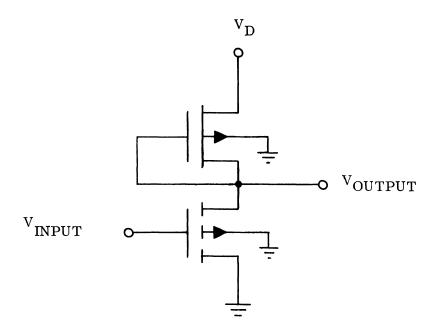

# MOSFET CIRCUITS

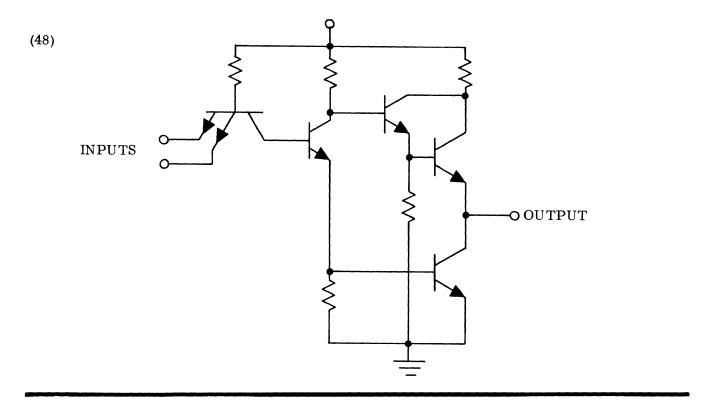

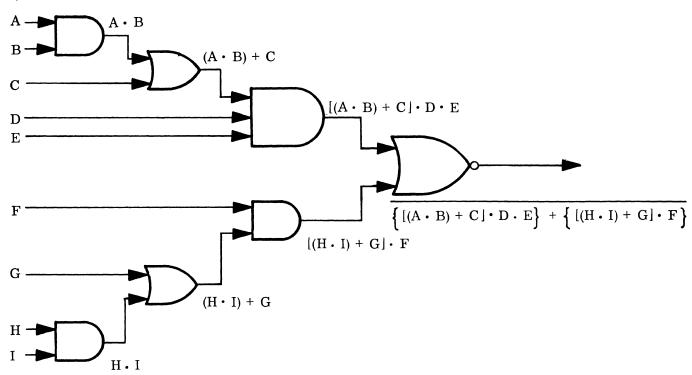

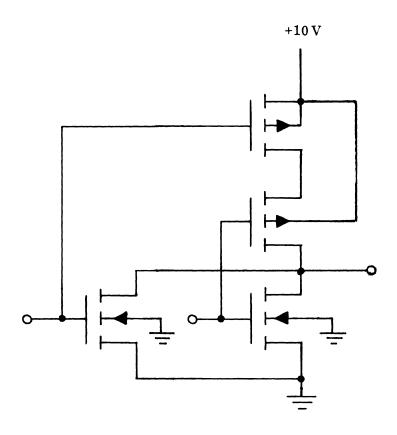

| (48) | In bipolar logic circuits, the main emphasis was on the different types of logic that were used, such as DTL, CML, TTL, etc. The circuits, such as the one for a TTL NAND gate shown here, were often fairly complex, even though each performed only a single logic function. This TTL gate, for instance, contains five resistors and five transistors to perform a simple NAND function. In MOSFET logic circuits, as we will see shortly, things can be much simpler. |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

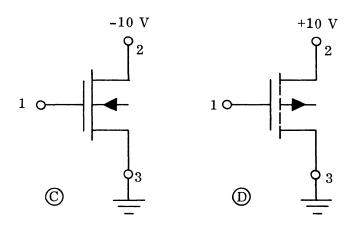

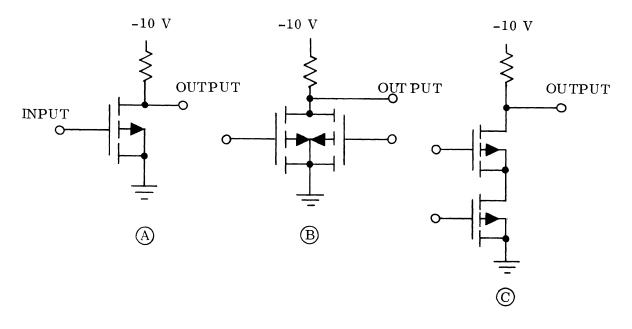

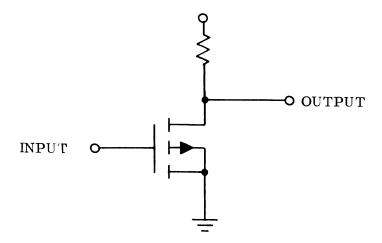

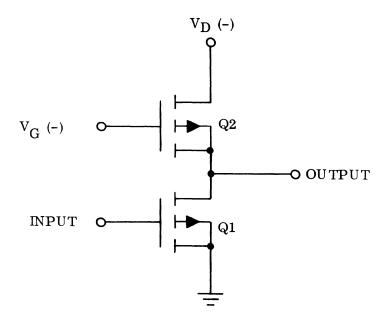

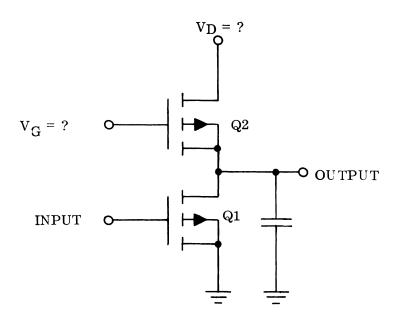

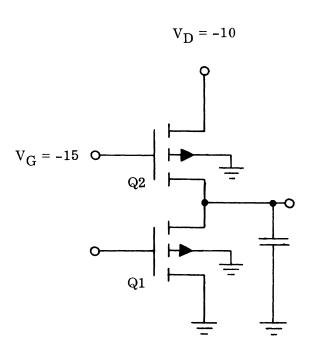

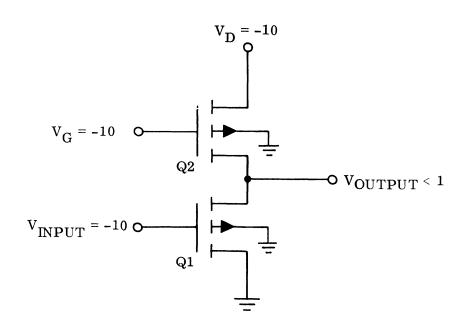

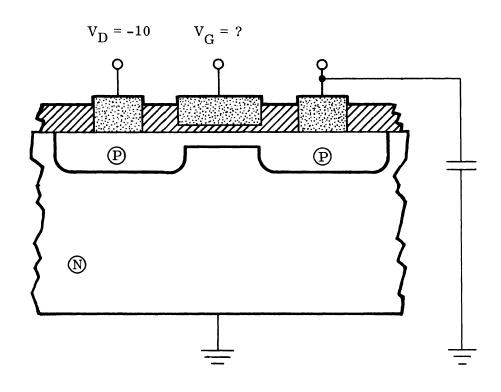

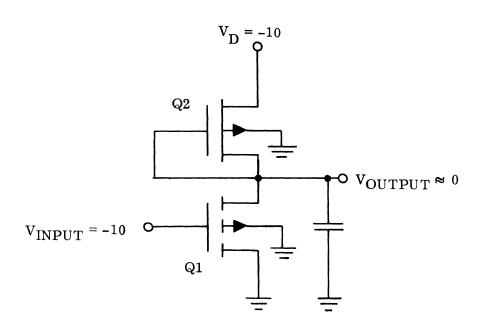

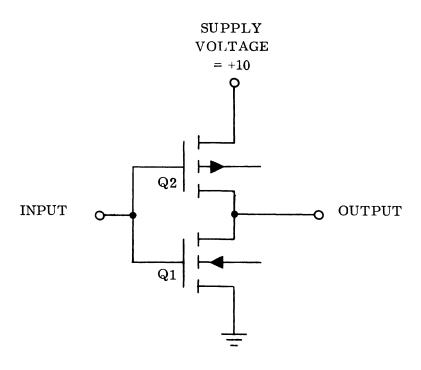

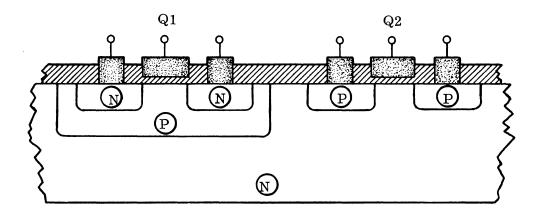

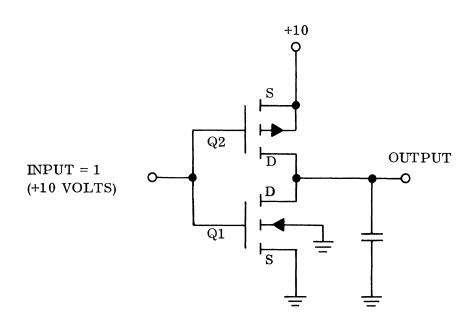

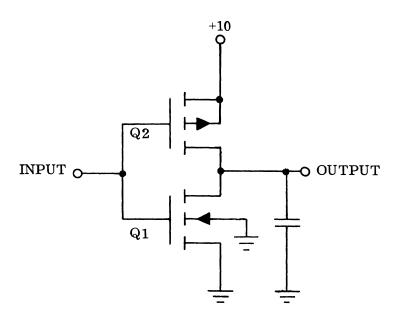

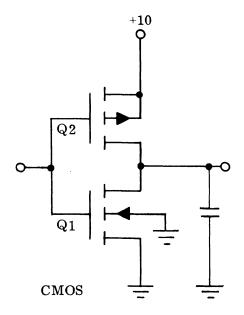

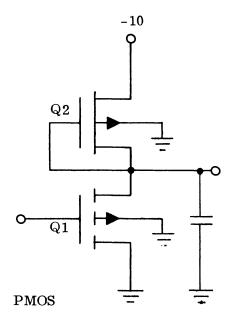

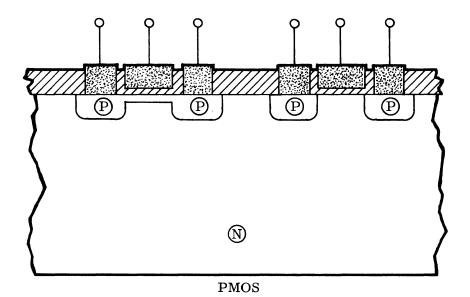

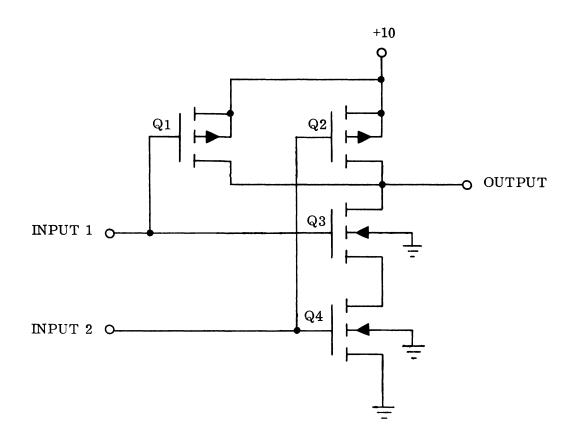

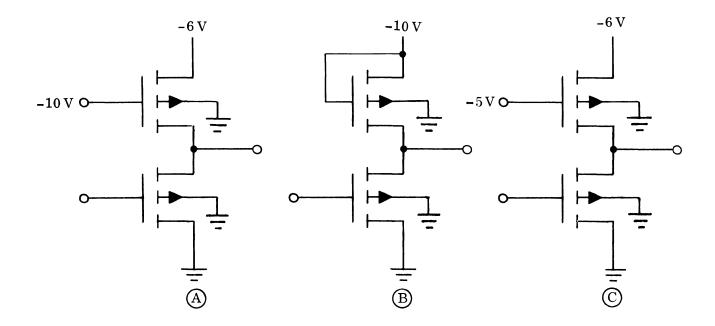

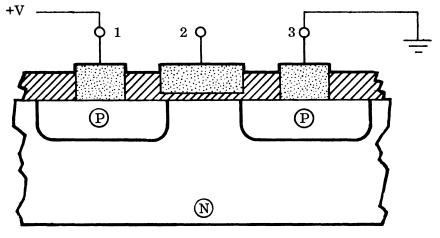

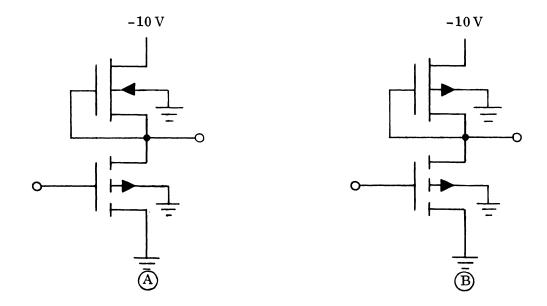

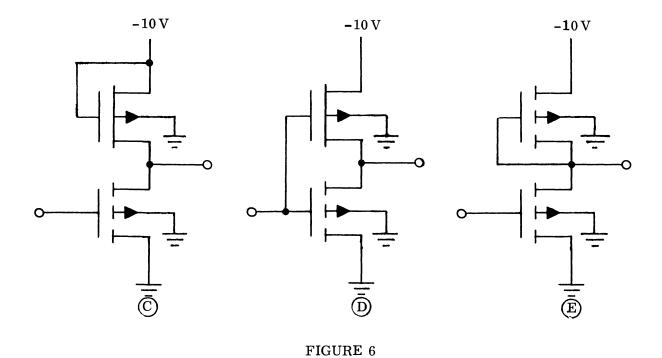

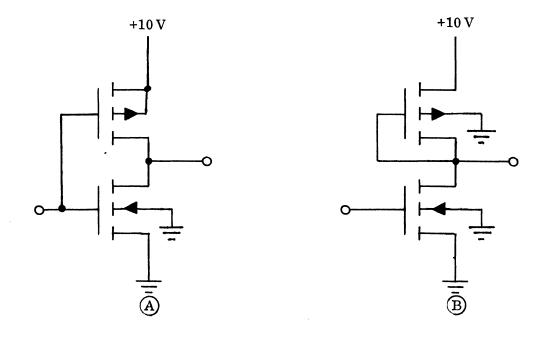

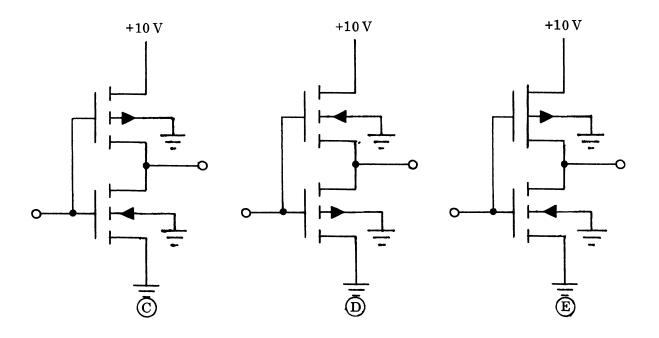

| (49) | Since the P-channel enhancement MOSFET was the first type to be widely used, that is what we will start with. Other types will be introduced as the discussion progresses.  The three basic MOSFET logic circuits are shown here. Assuming negative logic is used, -10 volts represents a logic 1, and 0 volts, or ground, represents a logic 0. This means that if a logic 1 is applied to the input of circuit A, the output would be a logic                           |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| (50) | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | The negative voltage on the gate would turn the MOSFET on, shorting the output to ground. This circuit, then, is simply an inverter. Circuit B is a/an gate.  (OR/NOR/AND/NAND) gate, and circuit C is a/an gate.                                                                                                                                                                                                                                                         |

| (51) | NOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | NAND                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

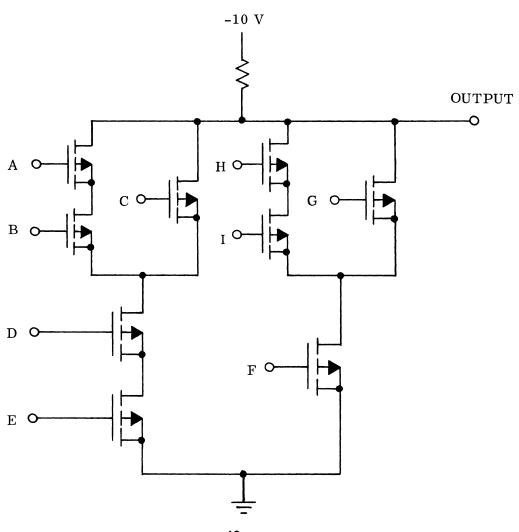

|      | There are variations on these, some of which we will discuss later, but basically these three circuits are the only ones used extensively. They are often used in complex and extensive combinations, but the overall circuits can usually be broken down into a number of these basic circuits.                                                                                                                                                                          |

(49) (50) (51)

| (52) | Another important difference between bipolar and MOSFET logic stems from a           |

|------|--------------------------------------------------------------------------------------|

|      | MOSFET characteristic that was discussed briefly several frames ago. At that         |

|      | time it was pointed out that, given the proper gate voltage, a MOSFET could be       |

|      | made into a short circuit. Its source-to-drain circuit would not have the built-in   |

|      | P-N junction voltage drop that all bipolar emitter-to-collector circuits have. It is |

|      | this characteristic, plus the fact that the gate is insulated from the source and    |

|      | drain, that allows the NAND gate to operate well. It would be difficult to get two   |

|      | bipolar transistors to operate efficiently as switches when connected in series that |

|      | way. Several MOSFET's, however, can be connected in series without any great         |

|      | problems. As a result, fairly complex logic functions can be performed by what is    |

|      | essentially a single gate. For instance, the logic diagram shown here can be         |

|      | implemented using the single gate illustrated below it. Each individual input con-   |

|      | trols a single MOSFET, and each MOSFET can be turned on or off independently.        |

|      |                                                                                      |

| This type of circuit is possible because a MOSFET gate             | $\underline{\hspace{1cm}}$ (does/does not) |

|--------------------------------------------------------------------|--------------------------------------------|

| have to draw current in order to turn the source-to-drain path on, | and because                                |

| there (is/is not) a fixed minimum voltage drop across              | a turned-on                                |

| MOSFET.                                                            |                                            |

| (53) does | not |

|-----------|-----|

|-----------|-----|

is not

| Now   | let's  | go ba | ck to the | simple   | est of our | basic   | circuits, | the inver  | ter, a | nd look  | at it |

|-------|--------|-------|-----------|----------|------------|---------|-----------|------------|--------|----------|-------|

| in a  | little | more  | detail.   | First,   | notice th  | at thei | re is one | MOSFET:    | and on | e resist | or    |

| in th | e circ | cuit. | The circ  | cuit cou | ld probab  | ly be   | made phy  | sically sm | aller  | if the   |       |

|       |        |       |           | wa       | s replace  | ed by a | another _ |            |        |          |       |

## (54) resistor

#### MOSFET or transistor

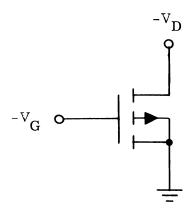

As was pointed out in the text on bipolar integrated circuits, resistors are rarely used when one or more transistors can be used to perform the same function. The same principle holds true for MOSFET's, only more so. For one thing, the size advantage of MOSFET's over resistors is even greater than that of bipolar transistors over resistors. For another, a resistor can usually be replaced by a single MOSFET rather than by a complete circuit. To see why, let's look at the operating characteristics of a MOSFET. We will use a P-channel enhancement MOSFET such as the one shown here. Notice that a negative drain voltage ( $V_D$ ) and a negative gate voltage ( $V_C$ ) have been applied. The resistance offered by this MOSFET would depend primarily on the (drain/gate) voltage.

(53)

(54)

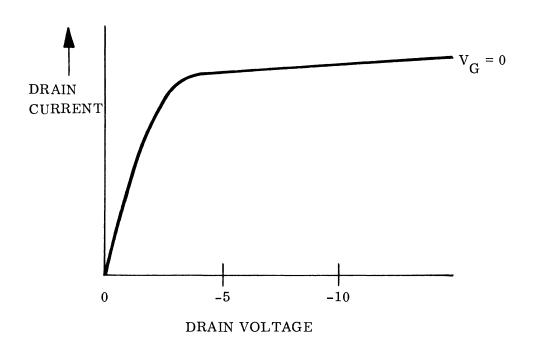

#### (55) gate

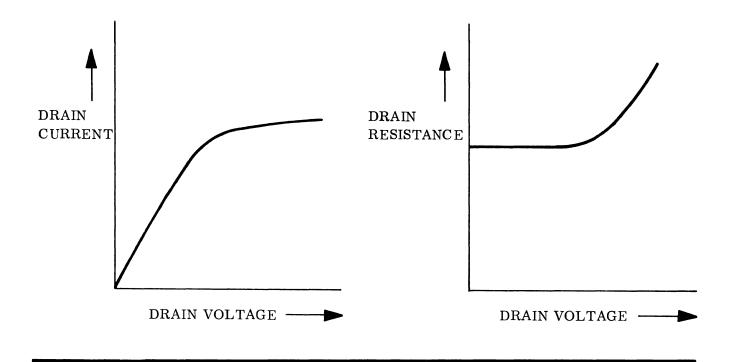

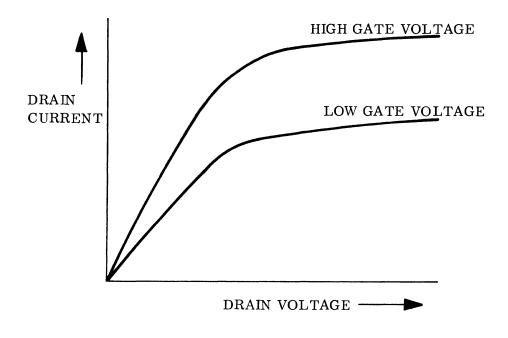

This is much like the grid voltage in a triode vacuum tube. With the gate-to-substrate voltage held constant at  $-V_G$ , the source-to-drain path acts like a fixed resistor — up to a point. Assuming the gate voltage is greater than the MOSFET's threshold voltage, the curves shown here indicate roughly what will happen. As long as the drain-to-source voltage is relatively low, the current increases more or less linearly as the drain-to-source voltage increases. Throughout this range, then, the resistance of the source-to-drain path remains fairly constant. Once this range is exceeded, however, the channel induced by gate voltage becomes saturated and the current levels off. In effect, the resistance begins to rise. If the gate voltage were higher, you would expect the induced channel to saturate at \_\_\_\_\_\_\_ (a higher/a lower/the same) level.

# (56) a higher level

The higher gate voltage would cause a deeper conduction channel to be formed, allowing more current to flow. Not only would the saturation current be greater, but the current for any given drain voltage would also be greater, as shown in these curves. The effective resistance of the MOSFET with the higher gate voltage would be \_\_\_\_\_\_ (higher/lower/unchanged).

(55)

(56)

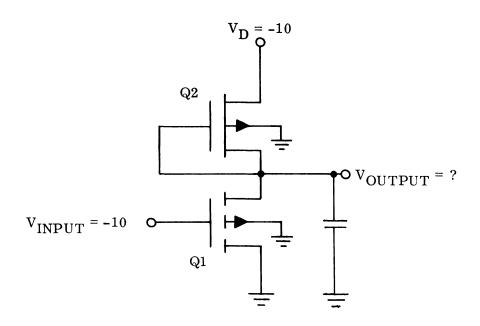

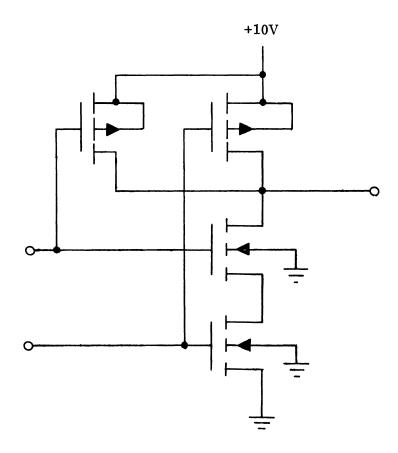

### (57) lower

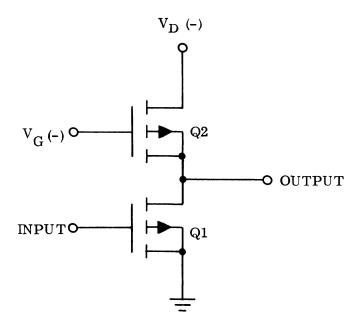

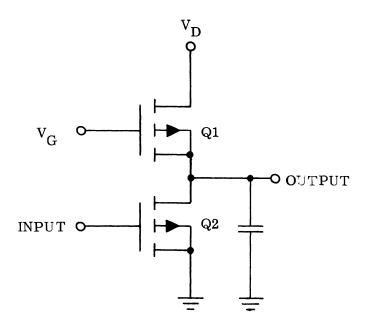

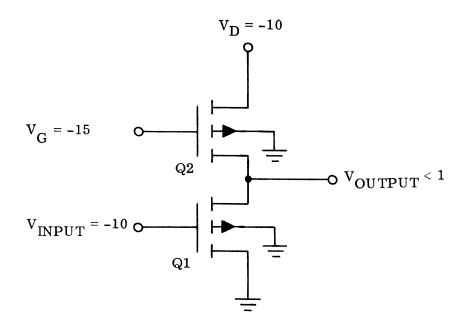

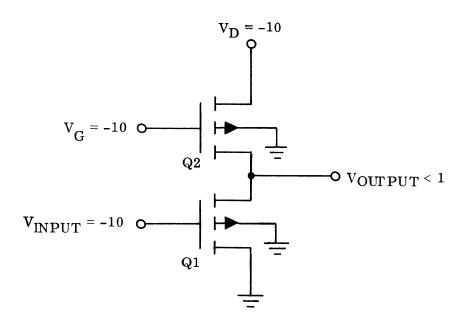

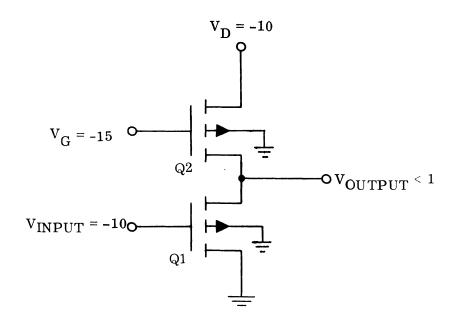

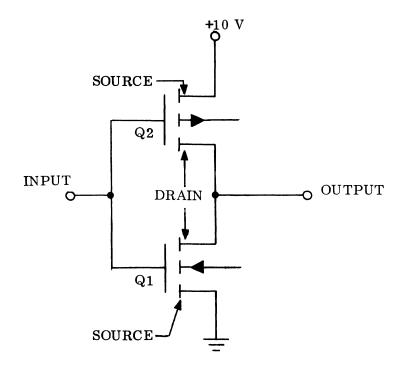

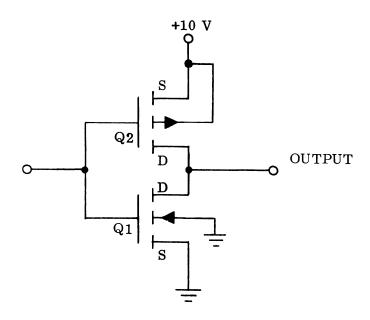

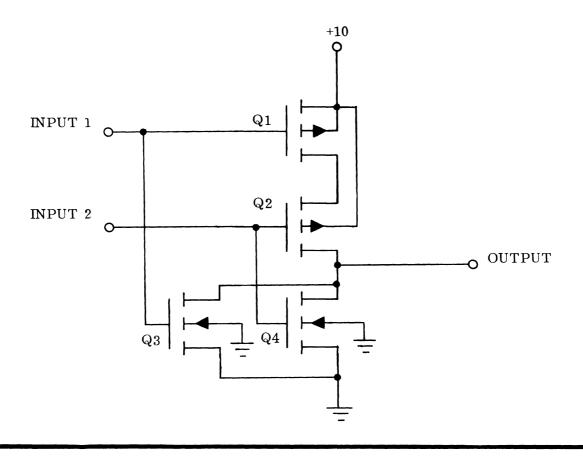

Now let's see what some of the differences are between a resistor and a MOSFET being used as a resistor. To start with, we will look at one of the basic MOSFET logic circuits, the inverter. In the inverter shown here, \_\_\_\_\_\_ (Q1/Q2) is being used as a resistor.

### (58) 😡 2

Precisely what happens in this circuit depends on a number of things, including the various voltage levels. To simplify the situation, we will assume that the drain supply voltage  $(V_D)$ , the gate supply voltage  $(V_G)$ , and the logic 1 voltage are all equal. If a logic 1 is applied to the Q1 gate, Q1 will be turned on heavily, and its drain voltage will begin to drop. Since the source and substrate of Q2 are both tied to the drain of Q1, the voltage there will also begin to drop. This means that the gate-to-substrate voltage of Q2 will \_\_\_\_\_\_ (increase/decrease).

| <b>(</b> 59) | increase                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|              | Thus, turning Q1 on tends to turn Q2 on as well. As long as there is a voltage drop across Q1, however, the Q2 gate-to-substrate voltage will always be somewhat(less/greater) than the Q1 gate-to-substrate voltage.                                                                                                                                  |  |  |  |  |  |  |

|              |                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|              |                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| (60)         | less                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|              | Thus, the resistance offered by Q2 would be somewhat greater than that offered by Q1. At some point, a balance would be reached and the output voltage would level off. At that balance point, the output would be closer to ( $V_D/g$ round) than to                                                                                                  |  |  |  |  |  |  |

| (61)         | closer to ground than to ${ m V}_{ m D}$                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|              | Ideally, though, the output should be very close to ground. If Q1 and Q2 are physically identical, this will never happen. The balance will be reached at some point well above ground. To avoid this problem, Q1 and Q2 should be constructed so that Q1 has a much (higher/lower) saturation current and therefore a much (higher/lower) resistance. |  |  |  |  |  |  |

- (59) (60) (61)

| (62) | higher (saturation current)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

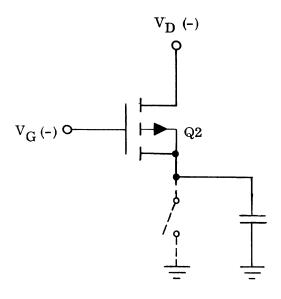

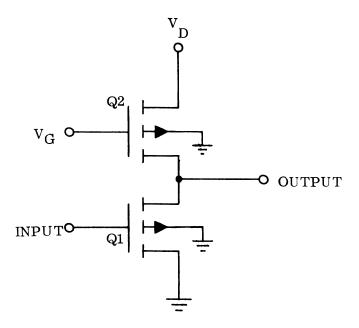

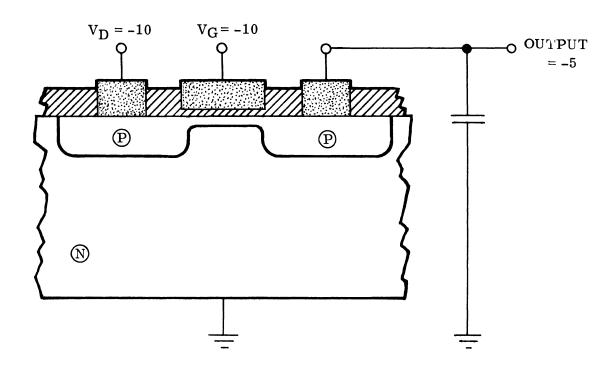

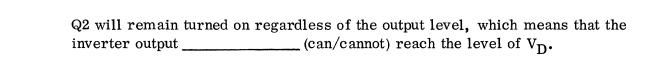

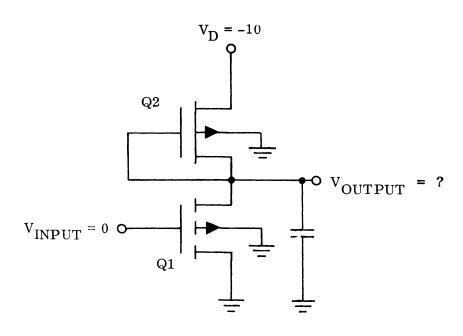

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | lower (resistance)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | In practice, with the same gate voltage, Q2 would have roughly 20 times the resistance of Q1. This means that Q1 can be considered to act like a switch, being opened and closed by the voltage applied to its gate. As we have just seen, a logic 1 will produce an output voltage that is very nearly zero. But now let's see what happens when a logic 0 is applied to the Q1 gate. Q1 would be turned off, and the circuit could be represented as shown here. The capacitor connected to the output represents the gate capacitance of the MOSFET circuit being driven by the inverter. As this capacitor charges up, the gate-to-substrate voltage of Q2 will (increase/decrease). |

| (63) | decresse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | This is just the reverse of what happened when Q1 was turned on. The voltage on the substrate and source of Q2 is increasing while the gate voltage remains constant. If the Q2 gate-to-substrate voltage drops below the threshold voltage, Q2 will be (turned on more heavily/turned off).                                                                                                                                                                                                                                                                                                                                                                                             |

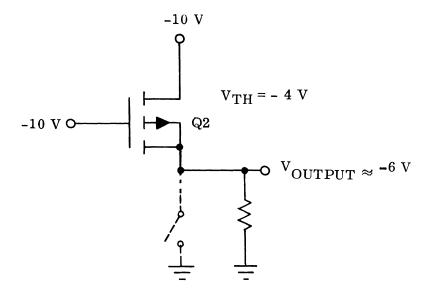

| (64) | turned off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | With Q2 turned off, the capacitor will stop charging and the voltage will level off. If the Q2 threshold voltage (VTH) is -4 volts and $V_G$ and $V_D$ are both -10 volts, the voltage across the capacitor will level off atvolts.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

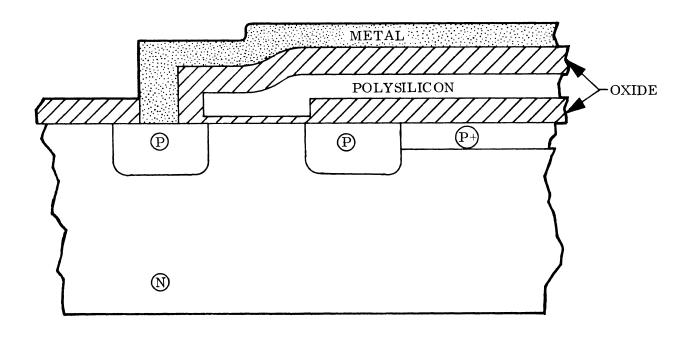

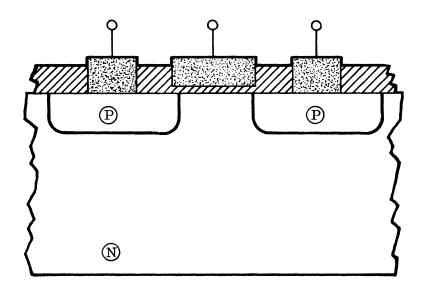

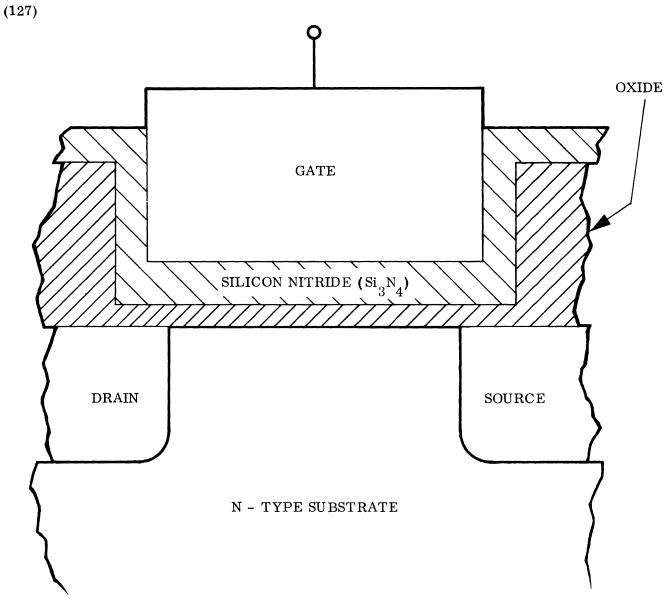

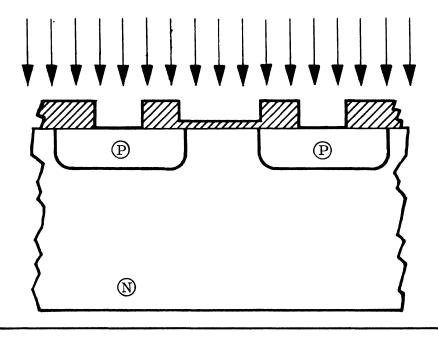

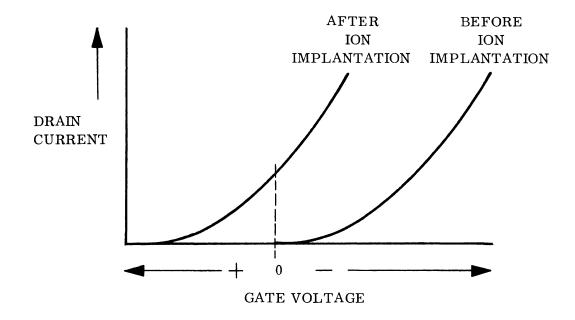

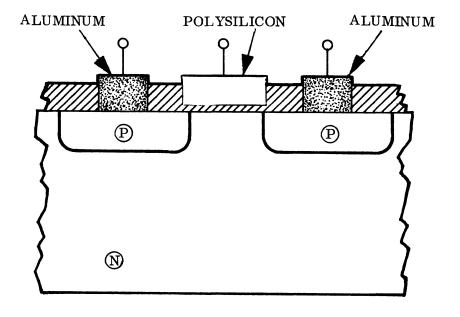

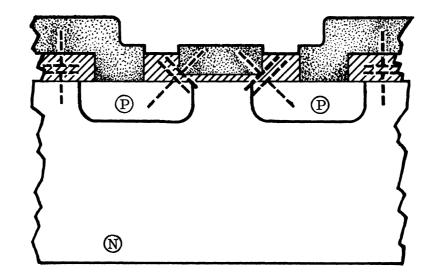

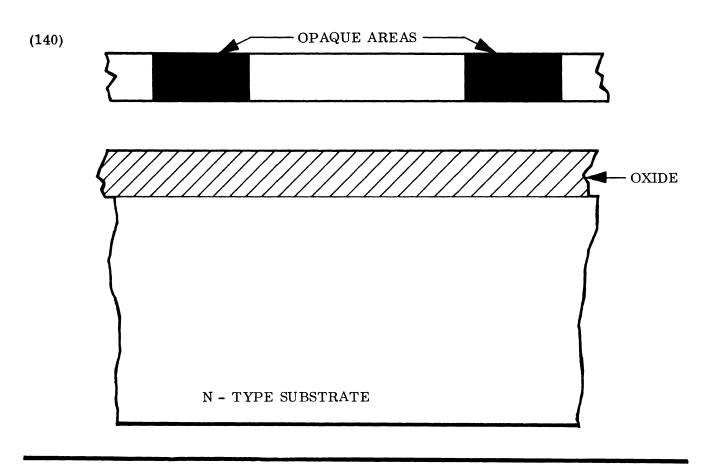

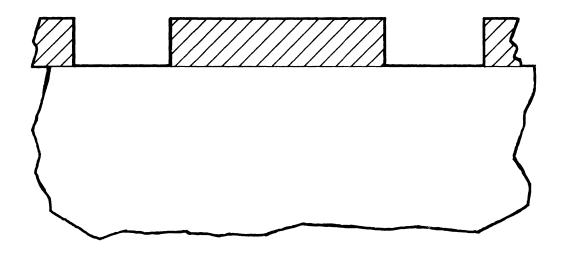

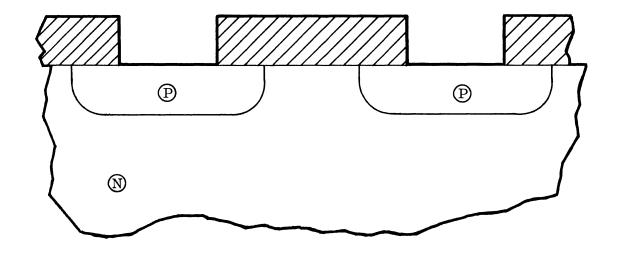

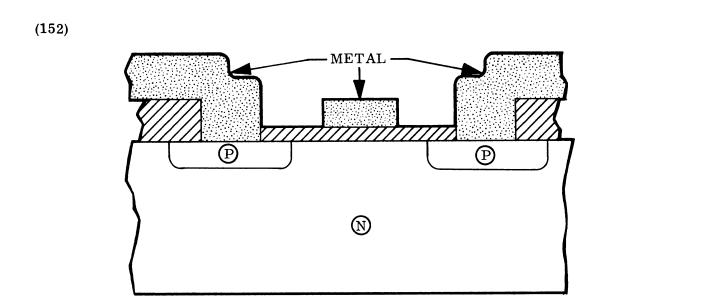

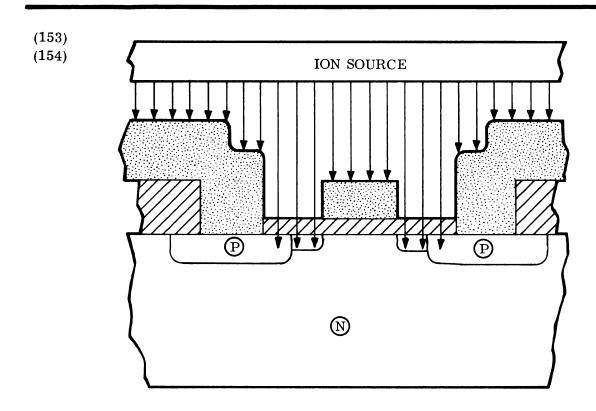

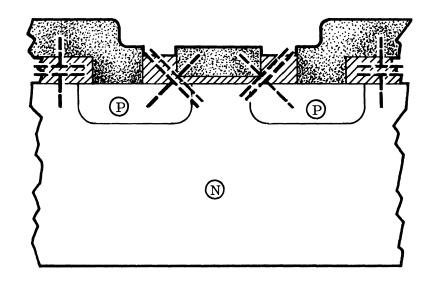

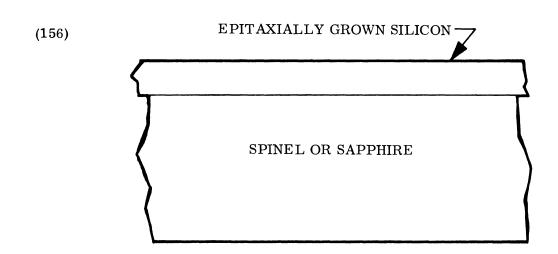

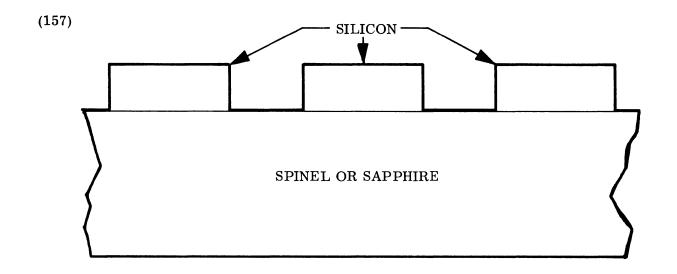

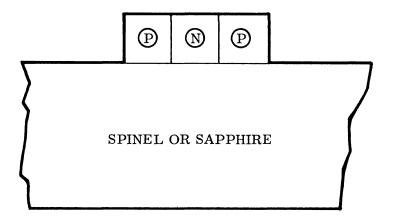

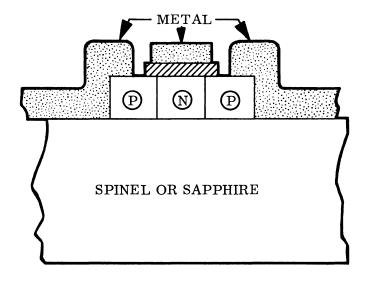

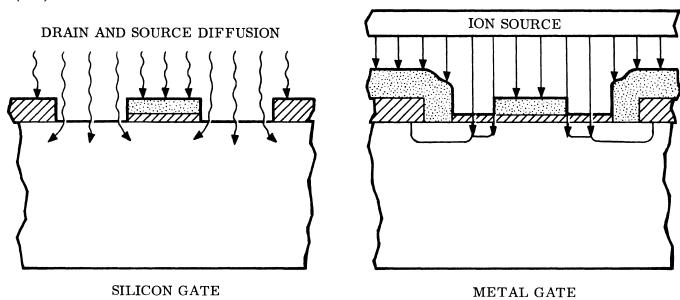

| (65) | -6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |