1969 EEE Linear Integrated-**Proceedings** Circuit-Clinic

1969 EEE Linear Integrated-Circuit-Clinic Proceedings

# 1969 EEE Linear IntegratedCircuit-Clinic Proceedings

© Copyright Mactier Publishing Corp.

Prepared for the 1969 EEE

Semiconductor-Device Clinic

on

Linear Integrated Circuits

New York, N. Y.

March 24, 1969

# Staff

Proceedings Editor: Jerry Eimbinder

Typing: Carolyn Neilsen

Layout: Carol Verlaan

Clinic Arrangements: Rhoda Glenner

# Publisher

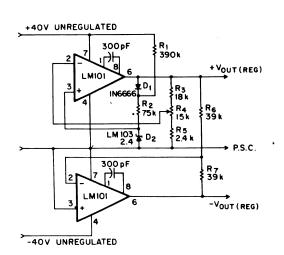

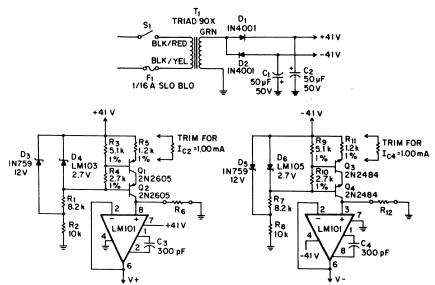

Published by EEE Magazine 820 Second Avenue New York, N. Y. 10017

Jerry Eimbinder, Editor

Michael Elphick. Senior Associate Editor

Gadi Kaplan, Associate Editor

Allan P. Yee, Associate Editor

James A. Lippke, Contributing Editor

Thea Welch, Assistant Editor

Carolyn Neilsen, Editorial Assistant

Carol Verlaan, Editorial Assistant

Rita Backer, Editorial Secretary

George Rostky, Editorial Director

# Previous Proceedings Available

"FET Applications Handbook." Includes Proceedings of the 1966 Clinic on Field-Effect Transistors. Tab Books, 288 pp., \$12.95.\*

"Linear Integrated Circuits: Theory and Application." Based on the 1967 EEE Clinic on Linear Integrated Circuits.

John Wiley & Sons, 318 pp., \$9.95.

"Designing With Linear Integrated Circuits,"

Based on the 1968 EEE Clinic

on Linear Integrated circuits.

John Wiley & Sons, 302 pp., \$10.95.

| 1.          | Factors to Consider in Selecting A Linear Integrated Circuit                                     |          |

|-------------|--------------------------------------------------------------------------------------------------|----------|

|             | by Jerry Eimbinder<br>EEE Magazine. New York, N. Y.                                              | 9-14     |

| 2.          | Interpreting Operational-Amplifier Specifications                                                |          |

|             | by Ray Stata Analog Devices, Cambridge, Mass.                                                    | 15-22    |

| 3.          | Applications for Operational Amplifiers                                                          |          |

|             | by W. S. Routh<br>National Semiconductor. Santa Clara, Calif.                                    | 23-39    |

| 4.          | Applications for Fully Compensated Operational Amplifiers                                        |          |

|             | by Michael English Fairchild Semiconductor. Mountain View, Calif.                                | 40-46    |

| 5.          | Understanding Fully Compensated IC Operational Amplifiers                                        |          |

|             | by Harry Gill<br>Raytheon Semiconductor                                                          |          |

|             | Mountain View, Calif.                                                                            | 47-55    |

| 6.          | High Frequency Characteristics of Wideband Inverter Op-Amps<br>by Heinrich Krabbe                |          |

|             | Zeltex. Concord, Calif.                                                                          | 56-65    |

| 7.          | Selected Linear Circuit Applications                                                             |          |

|             | by Ralph Seymour and Len Brown                                                                   |          |

|             | Signetics Corp.<br>Sunnyvale, Calif.                                                             | 66-70    |

| 8           | The Versatile Wideband IC Amplifier                                                              |          |

| •           | by Brent Welling                                                                                 |          |

|             | Motorola. Phoenix, Ariz.                                                                         | 71–86    |

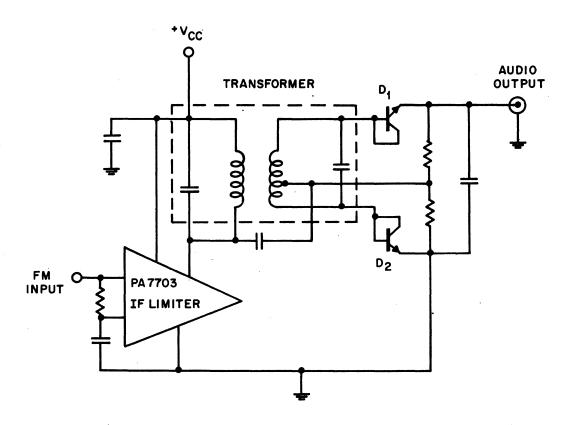

| 9.          | Applying Integrated Circuits to FM Detector Applications by W. F. Allen, Jr. and L. H. Hoke, Jr. |          |

|             | Philco-Ford Corp. Blue Bell, Pa.                                                                 | 87-107   |

|             |                                                                                                  |          |

| 10.         | The Dual Operational Amplifier by David Long and David Campbell                                  |          |

|             | Fairchild Semiconductor                                                                          | 100 100  |

|             | Mountain View, Calif.                                                                            | 108-123  |

| 11.         | FM Detector-Limiter Integrated Circuits                                                          |          |

|             | by Peter H. Mack and Norman S. Palazzini<br>Sprague Electric Co.                                 |          |

|             | North Adams, Mass.                                                                               | 124-137  |

| 12.         | The Linear Four-Quadrant Multiplier                                                              |          |

|             | by Ed Renschler<br>Motorola Semiconductor                                                        |          |

|             | Phoenix, Ariz.                                                                                   | 138 -155 |

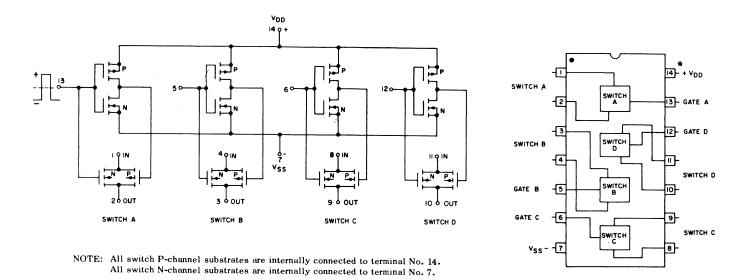

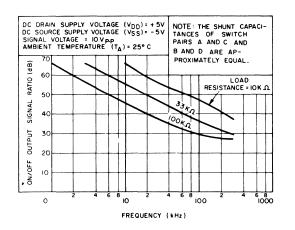

| 13.         | Multiplexing with Complementary MOS Integrated Circuits                                          |          |

|             | by R. L. Sanquini and A. A. Ahmed                                                                |          |

|             | Radio Corp. of America<br>Somerville, N. J.                                                      | 156-162  |

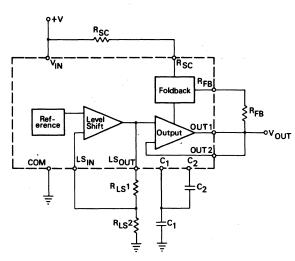

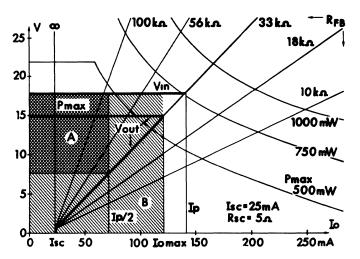

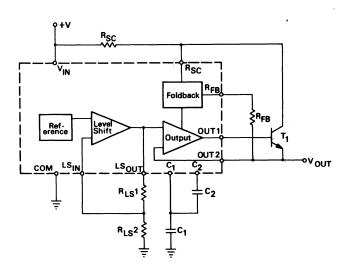

| 1/1         | Voltage Regulator ICs with Foldback Current Limiting                                             |          |

| <b>-</b> 7. | by Douglas R. Sullivan and Hans W. Mamie                                                         |          |

|             | Transitron Electronic Corp. Wakefield, Mass.                                                     | 163-176  |

|             | noncercta, ridge.                                                                                | 103-170  |

| 15. | Integrated Voltage Regulators by Edward L. Renschler Motorola Semiconductor Products Phoenix, Ariz.  | 177–189   |

|-----|------------------------------------------------------------------------------------------------------|-----------|

|     |                                                                                                      |           |

| 16. | Positive Voltage Regulators by Robert J. Widlar National Semiconductor. Santa Clara, Calif.          | 190-202   |

| 17. | Negative Voltage Regulators<br>by Robert J. Widlar<br>National Semiconductor.<br>Santa Clara, Calif. | 203 - 217 |

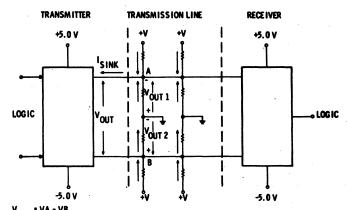

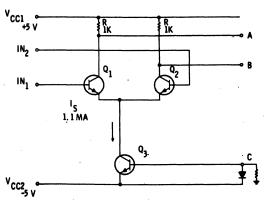

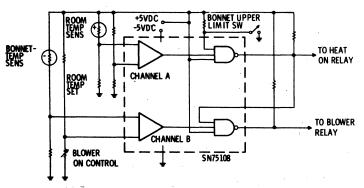

| 18. | A High-Speed Data-Transmission System by Jerry Avery                                                 |           |

|     | Texas Instruments Dallas, Texas                                                                      | 218-227   |

|  |  | * |   |  |

|--|--|---|---|--|

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   | , |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

|  |  |   |   |  |

1

Factors to Consider

In Selecting A Linear

Integrated Circuit

by Jerry Eimbinder

EEE Magazine

In choosing a linear integrated circuit (particularly if it's an operational-amplifier IC), finding one that meets your requirements can be only half the job (1). Often there will be many ICs available that you can use. In this case, narrowing down to the one IC best suited for your application can be a truly difficult task.

First of all, the specifications on the data sheet aren't the whole story. Factors often not readily obtainable from the data sheet which can affect your choice include reliability, acceptability and compatibility of the package and the supply requirements, capability to withstand the application's environmental stresses and degree to which the device is accident-proof.

Then, of course, there's price. Prices are rarely, if ever, present on data sheets. But if the device you're looking at is subjected to a lot of tests that you don't need, it's a good bet you'll do better price-wise if you look somewhere else. Ditto if the package is metal and you can get by with plastic, or if the allowable operating temperature range exceeds your requirements.

The rules presented in the following paragraphs can help in selecting that one IC which is right for your application. They are, of course, general rules but applied in conjunction with a little common sense, they can be very helpful.

# 1.1 RULE 1: DON'T OVERSPECIFY

Decide which specs are critical and which are not. If you're building a voltage regulator with op-amp ICs and there is a large differential voltage during turn-on, you'll have to consider this a very critical parameter. If you're working with a very-high-gain, high-source impedance amplifier, you'll want to consider offset current more critical than offset voltage. If you specify both very tightly, you'll be sending up the cost of the amplifier needlessly.

There are many parameters that can be given for an op-amp IC (for example: input offset voltage and current, input bias current, input impedance, input common-mode range, slew rate, common-mode and power-supply rejection, bandwidth, output drive capability, open-loop gain, drift, noise, dissipation and so on). Certainly, which of these parameters are optimized will vary from IC type to IC type. How the parameters are optimized will depend on the markets at which the IC's manufacturer is aiming (2).

There is usually enough compromise involved in designing a linear IC so that it can fit a variety of applications. Siegel warns, however, that some of the miscellaneous applications suggested on a manufacturer's data sheet, while technically feasible, may be f rancially ludicrous (3). Gifford indicates which parameters are the key ones for various applications and suggests typical values in "Designing With Linear Integrated Circuits" (4).

### 1.2 RULE 2: CHECK THE SAFETY FEATURES

Besides selecting which specs you want and which you don't need, you may have to do some choosing regarding safety factors, too. So as part of your elimination procedure, you'll want to check the safety features. One question that should be asked is: can this IC get me into trouble? Problems that will arise under fault conditions should be considered. Will the output become seriously distorted? Will the whole system go up in smoke? Some ICs are more goof-proof than others and this is a factor not to be taken lightly.

For example, op-amp ICs can be bought with or without output short-circuit protection and input overvoltage protection. Since the emitter-to-base junctions of input transistors are sensitive to damage by large applied voltages, some form of input protection may be desirable. Ungrounded soldering irons, excessive input signals and static discharges are all apt to challenge the input of the IC.

# 1.3 RULE 3: WEIGH COST AGAINST PERFORMANCE

Of course, when you add any features, even ones concerned with safety, you've got to consider how they'll affect the overall cost—not just the immediate cost of the chip. Reducing the cost of building or maintaining the system, however, should justify adding to the chip cost.

Cost, understandably, keeps getting into the picture during the evaluation of an IC. Throughout the elimination process you must continually weigh cost against performance. From an economical standpoint, a designer today, should be looking at operational—amplifier ICs that require little or no compensation. The prices of resistors and capacitors are bottoming out; to save money in the future, you'll have to eliminate these components by incorporating them on the chip. But, on the other hand, if you're planning to use a fully compensated op-amp IC right now, better make sure you're not limiting yourself frequencywise.

Judging cost is complicated by the fact that determining the overall system cost involves guesswork. Nevertheless, it shouldn't be too difficult to decide, for example, if using a dual op-amp IC instead of two separate units or a high-gain amplifier instead of two low-gain amplifiers are economical moves. Although if, as in the case of the dual op-amp IC, the close temperature tracking of two circuits on one chip is especially desirable, the weighing becomes more complex.

Reducing "can count" (the number of packages used) is generally a good idea from a reliability standpoint but the designer should make sure that this doesn't adversely affect flexibility and performance.

# 1.4 RULE 4: CONSIDER FREQUENCY COMPENSATION

The frequency compensation that will be required differs widely among commercially available op-amp ICs. At one time, in fact, opponents of op-amp ICs cited the need for frequency-compensation networks as the prime reason for not using op-amp ICs.

The discrete components required for frequency compensation do add to the space requirements and assembly cost. Various arrangements used for commercially available op-amp ICs can require from zero to seven components(5) depending on the IC and application. Certainly, it is of key importance for the designer to consider frequency compensation. He should look at the op-amp IC and attempt to determine how prone it is

to oscillation if the supply is not exactly bypassed properly. The IC should be evaluated to see how prone it is to oscillation with varying capacitive loads and how probable it is that stray capacitance around the circuit will send it into oscillation.

Too much bandwidth in an amplifier can work against you. Extra capacitors may be needed across the feedback resistors to prevent oscillation.

# 1.5 RULE 5: COMPARE THE SPECIFICATIONS OF VARIOUS VENDORS

It's essential to understand the nature of the input signal and to spell out what the worst-case conditions will be in terms of voltage swing, noise, supply variations, etc. If this is done, you're in a good position to compare the specs of various vendors. In working with the data sheets of IC manufacturers, care should be exercised in checking to see if the test conditions of both manufacturers are the same for a particular characteristic.

For example, if you're comparing offset voltages, see if the source impedances specified by both manufacturers are the same. If you're looking at slew rate, make sure both manufacturers are doing their measuring at the same gain.

Op-amp specifications are evolved from nonlinear characteristics and as Stata warns (6), it's not surprising if the circuit doesn't "play the first time around."

It's common practice for a semiconductor-device manufacturer to spec his product under favorable operating conditions. Therefore the user must also attempt to relate the data sheet information to his own application.

Widlar points out (7) that it's difficult to get the whole story on any IC from a data sheet. He notes that the IC must also be designed so that it's operation isn't erratic under certain conditions.

He also points out that it's not difficult to design an IC that will satisfy the requirements of a specific application and that can be manufactured with reasonable yield. The real trick, he says, is to design an IC which can be used in hundreds of different applications without complaints from the users.

Examples of IC assets that may not show up on the data sheet, cited by Widlar, include continuous short-circuit protection, capability not to latch up or perform erratically when the inputs are driven outside their operating range, ease in determining correct compensation and reliability.

# 1.6 RULE 6: CHECK THE PRODUCT'S HISTORY

A lot of people think that IC manufacturers leave reliability information off their data sheets for these two reasons: IC reliability doesn't vary much from manufacturer to manufacturer and customers won't put much stock in the IC makers' figures. Actually the real reason for the absence of this information on the spec sheet is rather simple: the IC makers just don't have it when they publish the spec sheet.

Spec sheets are prepared just before ICs are announced and there's insufficient time to run lifetest programs. Even after new ICs come out, the IC manufacturers are constantly modifying their masks and processing procedures to improve yields or performance.

For example the manufacturer may reduce the size of an individual die to increase the number of die per wafer. Conversely, he may find that there is some interaction

between active elements because the transistor locations on the chip are too close to each other. Possibly he may want to reduce the length of extra long metal interconnection patterns.

So how do you judge the reliability of competitive ICs? Some engineers believe that there is a relationship between noise and reliability. This has been disputed, however, and discounted by several top semiconductor-device authorities, including National Semiconductor's Bob Widlar.

There's a good possibility that you won't have enough time to run your own lifetests and even if you do, the manufacturer may change the device six times during the course of your test program. Instead you'll be better off if you check the product's history. Find out if there are other applications similar to yours in which the same device has been used with success. For that matter, see how successful the manufacturer has been with products of this type. Is this his first attempt at it or does he have a long history of developing such devices?

Some designers refuse to use any ICs that aren't available from several sources. While this policy will usually keep you out of trouble if your main source of supply dries up, it has one drawback. It could be a year or two before you can take advantage of advancements in the state-of-the-art (8).

If a new IC looks good and you decide to use it, you're gambling that either it's so good other companies will add it to their lines or the original supplier can be depended upon to continue supplying it. There's an American washing-machine manufacturer who guarantees to make every part used in his products available for 35 years. You won't get any such warrantees in the semiconductor business.

Some IC manufacturers will hold units in bonded stock for possible future purchase; however a higher price per unit is usually paid as a premium. Depending on the terms of the contract, the customer may wind up paying for the whole inventory even if he doesn't use it (8).

# 1.7 RULE 7: SEE IF THE IC LENDS ITSELF TO MASS PRODUCTION

But if that new IC really looks good and it can put you one step ahead of your competition, then see if the circuit lends itself to mass production. This isn't easy to determine, but if the circuit is very complex, the chip is large and the vendor has had delivery problems in the past, you may have reason to be nervous.

You might keep in mind that the more complex the chip, the greater the cost, and, quite possibly, the lower the yield. This doesn't mean that you should shy away from complex chips; but if the chip's crammed with a wide variety of tight-tolerance, difficult-to-make components, look out.

# 1.8 RULE 8: CONSIDER THE PROBABILITY OF WIDE ACCEPTANCE OF THE IC

At this point of your evaluation, you could also consider the probability of wide acceptance of the IC. If the volume won't be significant, obviously the cost isn't going to drop measurably in the future. However, if the IC's versatile, the chances of its being second-sourced are much improved.

The prices of newly announced ICs are based primarily on developmental costs, anticipated yield and projected sales volume. But even the best guesswork by an IC

manufacturer can't accurately determine what his competition is going to do. If a number of his competitors jump in, the price will go down.

It's wise to keep in mind that if a new IC appears to have characteristics that could limit its appeal (such as inconvenient supply requirements or elaborate compensation-network requirements), it could be a poor choice even though it meets the application's needs.

# 1.9 RULE 9: CHECK FOR APPLICABLE LITERATURE

One factor, sometimes overlooked, is evaluating your own capability to work with a product. First of all, is your knowledge of the product adequate for you to design it into your application? In this area, it's important to check for availability of application literature published by the IC manufacturer. This will not only help you engineer the product into your circuit, it'll also give you a good indication of how much the IC maker knows about the use of his own product.

The publishing of applications literature on linear ICs, fortunately, has been extensive. However, because of the rapid progress of the IC industry, some of the material that has been published suggests design solutions that are no longer economically feasible. Care should be exercised in using older linear IC literature as design criteria.

# 1.10 RULE 10: EVALUATE THE TESTING ASPECTS

Finally, if you can understand and design with the IC, can the rest of your company handle it? Will special assembly rigs have to be built to accommodate the package? Undoubtedly you'll have to evaluate the testing aspects. With IC manufacturers going to more and more complex chips, incoming inspection and testing are becoming more involved.

Questions which arise concerning inspection are: is the plant facilitated to thoroughly check out the devices? Can existing test equipment be modified and used or must new equipment be obtained? The IC user will have to test the devices when they arrive and he'll also have to determine how they'll be tested in completed systems by field maintenance personnel (9).

Every application has its own unique problems, but, regardless of the specific problems being encountered, the ten general rules mentioned in this chapter shouldn't be overlooked. By applying them, deciding which op-amp IC to use should become an easier chore.\_\_\_\_\_

# RÉFERENCES

- (1) Eimbinder, Jerry, "Selecting the Right Linear IC For Your Application," <u>EEE</u>, November 1968, pp. 48-52.

- (2) Gifford, Jack, "The Performance/Economics/Marketplace Inter-Relationships," Wescon Proceedings, Session 1, 1967, pp. 22-29.

- (3) Siegel, Murray, "Murray Siegel of Fairchild Speaks Out on IC User Beefs," <u>EEE</u>, October 1967, pp. 86-89.

- (4) Eimbinder, Jerry, Editor, "Designing With Linear Integrated Circuits," John Wiley & Sons, Inc., 1969, pp. 1-12.

- (5) Widlar, Robert J., "Monolithic Op Amp With Simplified Frequency Compensation," <u>EEE</u>, July 1967, pp. 58-63.

- (6) Stata, Ray, "Ray Stata of Analog Devices speaks Out On What's Wrong With Op-Amp Specs," EEE, July 1968, pp. 44-50.

- (7) Widlar, Robert J., "Bob Widlar of National Semiconductor Speaks Out on What Makes a Good IC," <u>EEE</u>, August 1968, pp. 80-85.

- (8) Eimbinder, Jerry, "Is a Single Source Safe," EEE, August 1968, pp. 96-97.

- (9) Eimbinder, Jerry, Editor, "Linear Integrated Circuits: Theory and Applications," John Wiley & Sons, Inc., 1968, pp. 93-110.

2

Interpreting Operational-Amplifier Specifications

by Ray Stata

Analog Devices

Operational amplifiers are complicated. They have many specifications, and most are only approximations of what's happening in the black box. Most parameters like voltage drift, current drift and open-loop gain are nonlinear functions of temperature; others, like common-mode rejection and common-mode impedance, are nonlinear functions of input voltage. And almost all parameters depend on supply voltages. Therefore, when you use a single number to specify a parameter, you must qualify the conditions of the measurements. Comprehensive graphs would be necessary to define performance completely.

Confronted with 50 more-or-less mysterious numbers, most engineers tend to select an op amp in terms of familiar values and to forget about the rest. An engineer who wants to replace a sensitive relay with a low-cost amplifier might simply concern himself with the output-current rating and neglect such factors as drift or gain.

# 2.1 THE LACK OF STANDARDS

Then there's the lack of standards for op-amp specs. Though various efforts have been made to unify terms throughout industry, this has not yet been done, so manufaçturers have loopholes for specsmanship.

Along with real, honest-to-goodness specsmanship, we find the inadvertent errors of omission. The holes in the spec, or usually, the lack of additional information, is not revealed until the engineer has assembled umpteen amplifiers into his product and the whole batch is waiting to be shipped.

In one case, a customer purchased a diff amp with a 5  $\mu V/^{O}C$  drift spec. The data sheet said that this number meant maximum voltage drift. What the sheet neglected to say was that the specs held only for steady-state temperature conditions. What happened during thermal transients was another kettle of fish that no numbers covered.

Though we were able to show that this point had been covered in an early application note, we certainly hadn't referred to it in spec sheets for any amplifiers. Actually we didn't know how to specify this mode of operation quantitatively. And some competitors had omitted the point.

Now, let's take a closer look at some of the major specifications and see how these problems come up.

# 2.2 VOLTAGE DRIFT

It can help to go back to first principles. We all know that a transistor's base-emitter voltage varies at roughly 2400 microvolts for every degree C change. This variation develops an output, or offset, exactly as if a true input of equal magnitude were driving the transistor. The use of differential pairs enables the net voltage offset to be drastically reduced because both transistors can be matched so their offsets track within a few microvolts over the temperature range. This is how the amplifier comes to have a drift spec of 5  $\mu V/^{O}C$  instead of 2400  $\mu V/^{O}C$ ; the transistors track within 5  $\mu V$  for every 2400  $\mu V$  of base-emitter drift, that is, for every  $1^{O}C$  rise.

But there's a flaw here. What happens if the base-emitter junctions are not at the same temperature? The spec states a figure for maximum drift, but this is really a tracking spec for base-emitter junctions at the same temperature.

# 2.3 THERMAL CONSIDERATIONS

Obviously, thermal gradients caused by adjacent heat-dissipating components can make nonsense of such specifications by making one junction hotter than the other. It only takes  $0.1^{\circ}$ C differential between the two junctions to develop 2400/10 = 240 microvolts offset. To say the least, this is a substantial offset for an op amp with a 5  $\mu V/{}^{\circ}$ C max drift spec.

In fact, offsets are caused not only by such obvious temperature-gradient sources as adjacent heat-dissipating elements and room-air drafts, but also by changes in the amplifier's own load current. Altering the output current from 2 mA to 20 mA produces an internal temperature transient that develops an offset due to unequal heating of the input transistor pair until temperature equilibrium is re-established. And when the amplifier has settled to its new output level, the input signal will invariably set the load current back to 2 mA, starting the problem all over again.

Offsets due to warmup and changes in operating conditions can be particularly annoying when an instrument or system is being adjusted. It takes only finger heat on one side of a differential amplifier to produce a distinctly-measurable offset error. How does one put performance specifications on such nebulous factors?

One way to sidestep the temperature-gradient error is to avoid the differential amplifier. A chopper-stabilized amplifier corrects automatically for transient offsets of this kind. Its error-sensing circuit is independent of mismatches between the transistors. But sometimes the chopper unit won't win. Apart from being twice as big and costly as a differential amplifier, the chopper-stabilized unit has only a single input terminal. (The other terminal is "used up" in the stabilizing circuit.) A single-ended amplifier can't easily be used in noninverting or differential circuits. So what you gain on the roundabouts breaks the rope on the swings.

Fortunately, some diff amps are inherently less susceptible to temperature gradients. Single-chip dual-transistor front-end circuits cut down thermal inertia and reduce physical spacing between base-emitter junctions of each differential pair. Monolithic IC op amps are generally good on this score because of the small spacing between junctions.

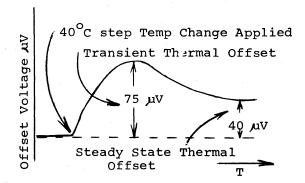

Consequently, temperature transients never pull the two junctions more than a few hundredths of a degree apart. Such amplifiers offer a meaningful steady-state maximum voltage drift of about 1  $\mu/V^O$ C, with a short-lived and worst-case offset of about 75 microvolts for 40 C thermal shock.

While an amplifier with a dual input transistor exhibits a considerable improvement in offset stability, there is no way to discern this fact in comparing the usual published offset-drift specifications. A user can get some idea of comparative thermal-gradient performance by making thermal shock tests, like dropping the amplifier in an oil bath 40°C above ambient. He'll get a response like the one shown in Figure 2.1.

Okay, so we've raised one straw man and then beaten it down. But aren't there other problems that only specsmanship has solved thus far?

# 2.4 ZEROING CAN HIDE SECOND-ORDER DEFECTS

What happens when you adjust an amplifier's offset potentiometer to zero its output at the selected working temperature? Not surprisingly, there's more to the process than meets the eye. And it's not always easy to tie up the sources of error in neat, crisp numbers.

The offset pot is frequently a variable resistor in series with a collector load resistor. The amplifier's output is zeroed by altering collector current to change voltage balance between the two front-end transistors.

So what? Well, it turns out that there's a second-order effect that causes interaction between the actual value of collector current and the rate at which the transistor's base-emitter voltage drifts with temperature. Adjust collector current in one transistor of a matched differential pair and it no longer tracks the other as temperature varies. True, the adjustment modifies the base-emitter drift by only  $0.7~\mu\text{V}/^{\text{O}}\text{C}$  for each 250  $\mu\text{V}$  change in emitter-base voltage or initial offset voltage.

But such differences can swamp the carefully-designed tracking specs of today's state-of-the-art differential amplifiers. For example, some chopperless differential amplifiers have better than 1  $\mu V/C^O$  maximum voltage drift. To zero an initial offset voltage of 1 mV with the internal balance pot in one of these amplifiers would introduce a change in temperature drift of 2.8  $\mu V/C^O$ . And that really screws up the works.

Some manufacturers neglect to point out the second-order effects caused by trimmer adjustments, but as op amp specs improve these effects can no longer be ignored. One must really know the condition of the balance resistor to specify voltage drift uniquely. We get around this by eliminating provisions for an internal offset trim on low-drift amplifiers and by recommending external offset biasing circuits.

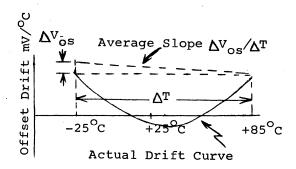

2.5 AVERAGE DRIFT

Average drift is a trap. Remember the man who drowned while wading through a stream with an average depth of only four feet? Neither voltage drift nor current drift are linear functions of ambient temperature. Accordingly, the numbers published for voltage drift and bias-current drift can refer only to average values, or to values at specific operating conditions. For example, an amplifier's total change in voltage offset for a temperature excursion from -25 to +85 $^{\circ}$ C might be 2200 microvolts (referred to the input). The average drift rate over this interval works out to 2200/110 $^{\circ}$  or 20  $\mu$ V/ $^{\circ}$ C. But when you look at the actual drift curve you see that the drift rate at the extremes of temperature can exceed the specified average drift rate by a substantial amount (see Figure 2.2).

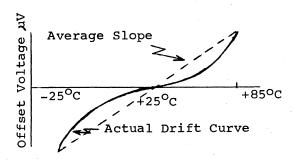

You have a special problem when the drift curve changes slope - a real live possibility. Here the average slope calculated by subtracting end points is entirely meaningless. Nonetheless, some manufacturers have taken advantage of this golden opportunity for specsmanship (see Figure 2.3).

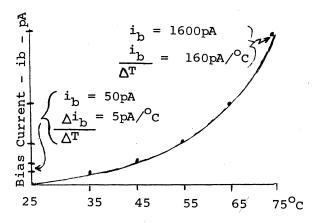

Perhaps trickier to interpret than the voltage-drift figures are the nonlinear errors caused by exponential variation of bias currents in FET and varactor-bridge amplifiers. Usually, the bias current at a given temperature is specified, and the spec reader is reminded that the bias current doubles for approximately 10°C temperature rise as illustrated in Figure 2.4.

If a value of bias-current drift is given, it is usually quoted at room temperature, where the slope of the bias current versus temperature curve (i.e., drift) is shallowest. But at 85°C, the bias current and drift slope will be 64 times worse than at room temperature, making the FET amplifier a worse choice for high-temperature applications than some bipolar transistor types. This is not really a question of specsmanship, but it certainly requires that the user know his way around a spec sheet. 2.6 OUTPUT

An amplifier output rating of  $\frac{1}{2}$ 10 volts,  $\frac{1}{2}$ 20 milliamps implies that the user can drive a 500-ohm load at the full signal swing of 10 volts, 20 milliamps. For discrete-component op amps this is usually what such specs mean. But some integrated circuit manufacturers have a different interpretation. "Sure you can get 10 volts output; certainly it will develop 20 milliamps," they say, but they often forget to add, "so long as you don't ask for them simultaneously." In fact, it is not unusual for an IC amplifier labeled as having a  $\frac{1}{2}$ 10 V,  $\frac{1}{2}$ 5 mA output to have a maximum power rating of only a fraction of the product of the VI figures given.

If an engineer needs an op amp with a relatively high output, he generally wants to know what gain he's getting at that current level. If 20 mA is the amplifier's full-load rating, it would be nice and simple if the manufacturer stated the amplifier's open-loop dc gain at this full load. Not all manufacturers do.

The op-amp user should know his amplifier's roll-off curve in order to build a circuit with adequate gain stability over the working frequency range. The manufacturer may be perfectly justfied in departing from the conventional 6 dB/octave frequency compensation to achieve desirable features like fast settling time, high slew rate, fast overload recovery, or increased gain stability over a wide range of frequencies.

But to obtain these improved features generally requires fast roll-off characteristics and therefore a propensity toward oscillation. Key to preventing instability, of course, is knowing that you have this kind of amplifier. You can then use one or more well known circuit techniques to tame the oscillations.

The great crime occurs when manufacturers use fast roll-off compensation to obtain improved published specs without giving an open-loop response curve or some other indication of what's going on.

# 2.7 COMMON-MODE SPECIFICATIONS

To many users the common-mode rejection ratio of an amplifier is a rather mysterious number that they'd like to forget. Many op-amp manufacturers feel the same way. In fact, if a particular amplifier has a poor common-mode spec, some manufacturers thoughtfully omit it from the data sheet.

Low-cost FET amplifiers are the worst culprits, with typical common-mode rejection ratios around 1000. This is exactly the kind of number that manufacturers would like

to lose. They often do. For a noninverting amplifier circuit, the common-mode error is 1/CMRR, which works out to 0.1% for an amplifier with CMRR of 1000, or 60 dB. Recently, new circuit tricks have enabled manufacturers to overcome this fundamental limitation of low CMRR, but a FET amplifier with 100,000 CMRR tends to cost more than \$100.

Picking a typical CMRR spec from measured op-amp data is great sport. The numbers vary over an enormous range -- from 500:1 to as high as 100,000 for FETs -- all seemingly at random. A reasonable way for a manufacturer to select a typical common-mode figure for his data sheet is to pick a value that is met by 70 or 80% of all units of that particular type. Some manufacturers, with considerable ingenuity, average all the test numbers to find a "typical" value. Tweaking up a few samples to get 100,000 CMRR can do great things for averages of this kind and can, of course, lead to very respectable-looking common-mode rejection figures.

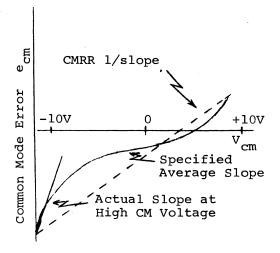

As with drift, an amplifier's common-mode-rejection performance can vary with operating conditions, notably with the value of common-mode input voltage as we can see in Figure 2.5. This leaves room for some really fancy footwork. For example, some well known FET types boast a common-mode voltage range of  $^{+}$ 10 volts. But the common-mode rejection figures are specified for a  $^{+}$ 5-V common-mode range. It's possible for the CMRR to degrade by as much as a factor of ten when the applied common-mode voltage is raised from 5 to 10 volts (see Figure 2.5).

Another difficulty with CMRR is that, since it's a nonlinear function of input common-mode voltage, a single spec number can at best give an average value over the test-voltage range. For small input-signal variation about some large common-mode voltage, the specified "average" CMRR gives little indication of the actual errors you can expect due to the steeper error slope at high voltages.

# 2.8 FULL-POWER RESPONSE

We all know that an amplifier rated at, say, 10-MHz unity-gain bandwidth, doesn't give full output-voltage swing at this frequency. Invariably, distortion caused by internal slew-rate limiting induces the manufacturer to specify the maximum full-power frequency several decades lower.

Generally, an amplifier with 10-MHz unity-gain bandwidth would have a full-power response of about 1 MHz or maybe as low as 100 kHz. At the "small signal" unity-gain bandwidth, the achievable output-voltage swing is usually related to the swing at the full-power bandwidth by the ratio of the full-power response,  $f_p$ , to the unity-gain bandwidth,  $f_t$ . Thus, for example, you get only a 100-mV swing from a 10-V amplifier at unity-gain bandwidth for an amplifier with an  $f_p$  of 100 kHz and an  $f_t$  of 10 MHz.

One large problem with full-power-response specs is that no one really says what he means by the published minimum number. For one thing full-power response has nothing to do with amplitude vs frequency as the term "response" normally implies. Instead it is a measure of output distortion caused by slew-rate limiting.

But there can be monstrous difference depending on whether you set 1% or 10% as the acceptable distortion level. We have evaluated some amplifiers where the output looks a triangle at the specified full-power response. Where do you draw the line on the

acceptable distortion level?

Distortion is only one consideration in setting the criteria for the full-power-response spec. A subtle, but very often more important side effect, is do offset error due to rectification. Feedback signals developed by an unsymmetrical, distorted output, will not counter-balance the input signal at the amplifier's summing junction. So, the error signal is rectified by the amplifier's input stage, generating an undesirable offset voltage.

But how can such application factors be reasonably prevented? Should each data sheet be turned into a thesis, or may the manufacturer assume that his customers are already aware of the difficulties awaiting them? There is no easy answer for either the manufacturer or the customer.

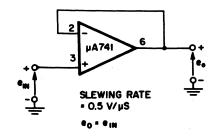

Slewing rate for the most part is just another way of looking at rate limiting of the amplifier's circuitry. The slewing-rate specification applies to transient response while full-power response applies to steady state or continuous response. For a step-function input, slewing rate tells how fast the output voltage can swing from one voltage level to another. Fast amplifiers will slew at up to 300 V/ $\mu$ s, while amplifiers designed primarily for dc applications often slew at 0.1 V/ $\mu$ s or less.

Maximum slew rate, S, is related to full-power response  $f_p$  by  $S=2 \ f_p E_o. \eqno(2.1)$

As the voltage swing is reduced below the peak output,  $\rm E_{\rm O}$ , the operating frequency can be proportionately increased beyond  $\rm f_{\rm p}$  without exceeding the slewing rate. For many amplifiers the slewing rate may differ in the inverting and noninverting configurations — a fact that is not always apparent from published specs. Moreover, there is almost always a difference in slewing rate between fall time and rise time, and between positive and negative output signals. Opportunities for specsmanship arise here since many possible slopes can be measured.

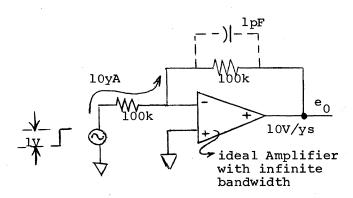

A recurrent complaint by customers is that an amplifier does not meet its slewing-rate spec. Closer inquiry typically shows that the customer is trying to obtain  $100 \text{ V/}\mu\text{s}$  slew rate with a circuit like the one in Figure 2.6.

The problem here is that the inevitable 1 pF of stray capacitance must be charged by the  $10-\mu A$  signal current. This limits theoutput slew rate to  $10~V/\mu s$  regardless of how fast the op amp may be. With an input impedance of  $10~K\Omega$  or less, the customer would obtain the desired  $100~V/\mu s$  slewing rate. In other words, you cannot get fast response from an inverting amplifier when using high input impedance owing to the slugging effect of stray capacitance.

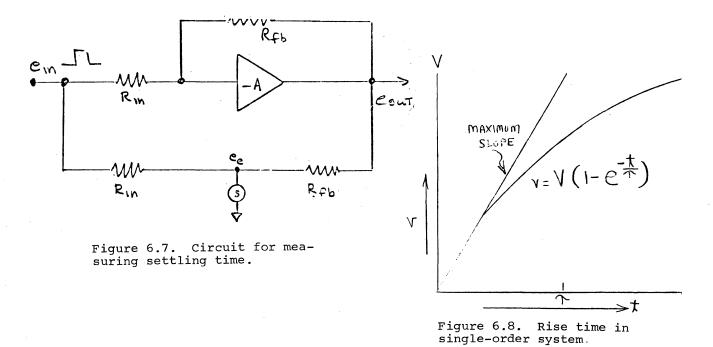

# 2.9 SETTLING TIME

Settling time is a parameter of increasing interest. This spec defines the time required for the output to settle within a given percentage of final value in response to a step-function input. Common accuracies of interest, are settling time to 0.1% and 0.01%. Heretofore, engineers have been forced to use slewing rate and unity-gain bandwidth as rough indicators of relative settling-time performance when comparing or choosing amplifiers, since no other data are given. As it turns out, these two specs have little bearing on settling time, particularly to 0.01%.

Manufacturers now realize this and are beginning to publish settling-time figures.

The hooker here is that settling time is really a closed-loop parameter (while all other op-amp specs are open-loop parameters), and therefore depends on the closed-loop configuration and gain. Fortunately, even when published for only one gain, usually unity gain, it serves as a realistic yardstick for comparing amplifier performance.

The few examples I've shown illustrate the tremendous difficulties in specifying op-amp performance and the many pitfalls confronting the user. In the long run the user and manufacturer are on the same side in seeking unambiguous communications.

There's one further point that can be most important of all. An engineer should breadboard his critical circuits instead of relying totally on paper designs.

### FIGURES

- Figure 2.1. Offset voltage characteristic after subjecting amplifier to oil bath at a temperature 40 C above ambient.

- Figure 2.2. Curves illustrating that average drift values can conceal the presence of larger actual drift values.

- Figure 2.3. Curve illustrating that average slope calculated by subtracting end points can be meaningless.

- Figure 2.4. Bias current as a function of temperature.

- Figure 2.5. CMRR is a nonlinear function; a single spec number at best gives only an average value over the test-voltage range.

- Figure 2.6. In the circuit shown regardless of the op amp's speed, the slew rate is limited by the 1 pF of stray capacitance. As a result, the slew rate is limited to 10  $V/\mu s$ .

Figure 2.1. Offset voltage characteristic after subjecting amplifier to oil bath at a temperature  $40^{\circ}\text{C}$  above ambient.

Figure 2.3. Curve illustrating that average slope calculated by subtracting end points can be meaningless.

Figure 2.5. CMRR is a nonlinear function; a single spec number at best gives only an average value over the test-voltage range

Figure 2.2. Curves illustrating that average drift values can conceal the presence of larger actual drift values.

Figure 2.4. Bias current as a function of temperature.

Figure 2.6. In the circuit shown regardless of the op amp's speed, the slew rate is limited by the 1 pF of stray capacitance. As a result, the slew rate is limited to  $10~V/\mu s$ .

3

Applications for Operational Amplifiers By William Routh

National Semiconductor

The usefulness of the operational amplifier is derived from the fact that it can be used in a feedback loop whose feedback properties determine the feed-forward characteristics of the amplifier and the loop combination. To suit it for this use, the ideal operational amplifier would have infinite input impedance, zero output impedance, infinite gain and an open-loop 3-db down point at infinite frequency rolling off at 6 db per octave. Unfortunately, the cost, in quantity, of such an amplifier would also be infinite.

Intensive development of the operational amplifier, particularly in integrated form, has resulted in circuits which are quite good approximations of the ideal for finite cost. Quantity prices for the best contemporary integrated amplifiers are low compared with transistor prices of five years ago. The low cost and high performance provided by these amplifiers permits their being designed into equipment and systems functions impractical with discrete components. An example is a low-frequency function generator which may use 15 to 20 operational amplifiers in generation, wave shaping, triggering and phase-locking.

The availability of the low-cost integrated operational amplifier makes it mandatory that systems and equipment engineers be familiar with operational-amplifier theory (1-4). This chapter will present amplifier applications ranging from a simple unity-gain buffer to relatively complex generator and wave-shaping circuits, all taking advantage of the operational amplifier's characteristics.

The discussion is shaded toward the practical; amplifier parameters will be discussed as they affect circuit performance, and application restrictions will be outlined.

The applications to be covered are arranged in order of increasing complexity in five categories: simple amplifiers, operational circuits, transducer amplifiers, wave shapers and generators, and power supplies. The integrated amplifiers shown in the circuit diagrams are for the most part internally compensated so frequency stabilization components are not used; however, as the discussion will show, other amplifiers may be used with stabilization components in many of these circuits to achieve greater operating speeds.

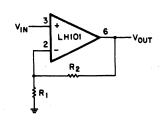

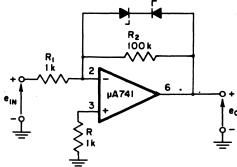

# 3.1 THE INVERTING AMPLIFIER

The basic operational-amplifier circuit is shown in Figure 3.1. This circuit, as the name implies, inverts. It offers a closed-loop gain of  $R_2/R_1$  provided that this ratio is small compared with the amplifier open-loop gain. The input impedance is equal to  $R_1$ ; the closed-loop bandwidth is equal to the unity-gain frequency divided by one plus the closed-loop gain.

The only precautions to keep in mind when using this circuit are 1) that  $R_3$  should be chosen to be equal to the parallel combination of  $R_1$  and  $R_2$  (to minimize the offset-voltage error due to bias current), and 2) there will be an offset voltage at the amplifier output equal to the closed-loop gain times the offset voltage at the amplifier input.

Offset voltage at the input of an operational amplifier is comprised of two components, these components are identified in specifying the amplifier as input offset voltage and input offset current. The input offset voltage is fixed for a particular amplifier, however the contribution due to input offset current is dependent on the circuit configuration used. For minimum offset voltage at the amplifier input without circuit adjustment the source resistance for both inputs should be equal. In this case the maximum offset voltage would be the algebraic sum of the amplifier offset voltage and the voltage drop across the source resistance due to offset current. Amplifier offset voltage is the predominant error term for low-source resistances and offset current produces the main error for high-source resistances.

In high-source resistance applications, offset voltage at the amplifier output may be set by adjusting the value of  $R_3$  and using the variation in voltage drop across it as an input-offset-voltage trim.

Offset voltage at the amplifier output is not as important in ac coupled applications. Here the only consideration is that any offset voltage at the output reduces the peak-to-peak linear output swing of the amplifier.

The gain-frequency characteristic of the amplifier and its feedback network can team up to cause oscillation. To avoid this condition, the phase shift through the amplifier and feedback network must never exceed 180° for any frequency where the gain of the amplifier and its feedback network is greater than unity. In practical applications, the phase shift should not approach 180° since this is a situation of conditional stability. Obviously the most critical case occurs when the attenuation of the feedback network is zero.

Amplifiers which are not internally compensated may be used to achieve increased performance in circuits where feedback network attenuation is high. As an example, the LM101 may be operated at unity gain in the inverting amplifier circuit with a 15-pF compensating capacitor since the feedback network has an attenuation of 6 dB; this IC however requires 30 pF in the non-inverting unity-gain connection where the feedback network has zero attenuation. Since amplifier slew rate is dependent on compensation, the LM101 (op-amp IC) slew rate in the inverting unity gain connection will be twice that for the non-inverting connection and the inverting-gain-of-ten connection will yield ten times the slew rate of the non-inverting, unity-gain connection. The compensation trade-off for a particular connection is stability versus bandwidth; larger values of compensation capacitor yield greater stability and lower bandwidth and vice versa.

The preceding discussion of offset voltage, bias current and stability applies to most amplifier applications and will be referenced in later sections. A detailed treatment has been given by Paynter (4).

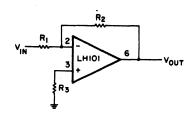

# 3.2 THE NON-INVERTING AMPLIFIER

A high input impedance non-inverting circuit is shown in Figure 3.2. This circuit gives a closed-loop gain equal to the ratio of the sum of  $R_1$  and  $R_2$  to  $R_1$  and a closed-loop 3-dB bandwidth equal to the amplifier unity-gain frequency divided by the closed-loop gain.

The primary differences between this circuit arrangement and the inverting circuit are 1) the output is not inverted and 2) the input impedance is very high and is equal to the differential input impedance multiplied by loop gain. (Open-loop gain/Closed-loop gain.) In dc coupled applications, input impedance is not as important as the input current and the voltage drop across the source resistance.

Application cautions are the same for this amplifier as for the inverting amplifier with one exception. The amplifier output will go into saturation if the input is allowed to float. This may be important if the amplifier must be switched from source to source. The compensation trade off discussed for the inverting amplifier is also valid for this connection.

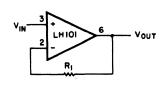

# 3.3 THE UNITY-GAIN BUFFER

The unity-gain buffer is shown in Figure 3.3. The circuit gives the highest input impedance of any operational-amplifier circuit. Input impedance is equal to the differential input impedance multiplied by the open-loop gain, in parallel with common-mode input impedance. The gain error of this circuit is equal to the reciprocal of the amplifier open-loop gain or to the common-mode rejection, whichever is less.

Input impedance is a misleading concept in a dc coupled unity-gain buffer. Bias current for the amplifier will be supplied by the source resistance and will cause an error at the amplifier input due to its voltage drop across the source resistance. Since this is the case; a low-bias-current amplifier such as the LH102 (6) should be chosen as a unity-gain buffer when working from high source resistances. Bias current compensation techniques have been covered by Widlar (5).

Three important considerations in the use of this circuit are 1) the amplifier must be compensated for unity gain operation, 2) the output swing of the amplifier may be limited by the amplifier common-mode range, and 3) some amplifiers exhibit a latch-up mode when the amplifier common-mode range is exceeded. The LH101 if used in this circuit eliminates these problems; for faster operation, the LM102 may be chosen.

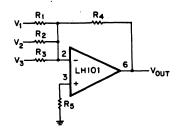

3.4 SUMMING AMPLIFIER

The summing amplifier, a special case of the inverting amplifier, is shown in Figure 3.4. The circuit gives an inverted output which is equal to the weighted algebraic sum of all three inputs. The gain of this circuit for any input is equal to the ratio of the appropriate input resistor to the feedback resistor, R<sub>4</sub>. Amplifier bandwidth may be calculated as in the inverting amplifier shown in Figure 3.1 by assuming the input resistor to be the parallel combination of R<sub>1</sub>, R<sub>2</sub>, and R<sub>3</sub>. Application cautions are the same as for the inverting amplifier. If an uncompensated amplifier is used, compensation is calculated on the basis of bandwidth as is discussed in the section describing the simple inverting amplifier.

The advantage provided by this circuit is that no interaction occurs between inputs, operations such as summing and weighted averaging are implemented very easily.

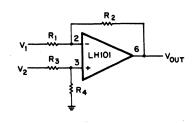

# 3.5 THE DIFFERENCE AMPLIFIER

The difference amplifier is the complement of the summing amplifier; it allows the subtraction of two voltages or, as a special case, the cancellation of a signal common to the two inputs. This circuit is shown in Figure 3.5 and is useful as a

computational amplifier, in making a differential to single-ended conversion or in rejecting a common-mode signal.

Circuit bandwidth may be calculated in the same manner as for the inverting amplifier, but input impedance is somewhat more complicated. Input impedance for the two inputs is not necessarily equal; inverting input impedance is the same as for the inverting amplifier of Figure 3.1 and the noninverting input impedance is the sum of  $R_3$  and  $R_4$ . Gain for either input is the ratio of  $R_1$  to  $R_2$  for the special case of a differential input single-ended output where  $R_1 = R_3$  and  $R_2 = R_4$ . The general expression for gain is given in the figure. Compensation should be chosen on the basis of amplifier bandwidth.

Care must be exercised in applying this circuit since input impedances are not equal for minimum bias current error.

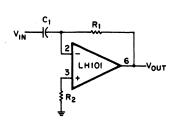

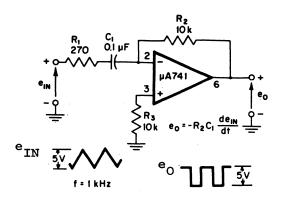

# 3.6 DIFFERENTIATOR

The differentiator is shown in Figure 3.6 and, as the name implies, is used to perform the mathematical operation of differentiation. The form shown is not the practical form, it is a true differentiator and is extremely susceptible to high-frequency noise since ac gain increases at the rate of 6 dB per octave. In addition, the feedback network of the differentiator,  $R_2C_1$ , is an RC low-pass filter which contributes  $90^{\circ}$  phase shift to the loop and may cause stability problems even with an amplifier which is compensated for unity gain.

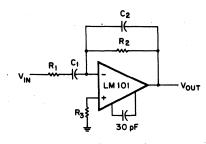

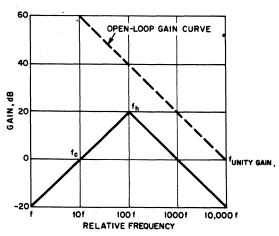

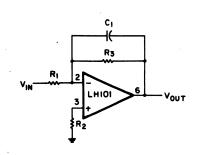

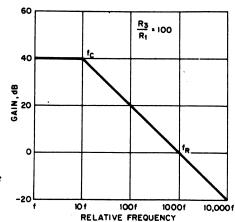

A practical differentiator is shown in Figure 3.7. Here both the stability and noise problems are corrected by the addition of two components,  $R_1$  and  $C_2$ .  $R_2$  and  $C_2$  form a 6 dB per octave high-frequency roll-off in the feedback network and  $R_1C_1$  form a 6 dB per octave roll-off network in the input network for a total high-frequency roll-off of 12 dB per octave to reduce the effect of high-frequency input and amplifier noise. In addition  $R_1C_1$  and  $R_2C_2$  form lead networks in the feedback loop which, if placed below the amplifier unity gain frequency, provide  $90^\circ$  phase lead to compensate the  $90^\circ$  phase lag of  $R_2C_1$  and prevent loop instability. A gain-frequency plot is shown in Figure 3.8 for clarity.

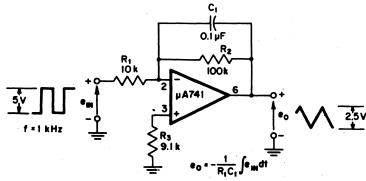

# 3.7 INTEGRATOR

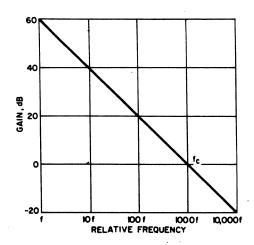

An integrator is shown in Figure 3.9. This circuit performs the mathematical operation of integration. It is essentially a low-pass filter with a frequency response decreasing at 6 dB per octave. An amplitude-frequency plot for the circuit is shown in Figure 3.10.

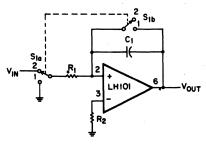

The circuit must be provided with an external method of establishing initial conditions as shown in the figure by  $\mathbf{S}_1$ . When  $\mathbf{S}_1$  is in position 1, the amplifier is connected for unity-gain and capacitor  $\mathbf{C}_1$  is discharged, setting an initial condition of zero volts. When  $\mathbf{S}_1$  is in position 2, the amplifier is connected as an integrator and its output will change in accordance with a constant multiplied by the time integral of the input voltage.

Precautions to be observed with this circuit are: the amplifier used must in all cases be stabilized for unity-gain operation and  $\rm R_2$  must equal  $\rm R_1$  for minimum error due to bias current.

### 3.8 SIMPLE LOW-PASS FILTER

A simple low-pass filter is shown in Figure 3.11. This circuit has a 6 dB per octave roll-off after reaching a closed-loop 3-dB point defined by  $f_c$ . Gain below this corner frequency is defined by the ratio of  $R_3$  to  $R_1$ . The circuit may be considered as an ac integrator at frequencies well above  $f_c$ ; however, the time domain response is that of a single RC rather than an integral.

The value of  $R_2$  should be chosen so that it is equal to the parallel combination of  $R_1$  and  $R_3$  thus minimizing errors due to bias current. Either the amplifier should be compensated for unity-gain or an internally compensated amplifier should be used.

A gain-frequency plot of the circuit response is shown in Figure 3.12 to illustrate the difference between this circuit and the true integrator.

# 3.9 THE CURRENT-TO-VOLTAGE CONVERTER

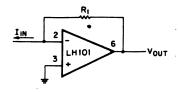

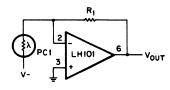

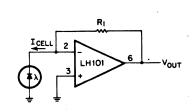

Current may be measured in two ways with an operational amplifier. The current may be converted into a voltage using a resistor and then amplified or the current may be injected directly into a summing node. Converting into voltage is undesirable for two reasons: first, an impedance is inserted into the measuring line causing an error; second, amplifier offset voltage is also amplified with a subsequent loss of accuracy. The use of a current-to-voltage transducer avoids both of these problems.

The current-to-voltage transducer is shown in Figure 3.13. The input current is fed directly into the summing node and the amplifier output voltage changes to extract the same current from the summing node through  $R_1$ . The scale factor of this circuit is  $R_1$  volts per ampere. The only conversion error in this circuit is  $I_{\mbox{bias}}$  which is summed algebraically with  $I_{\mbox{TN}}$ .

This basic circuit is useful for many applications other than current measurement. For example, it can be employed as a photocell amplifier.

The only design constraints that come into play are that scale factors must be chosen to minimize errors due to bias current, and since voltage gain and source impedance are often indeterminate (as with photocells) the amplifier must be compensated for unity-gain operation. Valuable techniques for bias current compensation have been covered by Widlar (5).

# 3.10 PHOTOCELL AMPLIFIERS

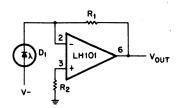

Amplifiers for photoconductive, photodiode and photovoltaic cells are shown in Figures 3.14, 3.15, and 3.16 respectively.

The voltages of all photogenerators have some dependence on both speed and linearity. It is obvious that the current through a photoconductive cell will not display strict proportionality to incident light if the cell terminal voltage is allowed to vary with cell conductance. Somewhat less obvious is the fact that photodiode leakage and photovoltaic cell internal losses are also functions of terminal voltage. The current-to-voltage converter neatly sidesteps gross linearity problems by fixing a constant terminal voltage, zero in the case of photovoltaic cells and a fixed bias voltage in the case of photoconductors or photodiodes.

Photodetector speed is optimized by operating into a fixed low load impedance. Currently available photovoltaic detectors show response times in the microsecond

range at zero load impedance and photoconductors, these speeds are slow but faster speeds can be obtained at low load resistances.

The feedback resistance,  $R_1$ , is dependent on cell sensitivity and should be chosen for either maximum dynamic range or for a desired scale factor.  $R_2$  is elective: in the case of photovoltaic cells or of photodiodes, it should equal  $R_1$ ; in the case of photoconductive cells, it should be chosen to minimize bias current error over the operating range.

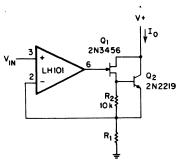

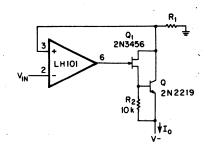

# 3.11 PRECISION CURRENT SOURCE

A precision current source is shown in Figures 3.17 and 3.18. The configurations depicted sink or source conventional current, respectively.

Caution must be exercised in applying these circuits. The voltage compliance of the source extends from  $\text{BV}_{\text{CER}}$  of the external transistor to approximately 1 V more negative than  $\text{V}_{\text{IN}}.$  The compliance of the current sink is the same in the positive direction.

The impedance of these current generators is essentially infinite for small currents and the generator outputs are accurate so long as  $V_{\rm IN}$  is much greater than  $V_{\rm OS}$  and  $I_{\rm O}$  is much greater than  $I_{\rm bias}$ .

The source and sink illustrated in Figures 3.17 and 3.18 use a field-effect transistor to drive a bipolar output transistor. It is possible to use a Darlington connection in place of the FET-bipolar combination in cases where the output current is high and the base current of the Darlington input would not cause a significant error.

The amplifiers used must be compensated for unity-gain and additional compensation may be required depending on load reactance and external transistor parameters.

# 3.12 ADJUSTABLE VOLTAGE REFERENCES

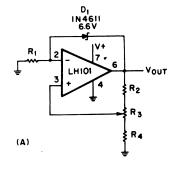

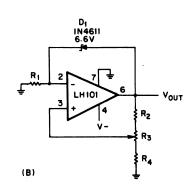

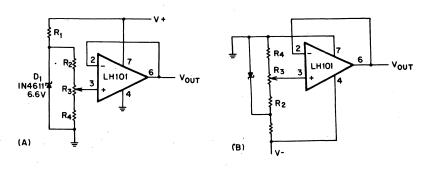

Adjustable voltage reference circuits are shown in Figures 3.19 and 3.20. The two circuits have different areas of application. The basic difference between the two is that the circuit in Figure 3.19 illustrates a voltage source which provides a voltage greater than the reference diode while the circuit in Figure 3.20 represents a voltage source which provides a voltage lower than the reference diode. The figures show both positive and negative voltage sources.

High-precision extended-temperature applications of the circuit in Figure 3.19 require that the range of adjustment of  $V_{OUT}$  be restricted. When this is done,  $R_1$  may be chosen to provide optimum zener current for a minimum zener temperature coefficient. Since  $I_Z$  is not a function of  $V^+$ , the reference temperature coefficient will be independent of  $V^+$ .

The circuit of Figure 3.20 is suited for high-precision extended-temperature service if  $V^+$  is reasonably constant since  $I_Z$  is dependent of  $V^+$ .  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$  are chosen to provide the proper  $I_Z$  for minimum T. C. and to minimize errors due to  $I_{\rm bias}$ .

The circuits shown should both be compensated for unity-gain operation or, if large capacitive loads are expected, should be overcompensated. Output noise may be reduced in both circuits by bypassing the amplifier imput.

The circuits shown employ a single power supply; this requires that common-mode range be considered in choosing an amplifier for these applications. If the common-mode range requirements are in excess of the capability of the amplifier, two power supplies may be used. The LH101 operational amplifier may be used with a single power supply since the common-mode range is from  $V^+$  to within approximately 2 volts of  $V^-$ .

# 3.13 THE RESET STABILIZED AMPLIFIER

The reset stabilized amplifier, a form of chopper-stabilized amplifier, is shown in Figure 3.21. The amplifier is operated closed-loop with a gain of one.

The connection shown is useful in eliminating errors due to offset voltage and bias current. The output of this circuit is a pulse whose amplitude is equal to  $V_{\rm IN}$ . Operation may be understood by considering the two conditions corresponding to the position of  $S_1$ . When  $S_1$  is in position 2, the amplifier is connected in the unity-gain connection and the voltage at the output will be equal to the sum of the input offset voltage and the drop across  $R_2$  due to input bias current. The voltage at the inverting input will be equal to the input offset voltage. Capacitor  $C_1$  will charge to the sum of the input offset voltage and  $V_{\rm IN}$  through  $R_1$ . When  $C_1$  is charged, no current flows through the source resistance and  $R_1$ , so there is no error due to the input resistance.

$S_1$  is then changed to position 1. The voltage stored on  $C_1$  is inserted between the output and inverting input of the amplifier and the output of the amplifier changes by  $V_{IN}$  to maintain the amplifier input at the input offset voltage. The output then changes from  $(V_{OS} + I_{bias}R_2)$  to  $V_{IN} + (V_{OS} + I_{bias}R_2)$  as  $S_1$  is switched from position 2 to position 1. Amplifier bias current is supplied through  $R_2$  from the output of the amplifier when  $S_1$  is in position 2 or from  $C_2$  when  $S_1$  is in position 1. Resistor  $R_3$  serves to reduce the offset at the amplifier output if the amplifier must have maximum linear range or if it is desired to dc couple the amplifier.

An additional advantage provided by this connection is that the input resistance approaches infinity as the capacitor  $C_1$  approaches full charge, eliminating errors due to loading of the source resistance. The time spent in position 2 should be sufficiently long with respect to the changing time of  $C_1$  to permit maximum accuracy.

The amplifier used must be compensated for unity-gain operation and it may be necessary to overcompensate because of the phase shift across  $R_2$  due to  $C_1$  and the amplifier input capacity. Since this connection is usually used at very low switching speeds, slew rate is not normally a practical consideration and overcompensation does not reduce accuracy.

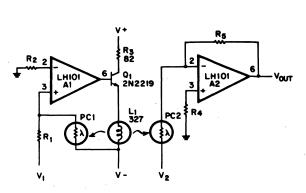

# 3.14 ANALOG MULTIPLIER

A simple analog multiplier is shown in Figure 3.22. This circuit circumvents many of the problems associated with the log-antilog circuit and provides three-quadrant analog multiplication which is relatively temperature insensitive and which is not subject to the bias-current errors which plague most multipliers.

The circuit operation may be understood by considering  ${\tt A}_2$  as a controlled-gain amplifier, amplifying  ${\tt V}_2$ , with the gain dependent on the ratio of the resistance of

$PC_2$  to  $R_5$  and by considering  $A_1$  as a control amplifier which establishes the resistance of  $PC_2$  as a function of  $V_1$ . In this way it is seen that  $V_{OUT}$  is a function of both  $V_1$  and  $V_2$ .

$A_1$ , the control amplifier, provides drive for the lamp,  $L_1$ . When an input voltage,  $V_1$ , is present,  $L_1$  is driven by  $A_1$  until the current to the summing junction from the negative supply through  $PC_1$  is equal to the current to the summing junction from  $V_1$  through  $R_1$ . Since the negative supply voltage is fixed, this forces the resistance of  $PC_1$  to a value proportional to  $R_1$  and to the ratio of  $V_1$  to  $V_1$ .  $L_1$  also illuminates  $PC_2$  and, if the photoconductors are matched, causes  $PC_2$  to have a resistance equal to  $PC_1$ .

$A_2$ , the controlled gain amplifier, acts as an inverting amplifier with a gain which is equal to the ratio of the resistance of PC<sub>2</sub> to R<sub>5</sub>. If R<sub>5</sub> is chosen equal to the product of R<sub>1</sub> and V<sup>-</sup>, then V<sub>OUT</sub> becomes simply the product of V<sub>1</sub> and V<sub>2</sub>. Resistor R<sub>5</sub> may be scaled in powers of ten to provide any required output scale factor.

$PC_1$  and  $PC_2$  should be matched for best tracking over temperature since the temperature coefficient of resistance is related to the resistance match of cells with the same geometry. Small mismatches may be compensated by varying the value of  $R_5$  as a scale-factor adjustment. The photoconductive cells should receive equal illumination from  $L_1$ ; this can be accomplished by mounting the cells in holes in an aluminum block and placing the lamp midway between them. This mounting method provides controlled spacing and also provides a thermal bridge between the two cells to reduce differences in cell temperature. This technique may be extended to use FETs or other devices to meet special resistance or environment requirements.

The circuit as shown provides an inverting output whose magnitude is equal to one-tenth the product of the two analog inputs. Input  $V_1$  is restricted to positive values, but  $V_2$  may assume both positive and negative values. This circuit is restricted to low-frequency operation by the lamp time constant.

Resistors  $R_2$  and  $R_4$  are chosen to minimize errors due to input offset current as previously mentioned for the photocell amplifier. Resistor  $R_3$  is included to reduce the in-rush current when  $L_1$  starts to turn on.

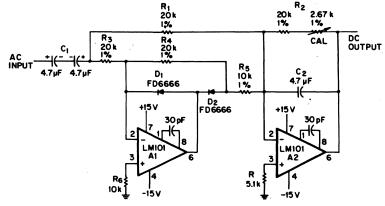

# 3.15 FULL-WAVE RECTIFIER AND AVERAGING FILTER

The circuit shown in Figure 3.23 is the heart of an average-reading, rms-calibrated ac voltmeter. As shown, the circuit is a rectifier and averaging filter. If  $C_2$  is deleted, the averaging function is removed and the circuit becomes a precision fullwave rectifier; deletion of  $C_1$  provides an absolute value generator.

The circuit operation may be understood by following the signal path first for negative, then for positive inputs. For negative signals, the output of amplifier  $A_1$  is clamped to +0.7 V by  $D_1$  and disconnected from the summing point of  $A_2$  by  $D_2$ .  $A_2$  then functions as a simple unity-gain inverter with input resistor,  $R_1$ , and feedback resistor,  $R_2$ , giving a positive going output.

For positive inputs,  $A_1$  operates as a normal amplifier connected to the  $A_2$  summing point through resistor,  $R_5$ . Amplifier  $A_1$  then acts as a simple unity-gain inverter

with input resistor,  $R_3$ , and feedback resistor,  $R_5$ . The gain accuracy of  $A_1$  is not affected by D2 since it is inside the feedback loop. Positive current enters the  $A_2$  summing point through resistor  $R_1$ , and negative current is drawn from the  $A_2$  summing point through resistor  $R_5$ . Since the voltages across  $R_1$  and  $R_5$  are equal and opposite, and  $R_5$  is one-half the value of  $R_1$ , the net input current at the  $A_2$  summing point is equal to and opposite from the current through  $R_1$ , and amplifier  $A_2$  operates as a summing inverter with unity gain, again giving a positive output.

The circuit becomes an averaging filter when  $C_2$  is connected across  $R_2$ . Operation of  $A_2$  is then similar to the simple low-pass filter previously described. The time constant  $R_2C_2$  should be chosen so that it is much larger than the maximum period of the input voltage which is to be averaged.

Capacitor  $C_1$  may be deleted if the circuit is to be used as an absolute-value generator. When this is done, the circuit output will be the positive absolute value of the input voltage.

The amplifiers chosen must be compensated for unity-gain operation and  $R_6$  and  $R_7$  must be chosen to minimize output errors due to input offset current.

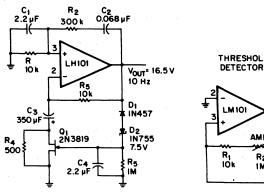

# 3.16 SINE-WAVE OSCILLATOR

An amplitude-stabilized sine-wave oscillator is shown in Figure 3.24. This circuit provides high-purity sine-wave output down to low frequencies with minimum circuit complexity. An important advantage of this circuit is that the traditional tungsten-filament-lamp amplitude regulator is eliminated along with its time constant and linearity problems.

In addition, the reliability problems associated with a lamp are eliminated.

A Wien-Bridge oscillator takes advantage of the fact that the phase of the voltage across the parallel branch of a series and a parallel RC network connected in series, is the same as the phase of the applied voltage across the two networks at one particular frequency and that the phase lags with increasing frequency and leads with decreasing frequency. When this network—the Wien Bridge—is used as a positive feedback element around an amplifier, oscillation occurs at the frequency at which the phase shift is zero. Additional negative feedback is provided to set the loop gain to unity at the oscillation frequency, to stabilize the frequency of oscillation, and to reduce harmonic distortion.

The circuit presented here differs from the classic form only in its negative feedback stabilization scheme in the circuit; negative peaks in excess of -8.25 V cause  $D_1$  and  $D_2$  to conduct, charging  $C_4$ . The charge stored in  $C_4$  provides bias to  $Q_1$ , which determines the amplifier gain.  $C_3$  is a low frequency roll-off capacitor in the feedback network and prevents offset voltage and offset current errors from being multiplied by amplifier gain.

Distortion is determined by the amplifier open-loop gain and by the response time of the negative feedback loop filter,  $R_5$  and  $C_4$ . A trade-off is necessary in determining amplitude stabilization time constant and oscillator distortion. Resistor  $R_4$  is chosen to adjust the negative feedback loop so that the FET is operated at a small negative gate bias. The circuit shown provides optimum values for a general-

purpose oscillator.

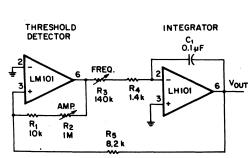

### 3.17 TRIANGLE-WAVE GENERATOR

A constant-amplitude triangular-wave generator is shown in Figure 3.25. This circuit provides a variable-frequency triangular wave whose amplitude is independent of frequency.

The generator contains an integrator which functions as a ramp generator and a threshold detector with hysterisis which is the reset circuit. The integrator has been described earlier in this chapter. The threshold detector is similar to a Schmit Trigger in that it is a latch circuit with a large dead zone. This function is implemented by using positive feedback around an operational amplifier. When the amplifier output is in either the positive or negative saturated state, the positive feedback network provides a voltage at the non-inverting input which is determined by the attenuation of the feedback loop and the saturation voltage of the amplifier. To cause the amplifier to change states, the voltage at the input of the amplifier must change polarity by an amount larger than the amplifier input offset voltage.

When this occurs, the amplifier saturates in the opposite direction and remains in that state until the voltage at its input again reverses. The complete operation of the circuit may be grasped by examining its operation with the output of the threshold detector in the positive state. The detector positive saturation voltage is applied to the integrator summing junction through the combination  $R_3$  and  $R_4$  causing a current  $\mathbf{I}^+$  to flow. The integrator then generates a negative-going ramp with a rate of  $\mathbf{I}^+/\mathbf{C}_1$  volts per second until its output equals the negative trip point of the threshold detector. The threshold detector then changes to the negative output state and supplies a negative current,  $\mathbf{I}^-$ , at the integrator summing point. The integrator now generates a positive-going ramp with a rate of  $\mathbf{I}^-/\mathbf{C}_1$  volts per second until its output equals the positive trip point of the threshold detector where the detector again changes output state and the cycle repeats.

The triangular-wave frequency is determined by  $R_3$ ,  $R_4$  and  $C_1$  and the positive and negative saturation voltages of the amplifier  $A_1$ . The amplitude is determined by the ratio of  $R_5$  to the combination of  $R_1$  and  $R_2$  and the threshold detector saturation voltages. The positive and negative ramp rates are equal, and positive and negative peaks are equal if the detector has equal positive and negative saturation voltages. The output waveform may be offset with respect to ground if the inverting input of the threshold detector,  $A_1$ , is offset with respect to ground.

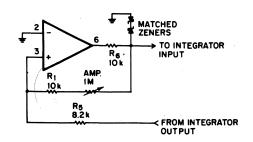

The generator may be made independent of temperature and supply voltage if the detector is clamped with matched zener diodes as shown in Figure 3.26.