# Memory **Databook**

- PROMs, EPROMs, EEPROMs

- Flash EPROMs and EEPROMs

- TTL I/O SRAMs

- ECL I/O SRAMs

- ECL I/O Memory Modules

, ÷

# A Corporate Dedication to Quality and Reliability

National Semiconductor is an industry leader in the manufacture of high quality, high reliability integrated circuits. We have been the leading proponent of driving down IC defects and extending product lifetimes. From raw material through product design, manufacturing and shipping, our quality and reliability is second to none.

We are proud of our success . . . it sets a standard for others to achieve. Yet, our quest for perfection is ongoing so that you, our customer, can continue to rely on National Semiconductor Corporation to produce high quality products for your design systems.

Charles E. Sporck

President, Chief Executive Officer National Semiconductor Corporation

# Wir fühlen uns zu Qualität und Zuverlässigkeit verpflichtet

National Semiconductor Corporation ist führend bei der Herstellung von integrierten Schaltungen hoher Qualität und hoher Zuverlässigkeit. National Semiconductor war schon immer Vorreiter, wenn es galt, die Zahl von IC Ausfällen zu verringern und die Lebensdauern von Produkten zu verbesern. Vom Rohmaterial über Entwurf und Herstellung bis zur Auslieferung, die Qualität und die Zuverlässigkeit der Produkte von National Semiconductor sind unübertroffen.

Wir sind stolz auf unseren Erfolg, der Standards setzt, die für andere erstrebenswert sind. Auch ihre Ansprüche steigen ständig. Sie als unser Kunde können sich auch weiterhin auf National Semiconductor verlassen.

#### La Qualité et La Fiabilité:

Une Vocation Commune Chez National Semiconductor Corporation

National Semiconductor Corporation est un des leaders industriels qui fabrique des circuits intégrés d'une très grande qualité et d'une fiabilité exceptionelle. National a été le premier à vouloir faire chuter le nombre de circuits intégrés défectueux et a augmenter la durée de vie des produits. Depuis les matières premières, en passant par la conception du produit sa fabrication et son expédition, partout la qualité et la fiabilité chez National sont sans équivalents.

Nous sommes fiers de notre succès et le standard ainsi défini devrait devenir l'objectif à atteindre par les autres sociétés. Et nous continuons à vouloir faire progresser notre recherche de la perfection; il en résulte que vous, qui êtes notre client, pouvez toujours faire confiance à National Semiconductor Corporation, en produisant des systèmes d'une très grande qualité standard.

## Un Impegno Societario di Qualità e Affidabilità

National Semiconductor Corporation è un'industria al vertice nella costruzione di circuiti integrati di altà qualità ed affidabilità. National è stata il principale promotore per l'abbattimento della difettosità dei circuiti integrati e per l'allungamento della vita dei prodotti. Dal materiale grezzo attraverso tutte le fasi di progettazione, costruzione e spedizione, la qualità e affidabilità National non è seconda a nessuro.

Noi siamo orgogliosi del nostro successo che fissa per gli altri un traguardo da raggiungere. Il nostro desiderio di perfezione è d'altra parte illimitato e pertanto tu, nostro cliente, puoi continuare ad affidarti a National Semiconductor Corporation per la produzione dei tuoi sistemi con elevati livelli di qualità.

Charles E. Sporck

President, Chief Executive Officer National Semiconductor Corporation

Charlie Spork

## **MEMORY**

## **DATABOOK**

1988 Edition

**CMOS EPROMs**

Flash CMOS EPROMs and EEPROMs

**EEPROMs**

**PROMs**

**ECL I/O Static RAMs**

TTL I/O Static RAMs

**Memory Modules**

**Physical Dimensions**

## 5

## 6

## 7

#### **TRADEMARKS**

Following is the most current list of National Semiconductor Corporation's trademarks and registered trademarks.

Abuseable<sup>TM</sup> Fairtech™ MOLETM **SCXTM** Anadig™ **FAST® MSTTM** SERIES/800™ Series 900TM ANS-R-TRAN™ 5-Star Service™ Naked-8TM **APPSTM** GAL® National® Series 3000™ **ASPECT™ GENIXTM** National Semiconductor® Series 32000® Auto-Chem Deflasher™ **GNXTM** National Semiconductor Shelf ∠Chek™ ВСРТМ **HAMR<sup>TM</sup>** Corp.® SofChek<sup>TM</sup> BI-FETTM HandiScan™ NAX 800™ SPIRETM Nitride Plus™ BI-FET IITM HEX 3000™ STARTM. **BI-LINETM НРСТМ** Nitride Plus Oxide™ Starlink<sup>TM</sup> **BIPLANTM** l3L® **NMLTM** STARPLEXTM. **BLCTM ICMTM NOBUSTM** SuperChip<sup>TM</sup> **BLXTM** INFOCHEX™ NSC800TM SuperScript<sup>TM</sup> Brite-LiteTM Integral ISETM **NSCISETM** SYS32TM **BTLTM** TapePak® Intelisplay<sup>TM</sup> NSX-16™ TDSTM CheckTrack™ **ISETM** NS-XC-16™ **CIMTM** ISE/06TM **NTERCOM™** TeleGate™ **CIMBUSTM** ISE/08TM **NURAM™** The National Anthem® **CLASICTM** ISE/16TM **OXISSTM** Time Chek™ TINATM Clock Chek™ ISE32TM P2CMOSTM COMBOTM PC Master™ TLCTM **ISOPLANAR™** COMBO ITM ISOPLANAR-ZTM Perfect Watch™ Trapezoidal™ COMBO IITM TRI-CODE™ KevScan™ Pharma Chek™ **LMCMOSTM** COPS™ microcontrollers PLANTM TRI-POLYTM Datachecker® M2CMOSTM **PLANARTM** TRI-SAFETM Macrobus<sup>TM</sup> **DENSPAKTM** Polycraft™ TRI-STATE® DIBTM Macrocomponent<sup>TM</sup> POSilink™ **TURBOTRANSCEIVERTM** MAXI-ROM® POSitalker™ VIPTM Digitalker® DISCERN™ Meat ✓ Chek™ Power + Control™ VR32TM DISTILLTM MenuMaster™ POWERplanar™ **WATCHDOG™** DNR® QUAD3000TM Microbus™ data bus **XMOSTM DPVMTM** MICRO-DACTM QUIKLOOKTM **XPUTM ELSTARTM** utalker™ **RATTM** Z STARTM

Z80® is a registered trademark of Zilog Corporation

TouchTone™ is a trademark of Western Electric Co., Inc.

CUPL® is a registered trademark of Assisted Technology, Inc.

ABEL® is a registered trademark of Data I/O

PAL® is a registered trademark of Monolithic Memories

FLASHTM is a trademark of SEEQ Technology, Inc.

Microtalker<sup>TM</sup>

MICROWIRETM

MICROWIRE/PLUSTM

#### LIFE SUPPORT POLICY

E-Z-LINKTM

**FAIRCADTM**

**FACTIM**

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

RTX16™

SABRIM

Script/ChekTM

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

883B/RETS™

883S/RETS™

National Semiconductor Corporation 2900 Semiconductor Drive, P.O. Box 58090, Santa Clara, California 95052-8090 (408) 721-5000 TWX (910) 339-9240

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied, and National reserves the right, at any time without notice, to change said circuitry or specifications.

# Memory Databook Introduction

National Semiconductor's Memory Databook is a comprehensive collection of information on advanced memory products intended to meet the needs of virtually every electronic system being designed today. National Semiconductor is committed to designing and supplying high performance memory products ranging from state-of-the-art static RAMs to programmable non-volatile EPROMs and EEPROMs.

National Semiconductor has an array of advanced technology processes to apply to memory design and development. These range from our unparalleled BiCMOS process used for the industry's most advanced line of high density ECL I/O SRAMs, to our small geometry, silicon gate, oxide isolated CMOS technology which is now producing unsurpassed, high performance EPROM and EEPROM non-volatile memory devices.

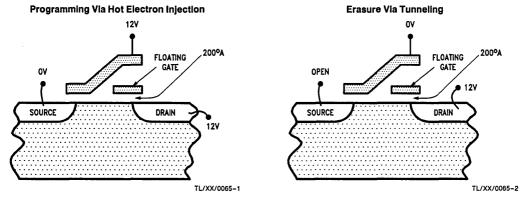

Concurrent with production of these leading edge memory devices is the development of an industry leading FLASHTM EPROM and FLASH EEPROM technology and family of devices designed to be the standard bearers for the next generation of non-volatile memory devices.

National Semiconductor is committed to excellence in design, manufacturing, reliability, and service to our customers through the continuing development of new products and technologies. As new information and devices become available, individual new data sheets will be issued. For the most current information, please contact your local National Semiconductor sales office or Distributor.

## **Product Status Definitions**

## **Definition of Terms**

| Data Sheet Identification     | Product Status            | Definition                                                                                                                                                                                                                                                             |  |  |  |  |

|-------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Advance Information           | Formative or<br>In Design | This data sheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                                                                    |  |  |  |  |

| Preliminary                   | First<br>Production       | This data sheet contains preliminary data, and supplementary data will be published at a later date. National Semiconductor Corporation reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |  |  |  |  |

| No<br>Identification<br>Noted | Full<br>Production        | This data sheet contains final specifications. National Semiconductor Corporation reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                       |  |  |  |  |

National Semiconductor Corporation reserves the right to make changes without further notice to any products herein to improve reliability, function or design. National does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of others.

## **Table of Contents**

| Alphanumeric Index                                                            | хi    |

|-------------------------------------------------------------------------------|-------|

| Section 1 CMOS EPROMS                                                         |       |

| CMOS EPROM Selection Guide                                                    | 1-3   |

| ONE TIME PROGRAMMABLE EPROMs—Introduction                                     | 1-5   |

| NMC27C16 16,384-Bit (2048 x 8) UV Erasable CMOS PROM                          | 1-6   |

| NMC27C32 32,768-Bit (4096 x 8) UV Erasable CMOS PROM                          | 1-13  |

| NMC27C32B 32,768-Bit (4k x 8) High Speed Version UV Erasable CMOS PROM        | 1-20  |

| NMC27C64 65,536-Bit (8k x 8) UV Erasable CMOS PROM                            | 1-29  |

| NMC27C64N 65,536-Bit (8k x 8) One-Time Programmable CMOS PROM                 | 1-38  |

| NMC27C64B 65,536-Bit (8k x 8) High Speed Version UV Erasable CMOS PROM        | 1-47  |

| NMC27C64BN High Speed Version 65,536-Bit (8k x 8) One-Time Programmable       |       |

| CMOS PROM                                                                     | 1-58  |

| NMC27CP128 131,072-Bit (16k x 8) UV Erasable CMOS PROM                        | 1-68  |

| NMC27C128B High Speed Version 131,072 (16k x 8) CMOS PROM                     | 1-76  |

| NMC27C128BN High Speed Version 131,072-Bit (16k x 8) One-Time Programmable    |       |

| CMOS PROM                                                                     | 1-86  |

| NMC27C128C 131,072-Bit (16k x 8) UV Erasable PROM Very High Speed Version     | 1-96  |

| NMC27C256 262,144-Bit (32k x 8) UV Erasable CMOS PROM                         | 1-105 |

| NMC27C256B High Speed Version 262,144-Bit (32k x 8) UV Erasable CMOS PROM     | 1-114 |

| NMC27C256BN High Speed Version 262,144-Bit (32k x 8) One-Time Programmable    |       |

| CMOS PROM                                                                     | 1-124 |

| NMC27C256C 262,144-Bit (32k x 8) UV Erasable CMOS PROM (Very High Speed       |       |

| Version)                                                                      | 1-133 |

| NMC27C512A 524,288-Bit High Speed Version (64k x 8) UV Erasable CMOS PROM     | 1-143 |

| NMC27C512AN 524,288-Bit (64k x 8) One-Time Programmable CMOS PROM             | 1-153 |

| NMC27C010 1,048,576-Bit (128k x 8) UV Erasable CMOS PROM                      | 1-162 |

| NMC27C1024 1,048,576-Bit (64k x 16) UV Erasable CMOS PROM                     | 1-172 |

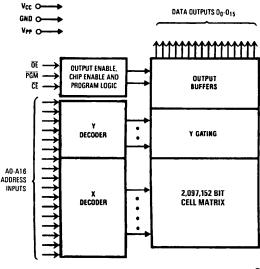

| NMC27C020 2,097,152-Bit (128k x 8) UV Erasable CMOS PROM                      | 1-181 |

| NMC27C2048 2,097,152-Bit (128k x 16) UV Erasable CMOS PROM                    | 1-191 |

| Section 2 FLASH ERASE CMOS EPROMS AND EEPROMS                                 |       |

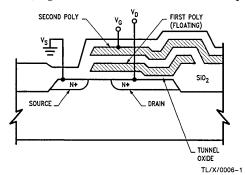

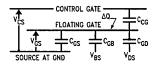

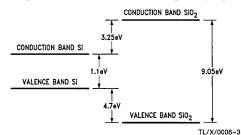

| FLASH TECHNOLOGY—Introduction                                                 | 2-3   |

| NMC48F512 524,288-Bit (64k x 8) CMOS Flash Electrically Erasable Programmable | 2-3   |

| Memory                                                                        | 2-5   |

| ·                                                                             | 2-5   |

| Section 3 EEPROMS                                                             |       |

| Electrically Erasable Programmable Memory Selection Guide                     | 3-3   |

| SERIAL ELECTRICALLY ERASABLE PROGRAMMABLE MEMORY                              | 3-4   |

| NMC9306 256-Bit Serial Electrically Erasable Programmable Memory              | 3-4   |

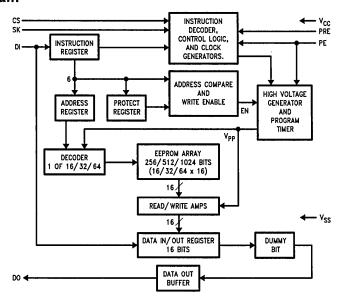

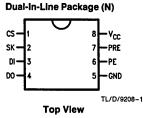

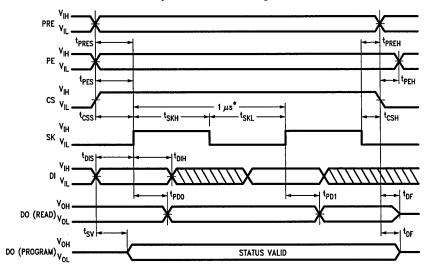

| NMC93C06/C26/C46 256-Bit/512-Bit/1024-Bit Serial Electrically Erasable        | 0.44  |

| Programmable Memory                                                           | 3-11  |

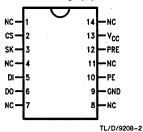

| NMC93CS06/CS26/CS46 256-Bit/512-Bit/1024-Bit Serial Electrically Erasable     | 0.40  |

| Programmable Memory                                                           | 3-19  |

| NMC9307 256-Bit Serial Electrically Erasable Programmable Memory              | 3-30  |

| NMC9313B 256-Bit Serial Electrically Erasable Programmable Memory             | 3-36  |

| NMC9346 1024-Bit Serial Electrically Erasable Programmable Memory             | 3-41  |

| NMC9314B 1024-Bit Serial Electrically Erasable Programmable Memory            | 3-48  |

| NMC93C56/C66 2048-Bit/4096-Bit Serial Electrically Erasable Programmable      |       |

| Memory                                                                        | 3-53  |

| NMC93CS56/CS66 2048-Bit/4096-Bit Serial Electrically Erasable Programmable    |       |

| Memory                                                                        | 3-61  |

| PARALLEL ELECTRICALLY ERASABLE PROGRAMMABLE MEMORY                            |       |

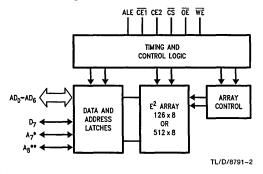

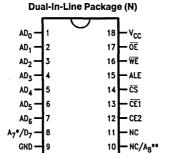

| NMC98C10/C20/C40 Electrically Erasable Programmable Memory                    | 3-72  |

## Table of Contents (Continued)

| , and the second |                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Section 3 EEPROMS (Continued) APPLICATIONS NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |

| AB-15 Protecting Data in Serial Electrically Erasable Programmable Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-78             |

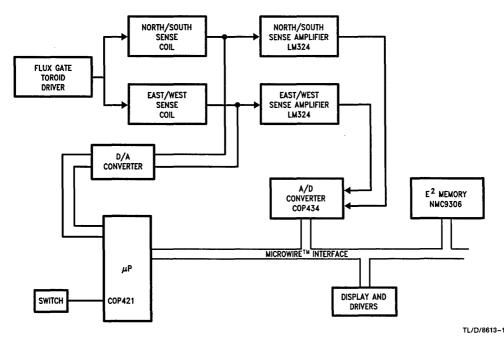

| AB-18 Electronic Compass Calibration Made Easy with Electrically Erasable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  |

| Programmable Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-80             |

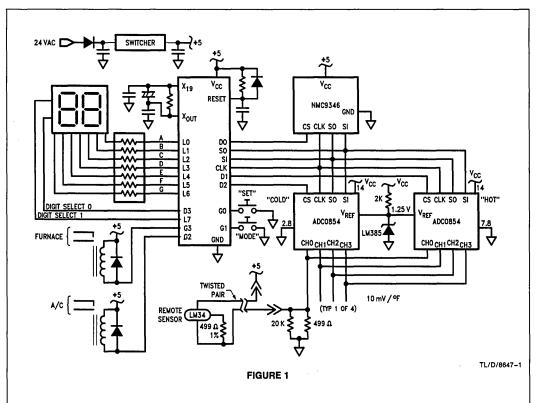

| AB-22 Automatic Low Cost Thermostat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-81             |

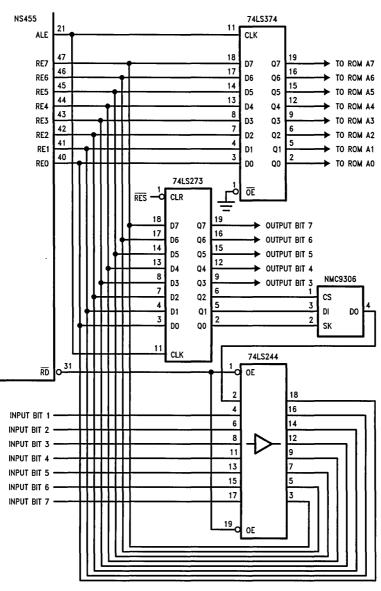

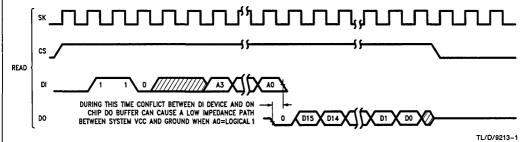

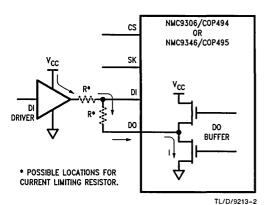

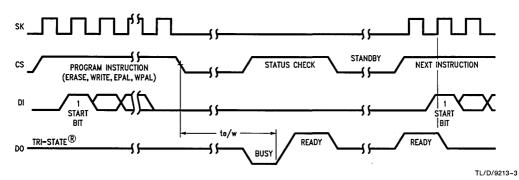

| AN-338 Designing with the NMC9306                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-83             |

| AN-423 NMC9346—An Amazing Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-89             |

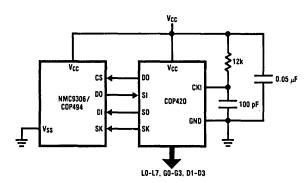

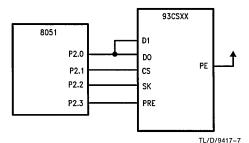

| AN-431 An Easy/Low Cost Serial Electrically Erasable Programmable Memory Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-92             |

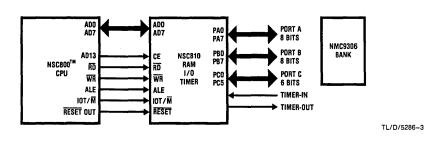

| AN-433 Using the NMC9306 for Configuration and Production Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-95             |

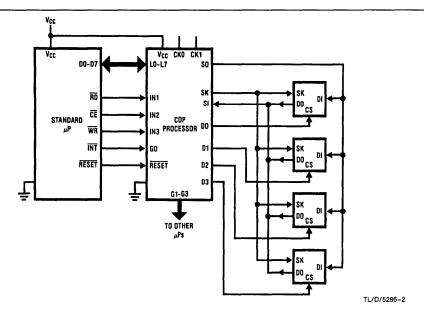

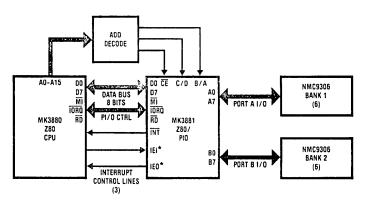

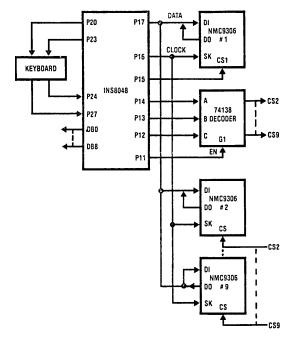

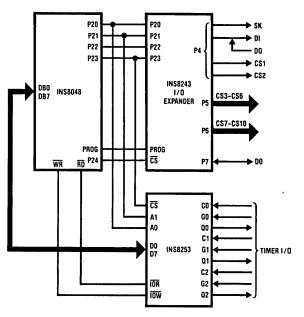

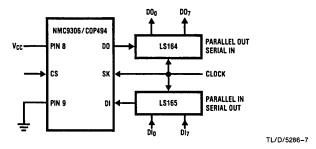

| AN-481 Common I/O Applications for the NMC9306 and NMC9346                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-98             |

| AN-482 Error Detection and Correction Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-101            |

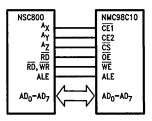

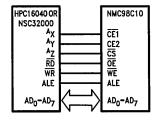

| AN-506 Using the NMC98CXXX Family of Electrically Erasable Programmable Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-106            |

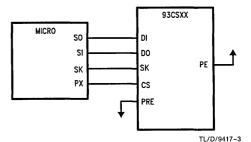

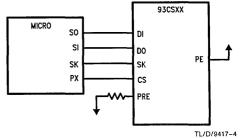

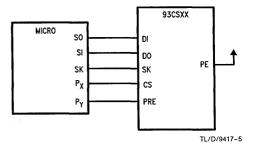

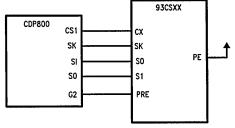

| AN-507 Using the NMC93CSXX Family of Electrically Erasable Programmable Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-111            |

| Reliability National Semiconductor's Electrically Erasable Programmable Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                  |

| Products                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-125            |

| Section 4 PROMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |

| Bipolar PROM Selection Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-3              |

| NON-REGISTERED BIPOLAR PROMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  |

| PL77/87X288B (32 x 8) 256-Bit TTL Logic PROMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-6              |

| DM54/74S188 (32 x 8) 256-Bit TTL PROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-11             |

| DM54/74S288 (32 x 8) 256-Bit TTL PROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-15             |

| DM54/74S287 (256 x 4) 1024-Bit TTL PROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-19             |

| DM54/74S387 (256 x 4) 1024-Bit TTL PROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-23             |

| DM54/74LS471 (256 x 8) 2048-Bit TTL PROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-27             |

| DM54/74S472 (512 x 8) 4096-Bit TTL PROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-31             |

| DM54/74S473 (512 x 8) 4096-Bit TTL PROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-35             |

| DM54/74S474 (512 x 8) 4096-Bit TTL PROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-39             |

| DM54/74S475 (512 x 8) 4096-Bit TTL PROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-43             |

| DM54/74S570 (512 x 4) 2048-Bit TTL PROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-47             |