HITACHI® LCD CONTROLLER/DRIVER LSI DATA BOOK

# LCD CONTROLLER/DRIVER LSI DATA BOOK

#### When using this document, keep the following in mind:

- This document may, wholly or partially, be subject to change without notice.

- All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

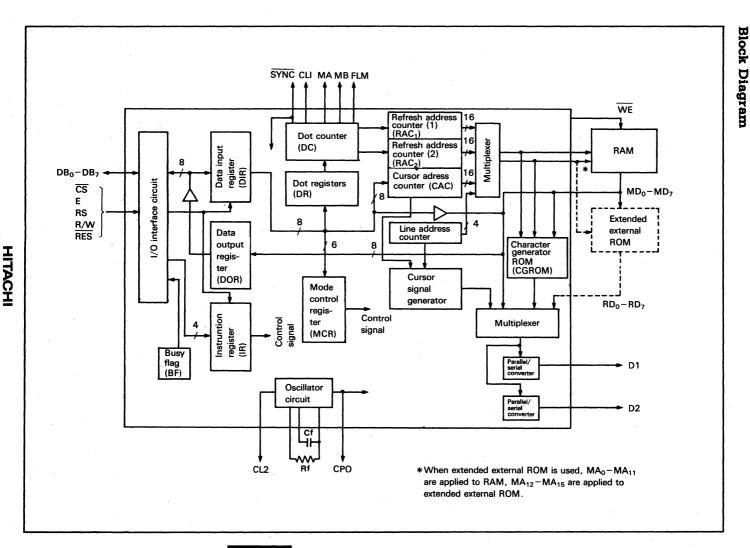

- Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's unit according to this document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

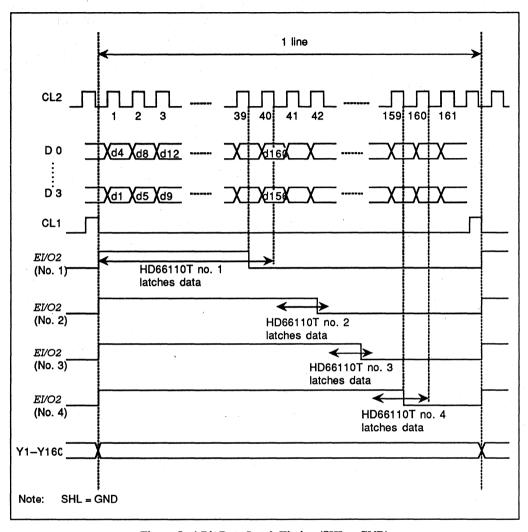

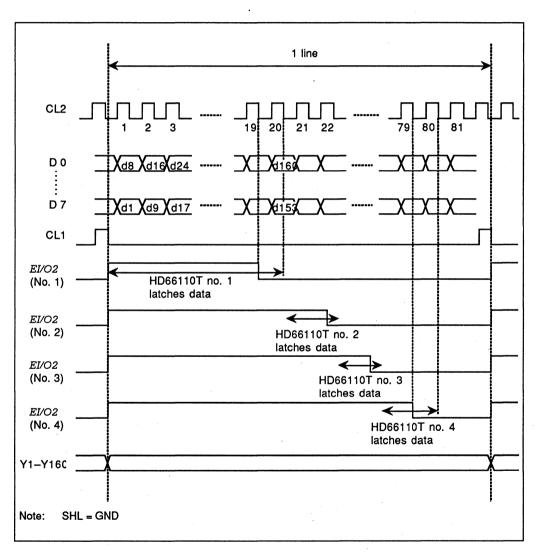

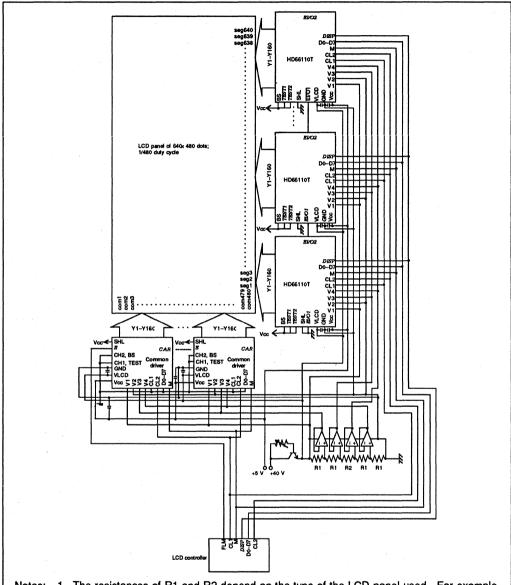

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

## INDEX LCD Controller/Driver LSI Data Book

General Information I

General Information II

DATA SHEETS

General Type LCD Driver

General I

Character Display LCD Controller/Driver

Graphic Display LCD Controller/Driver

Segment Type LCD Controller Driver

Special Application Driver

New Product Information

HITACHI

#### **CONTENTS**

#### LCD CONTROLLER/DRIVER LSI DATA BOOK

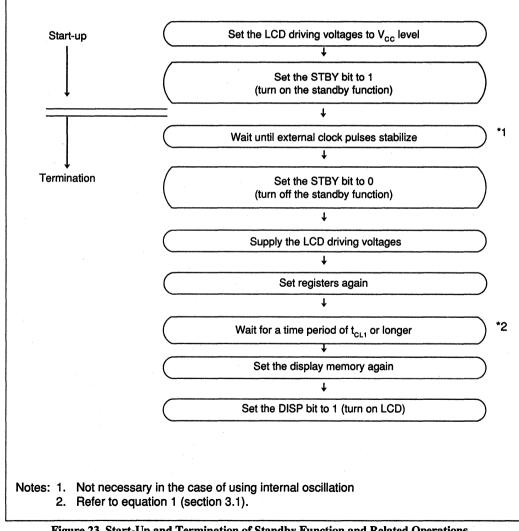

| SECTION 1 General I             | nformation I                                              |     |

|---------------------------------|-----------------------------------------------------------|-----|

| GENERAL INFORMATION             |                                                           | 7   |

| Quick Reference Guide           |                                                           | 9   |

| Type Number Order               |                                                           | 12  |

| Selection Guide                 |                                                           | 13  |

| • Differences Between Products  |                                                           | 16  |

| SECTION 2 General I             | nformation II                                             |     |

| • TCP (Tape Carrier Package)    |                                                           | 24  |

| Package Information             |                                                           | 44  |

| Reliability and Quality Assurar | nce                                                       | 49  |

| Reliability Test Data of LCD D  | Privers                                                   | 56  |

| • Flat Plastic Package (QFP) Mo | unting Methods                                            | 60  |

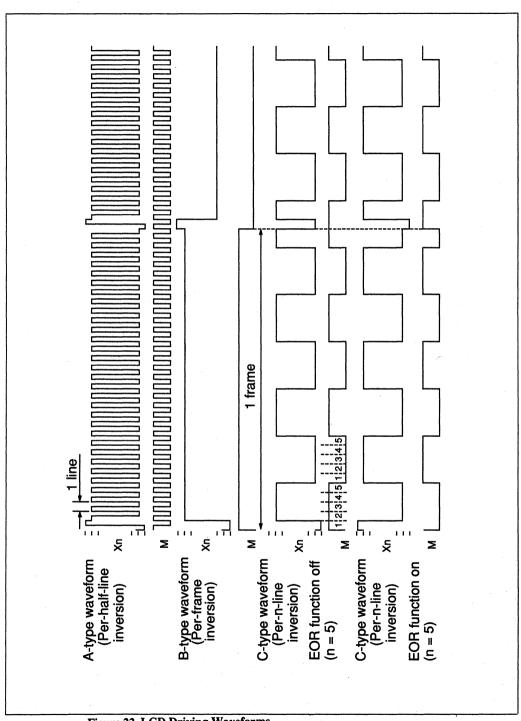

| Liquid Crystal Driving Method   | s                                                         | 63  |

| SECTION 3 General T             | ype LCD Driver                                            |     |

|                                 |                                                           |     |

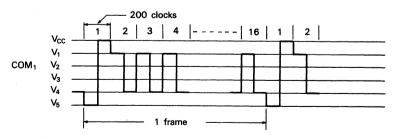

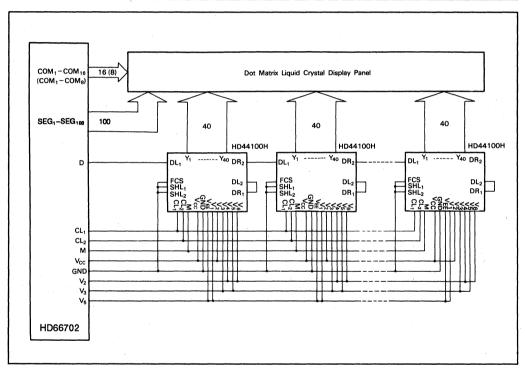

| HD44100H                        | LCD Driver with 40-Channel Outputs                        |     |

| HD66100F                        | LCD Driver with 80-Channel Outputs                        |     |

| HDOOTOOL                        | LCD DITVEL WILL 80-Channel Outputs                        | 67  |

| SECTION 4 Characte              | r Display LCD Controller/Display                          |     |

| HD43160AH                       | Controller with Built-in Character Generator              | 100 |

| HD44780, HD44780A (LCD-         | II) Dot Matrix Liquid Crystal Display Controller & Driver | 114 |

| HD66780 (LCD-IIA)               | Dot Matrix Liquid Crystal Display Controller & Driver     | 167 |

| SECTION 5 Graphic D             | Display LCD Controller/Driver                             |     |

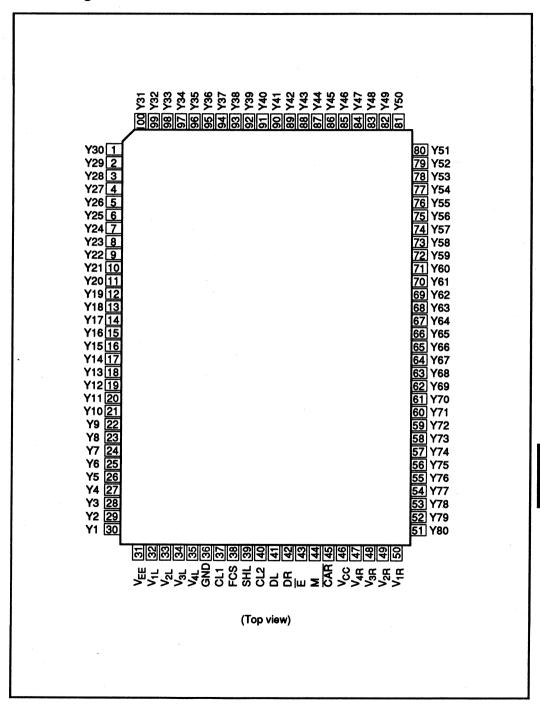

| HD44102CH                       | Dot Matrix Liquid Crystal Graphic Display Column Driver   | 216 |

| HD44103CH                       | Dot Matrix Liquid Crystal Graphic Display Common Driver   |     |

| HD44105H                        | Dot Matrix Liquid Crystal Graphic Display Common Driver   |     |

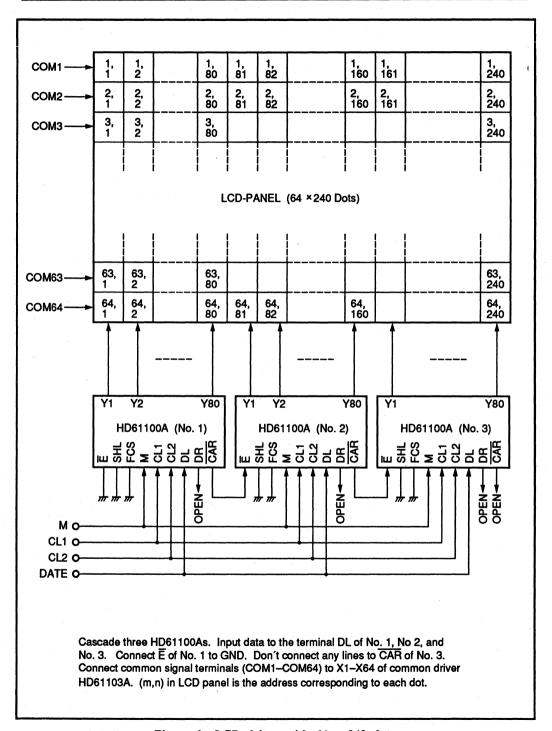

| HD61100A                        | LCD Driver with 80-Channel Output                         | 256 |

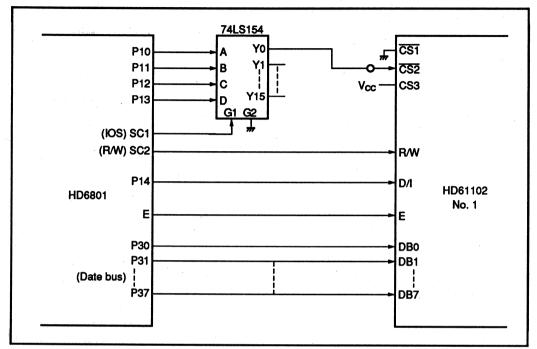

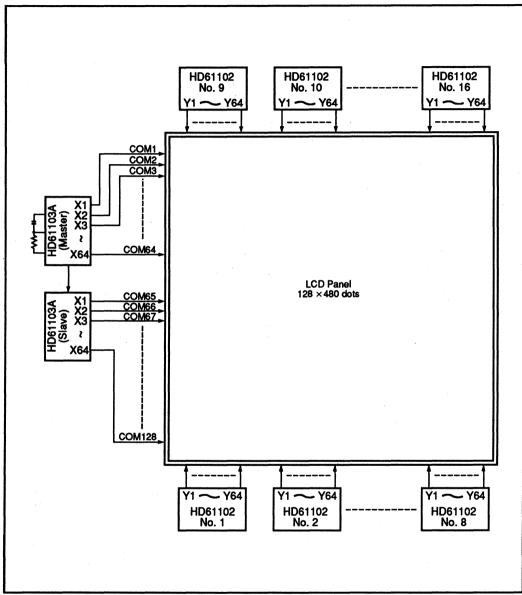

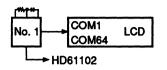

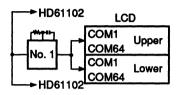

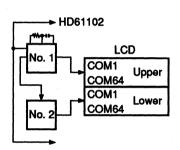

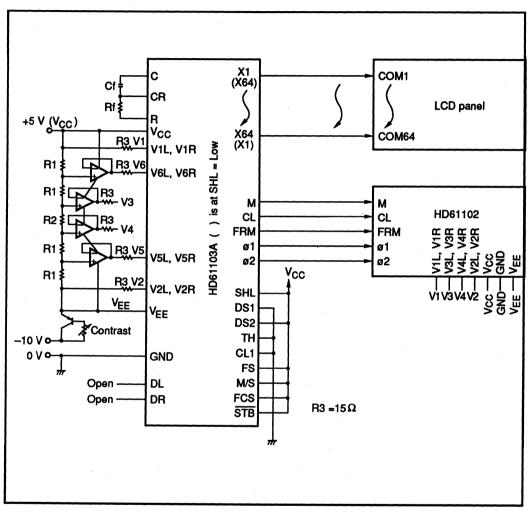

| HD61102                         | Dot Matrix Liquid Crystal Graphic Display Column Driver   | 268 |

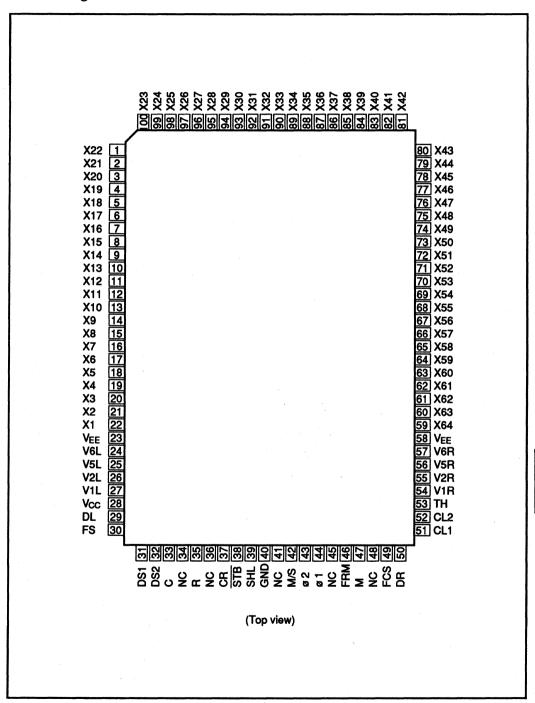

| HD61103A                        | Dot Matrix Liquid Crystal Graphic Display Common Driver   | 296 |

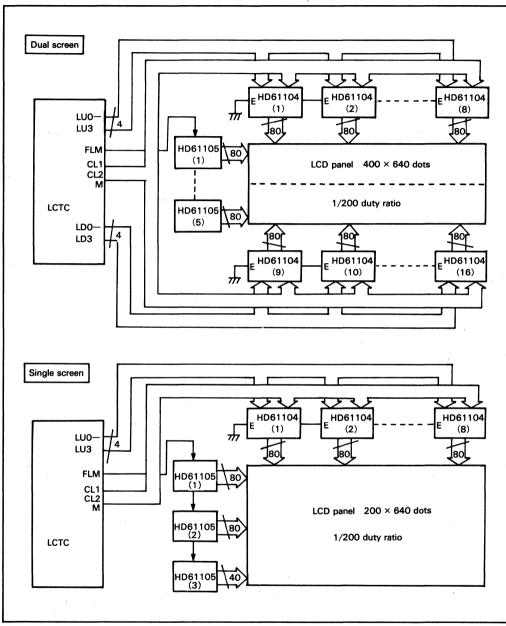

| HD61104, HD61104A               | Dot Matrix Liquid Crystal Graphic Display Column Driver   | 320 |

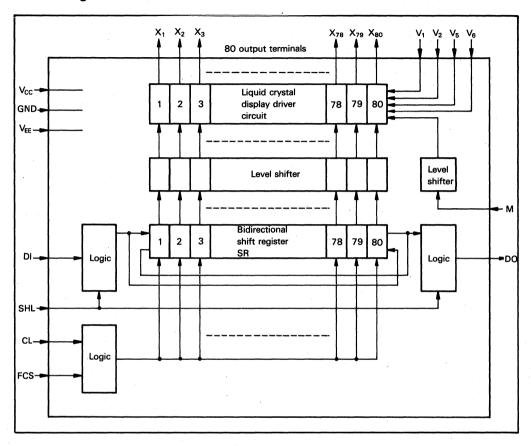

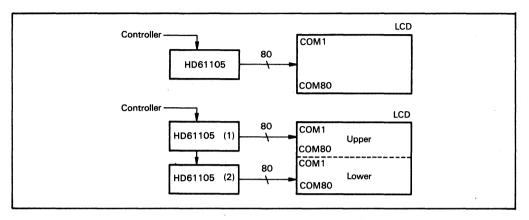

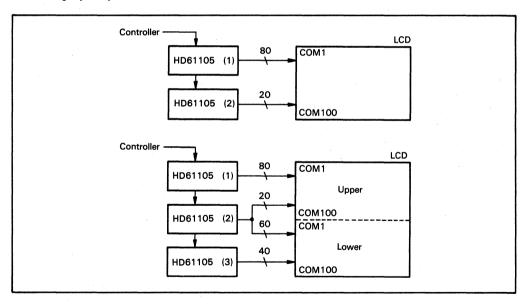

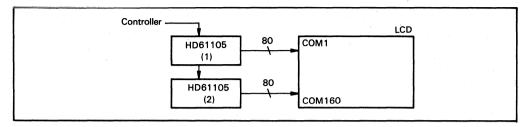

| HD61105, HD61105A               | Dot Matrix Liquid Crystal Graphic Display Common Driver   | 332 |

## CONTENTS (Continued)

| SECTION 5       | (Continued) |                                                                            |     |

|-----------------|-------------|----------------------------------------------------------------------------|-----|

| HD61200         | •           | LCD Driver with 80-Channel Output                                          | 35  |

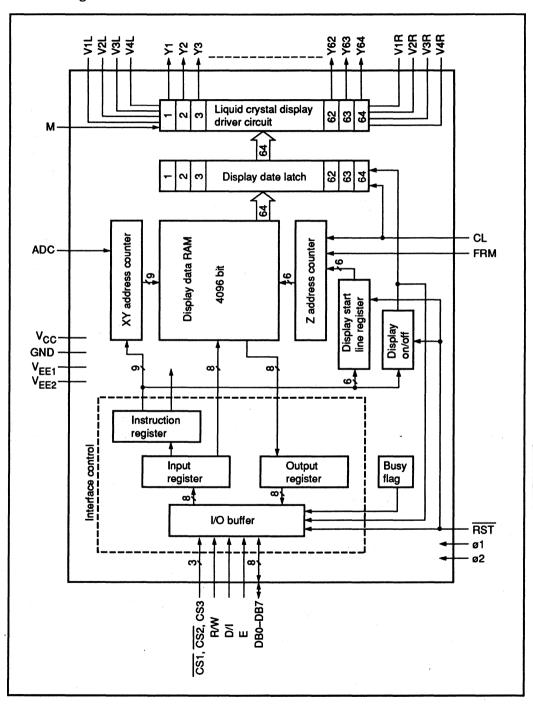

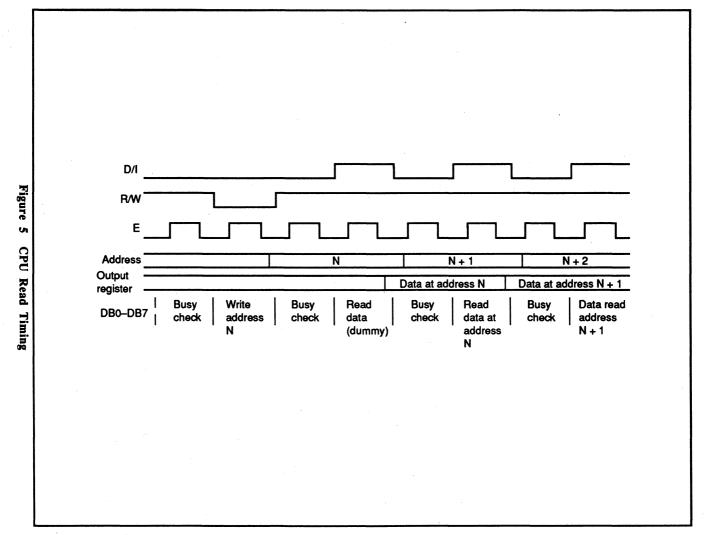

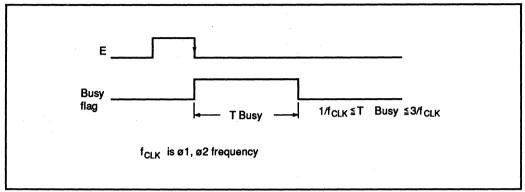

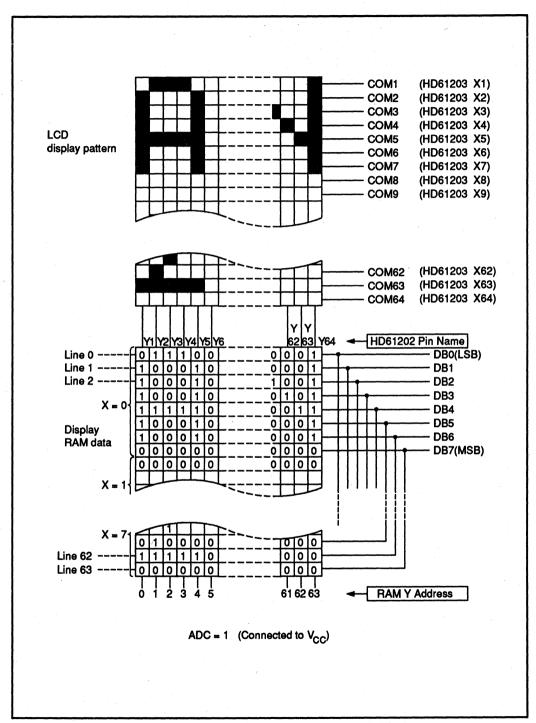

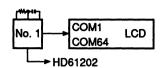

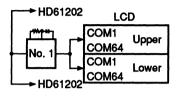

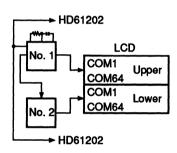

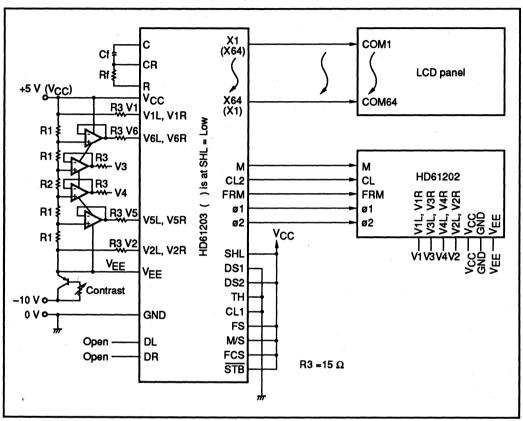

| HD61202         |             | Dot Matrix Liquid Crystal Graphic Display Column Driver                    | 36  |

| HD61203         |             | Dot Matrix Liquid Crystal Graphic Display Common Driver                    | 39  |

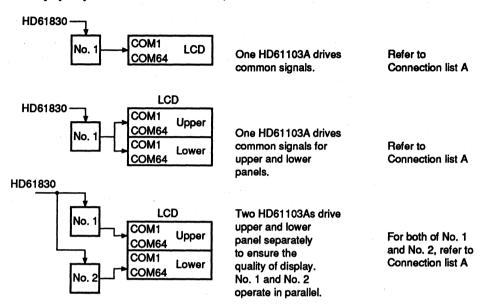

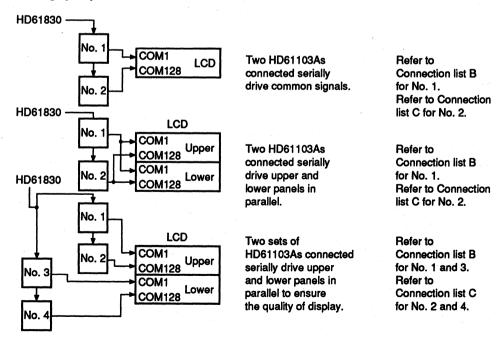

| HD61830         |             | LCTC (LCD Timing Controller)                                               |     |

| HD61830B        |             | LCTC (LCD Timing Controller)                                               | 44  |

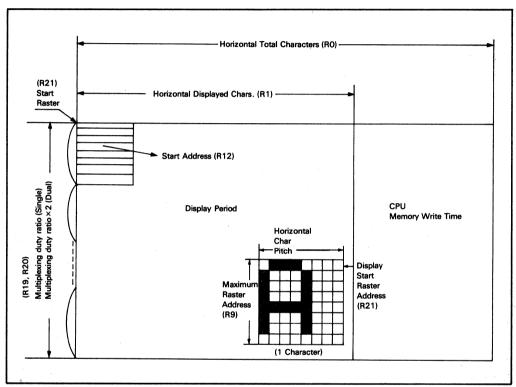

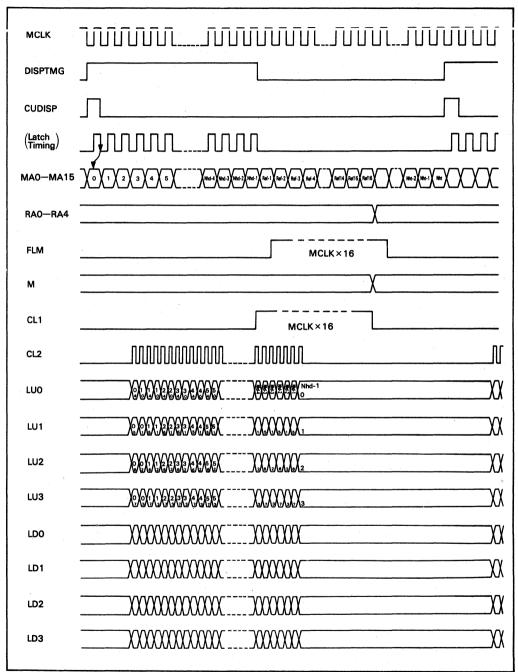

| HD63645F/H      | ID64645F    | LCD Timing Controller (LCTC)                                               | 46  |

| HD64646FS       |             | LCD Timing Controller (LCTC)                                               | 500 |

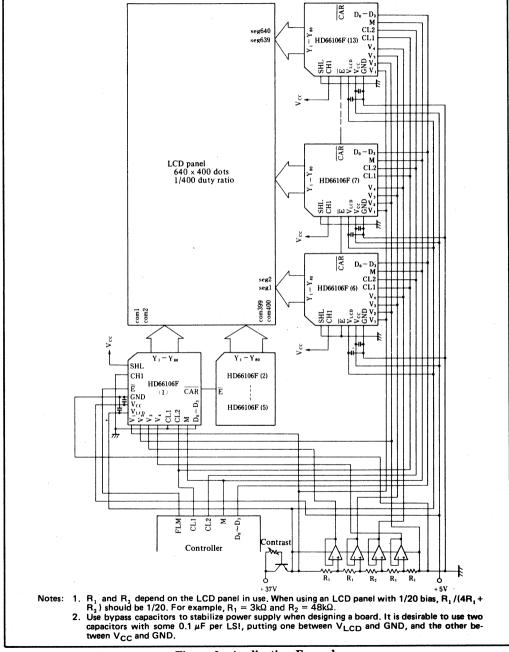

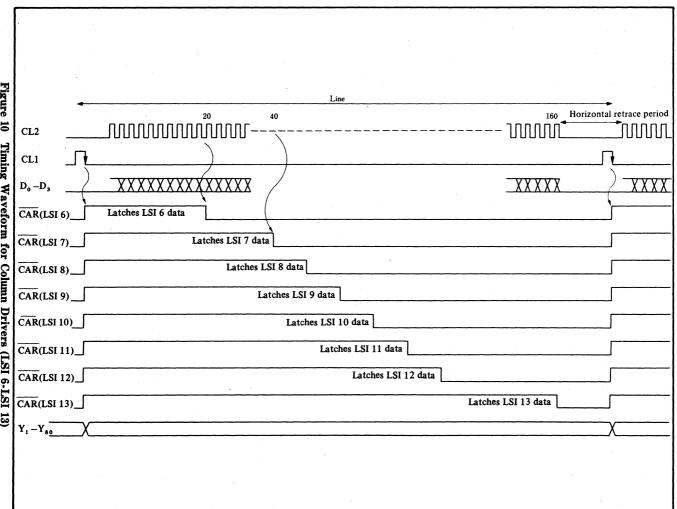

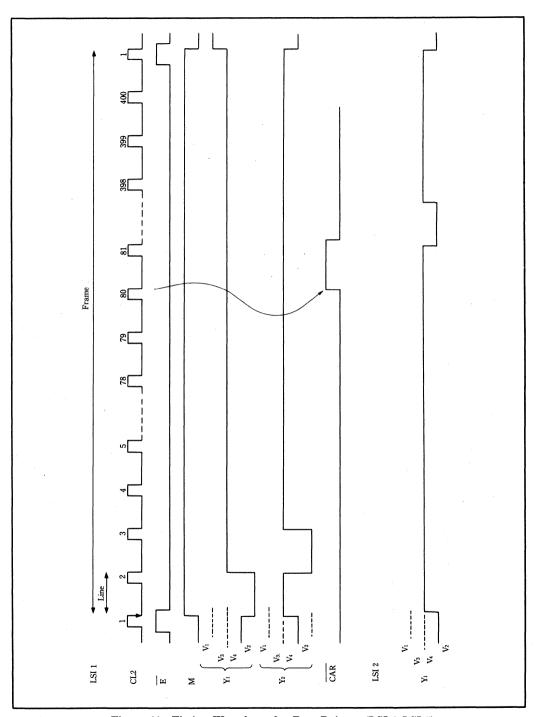

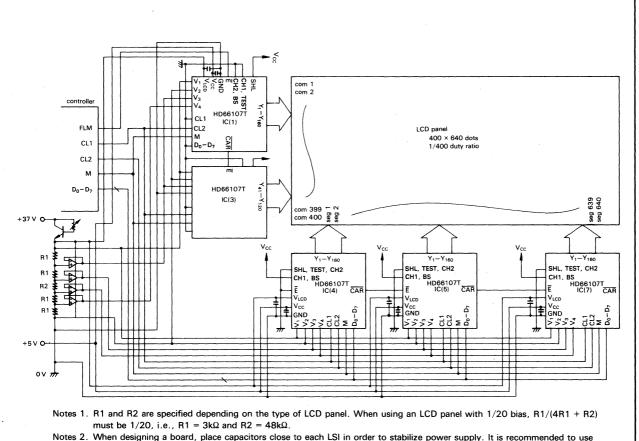

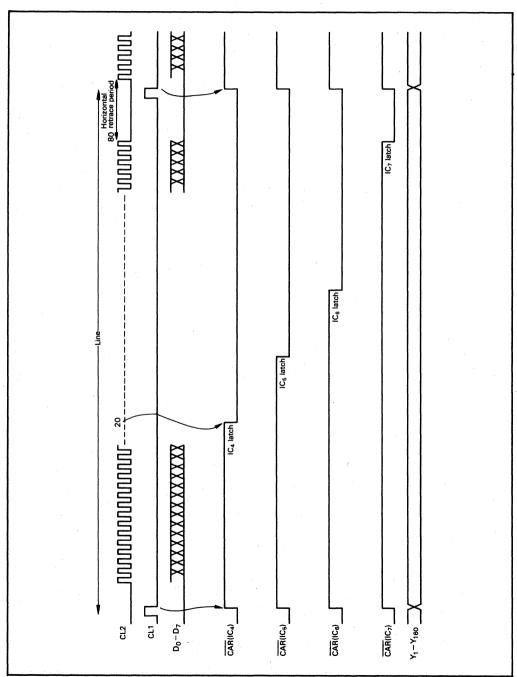

| HD66106F        |             | LCD Driver for High Voltage                                                |     |

| HD66107T        |             | LCD Driver for High Voltage                                                | 53  |

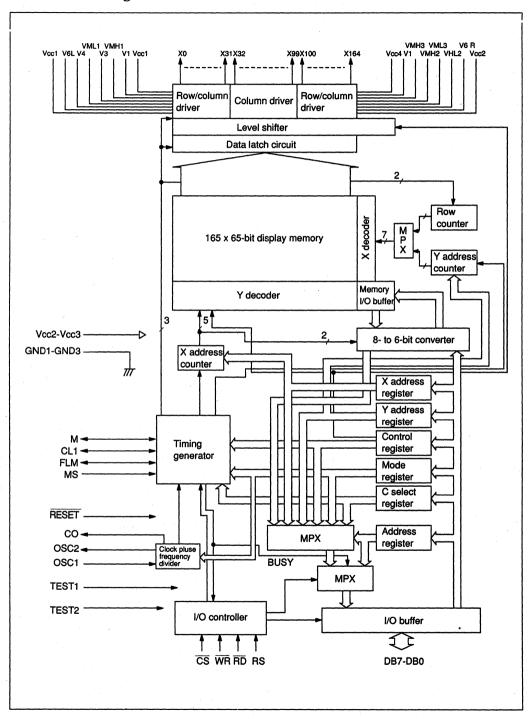

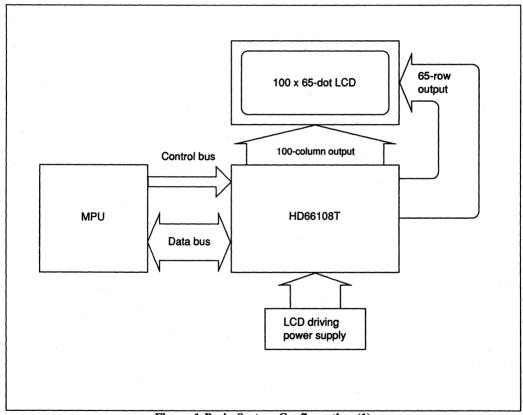

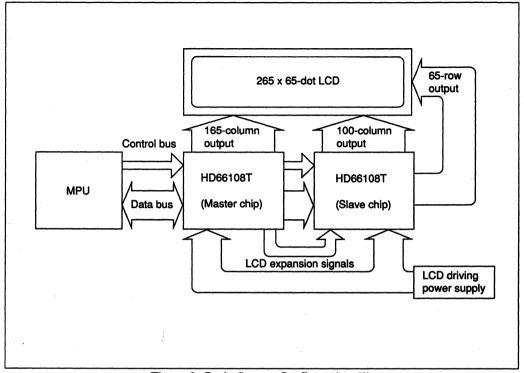

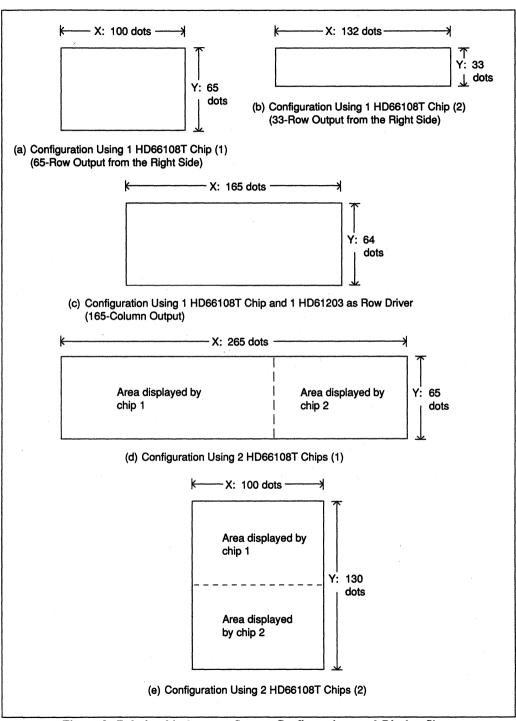

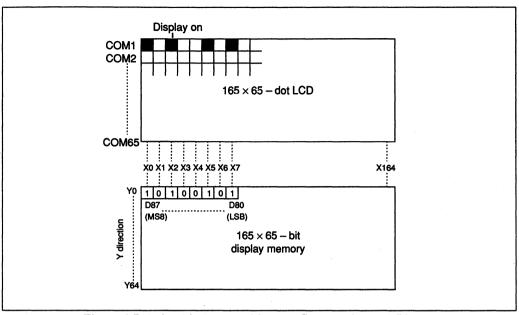

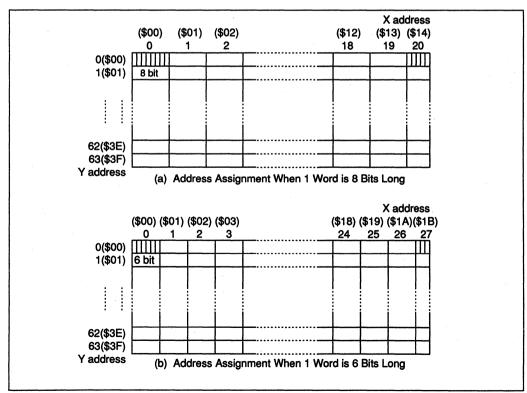

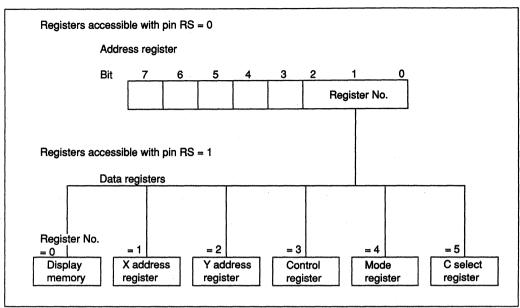

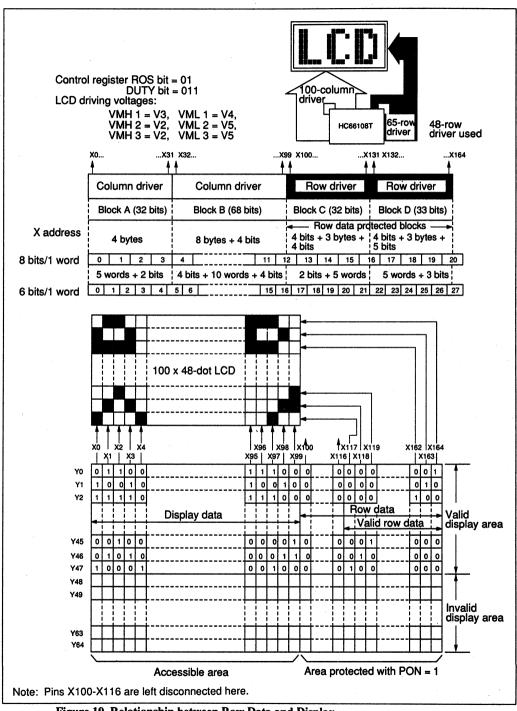

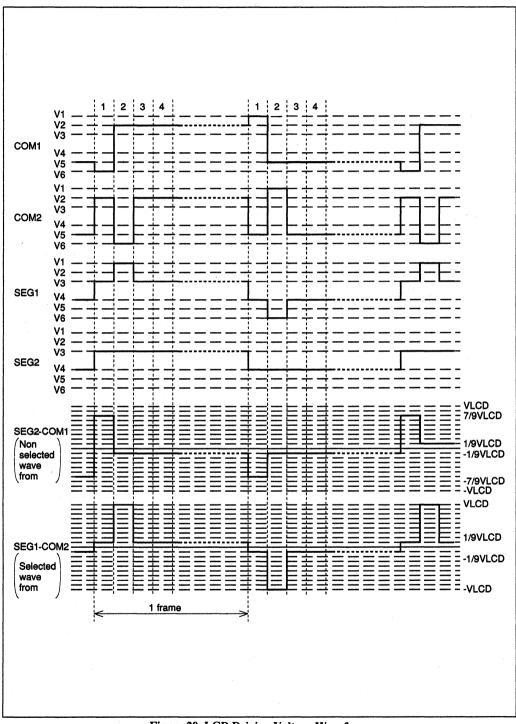

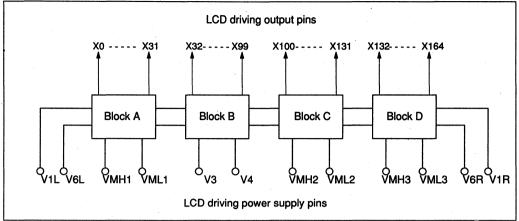

| HD66108T        |             | Ram-Provided 165-Channel LCD Driver for Liquid Crystal Dot Matrix Graphics | 55  |

| HD66840F        |             | LCD Video Interface Controller (LVIC)                                      | 60  |

| HD66841F        |             | LCD Video Interface Controller II (LVIC-II)                                | 65  |

| HD66850F        |             | Color LCD Interface Engine (CLINE)                                         |     |

| SECTION 6       | Segment Ty  | pe LCD Controller/Driver                                                   |     |

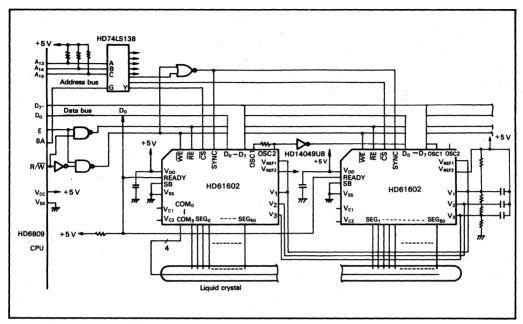

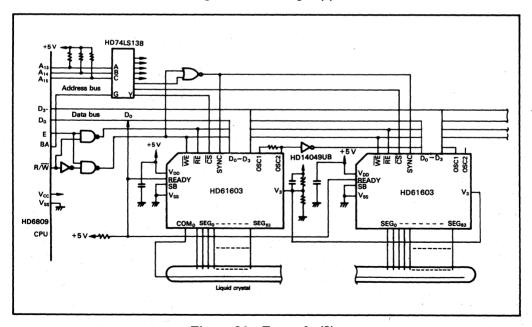

| HD61602/HI      | D61603      | Segment Type LCD Driver                                                    | 77  |

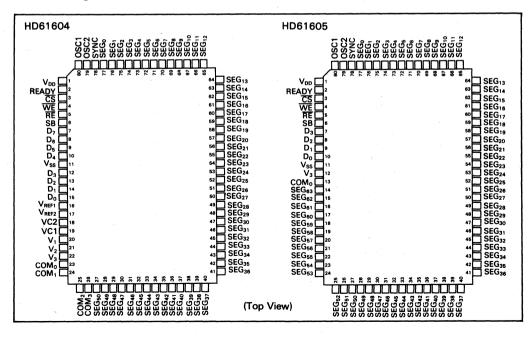

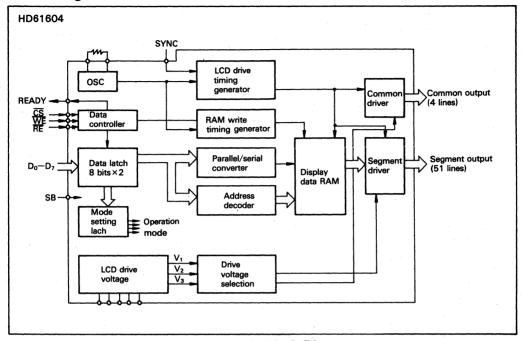

| HD61604/HI      | D61605      | Segment Type LCD Driver                                                    | 80′ |

| SECTION 7       | Special App | lication Drivers                                                           |     |

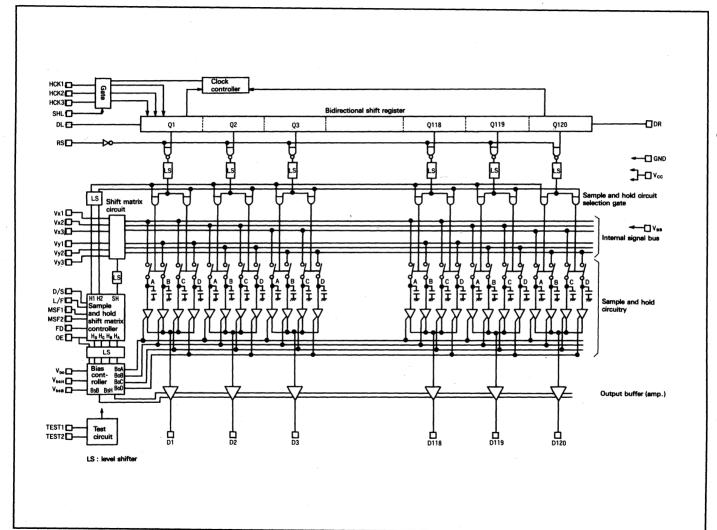

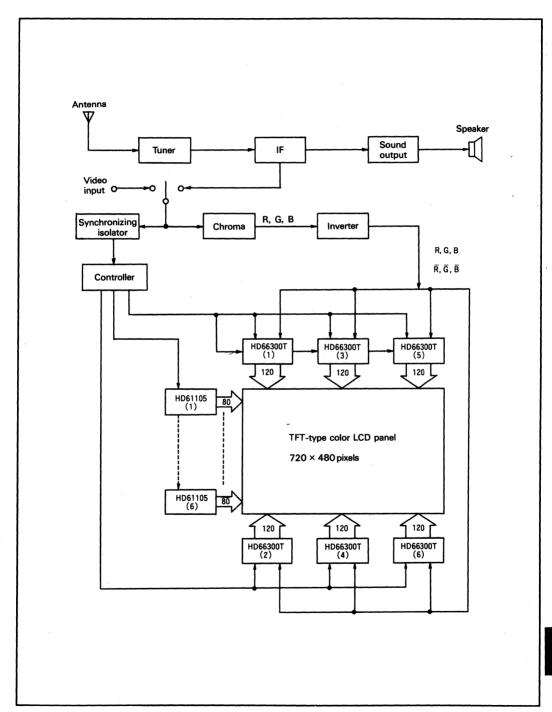

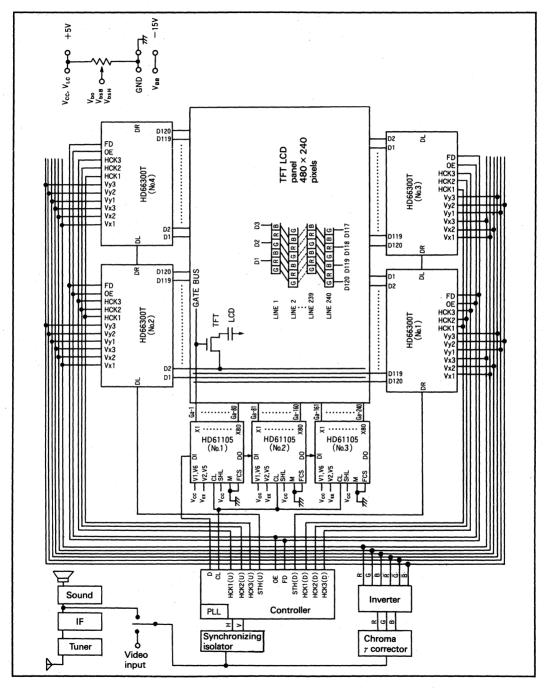

| HD66300T        | •           | Horizontal Driver for TFT-Type LCD Color TV                                | 83  |

| HD66310T        |             | TFT-Type LCD Driver for VDT                                                |     |

| SECTION 8       | New Produc  | ct Information                                                             |     |

| HD66110T        |             | Column Driver                                                              | 91  |

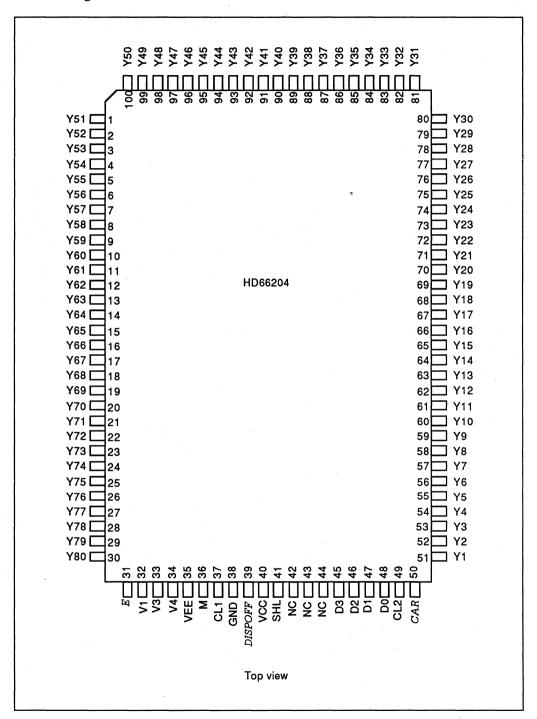

| HD66204         |             | Dot Matrix Liquid Crystal Graphic Display Column Driver                    |     |

| 11200201        |             | with 80-Channel Outputs                                                    | 93  |

| HD66205         |             | Dot Matrix Liquid Crystal Graphic Display Column Driver                    |     |

| HD66214T/F      | 4D66214TI   | with 80-Channel Outputs  Micro-TAB 80-Channel Column Driver in Micro-TCP   |     |

| HD66702LC       |             | Dot Matrix Liquid Crystal Display Controller and Driver                    |     |

| ■ HITACHI SALES | OFFICES     |                                                                            |     |

## LCD CONTROLLER/DRIVER LSI DATA BOOK

## Section One

# General Information I

- Quick Reference Guide

- Type Number Order

- Selection Guide

- Difference Between Products

#### **Quick Reference Guide**

| Туре                       |            | Column Dri  | ver          |                |            |            |                   |             |             |

|----------------------------|------------|-------------|--------------|----------------|------------|------------|-------------------|-------------|-------------|

| Type Numb                  | <b>190</b> | HD44100H    | HD66100F     | HD61100A       | HD61200    | HD61104    | HD61104A          | HD66106F    | HD66107T    |

| Power suppli               | •          | 5           | 5            | 5              | 5          | 5          | 5                 | 5           | 5           |

| Power suppl<br>LCD Drive C |            | 11          | 6            | 17             | 17         | 26         | 28                | 37          | 37          |

| Power<br>Dissipation (     | mW)        | 5           | 5            | 5              | 5          | 10         | 10                | 15          | 25          |

| Operating<br>Temperature   | ( C)       | -20 to +75* | -20 to +75*  | 1 -20 to +75*1 | -20 to +75 | -20 to +75 | -20 to +75        | -20 to +75  | -20 to +75  |

| Memory                     | ROM (bit)  | -           |              | -              | -          | -          | _                 | _           | _           |

|                            | RAM (bit)  |             | -            | _              | _          | _          | _                 | _           |             |

| LCD Driver                 | Common     | ′20         | <del>-</del> | _              | _          | _          | -                 | 80          | 160         |

|                            | Column     | 40 (20)     | 80           | 80             | 80         | 80         | 80                | 80          | 160         |

| Instruction S              | et         |             |              | -              |            | -          | _                 | _           | _           |

| Operation<br>Frequency (M  | MHz)       | 0.4         | 1            | 2.5            | 2.5        | 3.5        | 3.5               | 6           | 8           |

| Duty                       |            | Static-1/32 | Static-1/16  | Static-1/100   | 1/32-1/128 | 1/64-1/200 | 1/64-1/240        | 1/100-1/480 | 1/100-1/480 |

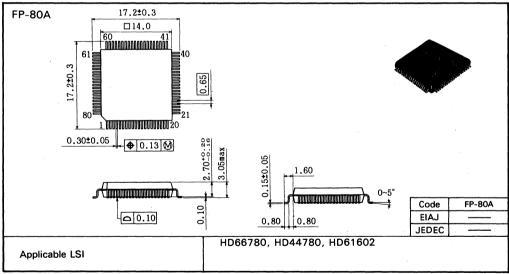

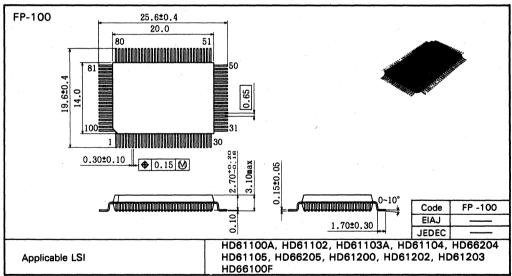

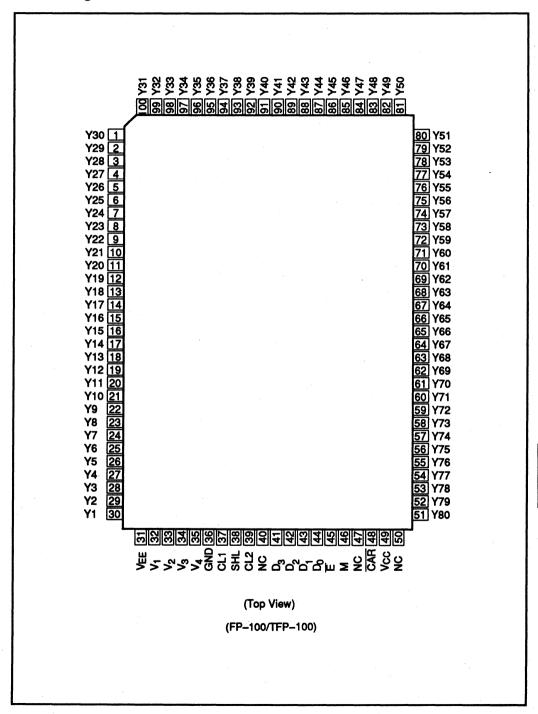

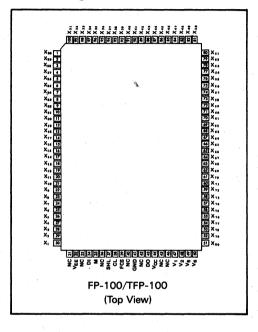

| Package                    | . *        | FP-60       | FP-100       | FP-100         | FP-100     | FP-100     | FP-100<br>TFP-100 | FP-100      | 192pin TCP  |

| Туре                          |           | Column Driv                     | er (RAM)    | Column Driver (TFT)      |                                                |            |                              |

|-------------------------------|-----------|---------------------------------|-------------|--------------------------|------------------------------------------------|------------|------------------------------|

| Type Numb                     | ner '     | HD44102CH                       | HD61102     | HD61202                  | HD66108T                                       | HD66300T   | HD66310T                     |

| Power suppl<br>internal circu | •         | 5                               | 5           | 5                        | 5                                              | 5          | 5                            |

| Power suppl<br>LCD Drive C    | •         | 11                              | 15.5        | 17                       | 15                                             | 15         | 23                           |

| Power<br>Dissipation (        | mW)       | 5                               | 5           | 5                        | 5                                              | 160        | 100                          |

| Operating<br>Temperature      | (°C)      | -20 to +75                      | -20 to +75  | -20 to +75               | -20 to +75                                     | -20 to +75 | -20 to +75*2<br>(-20 to +65) |

| Memory                        | ROM (bit) | -                               | _           | -                        | _                                              | -          | _                            |

|                               | RAM (bit) | 200×8                           | 512×8       | 512×8                    | 165×65                                         | _          | _                            |

| LCD Driver                    | Common    | -                               | _           | -                        | 0~65                                           | 120        | 160                          |

|                               | Column    | 50                              | 64          | 64                       | 100~165                                        | -          | ****                         |

| Instruction S                 | et        | 6                               | 7           | 7                        | 7                                              | _          | _                            |

| Operation<br>Frequency (f     | MHz)      | 0.28                            | 0.4         | 0.4                      | 4                                              | 4.8        | 12/15                        |

| Duty                          |           | 1/8,1/12,<br>1/16,1/24,<br>1/32 | Static-1/64 | 1/48,1/64,<br>1/96,1/128 | 1/32,1/34,<br>1/36,1/48,<br>1/50,1/64,<br>1/66 | -          |                              |

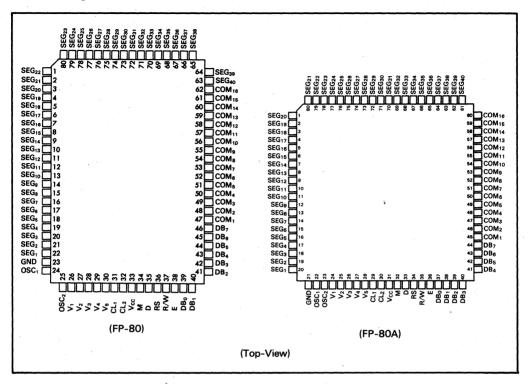

| Package                       |           | FP-80                           | FP-100      | FP-100                   | 208pin TCP                                     | 156pin TCP | 236pin TCP                   |

<sup>\*1 -40</sup> to +85°C (Special request). Please contact Hitachi agents. \*2 -20 to +75°C in 12 MHz Version, -20 to +65°C in 15 MHz Version.

<sup>\*3</sup> Under development

#### Quick Reference Guide

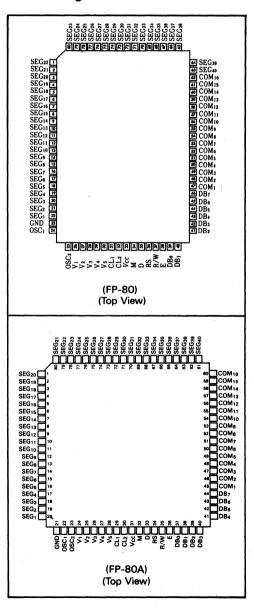

| Туре                     |           | Segment Display                          |              |                        |              |  |  |  |

|--------------------------|-----------|------------------------------------------|--------------|------------------------|--------------|--|--|--|

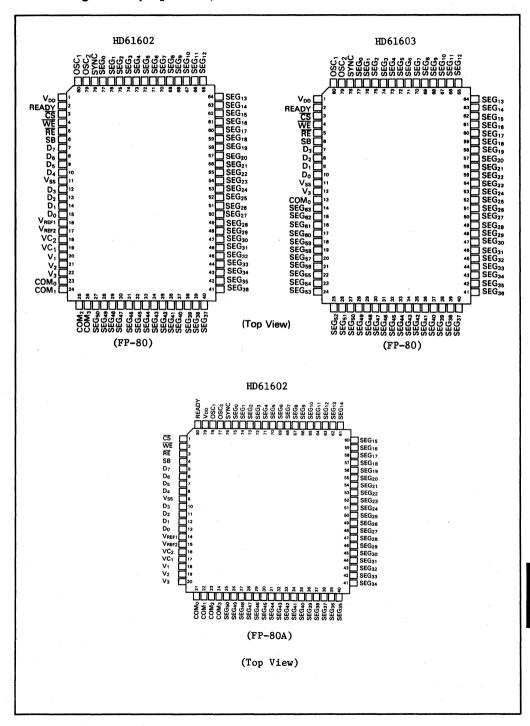

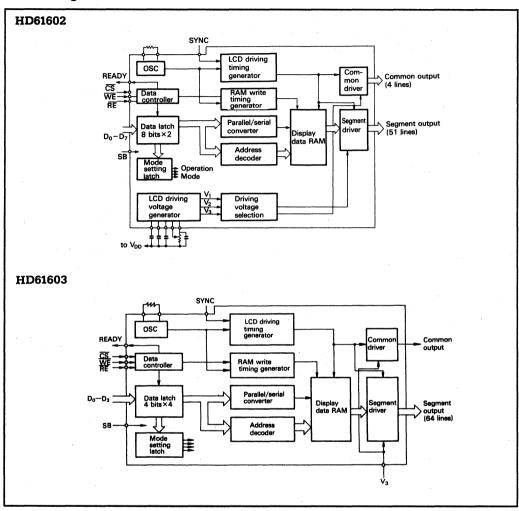

| Type Numi                | per       | HD61602                                  | HD61603      | HD61604                | HD61605      |  |  |  |

| Power suppl              | •         | 3 to 5                                   | 3 to 5       | 3 to 5                 | 3 to 5       |  |  |  |

| Power suppl              | •         | 5                                        | 5            | 5                      | 5            |  |  |  |

| Power<br>Dissipation (   | mW)       | 0.5                                      | 0.5          | 0.5                    | 0.5          |  |  |  |

| Operating<br>Temperature | (°C)      | -20 to +75*1                             | -20 to +75*1 | -20 to +75*1           | -20 to +75*1 |  |  |  |

| Memory                   | ROM (bit) | _                                        | <del>-</del> |                        | _            |  |  |  |

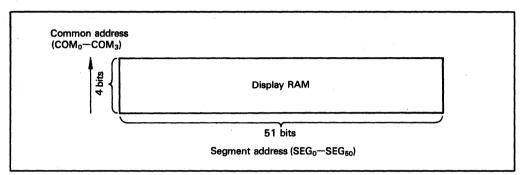

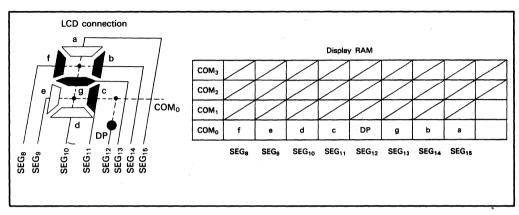

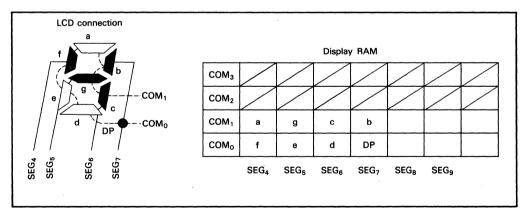

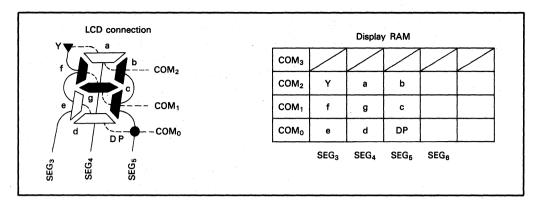

|                          | RAM (bit) | 204                                      | 64           | 204                    | 64           |  |  |  |

| LCD Driver               | Common    | 4                                        | 1            | 4                      | 1            |  |  |  |

|                          | Column    | 51                                       | 64           | 51                     | 64           |  |  |  |

| Instruction S            | et        | 4                                        | 4            | 4                      | 4            |  |  |  |

| Operation<br>Frequency ( | MHz)      | 0.52                                     | 0.52         | 0.52                   | 0.52         |  |  |  |

| Duty                     |           | Static, 1/2,<br>1/3, 1/4                 | Static       | Static,1/2,<br>1/3,1/4 | Static       |  |  |  |

| Package                  |           | FP-80,<br>FP-80A<br>TFP-80* <sup>2</sup> | FP-80        | FP-80                  | FP-80        |  |  |  |

<sup>\*1 -40</sup> to +85°C (Special request). Please contact Hitachi agents.

<sup>\*2</sup> Under development

| Туре                       |           | Common D                       | river                   |                      |              |            |                   |

|----------------------------|-----------|--------------------------------|-------------------------|----------------------|--------------|------------|-------------------|

| Type Numb                  | per       | HD44103CH                      | HD44105H                | HD61103A             | HD61203      | HD61105    | HD61105A          |

| Power supplinternal circu  | •         | 5                              | 5                       | 5                    | 5            | 5          | 5                 |

| Power suppl<br>LCD Drive C | •         | 11                             | 11                      | 17                   | 17           | 26         | 28                |

| Power<br>Dissipation (     | mW)       | 4.4                            | 4.4                     | 5                    | 5            | 5          | 5                 |

| Operating<br>Temperature   | ( °C)     | -20 to +75                     | -20 to +75              | -20 to +75           | -20 to +75   | -20 to +75 | -20 to +75        |

| Memory                     | ROM (bit) | _                              | -                       | - ,                  | -            | -          | -                 |

|                            | RAM (bit) | _                              |                         | _                    | -<br>-       | -          |                   |

| LCD Driver                 | Common    | 20                             | 32                      | 64                   | 64           | 80         | 80                |

|                            | Column    | -                              | -                       | -                    | <del>-</del> | _          | -                 |

| Instruction S              | et        | -                              | _                       |                      |              |            | _                 |

| Operation<br>Frequency (!  | MHz)      | 1                              | 1                       | 2.5                  | 2.5          | 0.1        | 0.1               |

| Duty                       |           | 1/8,1/12,<br>1/16,1/24<br>1/32 | 1/8,1/12,<br>,1/32,1/48 | Static-1/10,<br>1/64 | 1/32-1/128   | 1/64-1/200 | 1/64-1/240        |

| Package                    |           | FP-60                          | FP-60                   | FP-100               | FP-100       | FP-100     | FP-100<br>TFP-100 |

<sup>\*1 -40</sup> to +85°C (Special request). Please contact Hitachi agents.

<sup>\*2</sup> Under development

| Туре                       |           | Character Display |                              |                      | Graphic Display |                 |                                           |                  |                  |

|----------------------------|-----------|-------------------|------------------------------|----------------------|-----------------|-----------------|-------------------------------------------|------------------|------------------|

| Type Numb                  | )er       | HD43160AH         | HD44780<br>(LCD-II)          | HD66780<br>(LCD-IIA) | HD61830         | HD61830B        | HD63645F<br>HD64646F<br>HD64646FS<br>LCTC |                  | HD66850<br>CLINE |

| Power supplinternal circu  |           | 5                 | 5                            | 5                    | 5               | 5               | 5                                         | 5                | 5                |

| Power suppl<br>LCD Drive C | •         | _                 | 11                           | 5                    | _               | -               | _                                         | -                | _                |

| Power<br>Dissipation (     | mW)       | 10                | 2                            | 2                    | 30              | 50              | 50                                        | 250              | 500              |

| Operating<br>Temperature   | (°C)      | -20 to +75        | -20 to +75*1                 | -20 to +75           | -20 to +75      | -20 to +75*1    | -20 to +75                                | -20 to +75       | -20 to +75       |

| Memory                     | ROM (bit) | 6420              | 7200                         | 12000                | 7360            | 7360            | _                                         | -                | _                |

|                            | RAM (bit) | 80×8              | 80×8,<br>64×8                | 80×8,<br>64×8        | _               | _               | _                                         | _                | 9762             |

| LCD Driver                 | Common    | _                 | 16                           | 16                   | -               | _               | _                                         | _                | _                |

|                            | Column    | · <del>-</del>    | 40                           | 40                   | _               | _               | -                                         | -                | -                |

| Instruction S              | et        | 6                 | 11                           | 11                   | 12              | 12              | 15                                        | 16/24            | 63               |

| Operation<br>Frequency (M  | MHz)      | 0.25/0.375        | 0.25                         | 0.25                 | 1.1             | 2.4             | 10                                        | 30               | 32               |

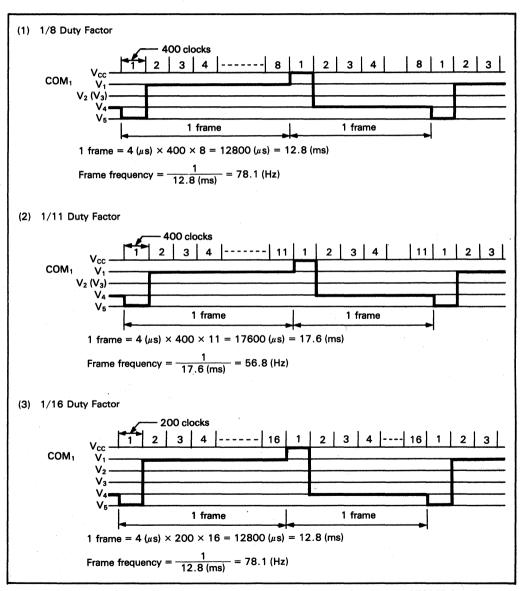

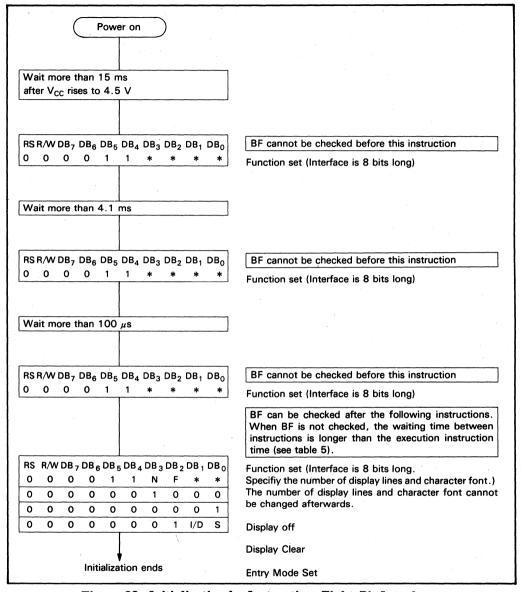

| Duty                       |           | 1/8,1/12,<br>1/16 | 1/8,1/11,<br>1/16            | 1/8,1/11,<br>1/16    | Static<br>1/128 | Static<br>1/128 | Static<br>1/512                           | Static<br>1/1024 | 1/480            |

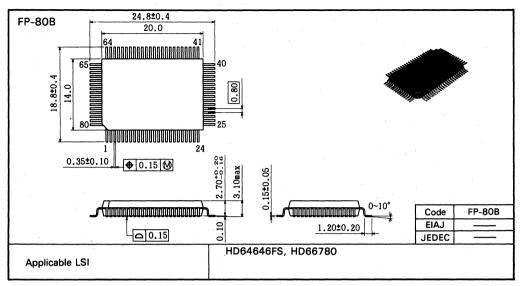

| Package                    |           | FP-54             | FP-80,<br>FP-80A<br>TFP-80*2 | FP-80A<br>FP-80B     | FP-60           | FP-60           | FP-80,<br>FP-80B                          | FP-100A          | FP-136           |

<sup>\*1 -40</sup> to +85°C (Special request). Please contact Hitachi agents.

<sup>\*2</sup> Under development

#### **Type Number Order**

| Туре             | Function                                                | Reference Page |

|------------------|---------------------------------------------------------|----------------|

| HD43160AH        | LCD Controller                                          | 100            |

| HD44100H         | LCD Driver with 40 Channel Output                       | 77             |

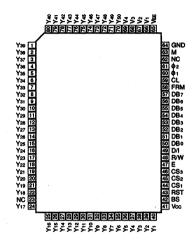

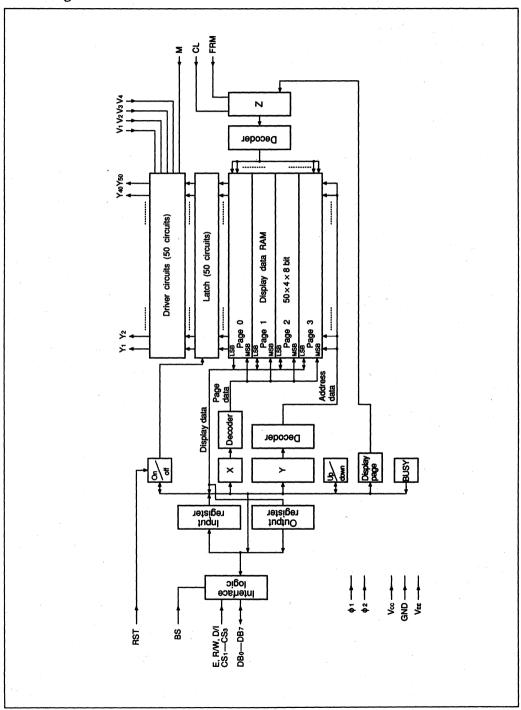

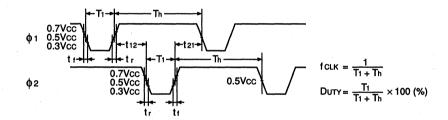

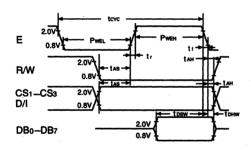

| HD44102CH        | LCD Column Driver with 50 Channel Output                | 216            |

| HD44103CH        | LCD Common Driver with 20 Channel Output                | 239            |

| HD44105H         | LCD Common Driver with 32 Channel Output                | 247            |

| HD44780 LCD-II   | LCD Controller/Driver                                   | 114            |

| HD6110A          | LCD Column Driver with 80 Channel Output                | 256            |

| HD61102          | LCD Column Driver with 64 Channel Output                | 268            |

| HD61103A         | LCD Common Driver with 64 Channel Output                | 296            |

| HD61104          | LCD Column Driver with 80 Channel Output                | 320            |

| HD61104A         | LCD Column Driver with 80 Channel Output                | 320            |

| HD61105          | LCD Common Driver with 80 Channel Output                | 332            |

| HD61105A         | LCD Common Driver with 80 Channel Output                | 332            |

| HD61200          | LCD Column Driver with 80 Channel Output                | 350            |

| HD61202          | LCD Column Driver with 64 Channel Output                | 363            |

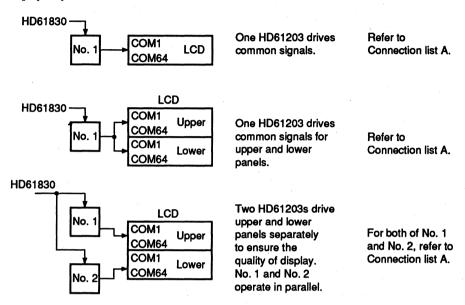

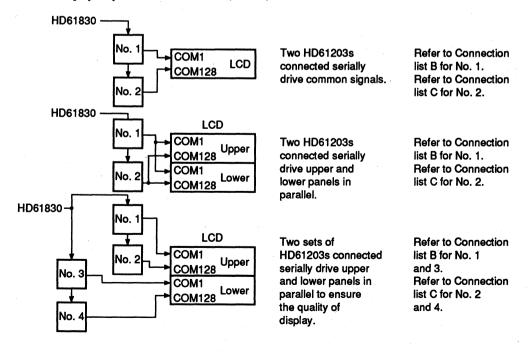

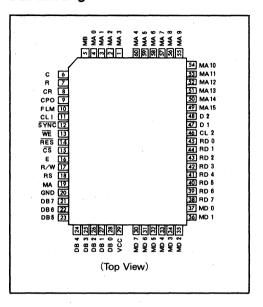

| HD61203          | LCD Common Driver with 64 Channel Output                | 394            |

| HD61602          | Segment Display Type LCD Driver                         | 778            |

| HD61603          | Segment Display Type LCD Driver                         | 778            |

| HD61604          | Segment Display Type LCD Driver                         | 807            |

| HD61605          | Segment Display Type LCD Driver                         | 807            |

| HD61830 LCTC     | LCD Timing Controller                                   | 413            |

| HD61830B LCTC    | LCD Timing Controller                                   | 443            |

| HD63645F LCTC    | LCD Timing Controller                                   | 466            |

| HD64645F LCTC    | LCD Timing Controller                                   | 466            |

| HD64646FS LCTC   | LCD Timing Controller                                   | 506            |

| HD66100F         | LCD Driver with 80 Channel Output                       | 87             |

| HD66106F         | LCD Column/Common Driver with 80 Channel Output         | 516            |

| HD66107T         | LCD Column/Common Driver with 160 Channel Output        | 531            |

| HD66108T         | Graphic LCD Controller/Driver                           | 551            |

| HD66110T         | Column Driver                                           | 916            |

| HD66204          | LCD Column Driver with 80 Channel Output                | 931            |

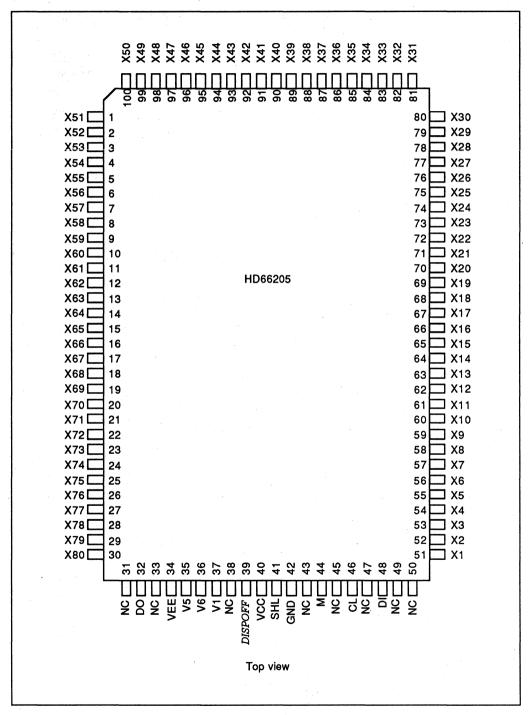

| HD66205          | LCD Common Driver with 80 Channel Output                | 945            |

| HD66214T         | Micro-TAB 80-Channel Column Driver                      | 959            |

| HD66214TL        | Micro-TAB 80-Channel Column Driver                      | 959            |

| HD66300T         | TFT Alalog Column Driver                                | 833            |

| HD66310T         | TFT Digital Column Driver                               | 894            |

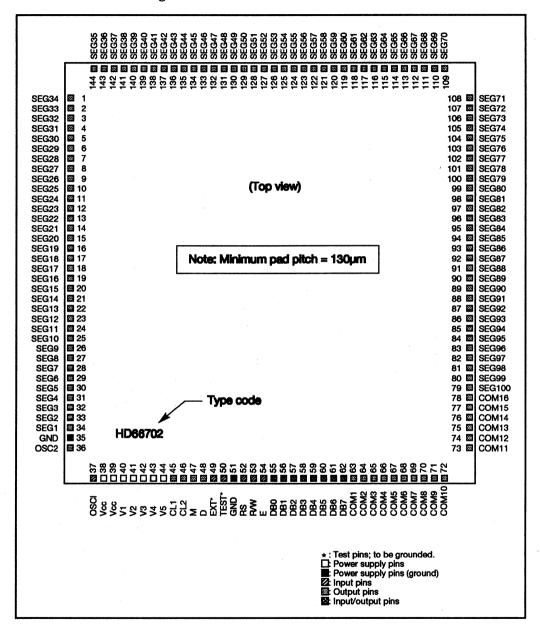

| HD66702 LCD-II   | Dot Matrix Liquid Crystal Display Controller and Driver | 975            |

| HD66780 LCD-IIA  | LCD Controller/Driver                                   | 167            |

| HD66840F LVIC    | LCD Video Interface Controller                          | 604            |

| HD66841F LVIC-II | LCD Video Interface Controller                          | 652            |

| HD66850F CLINE   | Color LCD Interface Engine                              | 708            |

|                  |                                                         |                |

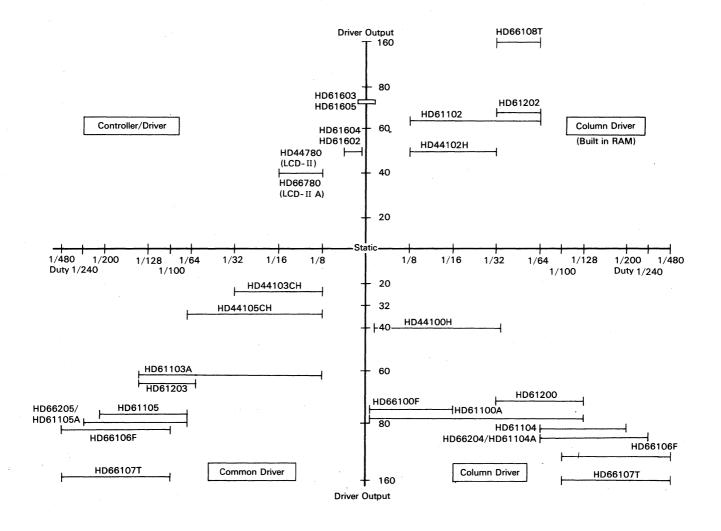

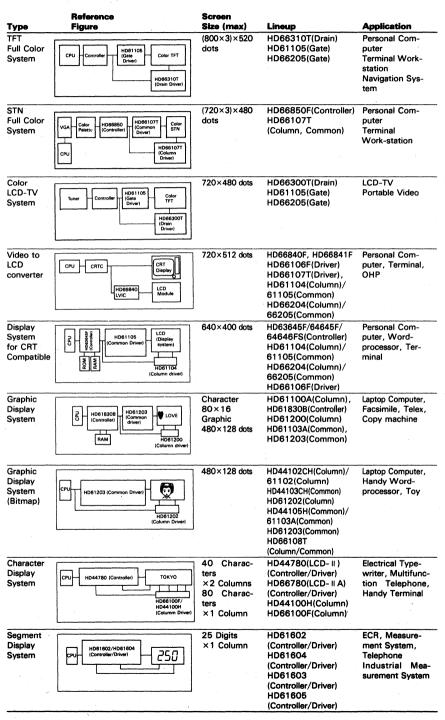

# **Selection Guide**

#### Selection Guide

#### Hitachi LCD Driver System

#### Application

#### Character and Graphic Display

1 character= $7 \times 8$  dot (15  $\times 7$  dot + cursor)

| Character<br>Line | 8 | 16 | 20 | 24                                                                         | 32           | 40         | Over 80 |

|-------------------|---|----|----|----------------------------------------------------------------------------|--------------|------------|---------|

| 1                 |   |    |    |                                                                            | HD66100F     |            |         |

| 2                 |   |    |    |                                                                            | HD00100F     |            |         |

| 3                 |   |    |    |                                                                            | UD44400U     |            |         |

| 4                 |   |    |    |                                                                            | HD44100H     |            |         |

| 6 to 8            |   |    |    | -                                                                          |              |            |         |

| 12 to 15          |   |    |    | HD61200 (                                                                  | Column) + HI | D61203 (Co | ommon)  |

| 16 to 25          |   |    |    | HD61104 (Column) + HD61105 (Common)<br>HD66204 (Column) + HD66205 (Common) |              |            |         |

| 26 to 50          |   |    |    |                                                                            | HD66106F, I  |            | mmon)   |

#### **Graphic Display**

| Horizontal<br>Vertical | 48 | 96                                                                         | 120        | 180          | 240         | 480   | Over 640 |  |

|------------------------|----|----------------------------------------------------------------------------|------------|--------------|-------------|-------|----------|--|

| 16                     |    |                                                                            |            |              |             |       |          |  |

| 32                     |    |                                                                            | HD61202 (C | Column) + HD | 061203 (Com | nmon) |          |  |

| 48                     |    |                                                                            | -          |              |             |       |          |  |

| 64                     |    |                                                                            |            |              |             |       |          |  |

| 128                    |    |                                                                            |            |              |             |       |          |  |

| 400                    |    | HD61104 (Column) + HD61105 (Common)<br>HD66204 (Column) + HD66205 (Common) |            |              |             |       |          |  |

| Over 400               |    |                                                                            |            | HD66106F, H  | HD66107T    |       |          |  |

Note: Applications on this page are only examples, and this combination of devices is not the best.

#### **Differences Between Products**

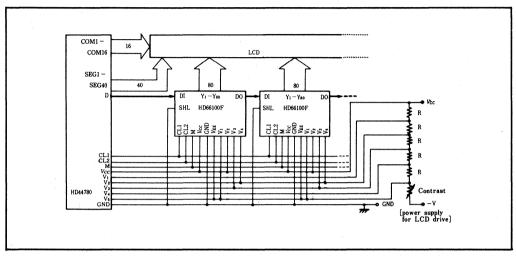

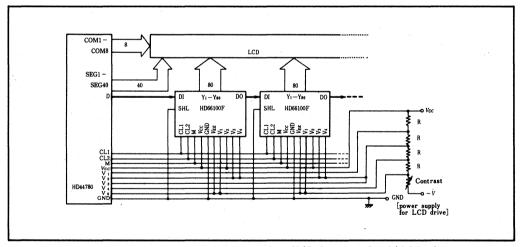

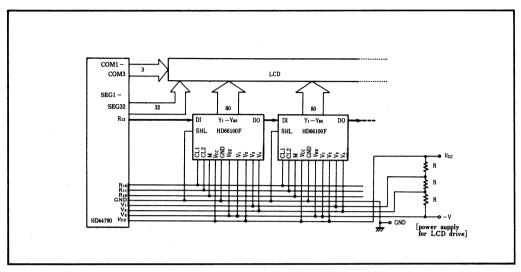

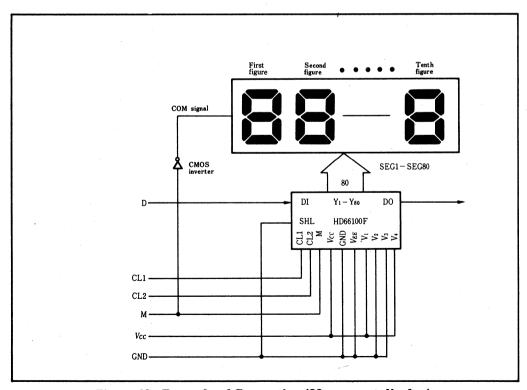

#### 1. HD66100F and HD44100H

|                                     | HD66100F            | HD44100H           |

|-------------------------------------|---------------------|--------------------|

| LCD drive circuits                  | 80                  | 20×2               |

| Power supply for internal logic (V) | 3 to 6              | 4.5 to 11          |

| Display duty                        | Static to 1/16      | Static to 1/32     |

| Package                             | 100 pin plastic QFP | 60 pin plastic QFP |

#### 2. HD61100A and HD61200

|                                                   |                      | HD61100A                                         | HD61200                |

|---------------------------------------------------|----------------------|--------------------------------------------------|------------------------|

| LCD drive circuits                                | common               | -                                                |                        |

|                                                   | column               | 80                                               | 80                     |

| Display duty                                      |                      | static to 1/128                                  | 1/32 to 1/128          |

| Power supply for LC                               | D drive circuits (V) | 0 to 17                                          | 8 to 17                |

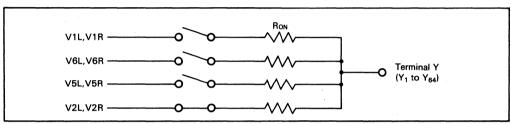

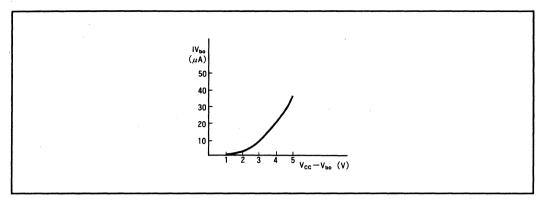

| Power supply limits of LCD driver circuit voltage |                      | V <sub>CC</sub> to V <sub>EE</sub><br>(no limit) | shown in figures below |

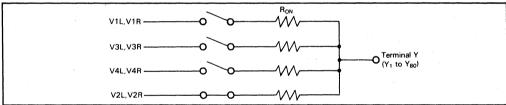

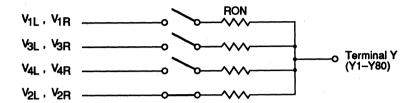

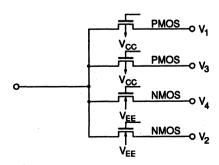

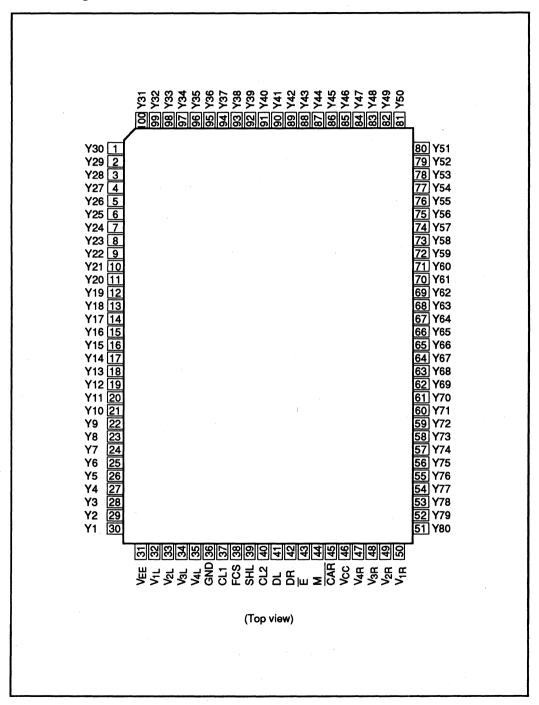

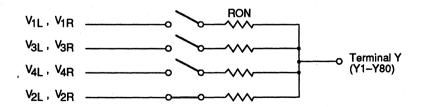

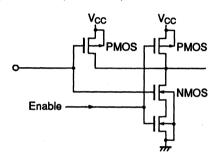

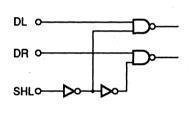

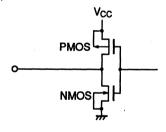

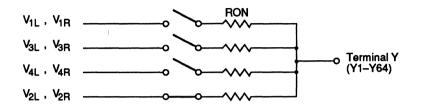

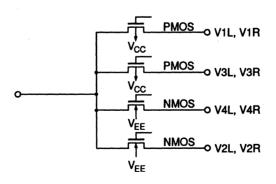

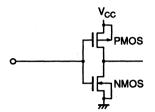

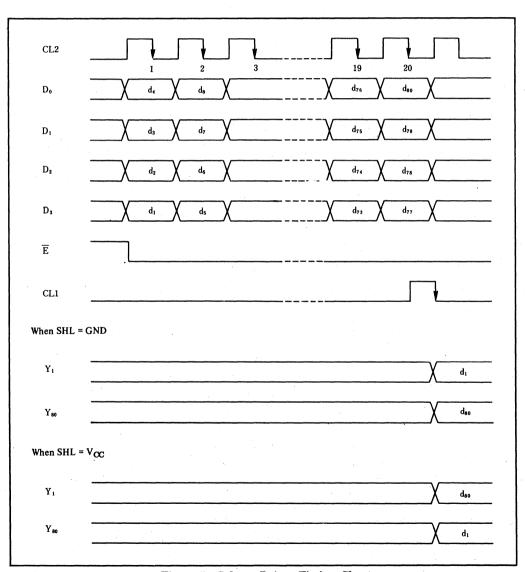

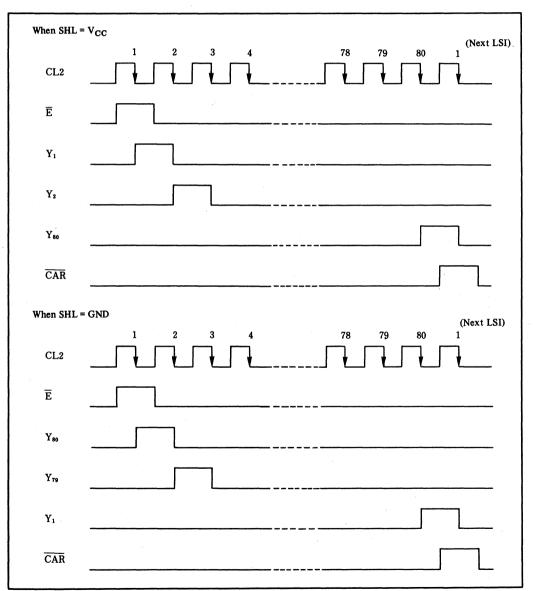

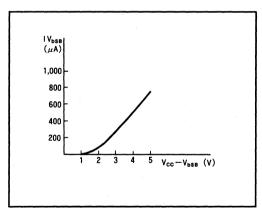

Resistance between terminal Y and terminal V (one of V1L, V1R, V2L, V2R, V3L, V3R, V4L, and V4R) when load current flows through one of the terminals  $Y_1$  to  $Y_{80}$  is specified

under the following conditions:

$V_{CC}-V_{EE}=17V$

$V1L = V1R, V3L = V3R = V_{CC} - 2/7 (V_{CC} - V_{EE})$

$V2L=V2R, V4L=V4R=V_{EE}+2/7 (V_{CC}-V_{EE})$

Figure 1 Resistance between Y ard V Terminals

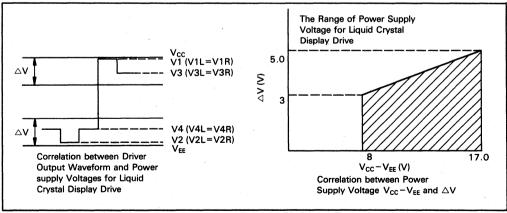

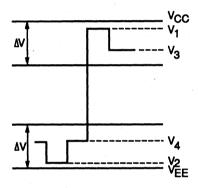

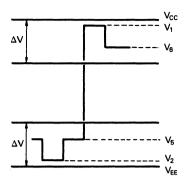

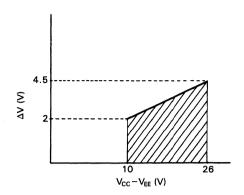

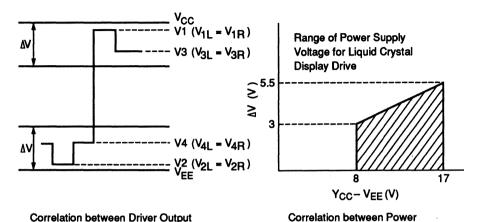

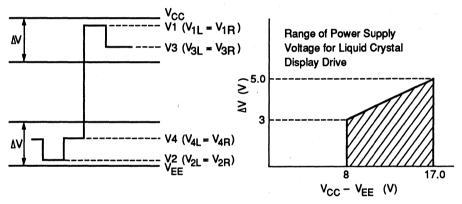

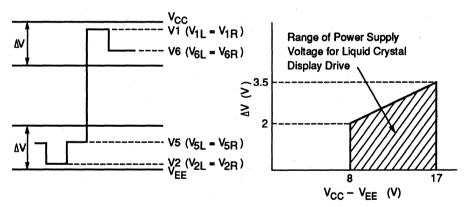

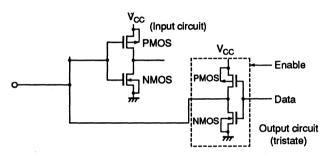

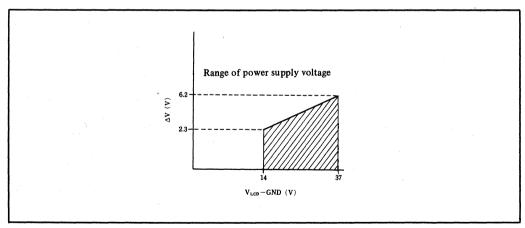

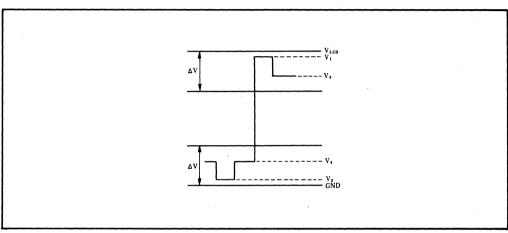

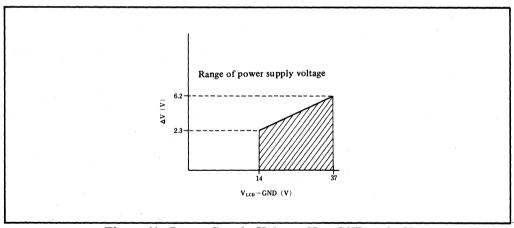

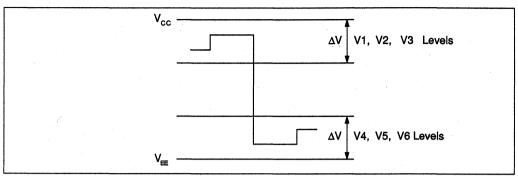

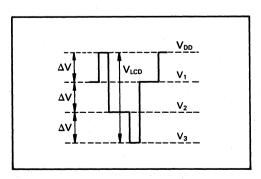

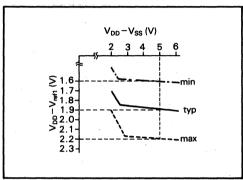

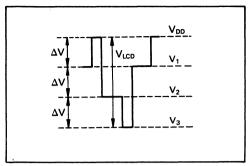

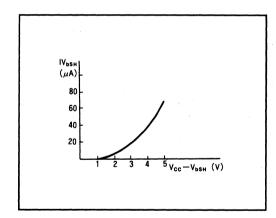

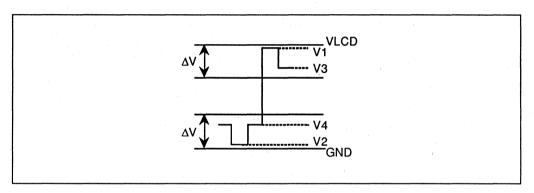

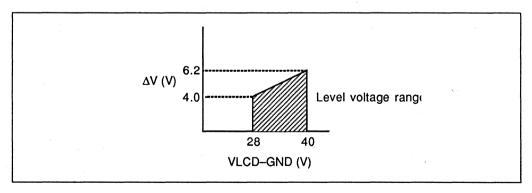

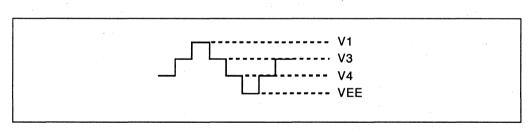

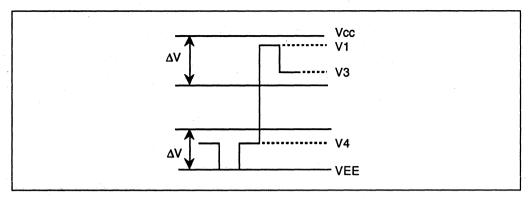

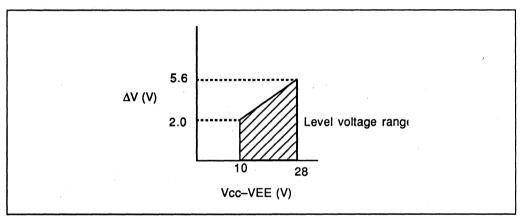

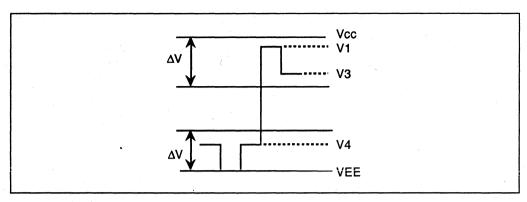

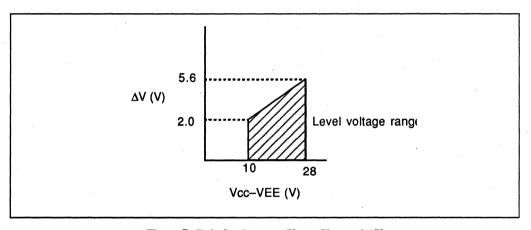

The following is a description of the range of power supply voltage for liquid crystal display drives. Apply positive voltage to V1L= V1R and V3L=V3R and negative voltage to

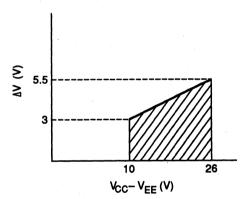

V2L=V2R and V4L=V4R within the  $\Delta V$  range. This range allows stable impedance on driver output (R<sub>ON</sub>). Notice the  $\Delta V$  depends on power supply voltage  $V_{\rm CC}-V_{\rm EE}$ .

Figure 2 Power Supply Voltage Range

#### 3. HD66100F and HD61100A

|                                         |        | HD66100F        | HD61100A            |

|-----------------------------------------|--------|-----------------|---------------------|

| LCD driver circuits                     | common | _               | _                   |

|                                         | column | 80              | 80                  |

| Power supply for LCD drive circuits (V) |        | 3 to 6          | 5.5 to 17.0         |

| Display duty                            |        | static to 1/16  | static to 1/128     |

| Operating frequency                     | (MHz)  | 1.0 MHz (max)   | 2.5 MHz (max)       |

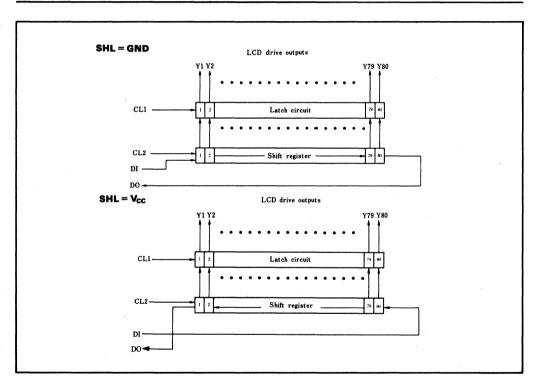

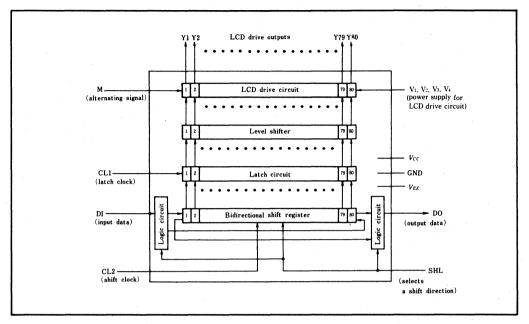

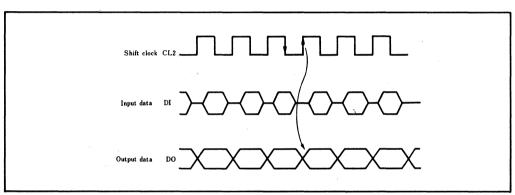

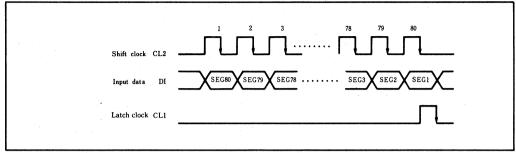

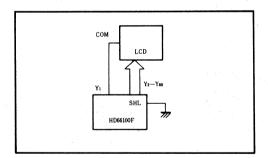

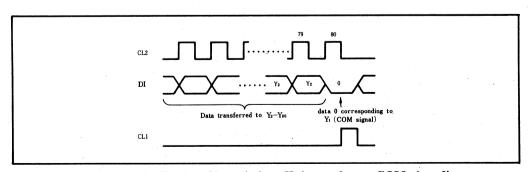

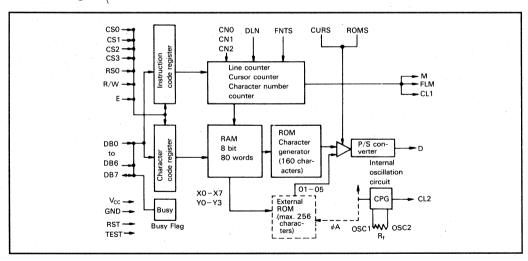

| Data fetch method                       |        | Shift           | Latch               |

| Package                                 |        | 100 pin Plastic | 100 pin plastic QFP |

|                                         |        | QFP (FP-100)    | (FP-100)            |

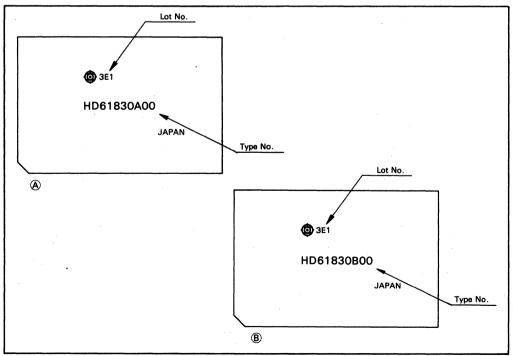

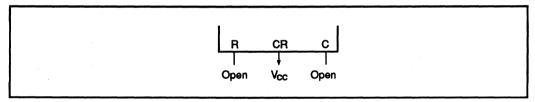

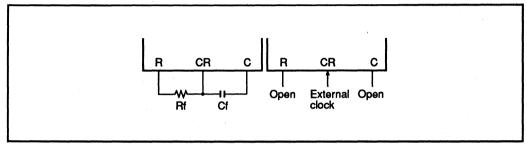

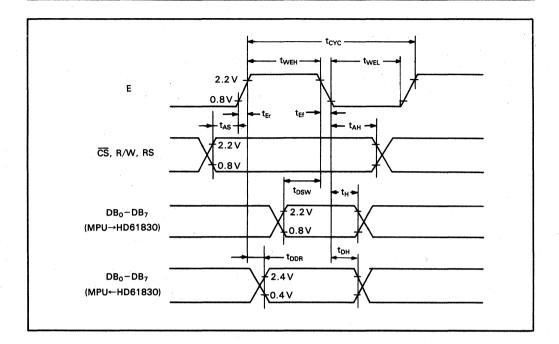

#### 4. HD61830 and HD61830B

|                                | HD61830                         | HD61830B                         |

|--------------------------------|---------------------------------|----------------------------------|

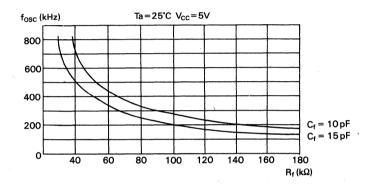

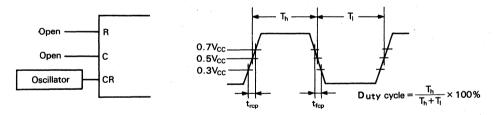

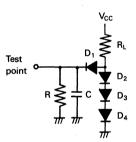

| Oscillator                     | Internal                        | External                         |

| Operating frequency (MHz)      | 1.1 MHz                         | 2.4 MHz                          |

| Display duty                   | static to 1/128                 | static to 1/128                  |

| Programmable screen size (Max) | 64×240 dots<br>(1/64 duty)      | 128×480 dots<br>(1/64 duty)      |

| Other                          | pin 6:C<br>pin 7:R<br>pin 9:CPO | pin 6:CE<br>pin 7:OE<br>pin 9:NC |

| Package Marking                | <b>(A)</b>                      | 8                                |

Figure 3 Package Marking

#### Differences Between Products

#### 5. HD61102 and HD61202

|                                                                     | HD61102                                          | HD61202                                          |

|---------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|

| Display duty                                                        | static to 1/64                                   | 1/32 to 1/64                                     |

| Recommended voltage between V <sub>CC</sub> and V <sub>EE</sub> (V) | 4.5 to 15.5                                      | 8 to 17                                          |

| Power supply limits of LCD driver circuits voltage                  | V <sub>CC</sub> to V <sub>EE</sub> (no limit)    | shown in following fig-<br>ures                  |

| Pin 88                                                              | DY (output)                                      | NC (no connection)                               |

| Absolute maximum rating of V <sub>EE</sub> (V)                      | V <sub>CC</sub> -17.0 to<br>V <sub>CC</sub> +0.3 | V <sub>CC</sub> -19.0 to<br>V <sub>CC</sub> +0.3 |

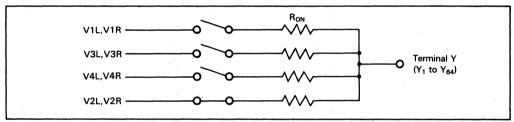

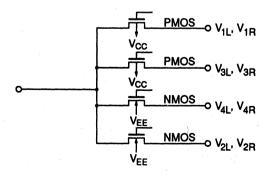

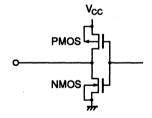

Resistance between terminal Y and terminal V (one of V1L, V1R, V2L, V2R, V3L, V3R, V4L and V4R) when load current flows through one of the terminals  $Y_1$  to  $Y_{64}$  is specified under the following conditions:

$$V_{CC}-V_{EE}=15V$$

$V1L=V1R$ ,  $V3L=V3R=V_{CC}-2/7$  ( $V_{CC}-V_{EE}$ )

$V2L=V2R$ ,  $V4L=V4R=V_{EE}+2/7$  ( $V_{CC}-V_{EE}$ )

Figure 4 Resistance between Y and V Terminals

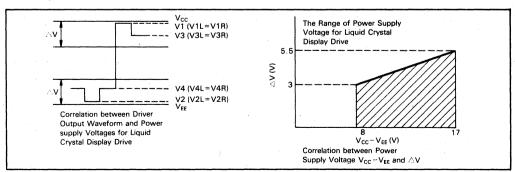

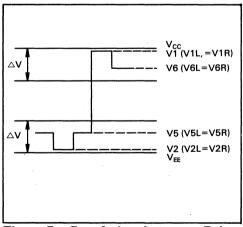

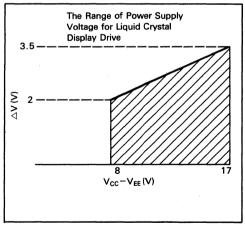

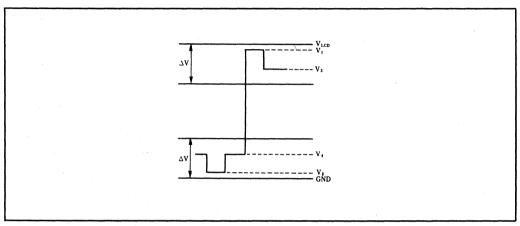

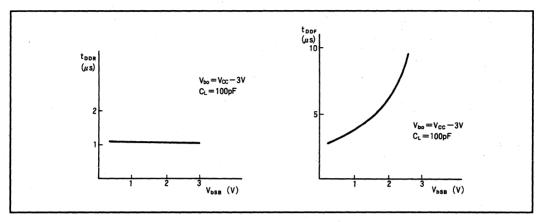

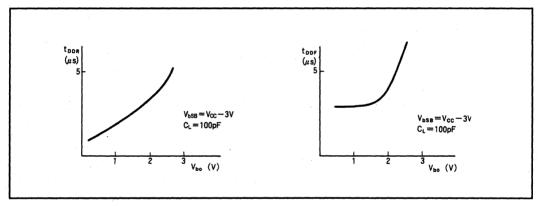

The following is a description of the range of power supply voltage for liquid crystal display drives. Apply positive voltage to V1L=V1R and V3L=V3R and negative voltage to

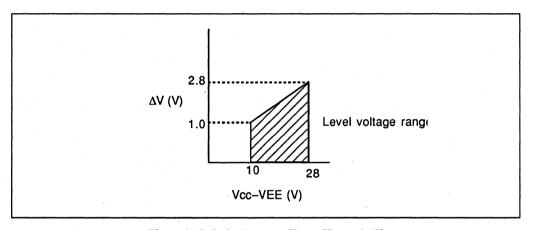

V2L=V2R and V4L=V4R within the  $\Delta V$  range. This range allows stable impedance on driver output (R<sub>ON</sub>). Notice that  $\Delta V$  depends on power supply voltage  $V_{CC}-V_{EE}$ .

Figure 5 Power Supply Voltage Range

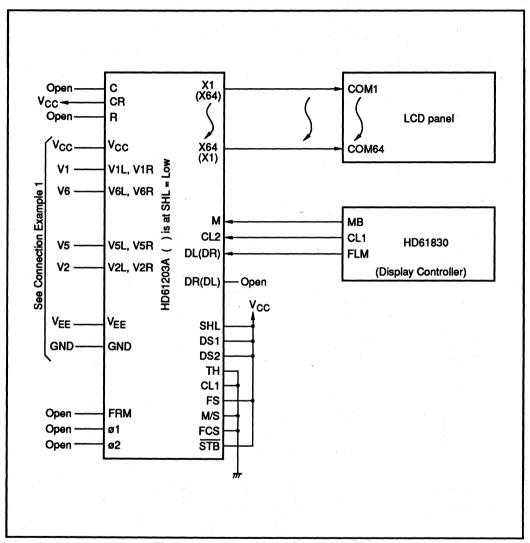

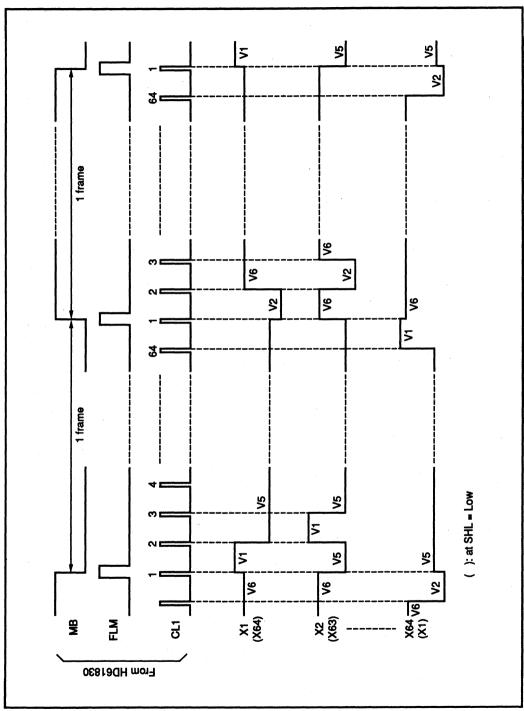

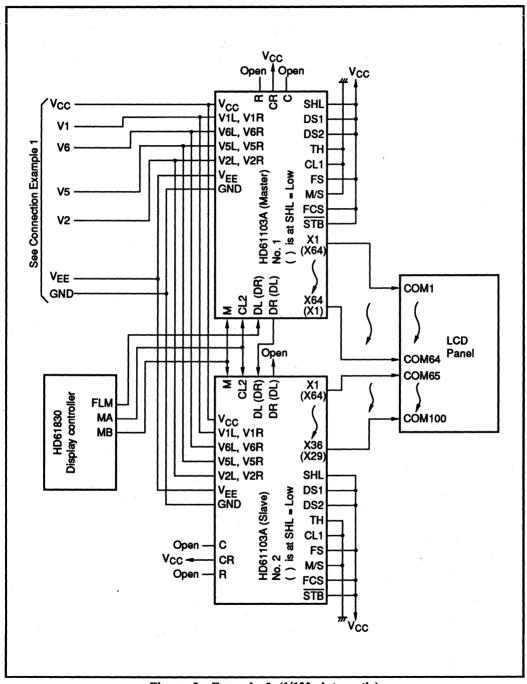

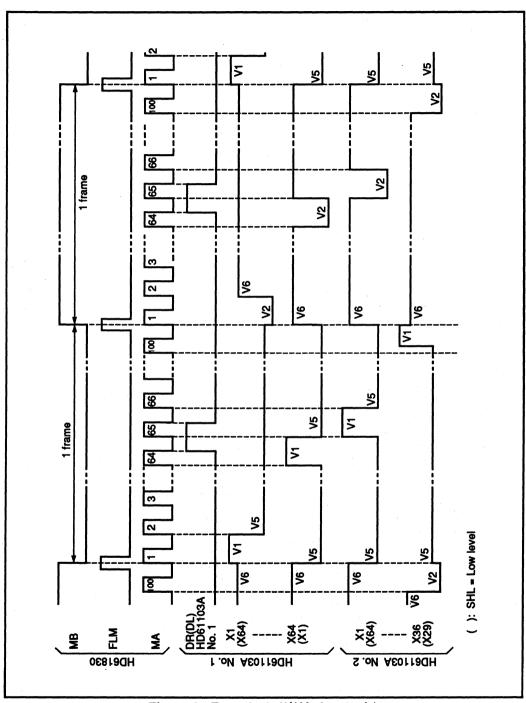

#### 6. HD61103A and HD61203

|                                                                     | HD61103A                                      | HD61203                     |

|---------------------------------------------------------------------|-----------------------------------------------|-----------------------------|

| Recommended voltage between V <sub>CC</sub> and V <sub>EE</sub> (V) | 4.5 to 17                                     | 8 to 17                     |

| Power supply limits of LCD drive circuits voltage                   | V <sub>CC</sub> to V <sub>EE</sub> (no limit) | shown in figures below      |

| Output terminal                                                     | shown in following figure 4                   | shown in following figure 5 |

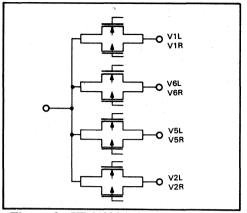

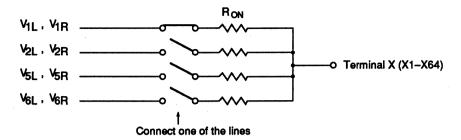

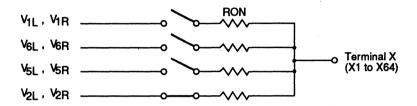

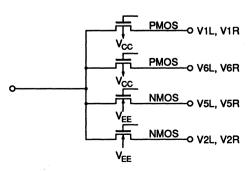

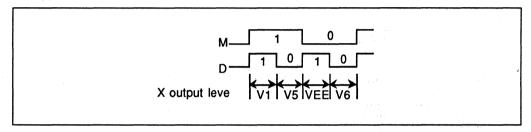

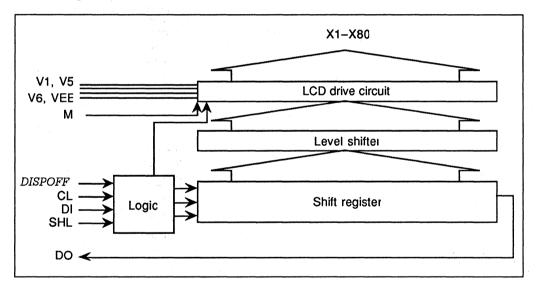

Resistance between terminal Y and terminal V (one of V1L, V1R, V2L, V2R, V5L, V5R, V6L and V6R) when load current flows through one of the terminals X1 to X64. This value is specified under the following conditions:

$$\begin{array}{l} V_{CC} - V_{EE} \! = \! 17V \\ V1L \! = \! V1R, \ V6L \! = \! V6R \! = \! V_{CC} \! - \! 1/7 \ (V_{CC} \! - \! V_{EE}) \\ V2L \! = \! V2R, \ V5L \! = \! V5R \! = \! V_{EE} \! + \! 1/7 \ (V_{CC} \! - \! V_{EE}) \end{array}$$

Figure 6 Resistance between Y and V Terminals

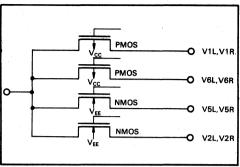

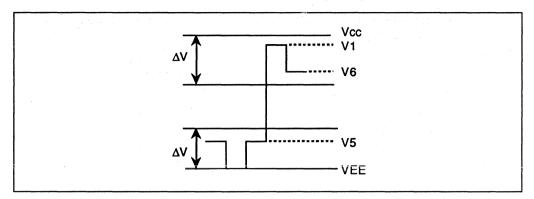

Here is a description of the range of power supply voltage for liquid crystal display drive. Apply postive voltage to V1L=V1R and V6L=V6R and negative voltage to V2L=V2R and

V5L=V5R within the  $\Delta V$  range. This range allows stable impedance on driver output (R<sub>ON</sub>). Notice that  $\Delta V$  depends on power supply voltage  $V_{CC}-V_{EE}$ .

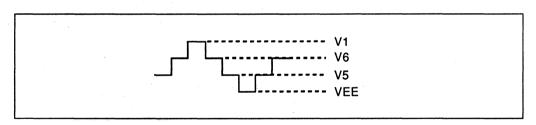

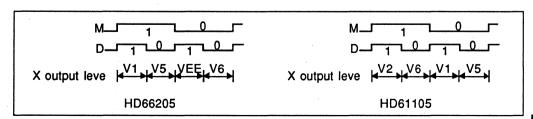

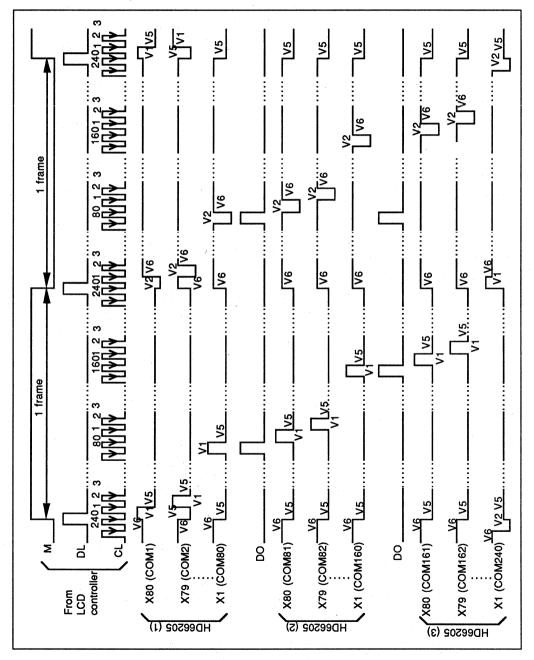

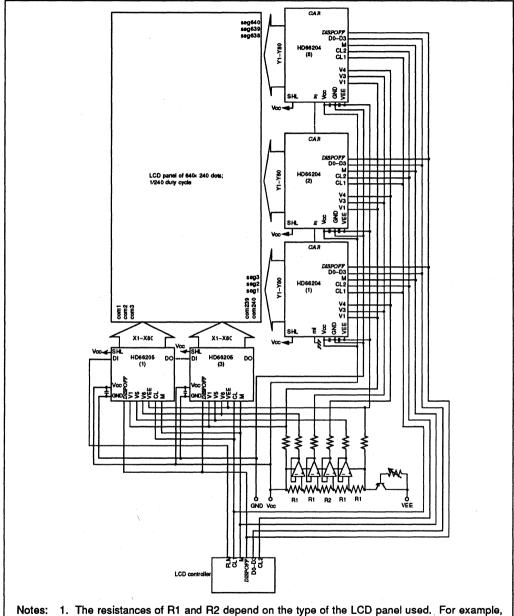

Figure 7 Correlation between Driver Output Waveform and Power Supply Voltages for Liquid Crystal Display Drive

Figure 8 Correlation between Power Supply Voltage V<sub>CC</sub>-V<sub>EE</sub> and  $\wedge$  V

#### **Differences Between Products**

Figure 9 HD61103A Output Termiral

Figure 10 HD61203 Output Termiral

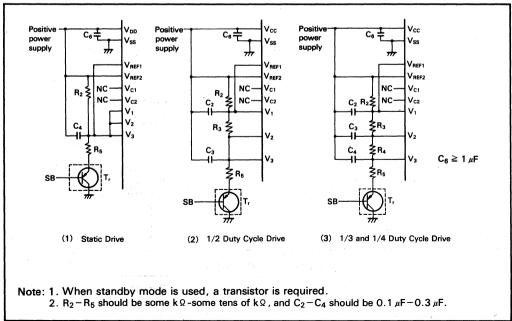

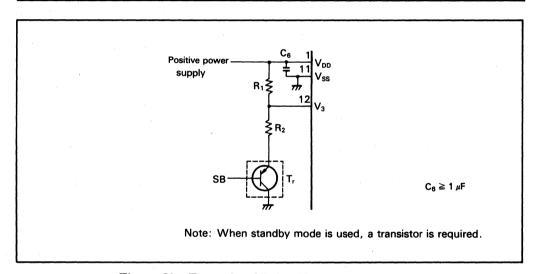

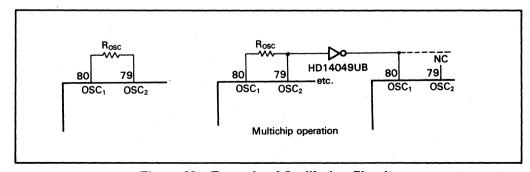

#### 7. HD61602, HD61603, HD61604, and HD61605

|                              |           | HD61602                      | HD61603          | HD61604                       | HD61605          |

|------------------------------|-----------|------------------------------|------------------|-------------------------------|------------------|

| Power supply (V <sub>D</sub> | D)        | 2.2~5.5V                     | 2.2~5.5V         | 4.5~5.5V                      | 4.5~5.5V         |

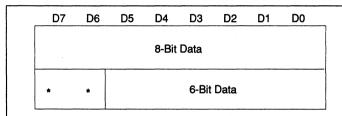

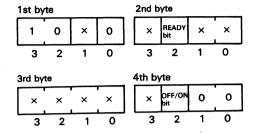

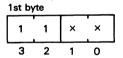

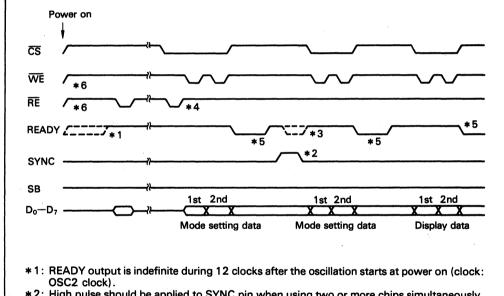

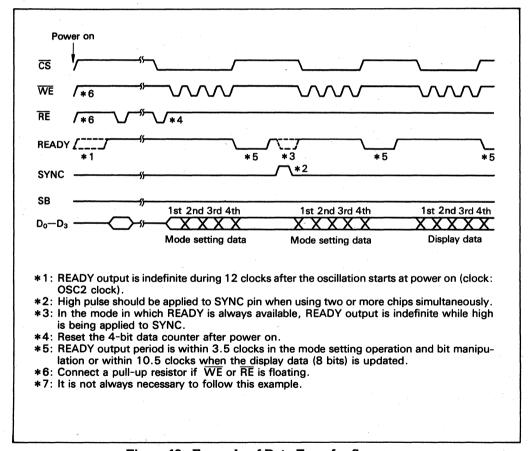

| Instruction word             |           | 8 bits × 2                   | 4 bits × 4       | 8 bits × 2                    | 4 bits × 4       |

| LCD power supply             | y circuit | Yes                          |                  | -                             | _                |

| Segment terminal             | s         | 51                           | 64               | 51                            | 64               |

| Display size frame frequency | Static    | 6 digits + 3 marks<br>33Hz   | 8 digits<br>33Hz | 6 digits + 3 marks<br>98Hz    | 8 digits<br>98Hz |

| (fosc = 100 kHz)             | 1/2 duty  | 12 digits + 6 marks<br>65Hz  |                  | 12 digits + 6 marks<br>195Hz  |                  |

|                              | 1/3 duty  | 17 digits<br>208Hz           | -                | 17 digits<br>521Hz            | _                |

|                              | 1/4 duty  | 25 digits + 4 marks<br>223Hz | _                | 25 digits + 4 marks<br>781 Hz | _                |

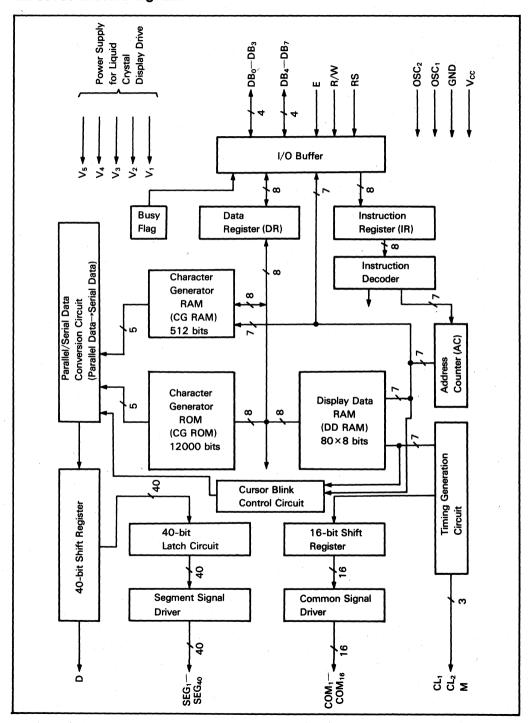

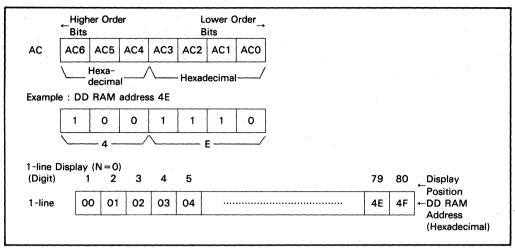

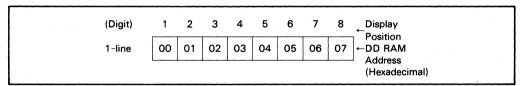

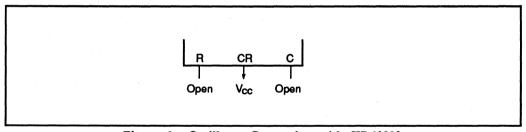

#### 8. HD44780 LCD-II and HD66780 LCD-II A

| item                                                     |          | LCD-II (HD44780)                         | LCD- II A (HD66780)                   | Note                              |

|----------------------------------------------------------|----------|------------------------------------------|---------------------------------------|-----------------------------------|

| Display RAM<br>(Maximum number of<br>display characters) |          | 80 bytes (80 characters)                 | •                                     |                                   |

| Character generator ROM                                  |          | 7200 bits                                | 12000 bits                            |                                   |

| (kinds of characters)                                    |          | 192 characters                           | 240 characters                        |                                   |

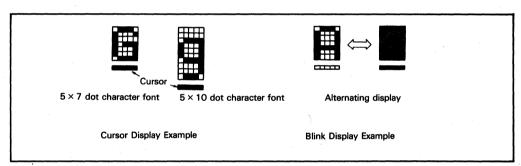

|                                                          |          | 5×7;160 characters<br>5×10:32 characters | 5×10;240 Characters                   |                                   |

| Character generator RAM (Number of characters)           |          | 64 bytes (8 characters)                  | · .                                   |                                   |

| LCD driving terminals                                    |          | 16 COMs                                  | <b></b>                               |                                   |

| (Maximum number of                                       |          | 40 SEGs                                  |                                       |                                   |

| display characters/<br>unit)                             |          | (16 characters)                          |                                       |                                   |

| Character font                                           |          | 5×8 dots                                 | 4                                     |                                   |

| (with a cursor)                                          |          | 5×11 dots                                |                                       |                                   |

| Multiplexing duty ratio                                  |          | 1/8, 1/11, 1/16                          | Same as LCD-II                        |                                   |

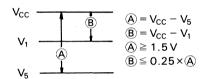

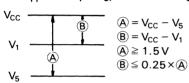

| *1LCD driving voltage                                    | 1/4 bias | 3.0 to 11 (V)                            | 3.0 to V <sub>CC</sub> (V)            | V <sub>CC</sub> to V <sub>5</sub> |

|                                                          | 1/5 bias | 4.6 to 11 (V)                            | 3.0 to V <sub>CC</sub> (V)            |                                   |

| *1LCD driving waveform                                   |          | waveform A                               | waveform B                            | Shown follow-<br>ing figures      |

| *Bus timing                                              |          | 1, 1.5MHz                                | 2MHz                                  |                                   |

| Instruction codes                                        |          | 11 instructions                          | <del></del>                           |                                   |

| Power-on reset circuit                                   |          | Yes                                      | -                                     |                                   |

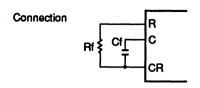

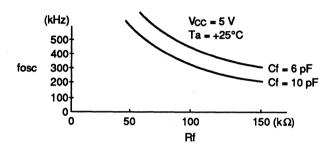

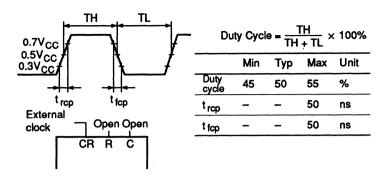

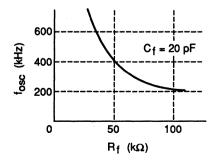

| Oscillator                                               |          | Ceramic filter, Rf,                      | <b>←</b>                              |                                   |

| (Frequency)                                              |          | external clock                           |                                       |                                   |

|                                                          |          | (250 kHz)                                | · · · · · · · · · · · · · · · · · · · |                                   |

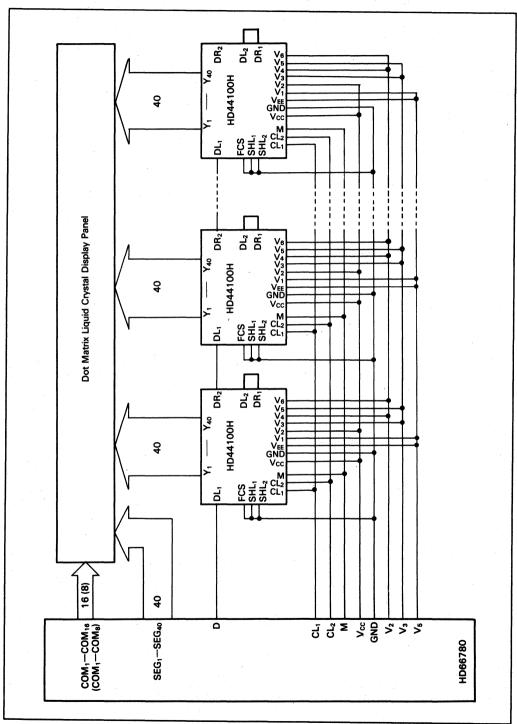

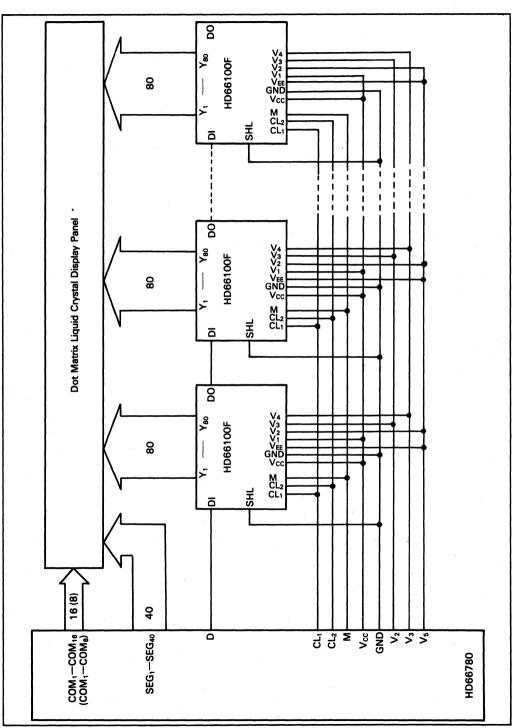

| Interface                                                |          | HD44100H                                 | HD44100H or HD66100                   | )F                                |

| Package                                                  |          | FP-80, FP-80A, TFP-80*2                  | FP-80, FP-80A                         |                                   |

Note: \*1 Indicates the modified items in LCD-II A.

#### \*2 Under development

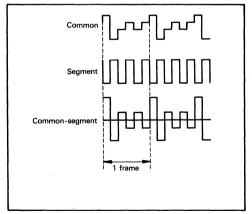

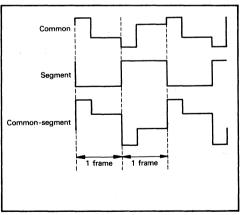

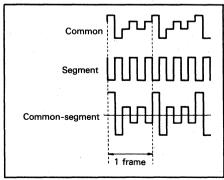

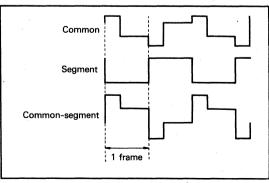

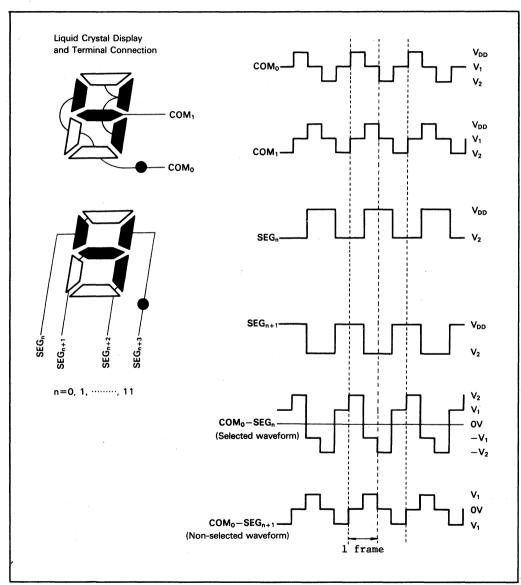

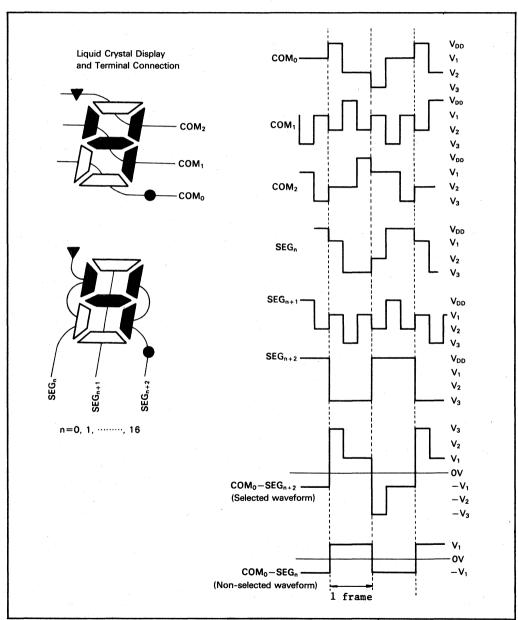

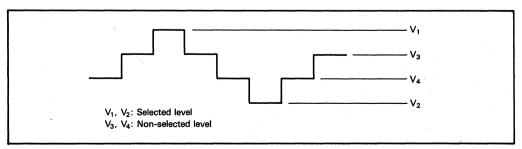

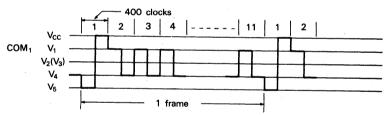

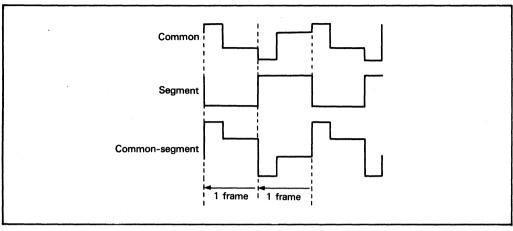

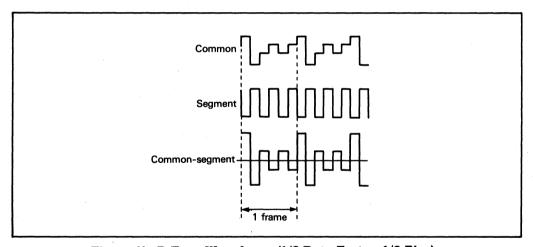

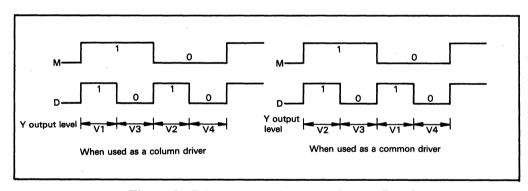

Figure 11 Waveform A (1/3 Duty, 1/3 Bias)

Figure 12 Waveform B (1/3 Duty, 1/3 Bias)

#### **Differences Between Products**

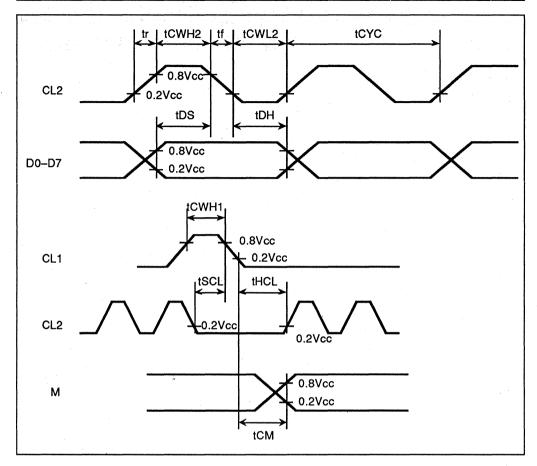

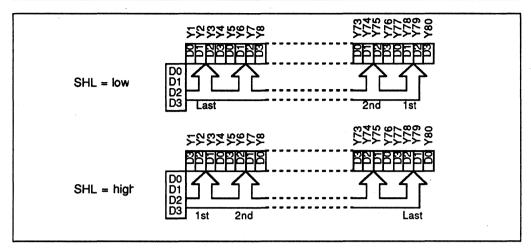

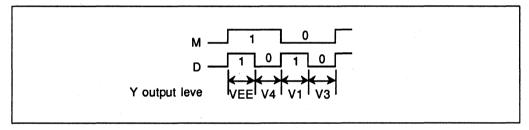

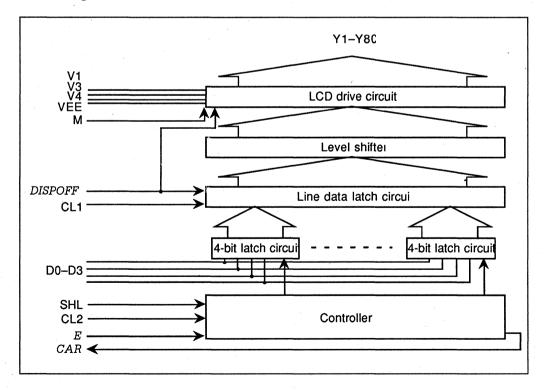

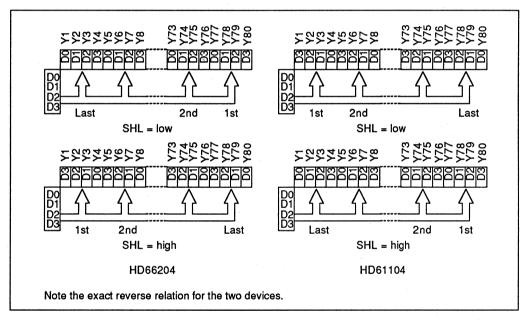

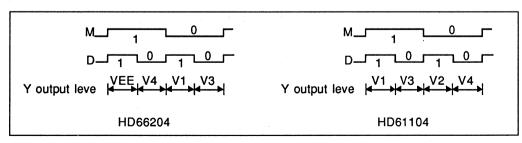

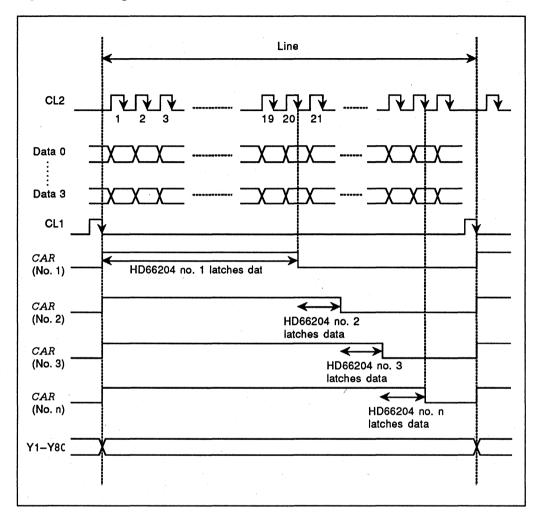

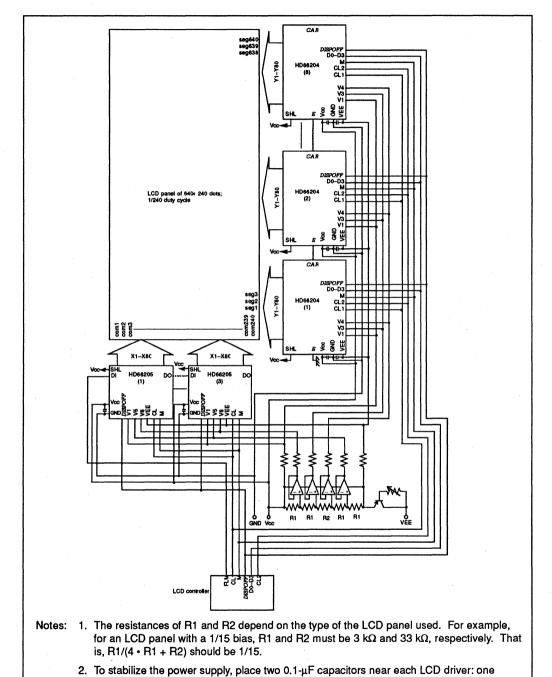

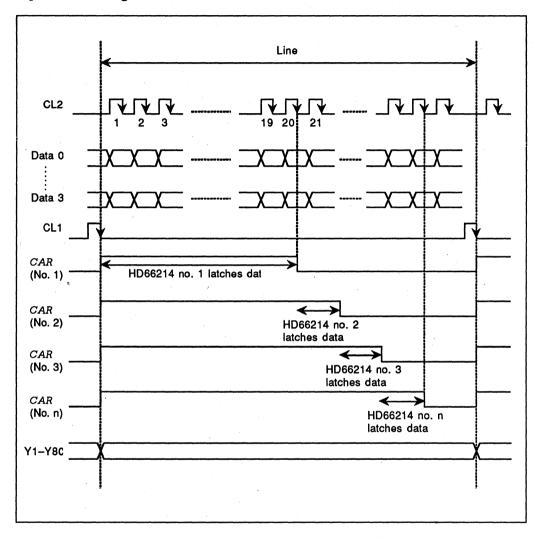

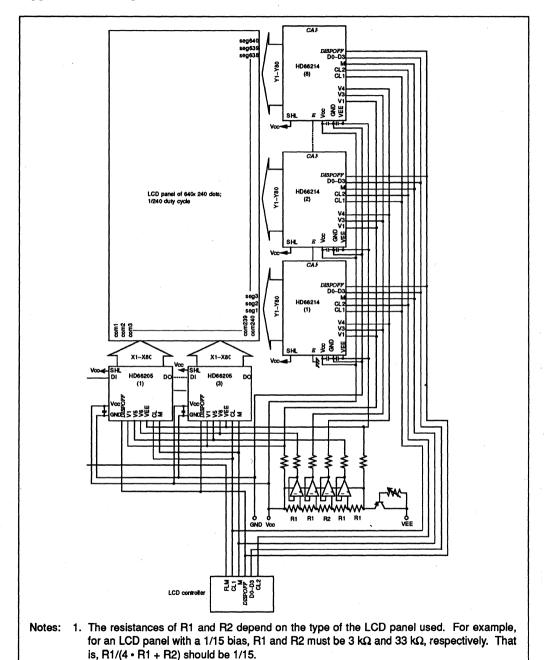

#### 9. HD61104, HD61104A and HD66204

|                                         | HD61104  | HD61104A | HD66204  |

|-----------------------------------------|----------|----------|----------|

| LCD drive circuits                      | 80       | 80       | 80       |

| Data transfer rate (MHz)                | 3.5      | 3.5      | 8        |

| Power supply for LCD drive circuits (V) | 10 to 26 | 10 to 28 | 10 to 28 |

| Display off function                    | No       | No       | Yes      |

#### 10. HD61105, HD61105A and HD66205

|                                         | HD61105  | HD61105A | HD66205  |

|-----------------------------------------|----------|----------|----------|

| LCD drive circuits                      | 80       | 80       | 80       |

| Power supply for LCD drive circuits (V) | 10 to 26 | 10 to 28 | 10 to 28 |

| Display off function                    | No       | No       | Yes      |

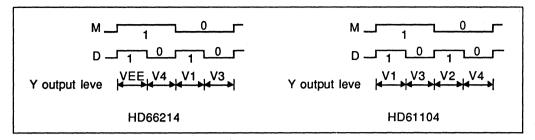

#### 11. HD66106F and HD61104

|                            | HD66106F                           | HD61104                                        |

|----------------------------|------------------------------------|------------------------------------------------|

| LCD drive circuits voltage | +14 to +35 (V <sub>LCD</sub> -GND) | -10 to -26 (V <sub>CC</sub> -V <sub>EE</sub> ) |

| Display Duty               | 1/100 to 1/400                     | 1/64 to 1/200                                  |

| Operating frequency (MHz)  | 6.0 MHz                            | 3.5 MHz                                        |

| Function                   | column and common driver           | column driver                                  |

#### 12. HD66106F and HD66107T

|                                     | HD66106F        | HD66107T      |

|-------------------------------------|-----------------|---------------|

| LCD drive circuits                  | 80              | 160           |

| Data transfer                       | 4-bits          | 4-bits/8-bits |

| Operating frequency (MHz)           | 6               | 8             |

| Power supply for LCD drive circuits | 14 to 37        | 14 to 37      |

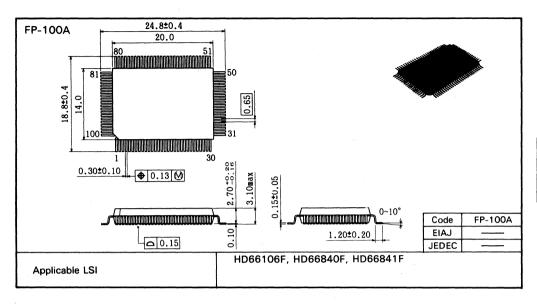

| Packge                              | 100-pin plastic | 192-pin TAB   |

|                                     | QFP (FP-100A)   |               |

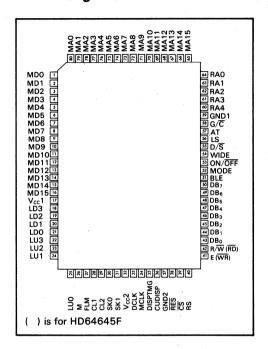

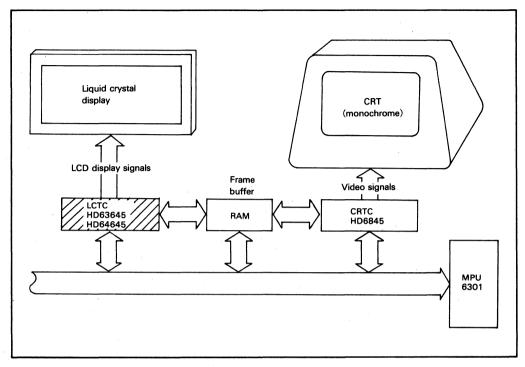

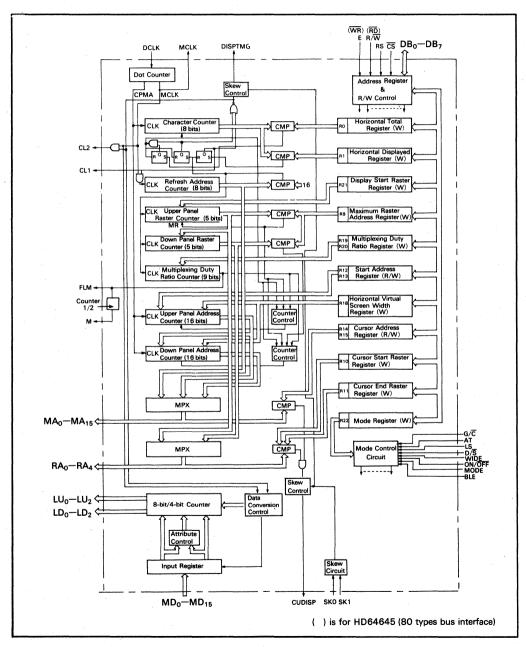

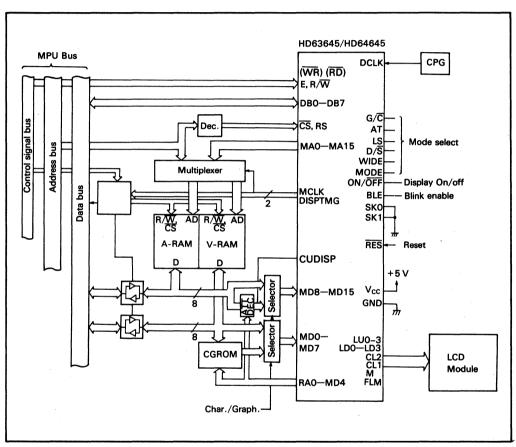

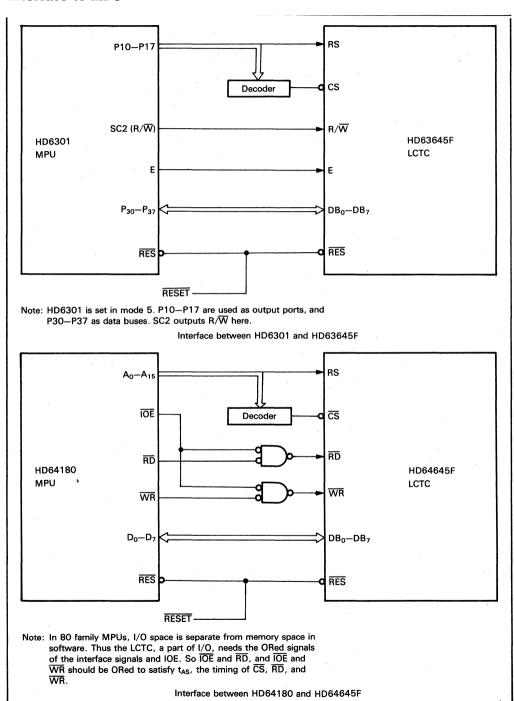

#### 13. HD63645F, HD64645F and HD64646FS

|               | HD63645F                      | HD64645F                      | HD64646FS                                          |

|---------------|-------------------------------|-------------------------------|----------------------------------------------------|

| CPU interface | 68 family                     | 80 family                     | 80 family                                          |

| Package       | 80-pin plastic<br>QFP (FP-80) | 80-pin plastic<br>QFP (FP-80) | 80-pin plastic<br>QFP (FP-80A)                     |

| Other         | · · · · · ·                   |                               | HD64646 has another LCD drive interface in HD64645 |

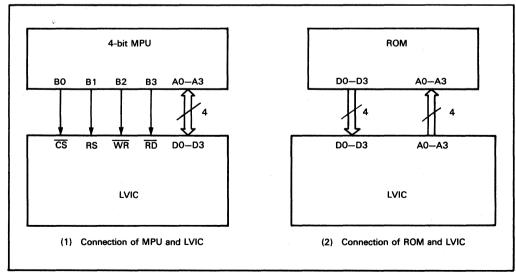

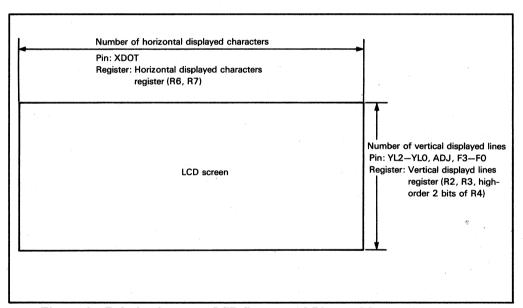

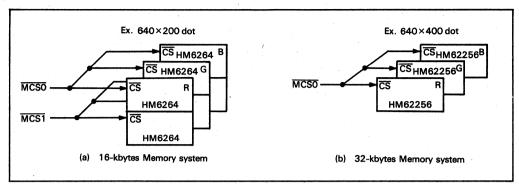

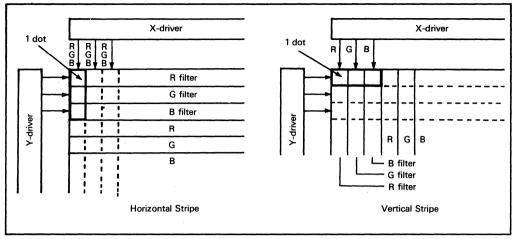

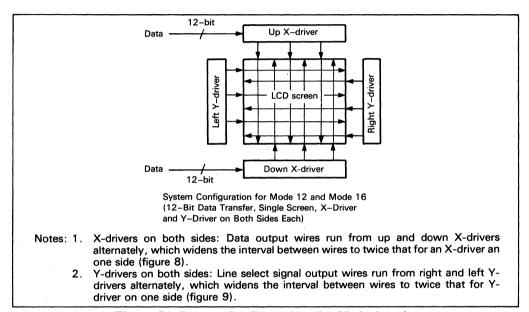

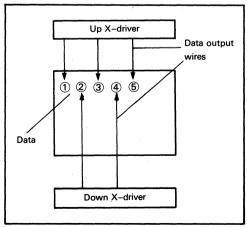

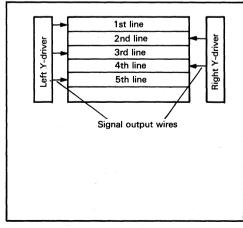

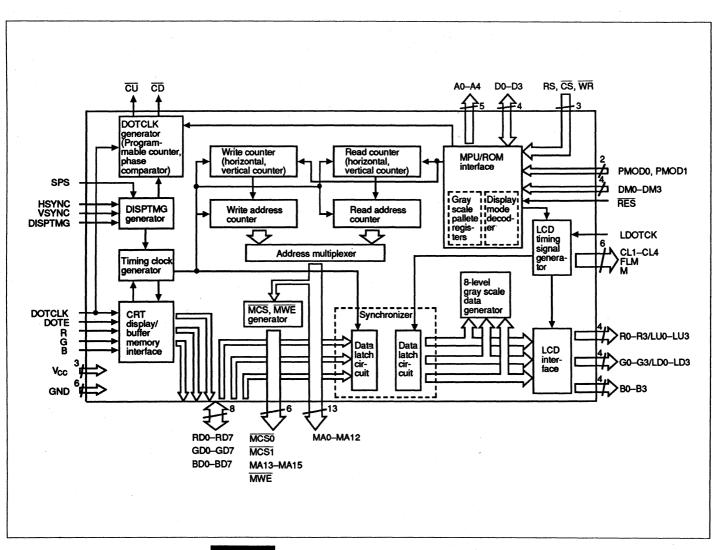

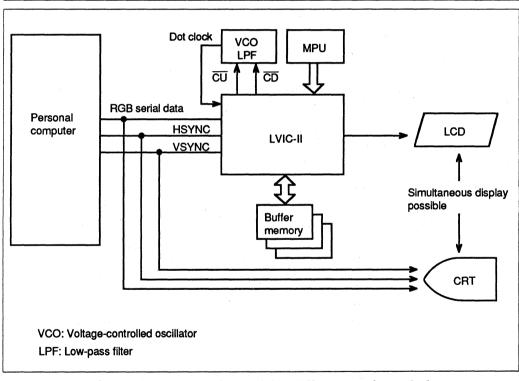

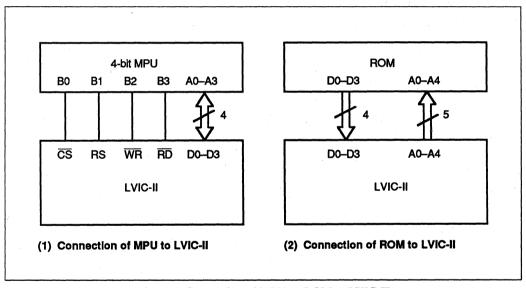

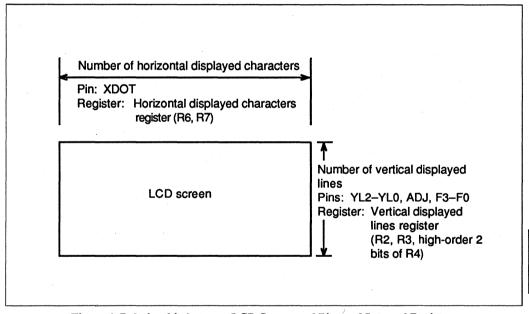

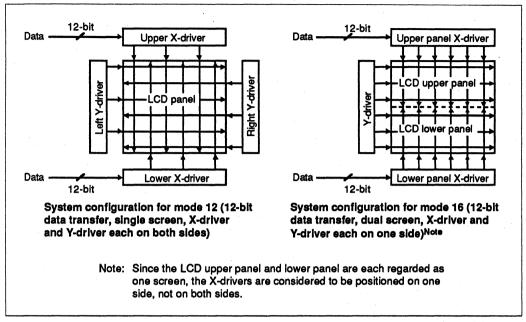

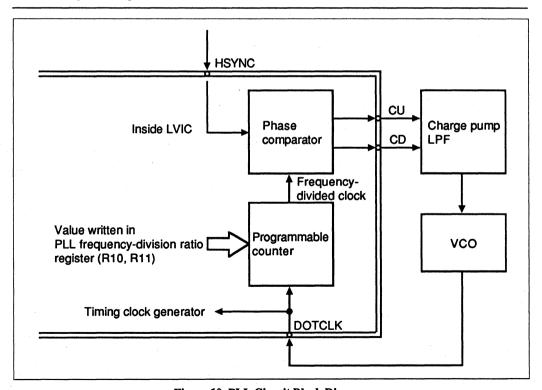

#### 14. HD66840F and HD66841F

| ·                            | HD66840F              | HD66841F               |

|------------------------------|-----------------------|------------------------|

| Frame-based thinning control | Eách line             | Each dot and each line |

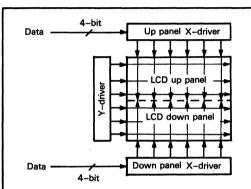

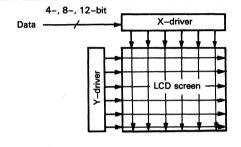

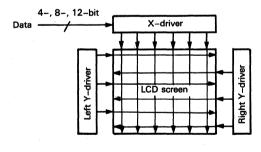

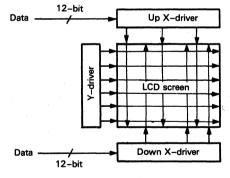

| Display mode 16              | Single screen         | Dual screen            |

|                              | Both sides X/Y driver | One sides X/Y driver   |

|                              | Horizontal stripe     | Vertical stripe        |

| Gray-scale palette           | No                    | 8 registers            |

|                              |                       |                        |

## LCD CONTROLLER/DRIVER LSI DATA BOOK

## **Section Two**

## General Information II

- TCP (Tape Carrier Package)

- Package Information

- Reliability and Quality Assurance

- Reliability Test Data of LCD Drivers

- Flat Plastic Package (QFP) Mounting Methods

- Liquid Crystal Driving Methods

#### TCP (Tape Carrier Package)

#### 1 Overview

Hitachi is developing TCP-applied LCD driver LSIs in response to the following situation.

Because LCDs are improving yearly, they have become second only to CRTs in terms of screen size and display quality. At the same time, LCD driver LSIs have also been improving in terms of voltage-resistivity and the number of pins.

At present, LCD screens with a maximum of 640×480 dots has been put into practical use, matching the size of conventional high-definition CRT display screens. Availability of this screen size promotes the development and improvement of new application fields such as laptop personal computers, portable word processors, and the like.

In the light of the above, higher performance has been demanded of LCD driver LSIs, especially in regards to LCD driving voltage, operating speed, and the number of pins. In fact, certain manufacturers of portable devices employing LCDs demand 1-mm-thick packages having a relatively large number of pins.

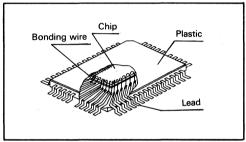

TCP packages have the advantages of being able to allow extra thin mounting and less restricted design of connecting leads, while in contrast, conventional packages utilizing wire bonding methods such as QFP require a relatively large area for board mounting, thus preventing thin and high-density mounting.

TCP packaging is also called "film carrier" since the wiring pattern for each product is formed continuously on a film-base tape.

TCP features are listed below.

- Great reduction in mounting size

- Increased number of pins for LSI devices

- Power-on burn-in possible

- \* TCP (Tape Carrier Package)

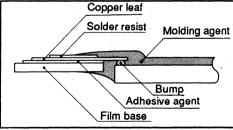

Photograph 1 shows the TCP tape exterior and figure 1 shows TCP structure.

Photograph 1 TCP Exterior

Figure 1 TCP Structure (Cross Section)

#### 1.1 Bump Formation

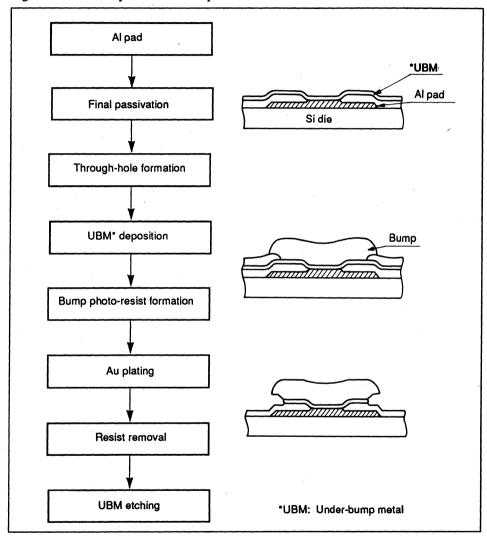

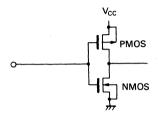

Although LSI electrodes and package leads are wired with Au-wire bonding for QFP, Au bumps formed on LSI electrodes (Al pads) and inner leads prefabricated on tape are thermo-compressed and bonded together for TCP. This method is called "inner-lead bonding" or ILB for short.

Figure 2 shows the sequence for Au bump formation.

Figure 2 Au Bump Formation

#### 1.2 Reliability Test Data

The result of the reliability test on TCP products are shown in table 1 through 3.

Table 1 HD66107T Reliability Test Result

| Test item                     | Test condition                               | Result | Remarks          |  |

|-------------------------------|----------------------------------------------|--------|------------------|--|

| Operation at high temperature | Ta=125°C, V <sub>CC</sub> =5.5 V<br>t=1000 h | 0/32   |                  |  |

| Standing at high temperature  | Ta=125°C, t=1000 h                           | 0/22   |                  |  |

| Standing at low temperature   | Ta=-55°C, t=1000 h                           | 0/22   |                  |  |

| Standing at high temperature  | Ta=65°C, RH=95%,<br>t=1000 h                 | 0/45   |                  |  |

| PCT                           | Ta=121°C, RH=100%, t=60 h                    | 0/22   |                  |  |

| Temperature cycle             | -40° to 85°C, 200 cycles                     | 0/45   | ·                |  |

| Thermal shock                 | 0° to 100°C, 15 cycles                       | 0/22   |                  |  |

| Solder heat resistance        | 260°C, 10 s                                  | 0/22   | Only lead dipped |  |

Table 2 HD61105T Reliability Test Result

| Test item                     | Test condition                               | Result | Remarks          |  |  |

|-------------------------------|----------------------------------------------|--------|------------------|--|--|

| Operation at high temperature | Ta=125°C, V <sub>CC</sub> =5.5 V<br>t=1000 h | 0/32   |                  |  |  |

| Standing at high temperature  | Ta=125°C, t=1000 h                           | 0/22   |                  |  |  |

| Standing at low temperature   | Ta=-55°C, t=1000 h 0/22                      |        | ·                |  |  |

| Standing at high temperature  | Ta=65°C, RH=95%,<br>t=1000 h                 | 0/45   |                  |  |  |

| PCT                           | Ta=121°C, RH=100%, t=60 h                    | 0/22   | ·                |  |  |

| Temperature cycle             | -40° to 85°C, 200 cycles                     | 0/45   |                  |  |  |

| Thermal shock                 | 0°C to 100°C, 15 cycles                      | 0/22   |                  |  |  |

| Solder heat resistance        | 260°C, 10 s                                  | 0/22   | Only lead dipped |  |  |

Table 3 Common Reliability Test Results of TCP

| Test item                    | Test condition                                 | Result | Remarks         |  |

|------------------------------|------------------------------------------------|--------|-----------------|--|

| Solderability                | 230°C, 5 s, Rosin flux                         | 0/11   |                 |  |

| Solvent resistance           | Isopropylalcohol, dipping for 10 min.          |        |                 |  |

| Salt spray                   | 5% NaCl aqueous solution, 0/22<br>35°C, t=24 h |        |                 |  |

| Tensile strength of terminal | 2.5 kg/mm <sup>2</sup> , 10 s, 1 cycle         | 0/11   | Input lead only |  |

#### 2 Standard Product Specifications

#### 2.1 Tape Design and Structure

#### (1) Tape components

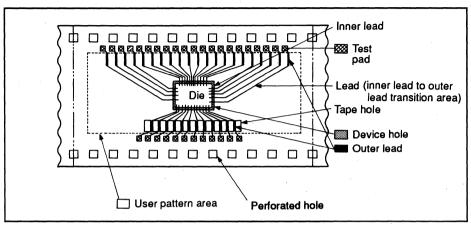

Figure 3 Tape Components

#### (2) Hitachi standard TCP product structure

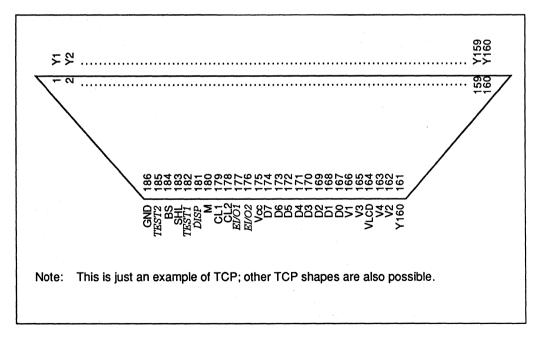

Hitachi can provide the standard TCP products listed in table 4 immediately. Figures 4 to 11 show the structure of each TCP product.

| No. | Product      | Base Chip | Function              | No. of outputs | Outer Lead<br>Pitch (µm) | Product<br>Length* | Tape<br>Thickness |

|-----|--------------|-----------|-----------------------|----------------|--------------------------|--------------------|-------------------|

| 1   | HD61104T02   | HD61104   | Column<br>LCD driver  | 80             | 300                      | 6                  | 125               |

| 2   | HD61105T02   | HD61105   | Common<br>LCD driver  | 80             | 300                      | 6                  | 125               |

| 3   | HD66107T00   | HD66107   | LCD driver            | 160            | 280                      | 12                 | 75                |

| 4   | HD66107T01   |           |                       | 80             | 280                      | 12                 | 75                |

| 5   | HD66107T11** |           |                       | 160            | 180                      | 8                  | 75                |

| 6   | HD66107T12** |           |                       | 160            | 250                      | 10                 | 75                |

| 7   | HD66108T00   | HD66108   | Graphic<br>LCD driver | 165            | 400                      | 8                  | 75                |

| 8   | HD66300T00   | HD66300   | TFT analog<br>driver  | 120            | 300                      | 10                 | 75                |

**Table 4 Hitachi Standard TCP Product Specifications**

160

180

8

75

HD66310

HD66310T00

TFT digital

driver

Number of perforations

Under development

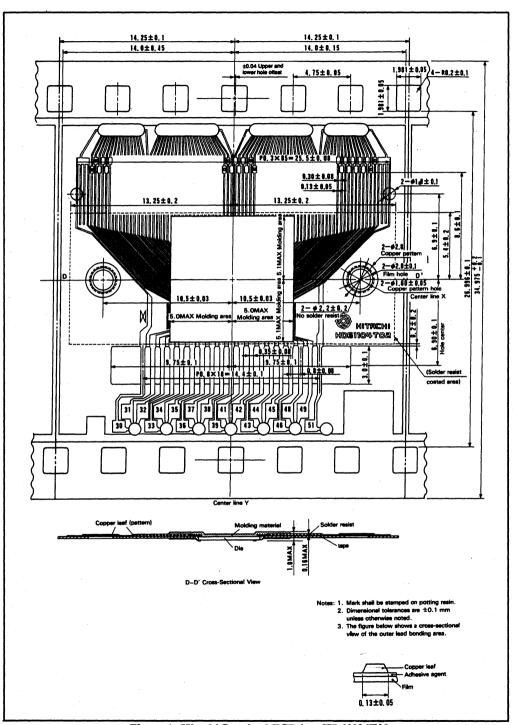

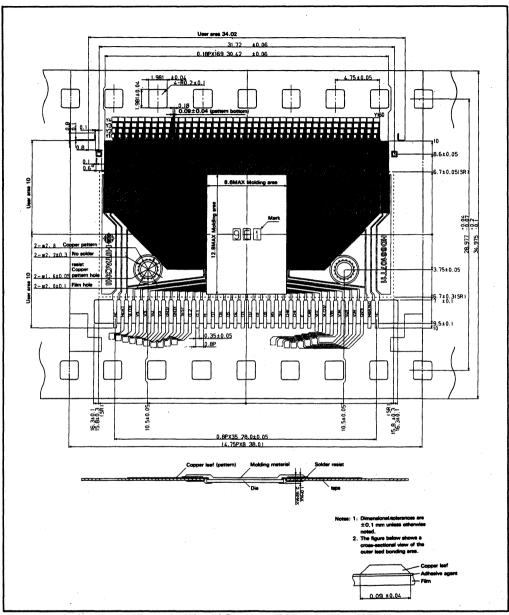

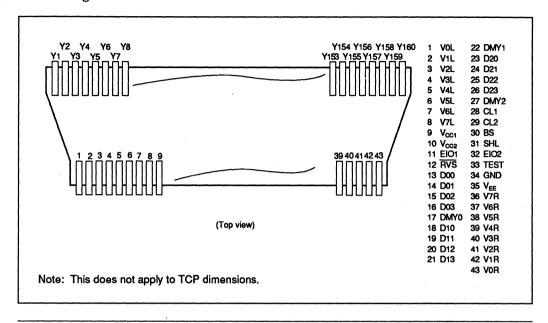

Figure 4 Hitachi Standard TCP 1 - HD61104T02 -

Figure 5 Hitachi Standard TCP 2 - HD61105T02 -

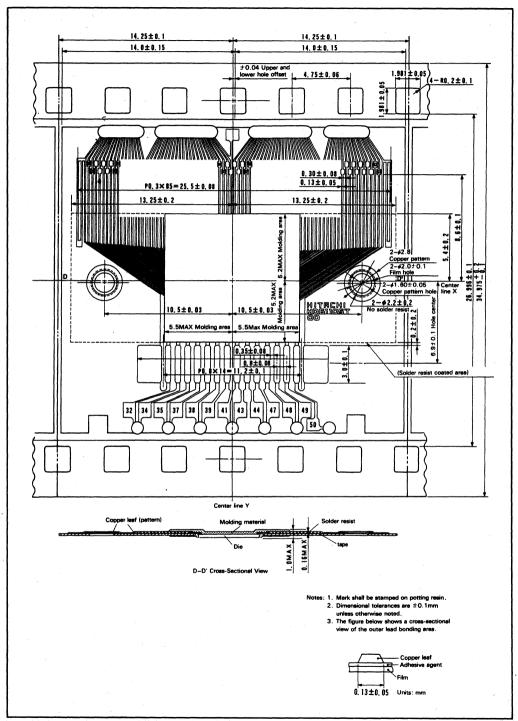

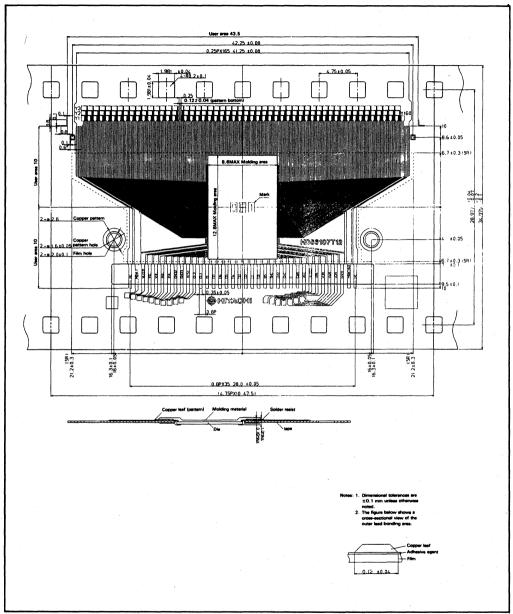

Figure 6 Hitachi Standard TCP 3 - HD66107T00 -

Figure 7 Hitachi Standard TCP 4 - HD66107T01 -

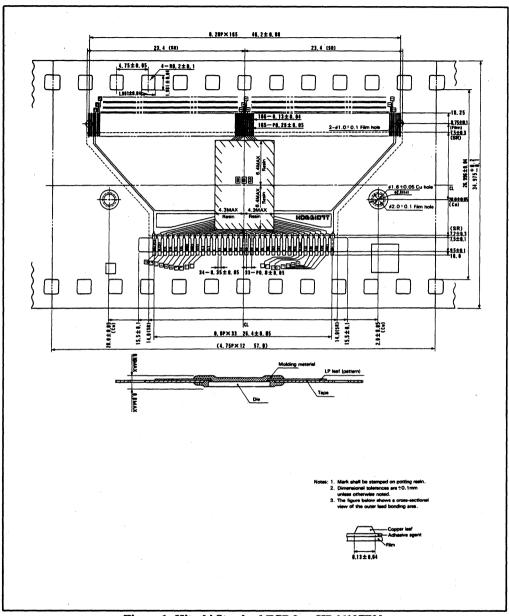

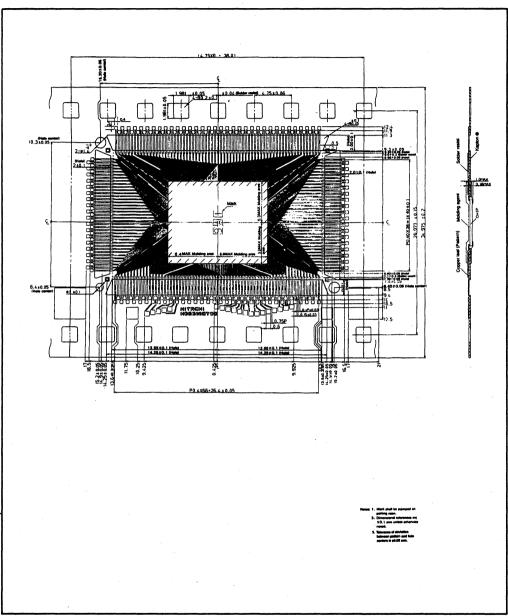

Figure 8 Hitachi Standard TCP 5 - HD66107T11 -

Figure 9 Hitachi Standard TCP 6 - HD66107T12 -

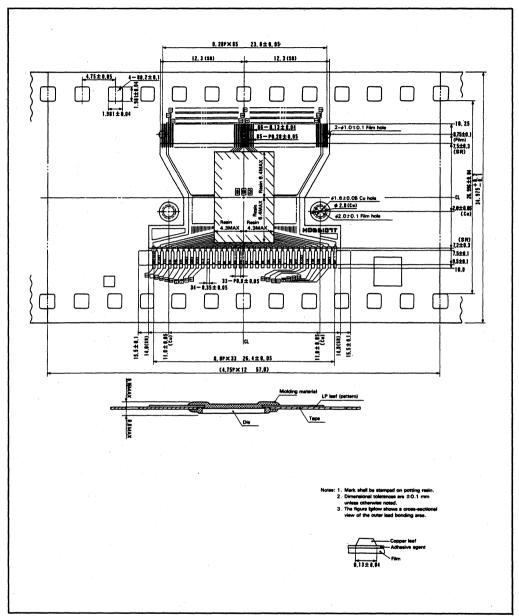

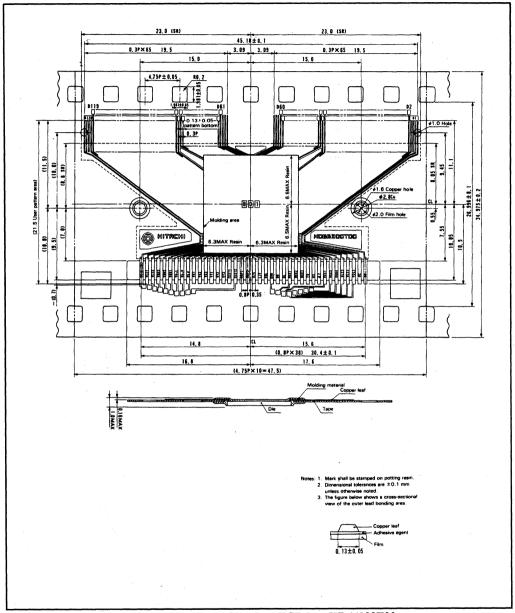

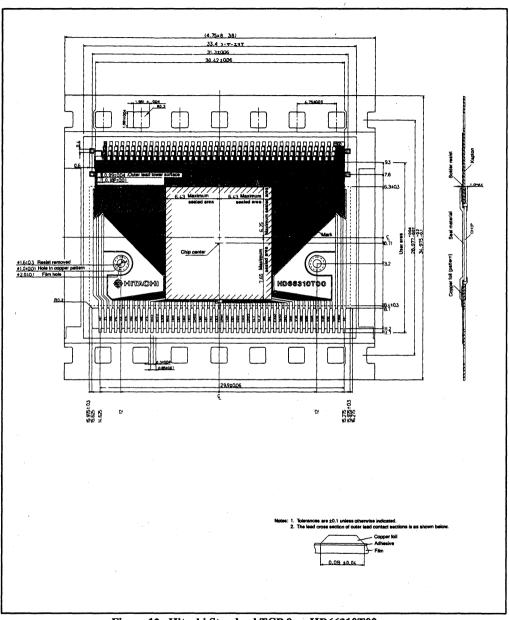

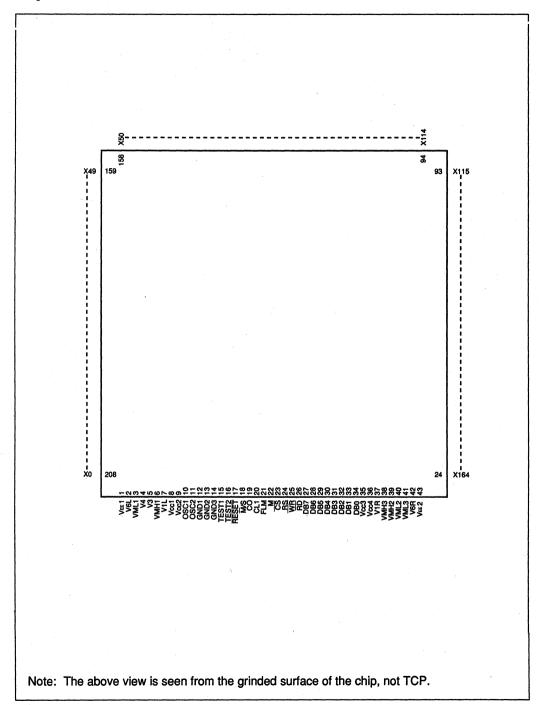

Figure 10 Hitachi Standard TCP 7 - HD66108T00 -

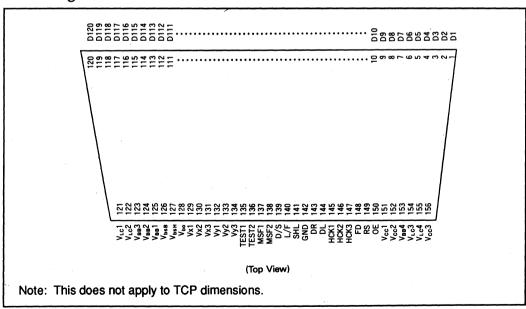

Figure 11 Hitachi Standard TCP 8 - HD66300T00 -

Figure 12 Hitachi Standard TCP 9 - HD66310T00 -

## 2.2 Product Delivery Specifications

Specifications for product delivery to customers is described below.

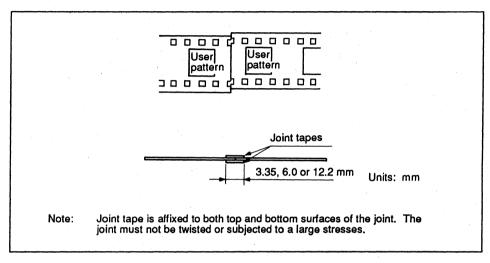

### 2.2.1 Tape Joint (Including Lead Tape Joint)

TCP tape is cut into strips for aging and other purposes, after which they are again joined together. Joint specifications are given below (figure 13).

Figure 13 Tape Joint

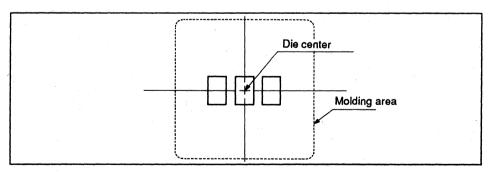

### 2.2.2 Mark

Hitachi control code, made up of three or six digits, is marked on potting resin as shown in figure 14. The HD66108T00 is marked on top of the solder resist.

Figure 14 Mark Pattern

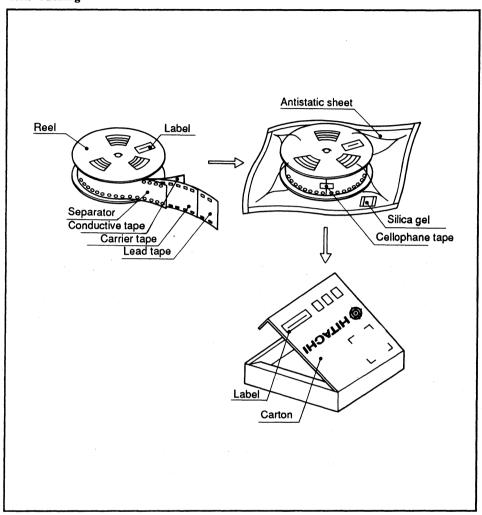

## 2.2.3 Packing

Figure 15 Packing

### TCP

(1) Delivery

A reel wound with carrier tape is sealed in an opaque antistatic sheet with N2 and packed into a carton before delivery.

(2) Tape

I. Carrier tape:

40 m

II. Lead tape:

2+0/-1 m added to both ends of the carrier tape

III. Conductive tape:

40 m

IV. Separator:

40 m

V. Tape is wound with its pattern surface on the inside.

Note: The length of I, III, and IV may vary slightly depending on the number of products contained on the tape.

(3) Request for Recovery of Packing Material

Please return the separator, lead tape, and reel to us after using the TCP product.

Detailed return procedures will be advised by our Sales Department.

### (3) Reel

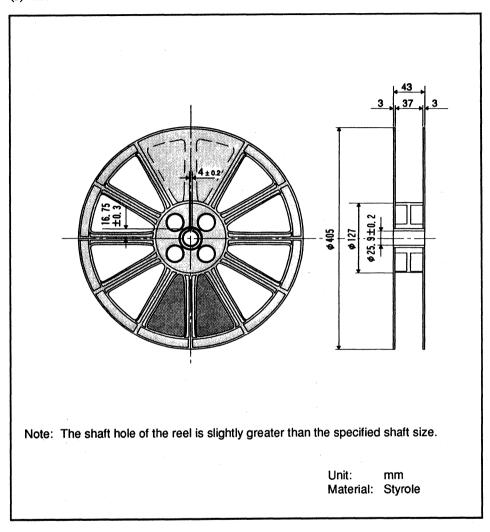

Figure 16 Reel Dimensions

Note: LSIs dtermined defective during classification, assembly, or other processes are punched out.

### 2.2.4 Storage Conditions

(1) When storing in the original packing

Store in normal atmospheric conditions, and use within 6 months of delivery.

(2) Storage after opening

Storage in a nitrogen atmosphere with a dew point of -30°C or below is recommended.

### 2.2.5 Usage Notes for TCP Products

### (1) Prevention of Static Damage

In addition to normal static preventive measures for IC circuits, observe the following precautions for TCP products.

- Since TCP products have a film layer on their base, they acquire a static charge easily. In

handling TCP products exert extra caution in the installation of ion blowers and grounding so

that the film does not become charged.

- At the same time as handling the circuits in a manner such that static electricity is not applied to

the package leads, carry out static electricity damage prevention measures in the equipment,

especially in the parts of the tape guide which contact the lead pins.

### (2) Lead Outer Coating

The lead spacing of TCP products is significantly narrower than that of other products and shorting problems are more easily caused by conductive foreign elements such as stray solder or machinings. We recommend an outer coating of resin over the leads as a preventive measure.

Also, to enable TCP products to be mounted at a high density, a conductive foil is bonded to the film, and wiring and leads are formed by precision manufacturing techniques. Therefore, it is possible that contamination of the foil with, for example, solder flux, may result in corrosion and broken connections. Thus, special care should be taken to avoid wiring and lead contamination when mounting TCP products by soldering or other methods.

### (3) Mechanical and Electrical Handling

To reduce thickness, the back surface of the chip is exposed in TCP products. To prevent chip cracking or static damage, mount TCP products in a manner which results in no mechanical or electrical contact with the back surface of the chip.

Since the wiring and leads on the TCP tape is fabricated from extremely thin copper foil, its mechanical strength is reduced. Mounting techniques and structures which apply strong external forces to the copper foil should be avoided.

Also, to assure electrical characteristics, avoid direct exposure to sunlight.

### (4) Unpacking

- The copper foil is plated. To assure good solderability, use the products as soon after unpacking as possible.

- Since TCP products use polyimide as their base film, the film expands when it absorbs

moisture. Although the packaging is moisture proof, TCP products should be used as soon after

opening as possible.

### (5) Other Items

- We recommend the use of the sprocket holes in the stamped product parts in positioning TCP products during individual punching.

- Since lead tape has a poor ability to withstand heat, and shrinks when heated, do not apply high temperatures to the lead tape.

- Bending TCP products can introduce cracks in the solder resist. Care should be taken to avoid bending when handling TCP products.

- When stacking TCP product boxes (the original packaging) for storage, do not stack more than 10 high.

- Do not apply large mechanical shocks to TCP product packaging.

# **Package Information**

### **Package Information**

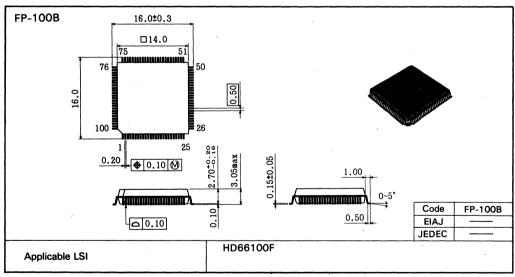

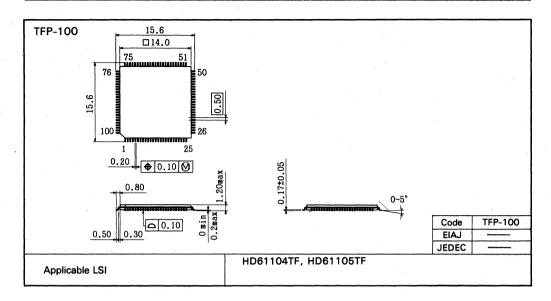

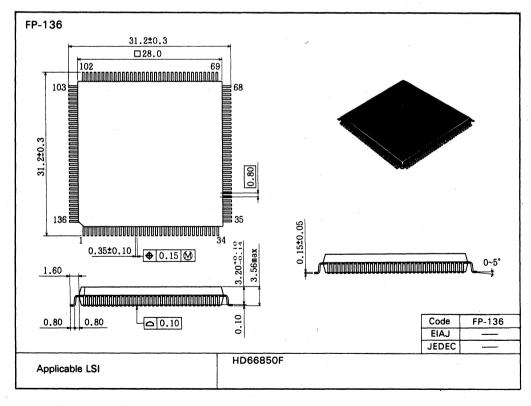

The Hitachi LCD driver devices use plastic flat packages to reduce the size of the

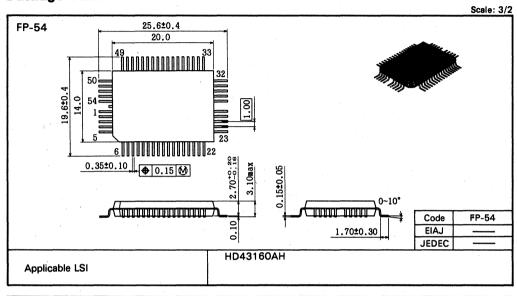

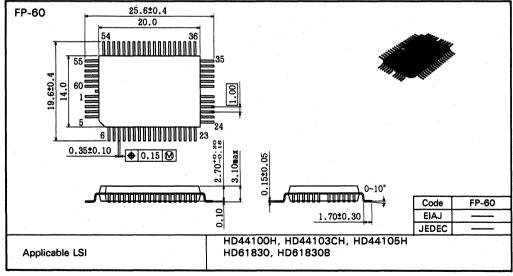

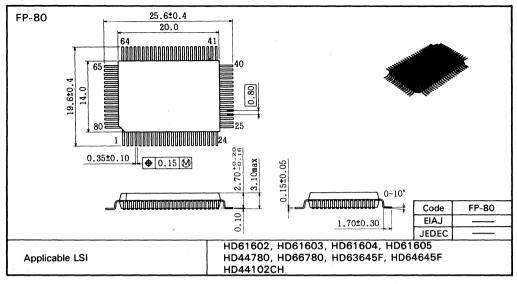

equipment in which they are incorporated and provide higher density mounting by utilizing the features of thin liquid crystal display elements.

### **Package Dimensions**

# Package Information

# Package Information

### 1. Views on Quality and Reliability

Hitachi's basic quality aims are to meet individual user's purchase purpose and quality required, and to be at a satisfactory quality level considering general marketability. Quality required by users is specifically clear if the contract specification is provided. If not, quality required is not always definite. In both cases, Hitachi tries to assure reliability so that semiconductor devices delivered can perform their function in actual operating circumstances. To realize this quality in the manufacturing process, the key points should be to establish a quality control system in the process and to enhance the quality ethic.

In addition, quality required by users of semiconductor devices is going toward higher levels as performance of electronic system in the market is increasing and expanding in size and application fields. To cover the situation, Hitachi is performing the following:

- Building in reliability in design at the stage of new product development.

- Buliding in quality at the sources of the manufacturing process.

- Executing stricter inspection and reliability confirmation of final products.

- Making quality levels higher with field data feedback.

- Cooperating with research laboratories for higher quality and reliability.

With the views and methods mentioned above, utmost efforts are made to meet users' requirements.

# 2. Reliability Design of Semiconductor Devices

### 2.1 Reliability Targets

The reliability target is the important factor in manufacture and sales as well as performance and price. It is not practical to rate reliability targets with failure rates under certain common test conditions. The reliability target is determined corresponding to the character of equipment taking design, manufacture, inner process quality control, screening and test method, etc. into consideration, and considering the operating circumstances of equipment the semiconductor device is used in, reliability target of the system, derating applied in design, operating condition, maintenance, etc.

### 2.2 Reliability Design

To achieve the reliability required based on reliability targets, timely study and execution

of design standardization, device design (including process design, structure design), design review, reliability test are essential.

### 2.2.1 Design Standardization

Establishment of design rules, and standardization of parts, material and process are necessary. To establish design rules, critical quality and reliability items are always studied at circuit design, device design, layout design, etc. Therefore, as long as standardized process, material, etc. are used, reliability risk is extremely small even in newly developed devices, except in cases where special functions are needed.

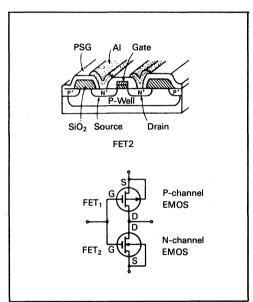

### 2.2.2 Device Design

It is important in device design to consider the total balance of process design, structure design, circuit and layout design. Especially when new processes and new materials are employed, careful technical study is executed prior to device development.

### 2.2.3 Reliability Evaluation by Test Site

Test site is sometimes called test pattern. It is a useful method for design and process reliability evaluation of ICs and LSIs which have complicated functions.

Purposes of test site are:

- · Making fundamental failure mode clear

- Analysis of relation between failure mode and manufacturing process condition

- Search for failure mechanism analysis

Establishment of QC point in manufactur-

- Establishment of QC point in manufacturing

Evaluation by test site is effective because:

- Common fundamental failure mode and failure machanism in devices can be evaluated.

- Factors dominating failure mode can be picked up, and comparison can be made with processes that have been experienced in field

- Relation between failure causes and manufacturing factors can be analyzed.

- · Easy to run tests.

- · Etc.

#### 2.3 Design Review

Design review is an organized method to confirm that a design satisfies the required performance (including users') and that design work follows the specified methods, and whether or not improved technical items accumulated in test data of individual major

fields and field data are effectively built in. In addition, from the standpoint of enhancement of the competitive power of products, the major purpose of the design review is to ensure quality and reliability of the products. In Hitachi, design reviews are performed from the planning stage for new products and even for design changed products. Items discussed and determined at design review are as follows:

- Description of the products based on specified design documents.

- From the standpoint of the specialties of individual participants, design documents are studied, and if unclear matter is found, calculation, experiments, investigation, etc. will be carried out.

- Determine contents of reliability and methods, etc. based on design documents and drawings.

- 4. Check process ability of manufacturing line to achieve design goal.

- 5. Discussion about preparation for produc-

- Planning and execution of subprograms for design changes proposed by individual specialists, and for tests, experiments and calculation to confirm the design changes.

- 7. Reference of past failure experiences with similar devices, confirmation of methods to prevent them, and planning and execution of test programs for confirmation of them. These studies and decisions are made using check lists made individually depending on the objects.

### 3. Quality Assurance System of Semiconductor Devices

### 3.1 Activity of Quality Assurance

General views of overall quality assurance in Hitachi are:

- Problems in an individual process should be solved in the process. Therefore, at final product stage, the potential failure factors have been already removed.

- Feedback of information should be used to ensure satisfactory level of process capability.

- To assure required reliability as a result of the items mentioned above is the purpose of quality assurance.

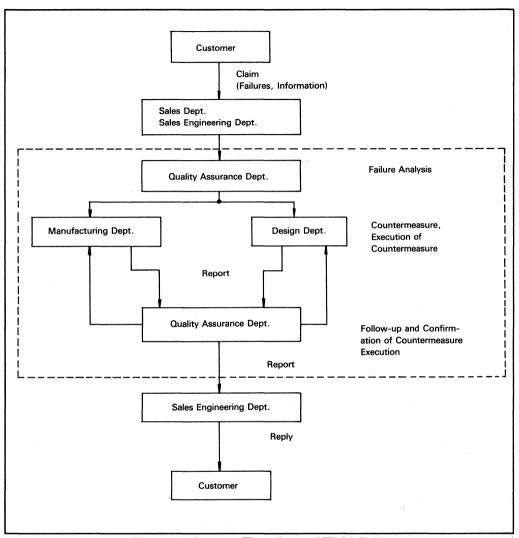

The following discusses device design, quality approval at mass production, inner process quality control, product inspection and reliability tests.

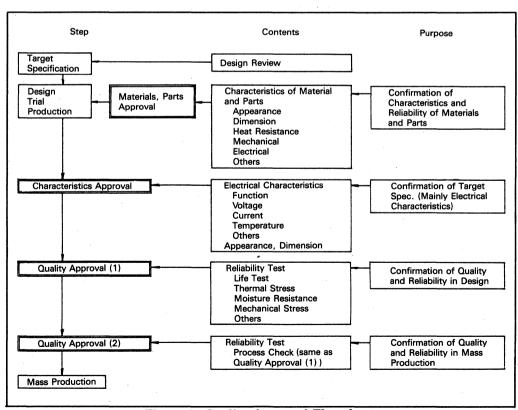

#### 3.2 Quality Approval

To ensure required quality and reliability, quality approval is carried out at the trial production stage of device design and the mass production stage based on reliability design as described in section 2.

Hitachi's views on quality approval are:

- A third party must perform approval objectively from the standpoint of customers.

- Fully consider past failure experiences and information from the field.

- Approval is needed for design change or work change.

- Intensive approval is executed on parts material and process.

- Study process capability and variation factor, and set up control points at mass production stage.

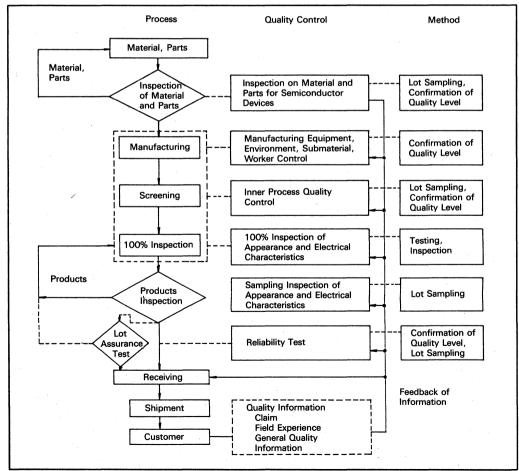

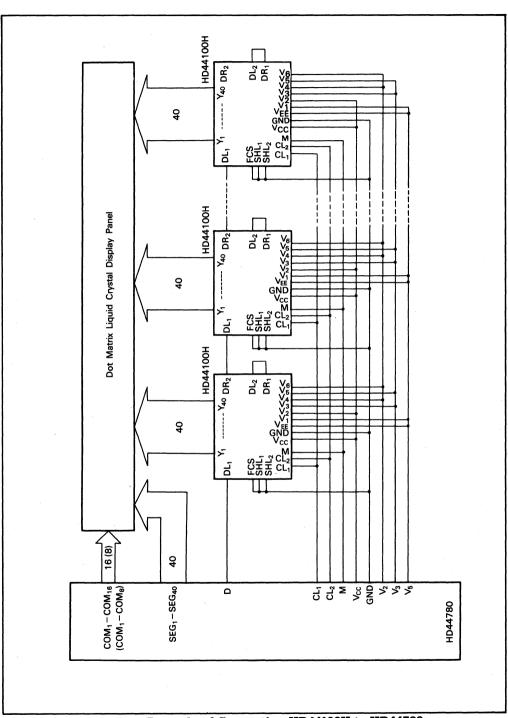

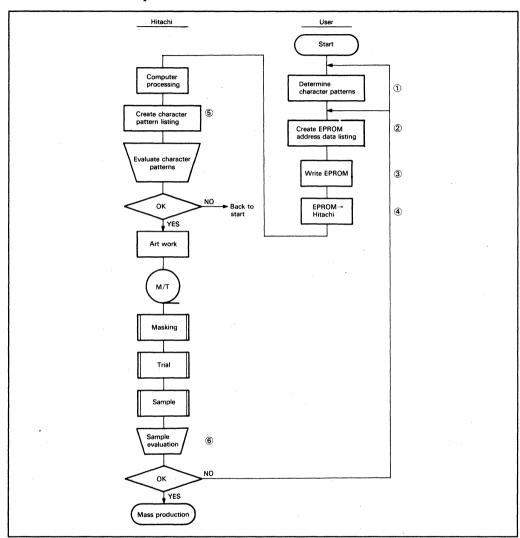

Considering the views mentioned above, figure 1 shows how quality approval is performed.

# 3.3 Quality and Reliability Control at Mass Production

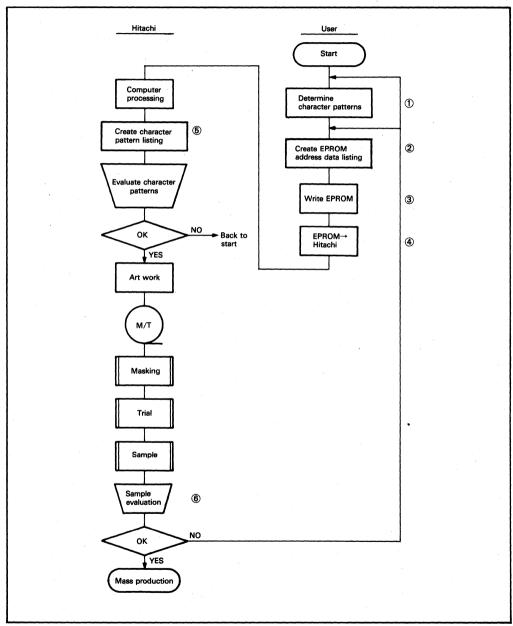

For quality assurance of products in mass production, quality control execution is divided organically by function between manufacturing department and quality assurance department, and other related departments. The total function flow is shown in figure 2. The main points are described below.

# 3.3.1 Quality Control of Parts and Material

As the performance and the reliability of semiconductor devices improve, the importance of quality control of material and parts (crystal, lead frame, fine wire for wire bonding, package) to build products, and materials needed in manufacturing process (mask pattern and chemicals) increases. Besides quality approval on parts and materials stated in section 3.2, the incoming inspection is also key in quality control of parts and materials. The incoming inspection is performed based on an incoming inspection specification, following purchase specification and drawings, and sampling inspection is executed based mainly on MIL-STD-105D.

The other activities of quality assurance are as follows:

- 1. Outside vendor technical information meeting

- Approval on outside vendors, and guidance of outside vendors

- 3. Physical chemical analysis and test

The typical check points of parts and materials are shown in table 1.

### 3.3.2 Inner Process Quality Control

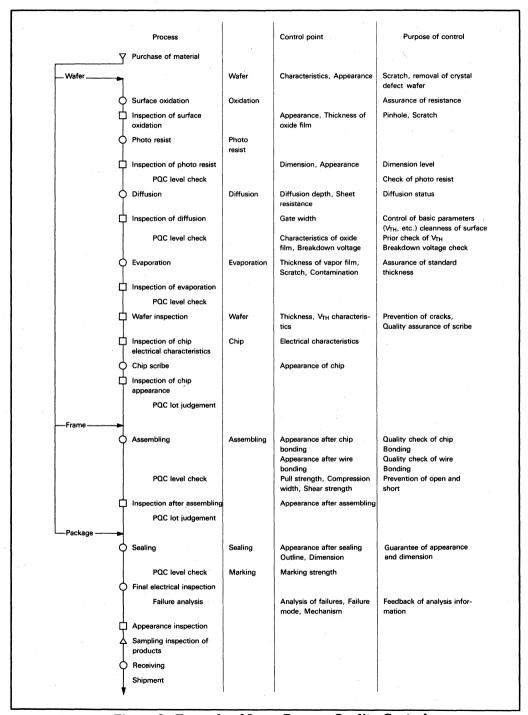

Inner process quality control performs a very important function in quality assurance of a semiconductor devices. The following is a description of control of semifinal products, final products, manufacturing facilities, measuring equipments, circumstances and submaterials. The quality control in the manufacturing process is shown in figure 3 corresponding to the manufacturing process.

1. Quality Control of Semifinal Products and Final Production Products

Potential failure factors of semiconductor devices should be removed in manufacturing process. To achieve this, check points are setup in each process, and products that have potential failure factors are not transferred to the next process. For high reliability semiconductor devices, especially manufacturing line is carefully selected, and the quality control in the

manufacturing process is tightly executed: Strict check on each process and each lot, 100% inspection to remove failure factor caused by manufacturing variation, and necessary screening, such as high temperature aging and temperature cycling. Contents of inner process quality control are:

- Condition control on individual equipment and workers, and sampling check of semifinal products.

- · Proposal and carrying-out of work improvement

- · Education of workers

- · Maintenance and improvement of yield

- Detection of quality problems, and execution of countermeasures

- · Transmission of information about quality

- 2. Quality Control of Manufacturing Facilities and Measuring Equipment Equipment for manufacturing semicon-

Figure 1 Quality Approval Flowchart

ductor devices have been developing extraordinarily, with required high performance devices and production inprovements. They are important factors to determine quality and reliability. In Hitachi, automation of manufacturing equipment is promoted to improve manufacturing variation, and controls maintain proper operation and function of high performance equipment. Maintenance inspection for quality control is performed daily based on related specifications, and also periodical inspections. At the inspection, inspection points listed in the specification are checked one by one to avoid any omissions. During adjustment and maintenance of measuring equipment, maintenance number and specifications are checked one by one to maintain and improve quality.

3. Quality Control of Manufacturing Circumstances and Submaterials

Quality and reliability of semiconductor

devices is greatly affected by manufacturing process. Therefore, manufacturing circumstances (temperature, humidity, dust) and the control of submaterials (gas, pure water) used in manufacturing process are intensively controlled. Dust control is described in more detail below.

Dust control is essential to realize higher integration and higher reliability of devices. In Hitachi, maintenance and

Figure 2 Flowchart of Quality Control in Manufacturing Process

improvement of cleanness and manufacturing site cleanness are executed paying close attention to buildings, facilities, airconditioning systems, packaging materials, clothes, work, etc., and periodical inspection for floating dust in room, falling dust, and floor dust.

# 3.3.3 Final Product Inspection and Reliability Assurance

Final Product Inspection

Lot inspection is done by quality assurance department for products that were judged to be 100% good in tests, which is

the final process in the manufacturing department. Though 100% good products is expected, sampling inspection is executed to prevent inclusion of failed products by mistake, etc. The inspection is executed not only to confirm that the products meet users' requirements, but to consider potential trouble factors. Lot inspection is executed based on MIL-STD-105D.

Reliability Assurance Tests

To assure reliability of semiconductor devices, periodical reliability tests and reliability tests on individual manufacturing lots required by user are performed.

Table 1 Quality Control Check Points of Material and Parts (Example)

| Material, Parts          | Important Control Items    | Points to Check                     |  |  |

|--------------------------|----------------------------|-------------------------------------|--|--|

| Wafer                    | Appearance                 | Damage and contamination on surface |  |  |

|                          | Dimension                  | Flatness                            |  |  |

|                          | Sheet resistance           | Resistance                          |  |  |

|                          | Defect density             | Defect numbers                      |  |  |

|                          | Crystal axis               |                                     |  |  |

| Mask                     | Appearance                 | Defect numbers, scratch             |  |  |

|                          | Dimension                  | Dimension level                     |  |  |

|                          | Registration               |                                     |  |  |

|                          | Gradation                  | Uniformity of gradation             |  |  |

| Fine wire for wire bond- | Appearance                 | Contamination, scratch, bend, twist |  |  |

| ing                      | Dimension                  |                                     |  |  |

|                          | Purity                     | Purity level                        |  |  |

|                          | Elongation ratio           | Mechanical strength                 |  |  |

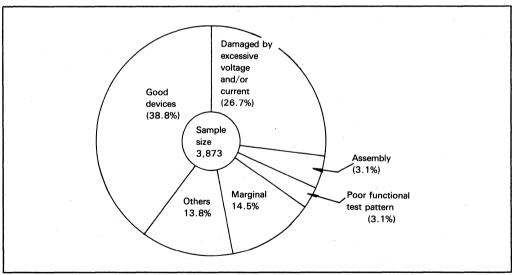

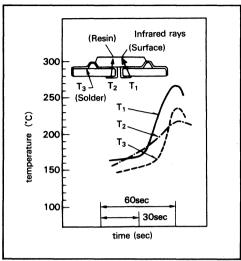

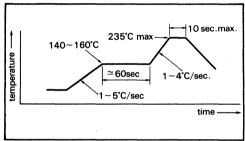

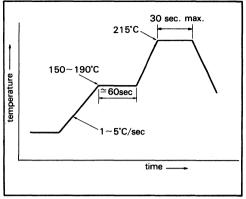

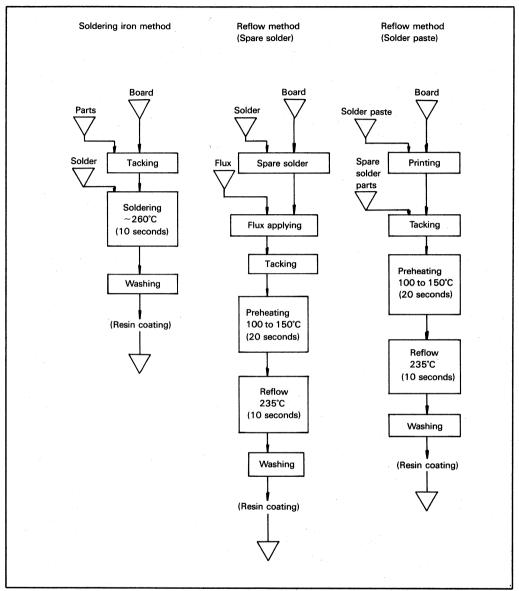

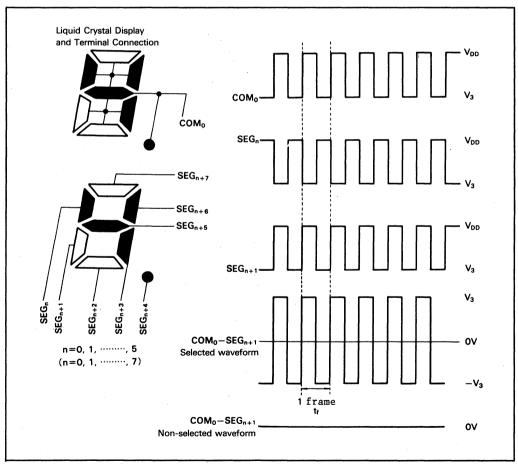

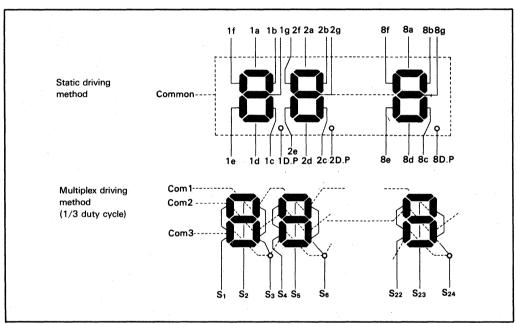

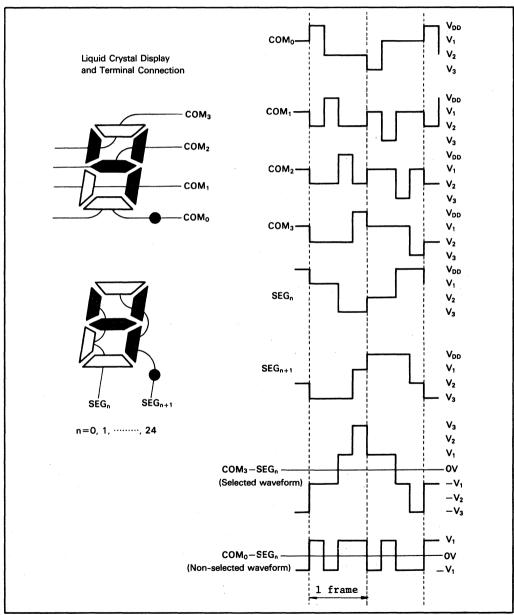

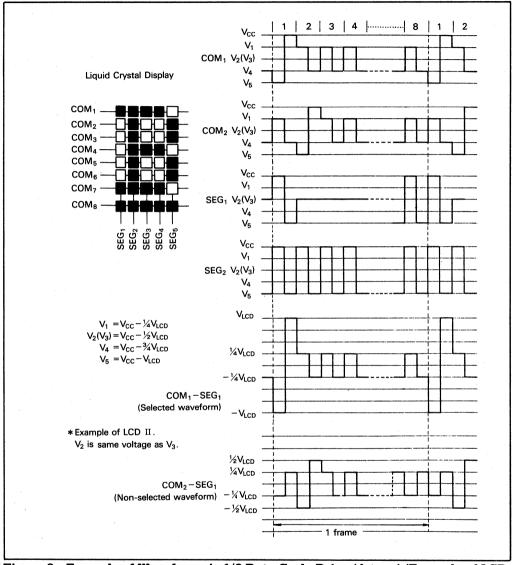

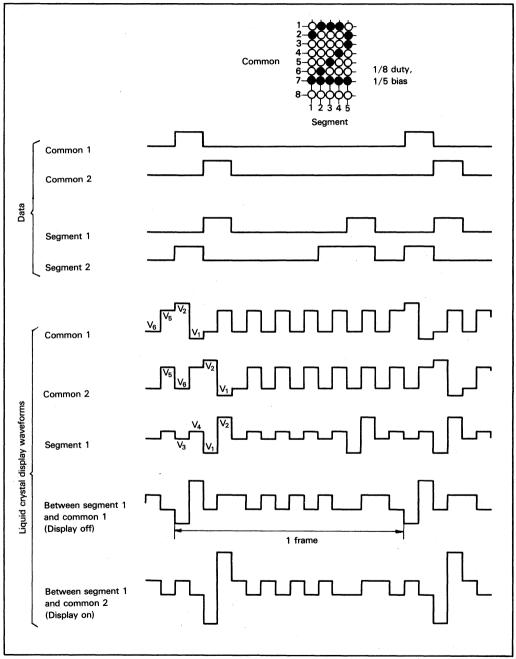

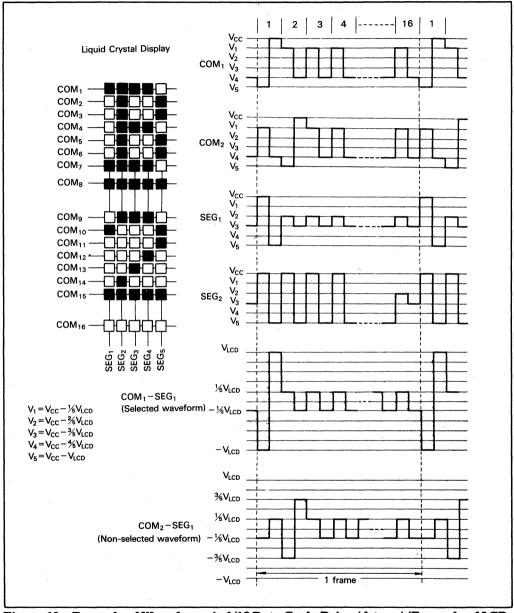

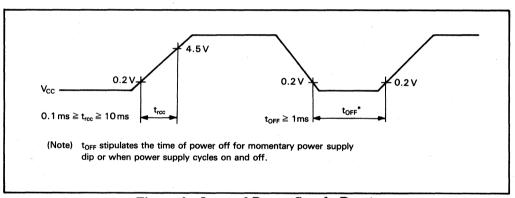

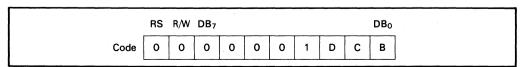

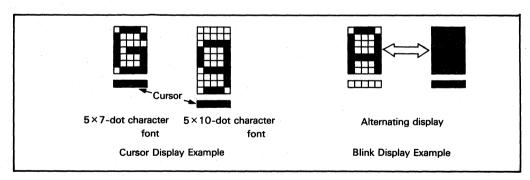

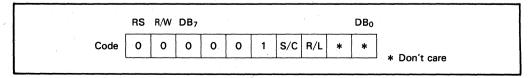

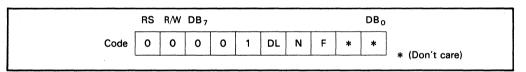

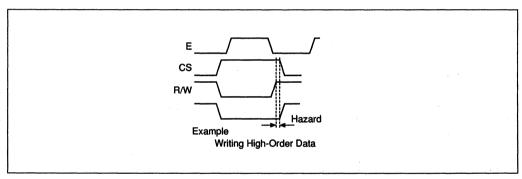

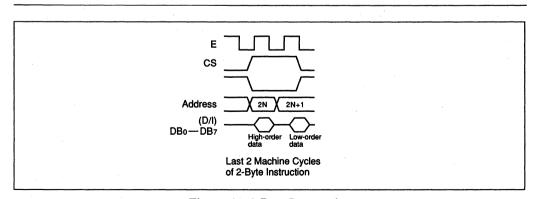

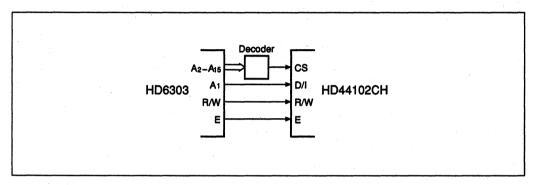

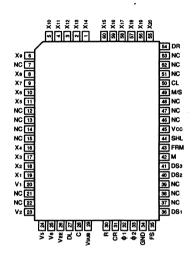

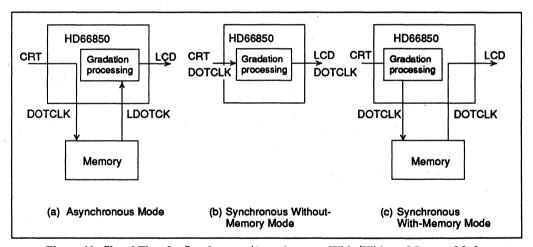

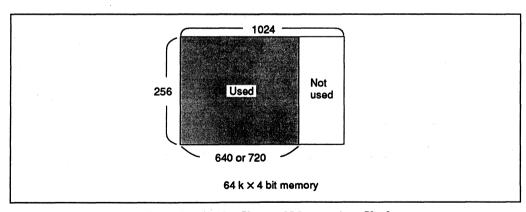

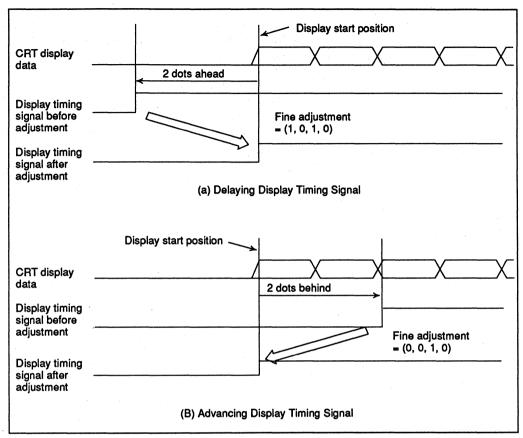

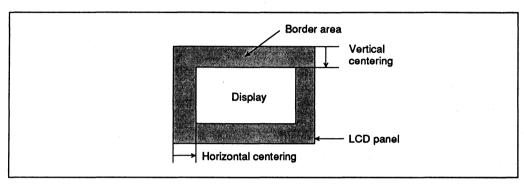

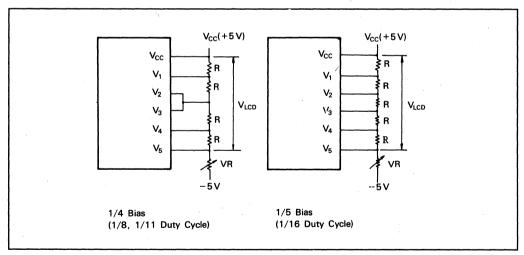

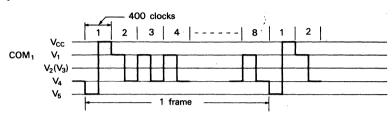

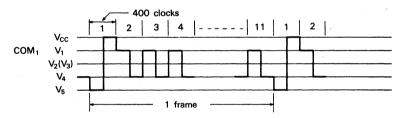

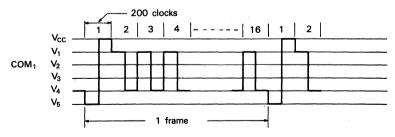

| Frame                    | Appearance                 | Contamination, scratch              |  |  |