# True Color VGA Family CL-GD542X

**Technical Reference Manual**

#### **Notice**

Cirrus Logic Inc. has made best efforts to ensure that the information contained in this document is accurate and reliable. However, the information is subject to change without notice. No responsibility is assumed by Cirrus Logic Inc. for the use of this information, nor for infringements of patents or other rights of third parties. This document is the property of Cirrus Logic Inc. and implies no license under patents, copyrights, or trade secrets. No part of this publication may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photographic, or otherwise, or used as the basis for manufacture or sale of any items without the prior written consent of Cirrus Logic Inc. Cirrus Logic, AutoMap, Fair Share, FeatureChips, Good Data, MediaDAC, MotionVideo, MVA, PicoPower, SimulSCAN, S/LA, SofTarget, UXART, Vision Port, Wave-Port, WIC, and WindowInterChip are trademarks of Cirrus Logic Inc. Other trademarks in this document belong to their respective companies. Cirrus Logic Inc. products are covered by the following U.S. patents: 4,293,783; Re. 31,287; 4,763,332; 4,777,635; 4,839,896; 4,931,946; 4,975,828; 4,979,173; 5,032,981; 5,122,783; 5,131,015; 5,140,595; 5,157,618; 5,179,292; 5,185,602; 5,220,295; 5,241,642; 5,276,856; 5,280,488; 5,287,241; 5,291,499; 5,293,159; 5,293,474; 5,297,184; 5,298,915; 5,300,835; 5,311,460; 5,313,224; 5,327,128; 5,329,554; 5,351,231; 5,359,631; 5,384,524; 5,384,786; 5,388,083; 5,396,133; 5,402,506; 5,402,513; 5,406,279; 5,406,613. Additional patents pending.

# **Revision History**

This technical reference manual has been modified to incorporate a new member of the True Color VGA family, the CL-GD5425. All pertinent information has been added, including:

- · Functional descriptions

- · Pin diagrams and descriptions

- Bus interface specifications

- Timing considerations

- Register information

- BIOS functions

- Schematics

- TV output support

- · Glossary definitions

# FOR THE LATEST SCHEMATICS, PLEASE CONTACT CIRRUS LOGIC.

This document was originally published in May, 1995.

# **Table of Contents**

| 1. | INT | FRODUCTION                                                  | 1-2  |

|----|-----|-------------------------------------------------------------|------|

|    | 1.1 | Scope of Document                                           | 1-2  |

|    | 1.2 | Applicable Chip Types                                       | 1-2  |

|    | 1.3 | Intended Audience                                           | 1-2  |

|    | 1.4 | Conventions                                                 | 1-2  |

| 2. | OV  | 'ERVIEW                                                     | 2-2  |

|    | 2.1 | Features                                                    | 2-2  |

|    | 2.2 | Chip Architecture                                           | 2-4  |

|    |     | 2.2.1 Host Access to CL-GD542X Registers                    | 2-5  |

|    |     | 2.2.2 Host Access to Display Memory                         | 2-5  |

|    |     | 2.2.3 Display Access to Display Memory                      | 2-5  |

|    |     | 2.2.4 Display Memory Refresh                                | 2-5  |

|    | 2.3 | Major Components                                            | 2-6  |

|    |     | 2.3.1 Sequencer                                             | 2-6  |

|    |     | 2.3.2 CRT Controller                                        | 2-7  |

|    |     | 2.3.3 Graphics Controller                                   | 2-8  |

|    |     | 2.3.4 Attribute Controller                                  | 2-10 |

|    |     | 2.3.5 Dual-Frequency Synthesizer                            | 2-11 |

|    |     | 2.3.6 Palette DAC                                           | 2-12 |

|    | 2.4 | Hardware/Software Compatibility                             | 2-13 |

|    | 2.5 | Video Subsystem Architecture                                | 2-13 |

| 3. | DA  | TA BOOK                                                     | 3-3  |

|    |     | Contents                                                    | 3-6  |

|    |     | Conventions                                                 | 3-9  |

|    | 1.  | Pin Information                                             | 3-11 |

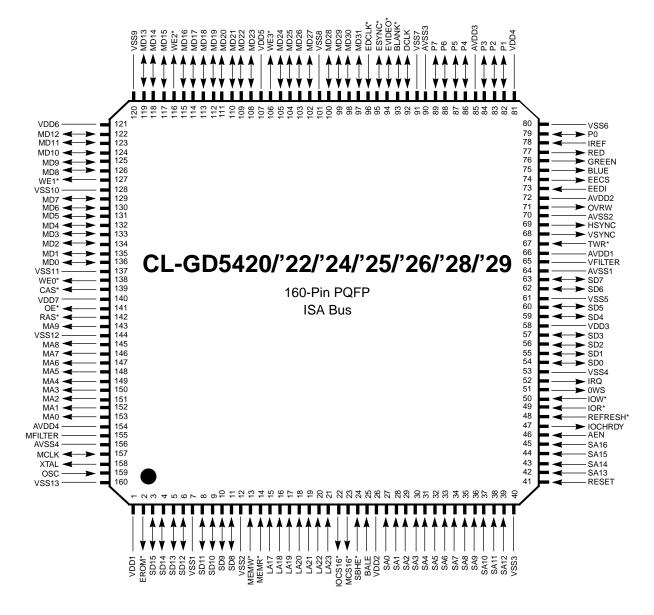

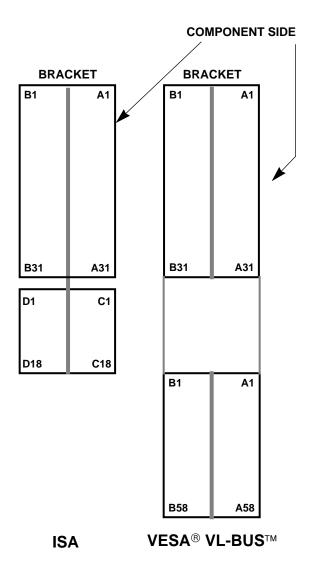

|    | 1.1 | Pin Diagram (ISA Bus)                                       | 3-11 |

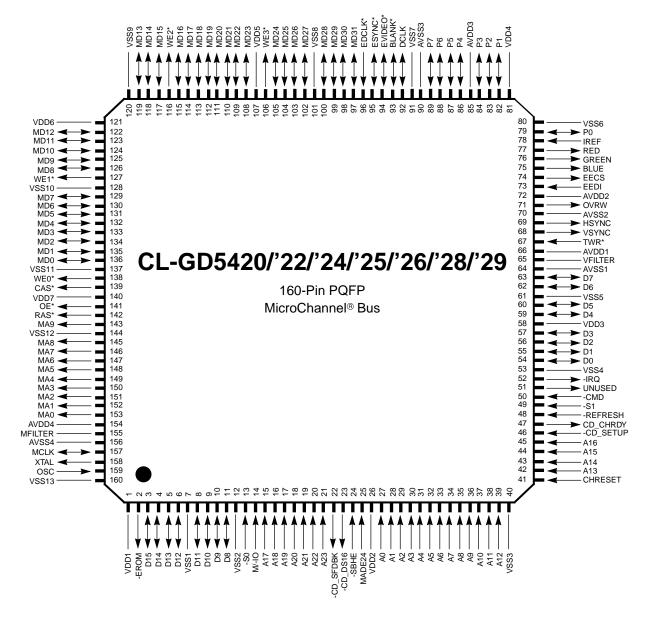

|    | 1.2 | Pin Diagram (MicroChannel® Bus)                             | 3-12 |

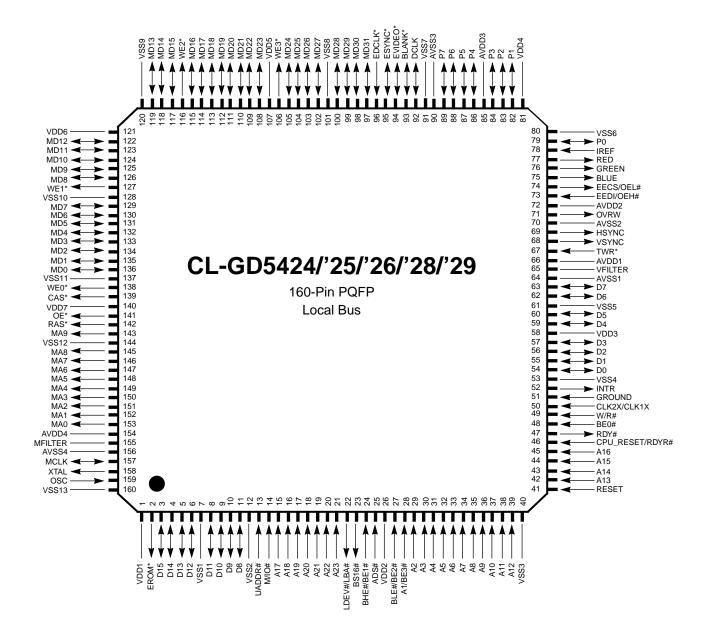

|    | 1.3 | Pin Diagram (Local Bus)                                     | 3-13 |

|    | 1.4 | Pin Summary                                                 | 3-15 |

|    | 2.  | Detailed Pin Descriptions                                   | 3-23 |

|    | 2.1 | Host Interface — ISA Bus Mode                               | 3-23 |

|    | 2.2 | Host Interface — MicroChannel® Bus Mode                     | 3-27 |

|    | 2.3 | Host Interface — Local Bus (CL-GD5424/'25/'26/'28/'29 only) | 3-30 |

|    | 2.4 | Dual-Frequency Synthesizer Interface                        | 3-33 |

|    | 2.5 | Video Interface                                             | 3-34 |

|    | 2.6 | Display Memory Interface                                    | 3-36 |

|    | 2.7 | Miscellaneous Pins                                          | 3-37 |

|    | 2.8 | Power Pins                                                  | 3-38 |

| 3. | DA   | TA BOOK (cont.)                                               |       |  |  |

|----|------|---------------------------------------------------------------|-------|--|--|

|    | 3.   | Functional Description                                        | 3-39  |  |  |

|    | 3.1  | General                                                       | 3-39  |  |  |

|    | 3.2  | Functional Blocks                                             | 3-39  |  |  |

|    | 3.3  | Functional Operation                                          | 3-41  |  |  |

|    | 3.4  | Performance                                                   | 3-42  |  |  |

|    | 3.5  | Compatibility                                                 | 3-42  |  |  |

|    | 3.6  | Board Testability                                             | 3-42  |  |  |

|    | 4.   | CL-GD542X Configuration Tables                                | 3-43  |  |  |

|    | 4.1  | Video Modes                                                   | 3-43  |  |  |

|    | 4.2  | Configuration Register, CF1                                   | 3-47  |  |  |

|    | 4.3  | Host Interface Signals                                        | 3-48  |  |  |

|    | 5.   | VGA Register Port Map                                         | 3-49  |  |  |

|    | 6.   | CL-GD542X Registers                                           | 3-51  |  |  |

|    | 7.   | Electrical Specifications                                     | 3-57  |  |  |

|    | 7.1  | Absolute Maximum Ratings                                      | 3-57  |  |  |

|    | 7.2  | DC Specifications (Digital)                                   | 3-58  |  |  |

|    | 7.3  | DC Specifications (Palette DAC)                               | 3-59  |  |  |

|    | 7.4  | DC Specifications (Frequency Synthesizer)                     | 3-59  |  |  |

|    | 7.5  | DAC Characteristics                                           | 3-60  |  |  |

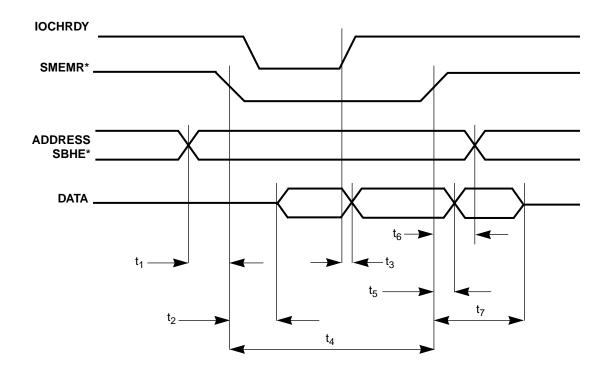

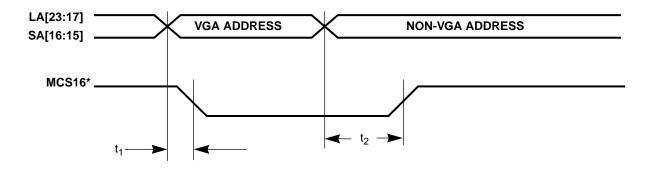

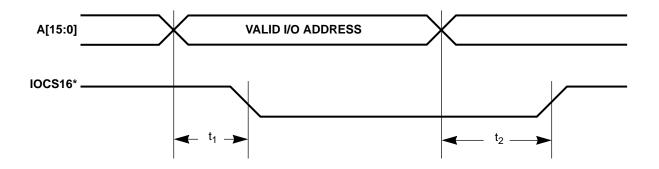

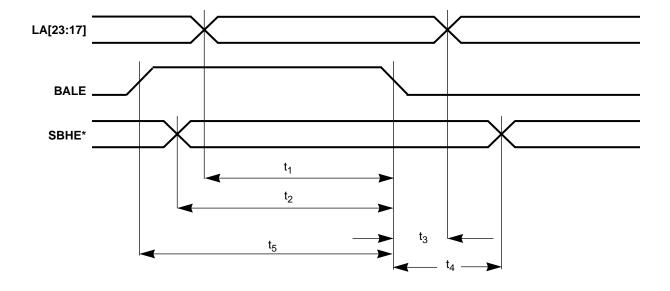

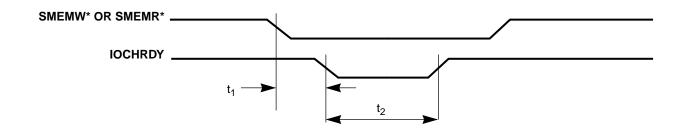

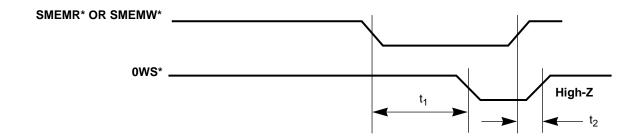

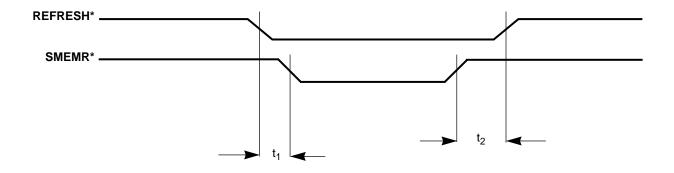

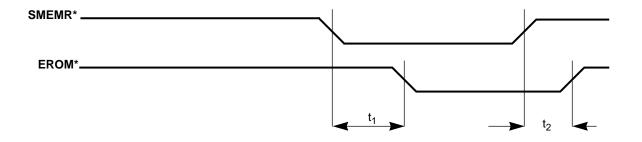

|    | 7.6  | List of Waveforms                                             | 3-61  |  |  |

|    | 8.   | Package Dimensions                                            | 3-105 |  |  |

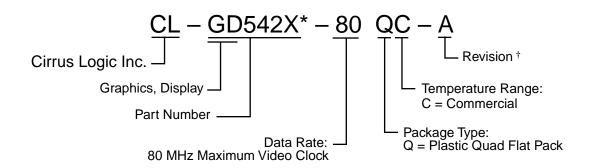

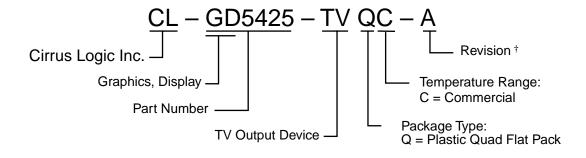

|    | 9.   | Ordering Information Examples                                 | 3-106 |  |  |

| ŀ. | EX   | TERNAL AND GENERAL REGISTERS                                  | 4-2   |  |  |

|    | 4.1  | POS 94: 102 Access Control Register (Write only)              | 4-3   |  |  |

|    | 4.2  | POS102: POS102 Register                                       | 4-4   |  |  |

|    | 4.3  | VSSM: Sleep Address Register (CL-GD5424/'25/'26/'28/'29 only) | 4-5   |  |  |

|    | 4.4  | VSSM: Adapter Sleep Address Register (Write only)             | 4-6   |  |  |

|    | 4.5  | MISC: Miscellaneous Output Register                           | 4-7   |  |  |

|    | 4.6  | FC: Feature Control Register                                  | 4-9   |  |  |

|    | 4.7  | FEAT: Input Status Register 0                                 | 4-10  |  |  |

|    | 4.8  | STAT: Input Status Register 1                                 | 4-11  |  |  |

|    | 4.9  | Pixel Mask Register                                           | 4-12  |  |  |

|    | 4.10 | Pixel Address Register (Read Mode — Write only)               | 4-13  |  |  |

|    | 4.11 | DAC State Register (Read only)                                | 4-14  |  |  |

|    | 4.12 | Pixel Address Register (Write Mode)                           | 4-15  |  |  |

|    | 4.13 | Pixel Data Register                                           | 4-16  |  |  |

| 5. | VG   | A SEQUENCER REGISTERS                               | . 5-2  |

|----|------|-----------------------------------------------------|--------|

|    | 5.1  | SRX: Sequencer Index Register                       | 5-3    |

|    | 5.2  | SR0: Reset Register                                 | 5-4    |

|    | 5.3  | SR1: Clocking Mode Register                         | 5-5    |

|    | 5.4  | SR2: Plane Mask Register                            | 5-7    |

|    | 5.5  | SR3: Character Map Select Register                  | 5-8    |

|    | 5.6  | SR4: Memory Mode Register                           | 5-10   |

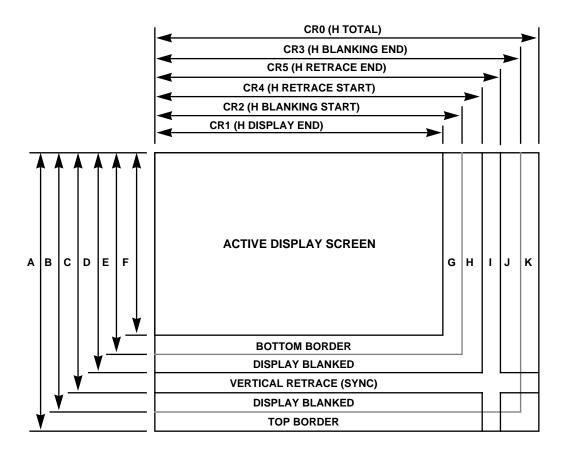

| 6. | CR   | T CONTROLLER REGISTERS                              | 6-2    |

|    | 6.1  | CRX: CRTC Index Register                            | 6-3    |

|    | 6.2  | CR0: Horizontal Total Register                      | 6-4    |

|    | 6.3  | CR1: Horizontal Display End Register                | 6-7    |

|    | 6.4  | CR2: Horizontal Blanking Start Register             | 6-8    |

|    | 6.5  | CR3: Horizontal Blanking End Register               | 6-9    |

|    | 6.6  | CR4: Horizontal Sync Start Register                 | . 6-11 |

|    | 6.7  | CR5: Horizontal Sync End Register                   | . 6-12 |

|    | 6.8  | CR6: Vertical Total Register                        | . 6-14 |

|    | 6.9  | CR7: Overflow Register                              | 6-15   |

|    | 6.10 | CR8: Screen A Preset Row Scan Register              | 6-16   |

|    | 6.11 | CR9: Character Cell Height Register                 | 6-17   |

|    | 6.12 | CRA: Text Cursor Start Register                     | 6-18   |

|    | 6.13 | CRB: Text Cursor End Register                       | 6-19   |

|    | 6.14 | CRC: Screen Start Address High Register             | 6-20   |

|    | 6.15 | CRD: Screen Start Address Low Register              | 6-21   |

|    | 6.16 | CRE: Text Cursor Location High Register             | 6-22   |

|    | 6.17 | CRF: Text Cursor Location Low Register              | 6-23   |

|    | 6.18 | CR10: Vertical Sync Start Register                  | 6-24   |

|    | 6.19 | CR11: Vertical Sync End Register                    | 6-25   |

|    | 6.20 | CR12: Vertical Display End Register                 | 6-27   |

|    | 6.21 | CR13: Offset Register                               | 6-28   |

|    | 6.22 | CR14: Underline Row Scanline Register               | 6-29   |

|    | 6.23 | CR15: Vertical Blank Start Register                 | 6-30   |

|    | 6.24 | CR16: Vertical Blank End Register                   | 6-31   |

|    | 6.25 | CR17: Mode Control Register                         | 6-32   |

|    | 6.26 | CR18: Line Compare Register                         | 6-34   |

|    | 6.27 | CR22: Graphics Data Latches Readback Register       | 6-35   |

|    | 6.28 | CR24: Attribute Controller Toggle Readback Register | 6-36   |

|    | 6 29 | CR26: Attribute Controller Index Readback Register  | 6-37   |

| 7. | VG   | A GRAPHICS CONTROLLER REGISTERS                                               | 7-2  |

|----|------|-------------------------------------------------------------------------------|------|

|    | 7.1  | GRX: Graphics Controller Index Register                                       | 7-3  |

|    | 7.2  | GR0: Set/Reset Register                                                       | 7-4  |

|    | 7.3  | GR1: Set/Reset Enable Register                                                | 7-5  |

|    | 7.4  | GR2: Color Compare Register                                                   | 7-6  |

|    | 7.5  | GR3: Data Rotate Register                                                     | 7-7  |

|    | 7.6  | GR4: Read Map Select Register                                                 | 7-8  |

|    | 7.7  | GR5: Mode Register                                                            | 7-9  |

|    | 7.8  | GR6: Miscellaneous Register                                                   | 7-12 |

|    | 7.9  | GR7: Color Don't Care Register                                                | 7-13 |

|    | 7.10 | GR8: Bit Mask Register                                                        | 7-14 |

| 8. | AT   | FRIBUTE CONTROLLER REGISTERS                                                  | 8-2  |

|    | 8.1  | ARX: Attribute Controller Index Register                                      | 8-3  |

|    | 8.2  | AR0-ARF: Attribute Controller Palette Registers                               | 8-4  |

|    | 8.3  | AR10: Attribute Controller Mode Register                                      | 8-5  |

|    | 8.4  | AR11: Overscan (Border) Color Register                                        | 8-7  |

|    | 8.5  | AR12: Color Plane Enable Register                                             | 8-8  |

|    | 8.6  | AR13: Pixel Panning Register                                                  | 8-9  |

|    | 8.7  | AR14: Color Select Register                                                   | 8-10 |

| 9. | EX   | FENSION REGISTERS                                                             | 9-2  |

|    | 9.1  | SR6: Unlock ALL Extensions Register                                           | 9-5  |

|    | 9.2  | SR7: Extended Sequencer Mode Register                                         | 9-6  |

|    | 9.3  | SR8: EEPROM Control Register                                                  | 9-8  |

|    | 9.4  | SR9, SRA: Scratch Pad 0, 1 Registers                                          | 9-10 |

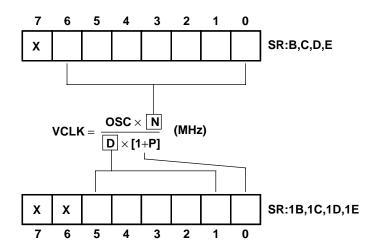

|    | 9.5  | SRB, SRC, SRD, SRE: VCLK0, 1, 2, 3 Numerator Registers                        | 9-11 |

|    | 9.6  | SRF: DRAM Control Register                                                    | 9-12 |

|    | 9.7  | SR10: Graphics Cursor X Position Register                                     | 9-14 |

|    | 9.8  | SR11: Graphics Cursor Y Position Register                                     | 9-15 |

|    | 9.9  | SR12: Graphics Cursor Attributes Register                                     | 9-16 |

|    | 9.10 | SR13: Graphics Cursor Pattern Address Offset Register                         | 9-17 |

|    | 9.11 | SR14, SR15: Scratch Pad 2, 3 Registers (CL-GD5425/'26/'28/'29 only)           | 9-18 |

|    | 9.12 | SR16: Performance Tuning Register (CL-GD5424/'25/'26/'28/'29 only)            | 9-19 |

|    | 9.13 | SR17: Configuration Readback and Extended Control Register (Except CL-GD5420) | 9-21 |

|    | 9.14 | SR18: Signature Generator Control Register (Except CL-GD5420)                 | 9-22 |

|    | 9.15 | SR19: Signature Generator Result Low Byte Register (Except CL-GD5420) .       | 9-24 |

|    |      | SR1A: Signature Generator Result High Byte Register (Except CL-GD5420)        |      |

|    | 9.17 | SR1B, SR1C, SR1D, SR1E: VCLK Denominator and Post Scalar Value Registers      | 9-26 |

| 9.18 | SR1F: BIOS ROM Write Enable and MCLK Select Register                  |      |

|------|-----------------------------------------------------------------------|------|

|      | (CL-GD5424/'25/'26/'28/'29 only)                                      |      |

|      | GR9: Offset Register 0                                                |      |

| 9.20 | GRA: Offset Register 1                                                | 9-31 |

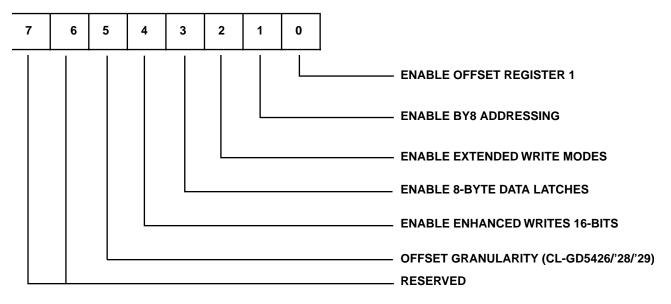

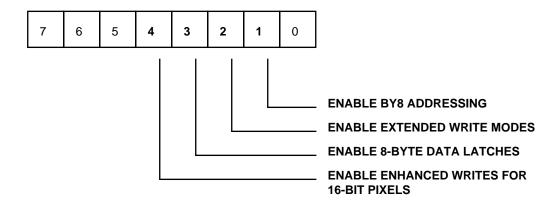

| 9.21 | GRB: Graphics Controller Mode Extensions Register                     | 9-32 |

| 9.22 | GRC: Color Key Compare Register (CL-GD5424/'25/'26/'28/'29 only)      | 9-34 |

| 9.23 | GRD: Color Key Compare Mask Register (CL-GD5424/'25/'26/'28/'29 only) | 9-35 |

| 9.24 | GRE: Miscellaneous Control Register (CL-GD5425/'28/'29 only)          | 9-36 |

| 9.25 | GR10: 16-bit Pixel Background Color High Byte Register                | 9-38 |

| 9.26 | GR11: 16-bit Pixel Foreground Color High Byte Register                | 9-39 |

| 9.27 | GR18: Extended DRAM Controls (CL-GD5429 only)                         | 9-40 |

| 9.28 | GR20: BLT Width Low Register (CL-GD5426/'28/'29 only)                 | 9-41 |

| 9.29 | GR21: BLT Width High Register (CL-GD5426/'28/'29 only)                | 9-42 |

| 9.30 | GR22: BLT Height Low Register (CL-GD5426/'28/'29 only)                | 9-43 |

| 9.31 | GR23: BLT Height High Register (CL-GD5426/'28/'29 only)               | 9-44 |

| 9.32 | GR24: BLT Destination Pitch Low Register (CL-GD5426/'28/'29 only)     | 9-45 |

| 9.33 | GR25: BLT Destination Pitch High Register (CL-GD5426/'28/'29 only)    | 9-46 |

| 9.34 | GR26: BLT Source Pitch Low Register (CL-GD5426/'28/'29 only)          | 9-47 |

| 9.35 | GR27: BLT Source Pitch High Register (CL-GD5426/'28/'29 only)         | 9-48 |

| 9.36 | GR28: BLT Destination Start Low Register (CL-GD5426/'28/'29 only)     | 9-49 |

| 9.37 | GR29: BLT Destination Start Mid Register (CL-GD5426/'28/'29 only)     | 9-50 |

| 9.38 | GR2A: BLT Destination Start High Register (CL-GD5426/'28/'29 only)    | 9-51 |

| 9.39 | GR2C: BLT Source Start Low Register (CL-GD5426/'28/'29 only)          | 9-52 |

| 9.40 | GR2D: BLT Source Start Mid Register (CL-GD5426/'28/'29 only)          | 9-53 |

| 9.41 | GR2E: BLT Source Start High Register (CL-GD5426/'28/'29 only)         | 9-54 |

| 9.42 | GR2F: BLT Write Mask Destination Register (CL-GD5429 only)            | 9-55 |

| 9.43 | GR30: BLT Mode Register (CL-GD5426/'28/'29 only)                      | 9-56 |

| 9.44 | GR31: BLT Start/Status Register (CL-GD5426/'28/'29 only)              | 9-59 |

|      | GR32: BLT Raster Operation Register (ROP) (CL-GD5426/'28/'29 only)    |      |

| 9.46 | GR34: BLT Transparent Color Low Register (CL-GD5426/'28 only)         | 9-62 |

| 9.47 | GR35: BLT Transparent Color High Register (CL-GD5426/'28 only)        | 9-63 |

| 9.48 | GR38: BLT Transparent Color Mask Low Register (CL-GD5426/'28 only)    | 9-64 |

| 9.49 | GR39: BLT Transparent Color Mask High Register (CL-GD5426/'28 only)   | 9-65 |

| 9.50 | CR19: Interlace End Register                                          | 9-66 |

| 9.51 | CR1A: Miscellaneous Control Register                                  | 9-67 |

| 9.52 | CR1B: Extended Display Controls Register                              | 9-69 |

| 9.53 | CR1C: Sync Adjust and GENLOCK Register (CL-GD5425 only)               | 9-71 |

|      | CR1D:Overlay Mode Register (CL-GD5425/'29 only)                       |      |

| 9.55 | CR25: Part Status Register                                            | 9-75 |

| 9.56 | CR27: ID Register                                                     | 9-76 |

| 9 57 | CR30: TV-Out Mode Control Register (CL-GD5425 only)                   | 9-77 |

|     | 9.58 | HDR: H   | idden DAC Register (Except CL-GD5420)                          | 9-80  |

|-----|------|----------|----------------------------------------------------------------|-------|

| 10. | VG   | A BIOS   | ò                                                              | 10-2  |

|     | 10.1 | BIOS O   | verview                                                        | 10-2  |

|     |      | 10.1.1 N | Main BIOS Features                                             | 10-2  |

|     |      | 10.1.2 E | Extended Video Mode Support                                    | 10-2  |

|     |      | 10.1.3   | Direct-Color Operation                                         | 10-2  |

|     |      | 10.1.4 H | High Performance                                               | 10-2  |

|     |      | 10.1.5   | System Integration                                             | 10-3  |

|     |      | 10.1.6   | Customization                                                  | 10-3  |

|     |      | 10.1.7   | Compatibility                                                  | 10-3  |

|     | 10.2 | CL-GD5   | 542X VGA BIOS Initialization and Power-Up Diagnostics          | 10-3  |

|     | 10.3 | Video I  | BIOS Interrupt Vectors                                         | 10-5  |

|     |      | 10.3.1   | Interrupt 10H: BIOS Video Service Routines Contents            | 10-6  |

|     | 10.4 | Descrip  | tion Of Functions                                              | 10-8  |

|     |      | 10.4.1   | Function: 00H • Set Video Mode                                 | 10-8  |

|     |      | 10.4.2   | Function: 01H • Set Cursor Type                                | 10-9  |

|     |      | 10.4.3   | Function: 02H • Set Cursor Position                            | 10-10 |

|     |      | 10.4.4   | Function: 03H • Get Cursor Position                            |       |

|     |      | 10.4.5   | Function: 04H • Get Light Pen Position                         | 10-11 |

|     |      | 10.4.6   | Function: 05H • Select Active Display Page                     | 10-11 |

|     |      | 10.4.7   | Function: 06H • Window Scroll Up                               | 10-12 |

|     |      | 10.4.8   | Function: 07H • Window Scroll Down                             | 10-12 |

|     |      | 10.4.9   | Function: 08H • Read Character/Attribute at Cursor Position    | 10-13 |

|     |      | 10.4.10  | Function: 09H • Write Character/Attribute at Cursor Position   | 10-13 |

|     |      |          | Function: 0AH • Write Character at Cursor Position             |       |

|     |      |          | Function: 0BH • CGA Palette                                    |       |

|     |      |          | Function: 0CH • Write Dot (Pixel)                              |       |

|     |      |          | Function: 0DH • Read Dot (Pixel)                               |       |

|     |      |          | Function: 0EH • Write Character to Active RAM in Teletype Mode |       |

|     |      |          | Function: 0FH • Get Video State                                |       |

|     |      |          | Function: 10H • VGA Palette                                    |       |

|     |      |          | Function: 11H • Fonts/Character Generator                      |       |

|     |      |          | Function: 12H • Alternate Select                               |       |

|     |      |          | Function: 13H • Write Teletype String                          |       |

|     |      |          | Function: 1AH • Display Combination Code                       |       |

|     |      |          | Function: 1BH • Get Functionality/State Information            |       |

|     |      |          | Function: 1CH • Save/Restore Video State                       |       |

|     |      |          | eep Mode and Display Switching                                 |       |

|     | 10.6 | Address  | s Maps                                                         | 10-47 |

# **Appendixes**

| <b>A</b> 1 | CONNECTOR PINOUTS A1-1             |                                                         |      |  |  |  |  |

|------------|------------------------------------|---------------------------------------------------------|------|--|--|--|--|

| В1         | 16-                                | 16-BIT ISA ADAPTER BOARD SCHEMATICS B1-1                |      |  |  |  |  |

| <b>B2</b>  | RESERVED                           |                                                         |      |  |  |  |  |

| В3         | 33 '486 VESA® LOCAL BUS SCHEMATICS |                                                         |      |  |  |  |  |

|            | 1.                                 | Introduction                                            | B3-2 |  |  |  |  |

|            | 2.                                 | '486 Local Bus                                          | B3-2 |  |  |  |  |

|            |                                    | 2.1 Motherboard '486 Local Bus Interface                | B3-2 |  |  |  |  |

|            |                                    | 2.2 VESA® VL-Bus™ '486 Local Bus Interface              | B3-3 |  |  |  |  |

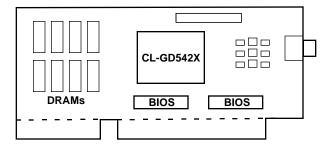

|            | 3.                                 | BIOS                                                    | B3-3 |  |  |  |  |

|            | 4.                                 | Display Memory                                          | B3-3 |  |  |  |  |

|            | 5.                                 | Monitor/Video DAC Interface                             | B3-4 |  |  |  |  |

|            | 6.                                 | Integrated Clock                                        | B3-4 |  |  |  |  |

|            | 7.                                 | Hardware Features                                       | B3-4 |  |  |  |  |

| В4         | CL.                                | -GD5425 VESA® VL-BUS™ SCHEMATICS                        | B4-1 |  |  |  |  |

| В5         | CL                                 | -GD5420-75QC-B VGA CONTROLLER                           | B5-1 |  |  |  |  |

|            | 1.                                 | Overview                                                | B5-2 |  |  |  |  |

|            | 2.                                 | Features                                                | B5-2 |  |  |  |  |

|            |                                    | 2.1 Video Clock Support                                 | B5-3 |  |  |  |  |

| В6         | TR                                 | UE COLOR MODES                                          | B6-1 |  |  |  |  |

|            | 1.                                 | Introduction                                            | B6-2 |  |  |  |  |

|            | 2.                                 | Programming for a True Color Multi-Mode Palette DAC     | B6-2 |  |  |  |  |

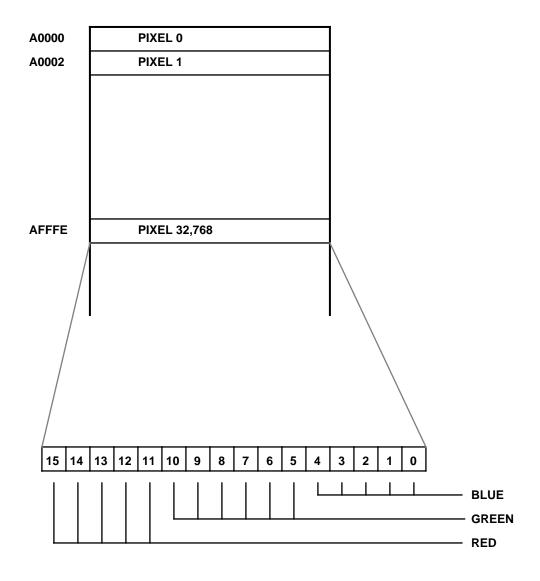

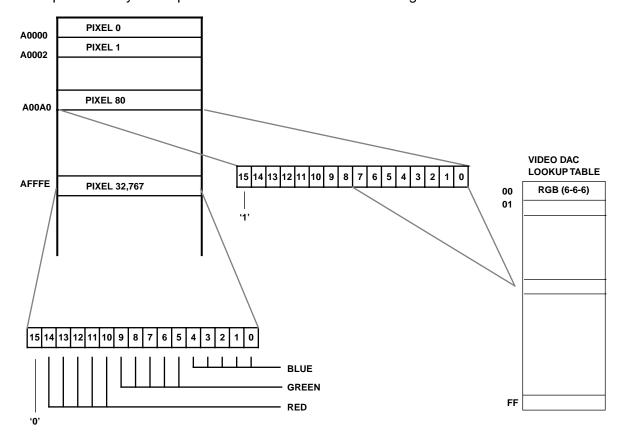

|            |                                    | 2.1 5-5-5 Mode with 32K Colors                          | B6-3 |  |  |  |  |

|            |                                    | 2.2 Mix Mode                                            | B6-3 |  |  |  |  |

|            |                                    | 2.3 5-6-5 Mode with 64K Colors                          | B6-4 |  |  |  |  |

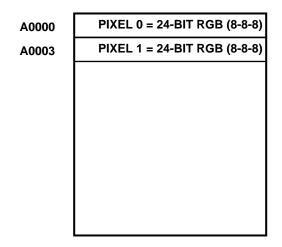

|            |                                    | 2.4 8-8-8 Mode with 16.8 Million Colors                 | B6-4 |  |  |  |  |

|            |                                    | 2.5 3-3-2 Mode with 256 Colors (CL-GD5425/'28/'29 only) | B6-5 |  |  |  |  |

|            |                                    | 2.6 8-bit Grayscale Mode (CL-GD5425/'28/'29 only)       | B6-5 |  |  |  |  |

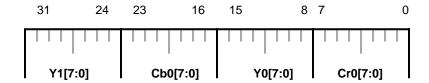

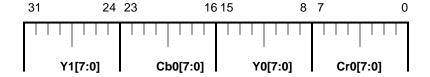

|            |                                    | 2.7 16-bit-per-pixel YCrCb Mode (CL-GD5425 only)        | B6-5 |  |  |  |  |

| <b>B7</b>  | ME                                 | MORY CONFIGURATIONS                                     | B7-1 |  |  |  |  |

| В8         | CLC                                | OCK OPTIONS                                             | B8-1 |  |  |  |  |

|            | 1.                                 | Introduction                                            | B8-2 |  |  |  |  |

|            | 2.                                 | MCLK — Memory Clock Selection                           | B8-2 |  |  |  |  |

|            | Programming MCLK Frequencyl        |                                                         |      |  |  |  |  |

|             | 4.    | VCLK — Video Clock Programming                        | B8-5   |

|-------------|-------|-------------------------------------------------------|--------|

|             |       | 4.1 Video Dot Clock (VCLKx) Selection                 | B8-7   |

|             |       | 4.2 Using MCLK as VCLK (CL-GD5428/'29 only)           | B8-8   |

| В9          | COI   | NFIGURATION NOTES                                     | B9-1   |

|             | 1.    | Introduction                                          | B9-2   |

|             | 2.    | Configuration Overview                                | B9-2   |

|             | 3.    | Configuration Notes for CL-GD5420                     | B9-4   |

|             | 4.    | Configuration Notes for CL-GD5422                     | B9-4   |

|             | 5.    | Configuration Notes for CL-GD5424/'26/'28             | B9-6   |

|             | 6.    | Configuration Notes for CL-GD5425                     | B9-8   |

|             | 7.    | Configuration Notes for CL-GD5429                     | B9-10  |

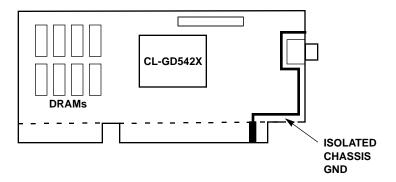

| B10         | PC    | BOARD LAYOUT CONSIDERATIONS                           | B10-1  |

|             | 1.    | Layout Considerations                                 | B10-2  |

|             | 2.    | Clock Synthesizer                                     | B10-3  |

|             | 3.    | Host Bus Interface                                    | B10-3  |

|             | 4.    | Video Output                                          | B10-3  |

|             | 5.    | Layouts Available                                     | B10-3  |

| <b>B</b> 11 | I SIG | GNATURE GENERATOR                                     | B11-1  |

| B12         | PC    | B LAYOUT CONSIDERATIONS FOR MOTHERBOARDS              | B12-1  |

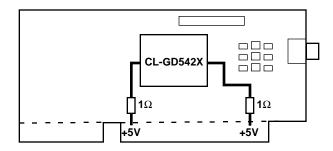

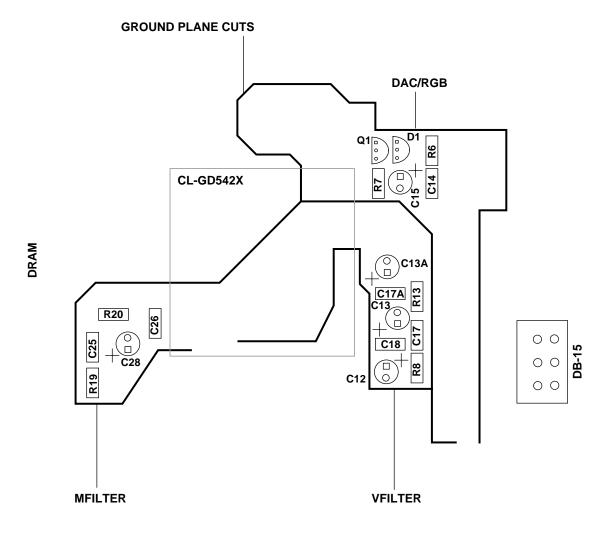

|             | 1.    | Layout Considerations (For Four Layers)               | B12-2  |

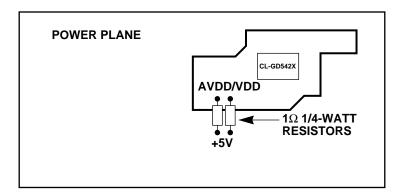

|             | 2.    | Power Plane                                           | B12-3  |

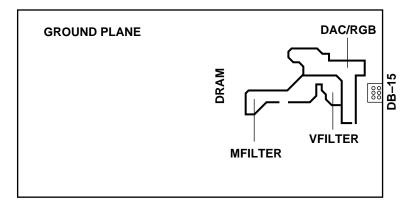

|             | 3.    | Ground Plane                                          | B12-3  |

| B13         | 3 PII | N SCAN TESTING                                        | B13-1  |

| B14         | 4 VII | DEO OVERLAY AND DAC MODE SWITCHING                    | B14-1  |

|             | 1.    | Introduction                                          | B14-2  |

|             | 2.    | Overview                                              | B14-2  |

|             | 3.    | Switch with EVIDEO*                                   | B14-5  |

|             | 4.    | Switch with Color Key                                 | B14-7  |

|             | 5.    | Switch with Color Key AND'ed with EVIDEO* (CL-GD5429) | B14-8  |

|             | 6.    | On-Chip Window Timing Generator                       | B14-9  |

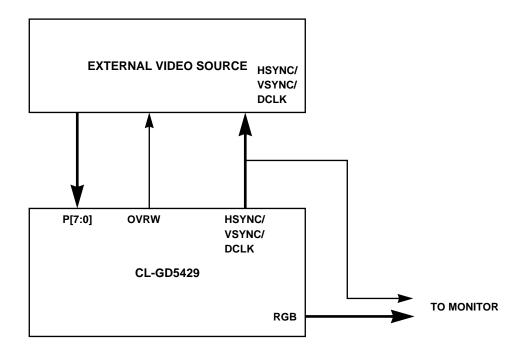

|             | 7.    | Switch with OVRW (CL-GD5429 only)                     |        |

|             | 8.    | VESA® Advanced Feature Connector (VAFC)               | B14-11 |

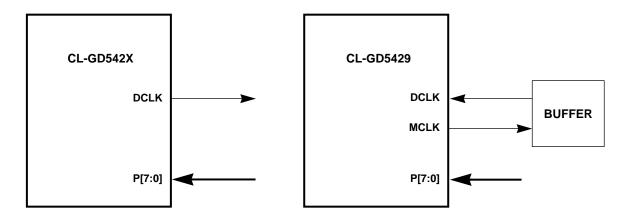

|     | 9.   | Using the Internal Clock with DCLK as Input   | B14-12 |

|-----|------|-----------------------------------------------|--------|

|     | 10   | Static Overlay                                | B14-12 |

| B1: | 5 EE | PROM INTERFACE AND PROGRAMMING                | B15-1  |

|     | 1.   | Introduction                                  | B15-2  |

|     | 2.   | Extension Register SR8                        | B15-2  |

|     | 3.   | Timing Considerations                         |        |

|     | •    | 3.1 Write Example                             |        |

|     |      | 3.2 Read Example                              |        |

| B16 | 6 FA | MILY COMPATIBILITY AND UPGRADING              | B16-1  |

|     | 1.   | Introduction                                  | B16-2  |

|     | 2.   | DRAM Upgrades                                 | B16-3  |

|     | 3.   | Software Considerations                       |        |

|     | 4.   | Local Bus Considerations                      | B16-4  |

| B17 | 7 P- | WELL/N-WELL LAYOUT CONSIDERATIONS             | B17-1  |

|     | 1.   | Introduction                                  | B17-2  |

|     | 2.   | P-Well versus N-Well Process                  |        |

|     |      | 2.1 Identifying P-WELL and N-WELL Devices     |        |

|     | 3.   | Recommended Changes                           |        |

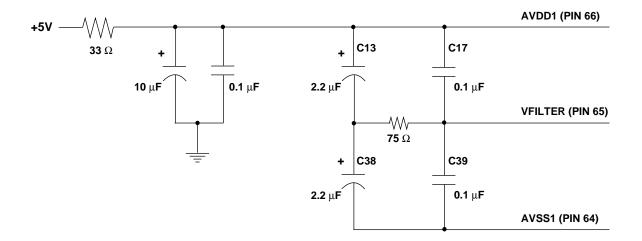

|     |      | 3.1 VDD Filter Change                         |        |

|     |      | 3.2 Layout Change                             | B17-3  |

| B18 | 8 M  | ANUFACTURING TEST                             | B18-1  |

|     | 1.   | Manufacturing Test Program                    | B18-2  |

|     |      | 1.1 Specifications and Operating Instructions | B18-2  |

|     |      | 1.2 Using the MFGTST Menu-Driven Interface    | B18-2  |

|     |      | 1.3 Display and Miscellaneous Tests           | B18-4  |

|     |      | 1.4 Miscellaneous Test Descriptions           | B18-5  |

|     |      | 1.5 Running MFGTST from the Command Line      | B18-8  |

|     |      | 1.6 Command Line Examples                     | B18-9  |

|     |      | 1.7 Manufacturing Test Updates                | B18-9  |

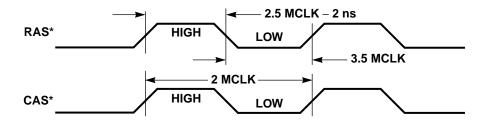

| B19 | 9 DF | RAM TIMING CALCULATIONS                       | B19-1  |

|     | 1.   | Introduction                                  | B19-2  |

|     | 2.   | MCLK Frequencies                              | B19-2  |

|     | 3.   | Standard RAS* vs. Extended RAS*               | B19-4  |

|     | 4.   | 70-ns DRAMs                                   | B19-6  |

|     | 5.   | A Combined Example                            | B19-7  |

| B20 | B20 MEMORY-MAPPED I/OB20-1   |                   |                                                       |        |  |  |

|-----|------------------------------|-------------------|-------------------------------------------------------|--------|--|--|

| B21 | PO                           | WEI               | R MANAGEMENT                                          | B21-1  |  |  |

|     | 1.                           | B21-2             |                                                       |        |  |  |

|     | 2.                           | Dis               | B21-2                                                 |        |  |  |

|     |                              | 2.1               | Report VBE/PM Capabilities                            |        |  |  |

|     |                              | 2.2               | Set Display Power State                               | B21-3  |  |  |

|     |                              | 2.3               | Get Display Power State                               | B21-4  |  |  |

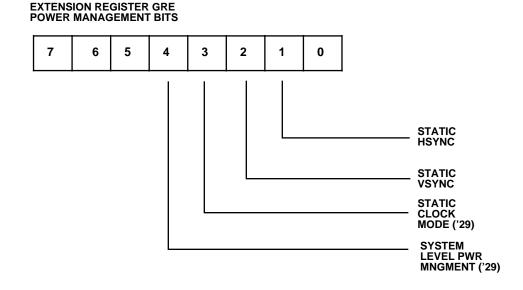

|     | 3.                           | Pov               | ver Management Hardware Bits (CL-GD5425/'29 only)     | B21-4  |  |  |

|     | 4.                           | Pov               | ver Management Hardware Bites (CL-GD5422/'24/'26/'28) | B21-5  |  |  |

|     |                              | 4.1               | DAC Power-Down                                        | B21-5  |  |  |

|     |                              | 4.2               | Video Clock/Display Memory Refresh                    | B21-5  |  |  |

|     |                              | 4.3               | Memory Clock                                          | B21-6  |  |  |

| B22 | CL                           | -GD               | 5425 NOTES                                            | B22-1  |  |  |

|     | 1.                           | Intro             | oduction                                              | B22-2  |  |  |

|     | 2.                           | Ove               | erview                                                | B22-2  |  |  |

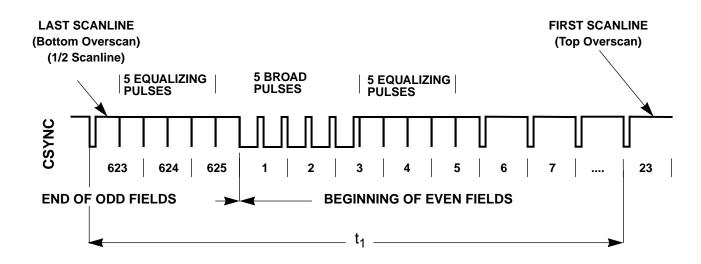

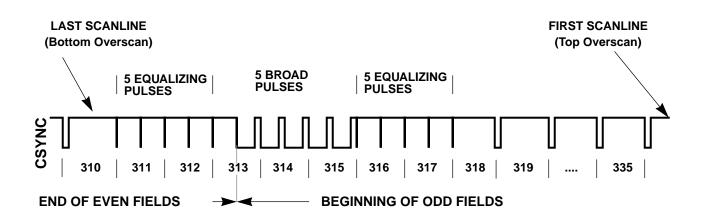

|     | 3.                           | TV Output Support |                                                       |        |  |  |

|     |                              | 3.1               | Pins Redefined for TV Modes                           | B22-2  |  |  |

|     |                              | 3.2               | Reference Frequencies for TV Modes                    | B22-3  |  |  |

|     |                              | 3.3               | Modes Supported for TV Output                         | B22-5  |  |  |

|     |                              | 3.4               | Expansion/Scaling                                     | B22-6  |  |  |

|     |                              | 3.5               | Color Subcarrier Reference Output                     | B22-7  |  |  |

|     |                              | 3.6               | Encoders Supported                                    | B22-7  |  |  |

|     |                              | 3.7               | Flicker-filter Processing                             | B22-10 |  |  |

|     |                              | 3.8               | TV Operation with/without a VGA Monitor Connected     | B22-10 |  |  |

|     | 4.                           | Mod               | de 13X                                                | B22-11 |  |  |

|     |                              | 4.1               | Introduction                                          | B22-11 |  |  |

|     |                              | 4.2               | Vertical Resolution Changes                           | B22-11 |  |  |

|     |                              | 4.3               | Mode 13X Horizontal Adjust for 360-Pixel Resolution   | B22-11 |  |  |

|     | 5.                           | Mul               | timedia Features                                      | B22-12 |  |  |

|     |                              | 5.1               | YCrCb Support                                         | B22-12 |  |  |

|     |                              | 5.2               | Overlay Modes                                         | B22-13 |  |  |

|     |                              | 5.3               | DAC Modes                                             | B22-13 |  |  |

|     | 6.                           | 640               | imes 480 NTSC 'Overscan' in Modes 5F and 64           | B22-13 |  |  |

|     | 7.                           | NTS               | SC Composite Output                                   | B22-14 |  |  |

|     | 8. CRTC Programming ValuesB2 |                   |                                                       |        |  |  |

|            | 9. | BIO   | S Functions                                                                  | B22-18 |

|------------|----|-------|------------------------------------------------------------------------------|--------|

|            |    | 9.1   | Set Horizontal Underscan/Overscan                                            | B22-19 |

|            |    | 9.2   | Set Vertical Scaling Enable/Disable                                          | B22-19 |

| <b>C</b> 1 | SC | OFTW  | /ARE SUPPORT                                                                 | C1-1   |

|            | 1. | Intro | oduction                                                                     | C1-2   |

|            | 2. | CL-   | GD542X VGA Software Utilities                                                | C1-2   |

|            |    | 2.1   | CLMODE — A CL-GD542X Video Mode Configuration Utility                        | C1-2   |

|            |    | 2.2   | VGA.EXE — RAMBIOS Utility                                                    | C1-2   |

|            |    | 2.3   | OEM System Integration (OEMSI) Utility                                       | C1-3   |

|            |    | 2.4   | SETRES Utility                                                               | C1-3   |

|            | 3. | CL-   | GD542X VGA Software Drivers                                                  | C1-4   |

|            |    | 3.1   | Driver Applicability                                                         | C1-4   |

| D1         | E  | (TEN  | DED VIDEO MODES PROGRAMMING                                                  | D1-1   |

|            | 1. | Intro | oduction                                                                     | D1-3   |

|            | 2. | Sup   | er VGA Display Modes                                                         | D1-4   |

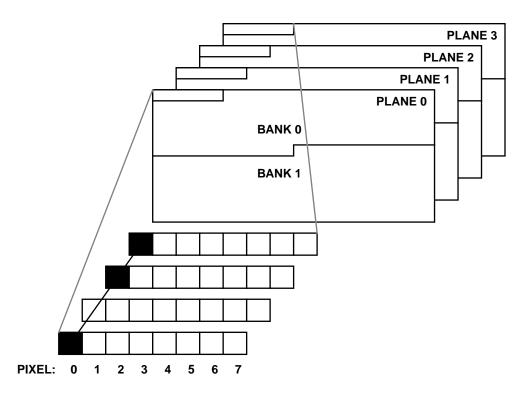

|            | 3. | 16-0  | Color Planar Mode Memory Organization                                        | D1-5   |

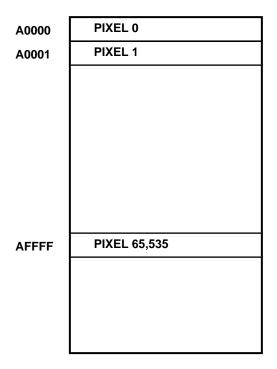

|            | 4. | 256   | -Color Packed Pixel Modes                                                    | D1-6   |

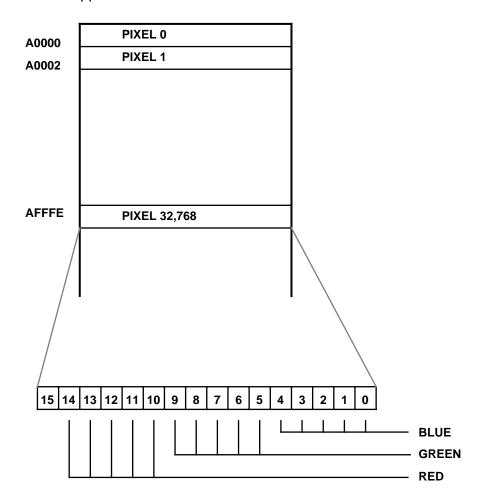

|            | 5. | Dire  | ct-Color (32,768 or 65,536) Packed Pixel Modes                               | D1-7   |

|            | 6. |       | ed 32,768 Colors (RGB 5-5-5) and 256-Color (8 bpp)<br>ked Pixel Modes        | D1-9   |

|            | 7. | True  | e Color 24-Bit (16.8 Million Colors) Packed Pixel Modes                      | D1-10  |

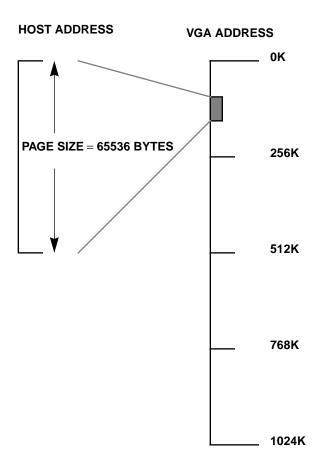

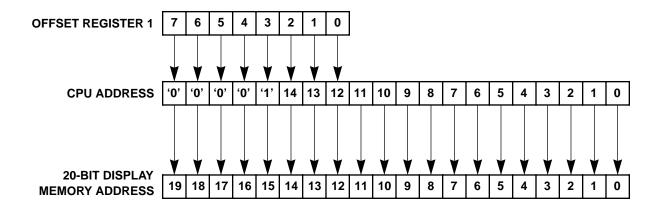

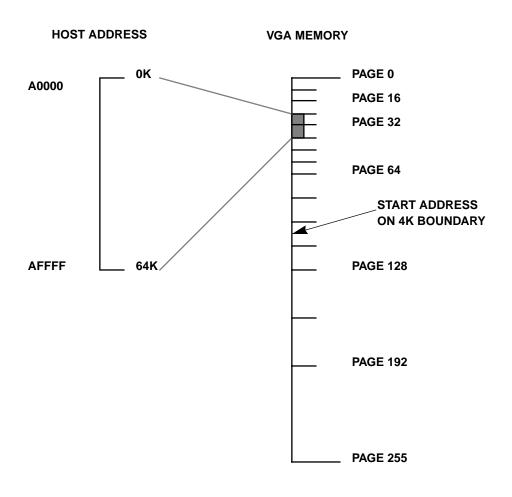

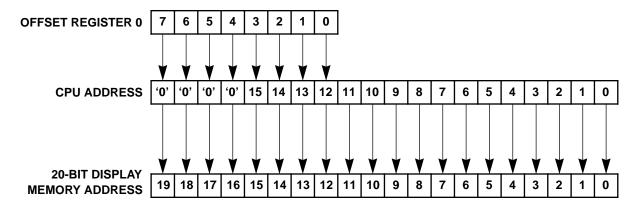

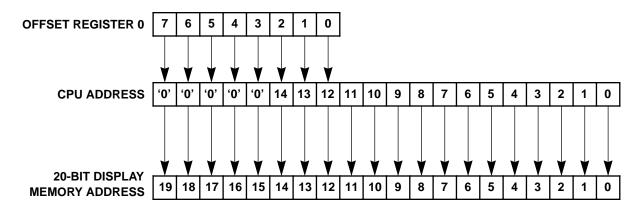

|            | 8. | Exte  | ended Video Memory addressing Techniques                                     | D1-11  |

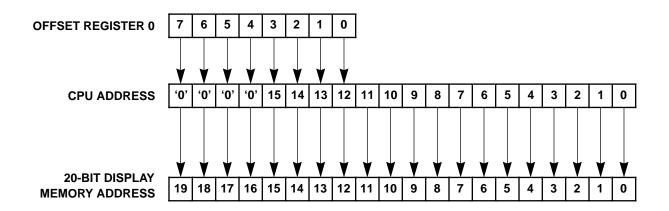

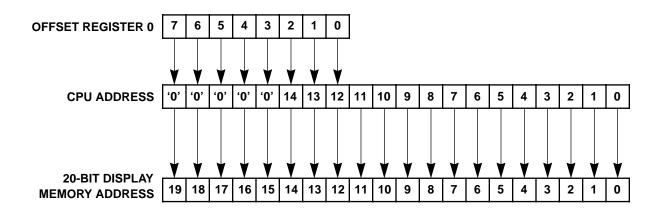

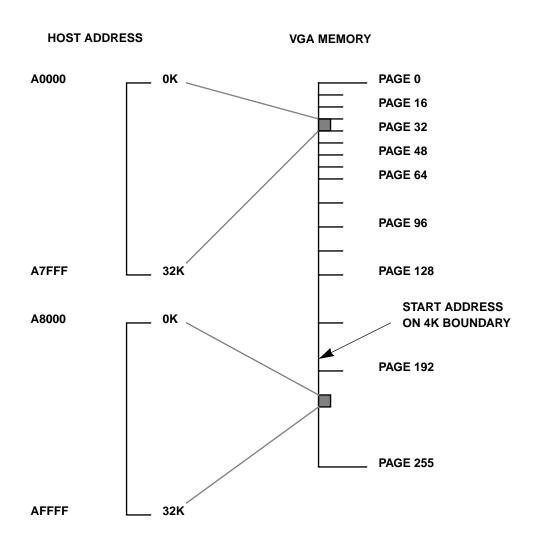

|            |    | 8.1   | Single-Page Addressing                                                       | D1-11  |

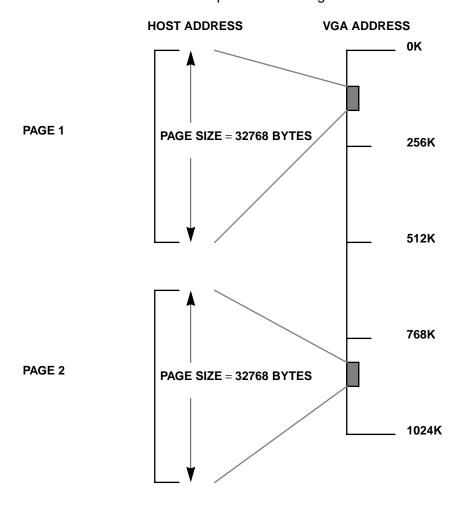

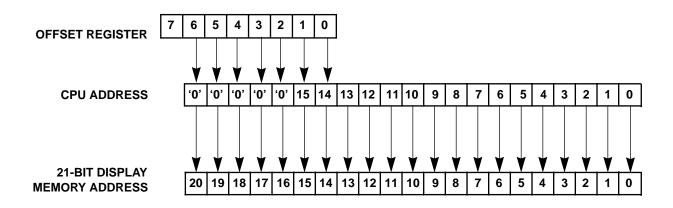

|            |    | 8.2   | Dual-Page Addressing                                                         | D1-13  |

|            | 9. | VG    | A Programming Examples                                                       | D1-17  |

|            |    | 9.1   | Identifying the CL-GD542X Controllers                                        | D1-18  |

|            |    | 9.2   | Determining if VGA Controller is a CL-GD542X                                 | D1-18  |

|            |    | 9.3   | Initializing CL-Gd542X Super VGA Mode via INT 10h Call                       | D1-20  |

|            |    | 9.4   | Programming Single-Page Mapping                                              | D1-21  |

|            |    | 9.5   | Programming Dual-Page Mapping                                                | D1-22  |

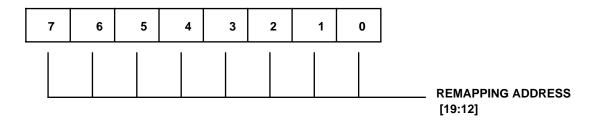

|            |    | 9.6   | Programming the Address Remapping Registers                                  | D1-22  |

|            |    | 9.7   | Programming Single-Page Remapping with a 64-Kbyte Segment Bank Address       | D1-23  |

|            |    | 9.8   | Programming Dual-Page Remapping Address with a 34-Kbyte Segment Bank Address | D1-25  |

| D2        | LI              | NEAR ADDRESSING                               | D2-1 |

|-----------|-----------------|-----------------------------------------------|------|

|           | 1.              | Introduction                                  | D2-2 |

|           | 2.              | Linear Address Advantages                     | D2-2 |

|           | 3.              | Linear Address Mapping                        | D2-2 |

|           | 4.              | Summary                                       | D2-3 |

| D3        | ΗA              | ARDWARE CURSOR                                | D3-1 |

|           | 1.              | Introduction                                  | D3-2 |

|           | 2.              | Hardware Cursor Operation                     | D3-2 |

|           | 3.              | 32 × 32 Hardware Cursor                       | D3-3 |

|           | 4.              | 64 × 64 Hardware Cursor                       | D3-4 |

|           | 5.              | Summary                                       | D3-4 |

| D4        | IN <sup>-</sup> | TERLACED MODE                                 | D4-1 |

|           | 1.              | Introduction                                  | D4-2 |

|           | 2.              | Interlaced Mode Display Operation             | D4-2 |

|           | 3.              | 1024 × 768 Interlaced Mode                    | D4-2 |

| D5        | 13              | 2-COLUMN TEXT MODE                            | D5-1 |

|           | 1.              | Introduction                                  | D5-2 |

|           | 2.              | 132-Column Text Mode Operation                | D5-2 |

|           | 3.              | 132-Column CRT Controller Programming         | D5-3 |

| D6        | CC              | DLOR EXPANSION                                | D6-1 |

|           | 1.              | Introduction                                  | D6-2 |

|           | 2.              | Color Expansion — How Performance is Enhanced | D6-2 |

|           | 3.              | Color Expansion without the BitBLT Engine     | D6-2 |

|           | 4.              | Extended Write Mode 4                         | D6-3 |

|           | 5.              | Extended Write Mode 5                         | D6-4 |

|           | 6.              | Color Expansion using the BitBLT Engine       | D6-4 |

| <b>D7</b> | RE              | SERVED                                        |      |

| D8        | ВІТ             | BLT ENGINE                                    | D8-1 |

|           | 1.              | Introduction                                  | D8-2 |

|           | 2.              | Definitions                                   | D8-2 |

|           | 3.              | An Example: Display Memory to Display Memory  | D8-4 |

|           | 4.              | ROPs (Raster Operations)                      | D8-6 |

|    | 5.      | Color Expansion                                          | D8-7  |

|----|---------|----------------------------------------------------------|-------|

|    | 6.      | Color Expansion with Transparency (CL-GD5426/'28)        | D8-8  |

|    | 7.      | Color Expansion with Transparency (CI-GD5429)            | D8-8  |

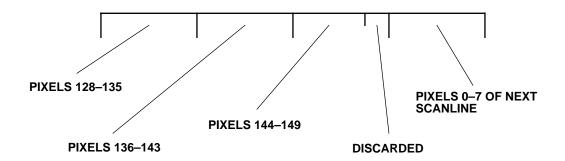

|    | 8.      | Color Expansion with Left Edge Clipping (CL-GD5429 only) | D8-9  |

|    | 9.      | Pattern Fills                                            | D8-9  |

|    | 10.     | Pattern Vertical Preset (CL-GD5429 only)                 | D8-9  |

|    | 11.     | Patterned Polygon Fills (CL-GD5429 only)                 | D8-10 |

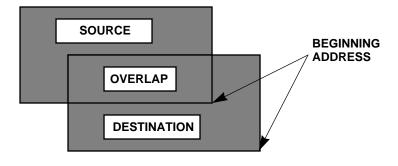

|    | 12.     | BLT Direction                                            | D8-10 |

|    | 13.     | System Memory                                            | D8-11 |

|    |         | Start/Suspend/Reset Controls                             |       |

|    |         | Complete BLT Register List                               |       |

|    |         | Memory-Mapped I/O (CL-GD5429 only)                       |       |

|    |         | Miscellanea                                              |       |

|    |         | Examples                                                 |       |

| D9 |         | RUS LOGIC BBS                                            |       |

|    | 1.      | Introduction                                             |       |

|    | 2.      | Telephone Number and Communication Parameters            |       |

|    | 3.      | First Time Log On                                        |       |

|    |         | <u> </u>                                                 |       |

|    | 4.<br>- | Upgraded Access                                          |       |

|    | 5.      | Organization of the Board                                |       |

| E1 | VG      | A BIOS                                                   | E1-1  |

|    | 1.      | Introduction                                             | E1-2  |

|    |         | 1.1 Main Features                                        |       |

|    |         | 1.2 Implementation Type                                  |       |

|    |         | 1.3 Configuration                                        | E1-3  |

|    | 2.      | Video Modes                                              | E1-4  |

|    | 3.      | Interrupt 10h interface Extensions                       | E1-7  |

|    |         | 3.1 Function Summary                                     | E1-7  |

|    |         | 3.2 Inquiry Functions                                    | E1-7  |

|    |         | 3.3 Miscellaneous Functions                              | E1-9  |

|    |         | 3.4 Additional Functions                                 | E1-9  |

|    |         | 3.5 Global Functions                                     | F1-10 |

# **CONTENTS**

|    | 4.   | VES | SA <sup>®</sup> Super VGA Standard    | E1-12 |

|----|------|-----|---------------------------------------|-------|

|    |      | 4.1 | Goals and Objectives                  | E1-12 |

|    |      | 4.2 | Standard VGA BIOS                     | E1-13 |

|    |      | 4.3 | Super VGA Mode Numbers                | E1-13 |

|    |      | 4.4 | Extended VGA BIOS                     | E1-14 |

|    | 5.   | Ext | ended Modes in RAM                    | E1-25 |

|    |      | 5.1 | Extensions to the Save Area Table     | E1-25 |

|    |      | 5.2 | BIOS Processing                       | E1-25 |

|    |      | 5.3 | Extended Mode Supplemental Parameters | E1-26 |

| F1 | GL   | oss | ARY AND BIBLIOGRAPHY                  | F1-1  |

|    | INIT | )FY |                                       |       |

# 1. INTRODUCTION

# 1.1 Scope of Document

This manual provides technical information for the CL-GD542X family of VGA controllers. This manual includes a description of each major component integrated into the chip, a data book, detailed information on each register, BIOS, and a number of application notes to assist hardware and software designers.

# 1.2 Applicable Chip Types

This manual documents chip Revision A or later.

The CL-GD542X ID Register — CR27, will read back a value indicating the chip-family member. Refer to Chapter 9, "Extension Register Descriptions", for further information.

# 1.3 Intended Audience

This manual is intended for the technically sophisticated audience. It is assumed that the reader is familiar with assembly language programming on the 8088/8086, 80286/80386/80486, 80386SX, or similar microprocessor, and understands the fundamentals of video display technology.

Management personnel should find Chapter 2, "Overview", useful.

Hardware engineers should find Chapter 3, "Data Book", useful. It contains the pinouts and detailed pin descriptions, tables indicating how the various interfaces must be connected, and detailed DC and AC characteristics. In addition, the application notes in Appendix B should be helpful for board designs.

Software engineers should find Chapters 4–9 (register descriptions) useful for BIOS- and driver-level codes. All registers are described to the bit level. Also, the application notes in Appendices B–D should be helpful, especially those discussing the palette DAC and clock options, and programming methods.

# 1.4 Conventions

This section discusses conventions used throughout this document. Conventions include acronyms, abbreviations, and nomenclature usage. For a quick reference of acronyms see Table 1-1.

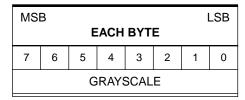

# **Bits**

Bits are always listed in descending order, most-significant (highest number) to least-significant (lowest number). When discussing a bit field within a register or memory, the bit number of the most-significant bit is given on the left, followed by a colon (:) and then the bit number of the least-significant bit (for example, bits 7:0). A field consists of a set of adjoining bits with common functionality. Registers are made up of fields of one or more bits.

# Acronyms

Table 1-1 lists acronyms common to this manual. For further definitions, refer to Appendix F1, "Glossary and Bibliography".

Table 1-1. Acronym Quick Reference

| Acronym  | Definition                                  |  |  |

|----------|---------------------------------------------|--|--|

| A.N.     | alpha numeric                               |  |  |

| BIOS     | basic input output system                   |  |  |

| ВРР      | bits per pixel                              |  |  |

| CGA      | color graphics adapter                      |  |  |

| CMOS     | complementary metal-<br>oxide semiconductor |  |  |

| DRAM     | dynamic random access<br>memory             |  |  |

| EGA      | enhanced graphics adapter                   |  |  |

| EPROM    | electrically programmable read-only memory  |  |  |

| High-Z   | high-impedance                              |  |  |

| 1/0      | input/output                                |  |  |

| LUT      | lookup table                                |  |  |

| MSB      | most-significant bit                        |  |  |

| RAM      | random access memory                        |  |  |

| RGB      | red, green, blue                            |  |  |

| SR logic | set/reset logic                             |  |  |

| VAFC     | VESA® Advanced Feature<br>Connector         |  |  |

| VGA      | video graphics array                        |  |  |

| VRAM     | video (dynamic) random<br>access memory     |  |  |

| Acronym     | Definition                                                 |  |  |  |

|-------------|------------------------------------------------------------|--|--|--|

| A.P.A.      | all points addressable                                     |  |  |  |

| BitBLT      | bit boundary block transfer                                |  |  |  |

| CAS         | column address strobe                                      |  |  |  |

| CLUT        | color lookup table                                         |  |  |  |

| DI          | data in                                                    |  |  |  |

| EEPROM      | electrically erasable/<br>programmable read-only<br>memory |  |  |  |

| EISA        | extended industry standard architecture                    |  |  |  |

| FIFO        | first-in/first-out                                         |  |  |  |

| HSYNC/VSYNC | horizontal/vertical synchronization                        |  |  |  |

| LSB         | least-significant bit                                      |  |  |  |

| MD          | memory data                                                |  |  |  |

| N/A         | not available                                              |  |  |  |

| RAS         | row address strobe                                         |  |  |  |

| R/W         | read/write                                                 |  |  |  |

| TTL         | transistor-transistor logic                                |  |  |  |

| VESA®       | Video Electronics Standards<br>Association                 |  |  |  |

| VLUT        | video lookup table                                         |  |  |  |

#### Abbreviations

The unit 'Kbyte' designates 1024 bytes. The unit 'Mbyte' designates 1,048,576 bytes (1024 squared). The unit 'Gbyte' designates 1000 megabytes. The unit 'Hz' designates hertz. The unit 'kHz' designates 1000 hertz. The unit 'MHz' designates 1000 kilohertz. The unit 'ns' designates nanosecond. The unit ' $\mu$ s' designates microsecond (1000 nanoseconds). The unit 'ms' designates millisecond (1000 microseconds). The unit 'mA' designates milliampere. The use of 'tbd' in tables indicates values that are 'to be determined'.

# **Numeric Naming**

Hexadecimal numbers are represented with all letters in uppercase and a lowercase 'h' is appended to them (for example, '14h', '3A7h', and 'C000h' are hexadecimal numbers). Numbers not indicated by an 'h' are decimal. Octal numbers are not used in this manual.

#### Reserved

When a system memory or I/O address is referred to as 'Reserved', it means that writing to that address is not permitted. Reserved bits *must* be written as '0' to maintain upward compatibility.

# Read-Only

The word 'Read-only' is used to indicate registers and bits that can be read, but not written to.

# 2. OVERVIEW

The True Color VGA family of VGA controllers supports high-resolution graphics and text display modes for a variety of color CRT monitors using industry-standard 15-pin analog video and VESA interfaces.

The CL-GD542X chips are hardware- and software-compatible with the IBM® VGA, and provide improved performance and additional functionality.

Highly integrated, these chips include a programmable dual-frequency synthesizer and palette DAC. A complete 512 Kbyte motherboard solution can be implemented with a single DRAM.

The CL-GD542X implements all control and data registers in the standard VGA controller. It also implements all data manipulation capabilities and data paths in the standard VGA adapter.

# 2.1 Features

Table 2-1 is a list of the major features of the CL-GD542X family of VGA controllers.

Table 2-1. CL-GD542X Family Features

| Features                                                           | 'GD5420       | 'GD5422       | 'GD5424       | 'GD5425       | 'GD5426       | 'GD5428       | 'GD5429               |  |

|--------------------------------------------------------------------|---------------|---------------|---------------|---------------|---------------|---------------|-----------------------|--|

| Performance                                                        |               |               |               |               |               |               |                       |  |

| VESA <sup>®</sup> VL-Bus™ and Direct<br>'386 or '486 CPU Interface |               |               | <b>√</b>      | ✓             | 1             | 1             | 1                     |  |

| BitBLT engine                                                      |               |               |               |               | 1             | Enhanced      | Memory-<br>mapped I/O |  |

| Zero-wait-state operation                                          | 1             | ✓             | ✓             | ✓             | 1             | 1             | 1                     |  |

| Maximum display memory                                             | 1 Mbyte       | 1 Mbyte       | 1 Mbyte       | 1 Mbyte       | 2 Mbytes      | 2 Mbytes      | 2 Mbytes              |  |

| Display memory interface                                           | 16-bit        | 32-bit        | 32-bit        | 32-bit        | 32-bit        | 32-bit        | 32-bit                |  |

| Hardware cursor (in pixels)                                        | up to 32 × 32 | up to 64 × 64         |  |

| Maximum dot clock frequency                                        | 75 MHz        | 80 MHz        | 86 MHz                |  |

| Maximum MCLK frequency                                             | 50 MHz        | 50 MHz        | 50 MHz        | 60 MHz        | 50 MHz        | 50 MHz        | 60 MHz                |  |

| High Integration                                                   | ı             | •             |               |               |               | · ·           | l                     |  |

| Integrated palette DAC and dual-frequency synthesizer              | 1             | 1             | 1             | 1             | 1             | 1             | 1                     |  |

| Motherboard VGA solution with only two ICs                         | 1             | 1             | 1             | ✓             | 1             | 1             | 1                     |  |

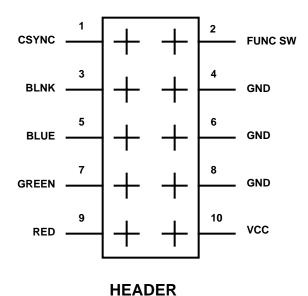

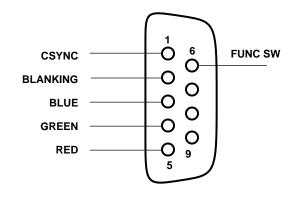

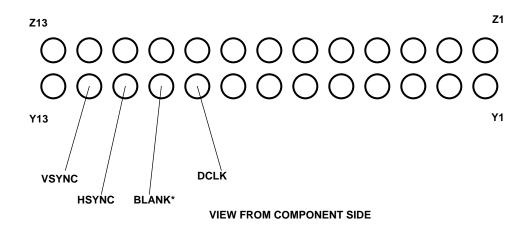

| Built-in port for VESA® feature connector                          | 1             | 1             | 1             | ✓             | 1             | 1             | 1                     |  |

| Built-in ISA<br>(up to 12.5 MHz),<br>MicroChannel® bus support     | 1             | 1             | 1             | 1             | 1             | 1             | 1                     |  |

| Built-in TV output support                                         |               |               |               | ✓             |               |               |                       |  |

Table 2-1. CL-GD542X Family Features (cont.)

| Features                                                                  | 'GD5420   | 'GD5422   | 'GD5424   | 'GD5425   | 'GD5426   | 'GD5428   | 'GD5429   |

|---------------------------------------------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Flexibility                                                               |           |           |           |           |           |           |           |

| Support for ×4-, ×8-, and ×16-bit-wide memory DRAMs                       | 1         | 1         | 1         | 1         | 1         | 1         | <b>√</b>  |

| 8- or 16-bit host bus I/O and memory interface                            | 1         | 1         | 1         | 1         | <b>√</b>  | 1         | ✓         |

| 8-bit gray and 3-3-2 RGB<br>DAC modes                                     |           |           |           | 1         |           | 1         | ✓         |

| CCIR 601 YCrCb mode                                                       |           |           |           | 1         |           |           |           |

| General                                                                   | '         |           |           |           |           |           |           |

| 100% hardware- and BIOS-<br>compatible with IBM® VGA<br>display standards | 1         | 1         | 1         | 1         | ✓         | 1         | <b>√</b>  |

| 'Green PC' compliant                                                      | 1         | 1         | 1         | 1         | ✓         | 1         | ✓         |

| 132-column text mode support                                              | 1         | 1         | 1         | 1         | <b>√</b>  | 1         | ✓         |

| 46E8 or 3C3 sleep<br>mechanism                                            |           | 1         | 1         | 1         | ✓         | 1         | ✓         |

| Video overlay and<br>'color key' support                                  |           | 1         | 1         | 1         | <b>√</b>  | 1         | ✓         |

| VESA <sup>®</sup> VAFC <sup>™</sup> base support (for video overlay)      |           |           |           | 1         |           |           | <b>√</b>  |

| Clocking support for CL-PX2080 MediaDAC™                                  |           |           |           | 1         |           | 1         | ✓         |

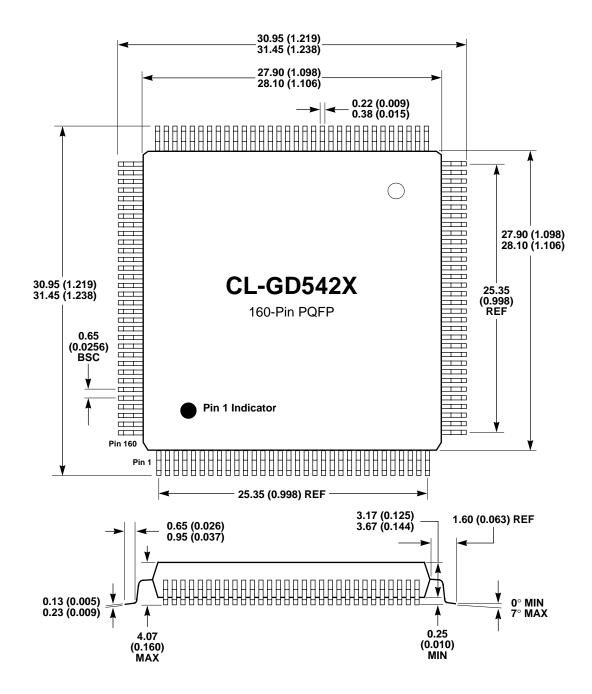

| Low-power CMOS,<br>160-pin package                                        | 1         | 1         | 1         | 1         | <b>√</b>  | 1         | ✓         |

| Screen resolution and colo                                                | rs        |           | Į.        | Į.        |           |           |           |

| 640 × 480                                                                 | up to 256 | up to 16M |

| 800 × 600                                                                 | up to 256 | up to 64K |

| 1024 × 768 (interlaced)                                                   | up to 256 | up to 64K | up to 64K |

| 1024 × 768 (non-interlaced)                                               | up to 256 |

| 1280 × 1024 (interlaced)                                                  |           | up to 16  | up to 16  | up to 16  | up to 256 | up to 256 | up to 256 |

**Table 2-2. Summary of Screen Resolutions**

| Resolutions                                                          | CL-GD5420 | CL-GD5422 | CL-GD5424<br>CL-GD5425 | CL-GD5426<br>CL-GD5428<br>CL-GD5429 |

|----------------------------------------------------------------------|-----------|-----------|------------------------|-------------------------------------|

| 640 × 480 × 256 color, 8 bits/pixel                                  | 1         | ✓         | ✓                      | ✓                                   |

| 640 × 480 × 32K color, 16 bits/pixel                                 |           | ✓         | ✓                      | ✓                                   |

| 640 × 480 × 64K color, 16 bits/pixel                                 |           | ✓         | ✓                      | ✓                                   |

| 640 × 480 × 16M color, 24 bits/pixel                                 |           | ✓         | ✓                      | ✓                                   |

| $800 \times 600 \times 16$ color, 4 bit planes                       | ✓         | ✓         | ✓                      | ✓                                   |

| $800 \times 600 \times 256$ color, 8 bits/pixel                      | <b>√</b>  | ✓         | ✓                      | ✓                                   |

| $800 \times 600 \times 32$ K color, 16 bits/pixel                    |           | ✓         | ✓                      | ✓                                   |

| $800 \times 600 \times 64$ K color, 16 bits/pixel                    |           | ✓         | ✓                      | ✓                                   |

| 1024 × 768 × 16 color, 4 bit planes (interlaced and non-interlaced)  | 1         | 1         | <b>✓</b>               | 1                                   |

| 1024 × 768 × 256 color, 8 bits/pixel (interlaced and non-interlaced) | 1         | 1         | 1                      | 1                                   |

| 1024 × 768 × 32K color, 16 bits/pixel (interlaced)                   |           |           |                        | ✓                                   |

| 1024 × 768 × 64K color, 16 bits/pixel (interlaced)                   |           |           |                        | ✓                                   |

| $1280 \times 1024 \times 16$ color, 4 bit planes (interlaced)        |           | ✓         | ✓                      | ✓                                   |

| $1280 \times 1024 \times 256$ color, 8 bits/pixel (interlaced)       |           |           |                        | ✓                                   |

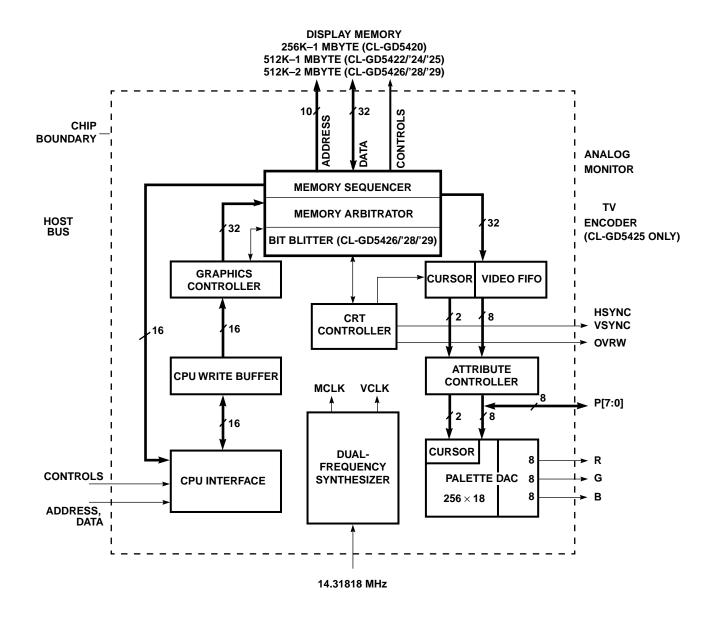

# 2.2 Chip Architecture

The CL-GD542X includes all the hardware required to implement CPU updates to display memory, Screen Refresh, and DRAM Refresh. It interfaces directly with the host system or the local bus, the display memory, and the monitor. The host interface can be either 8-or-16-bits-wide for memory and I/O. The CL-GD542X requires no glue logic for address decoding and control logic handshaking.

The four major activities supported by the CL-GD542X are:

- Host access to CL-GD542X registers

- · Host access to display memory

- Display access to display memory (screen refresh)

- Display Memory Refresh

# 2.2.1 Host Access to CL-GD542X Registers

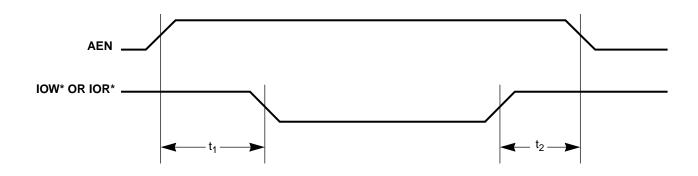

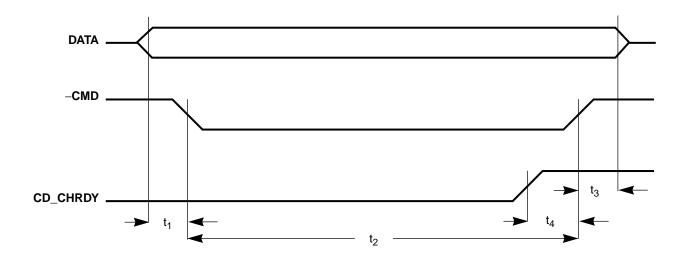

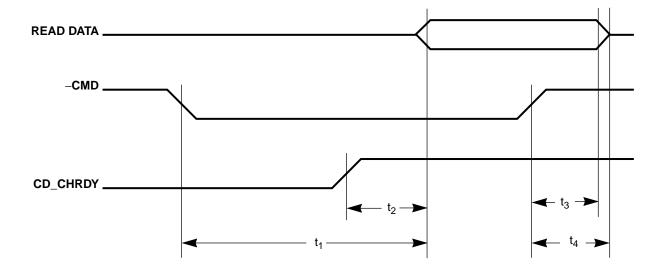

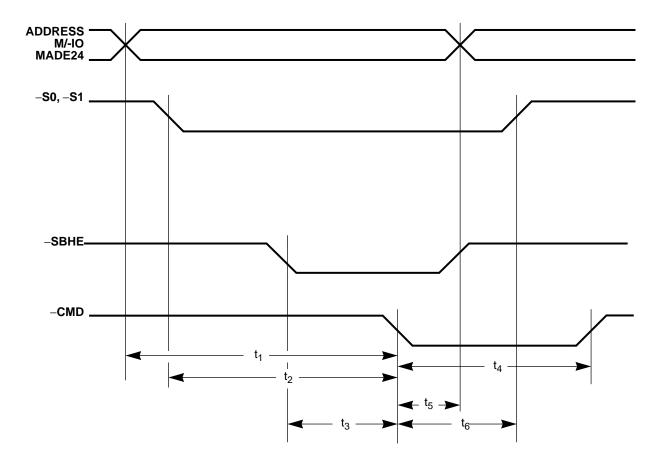

The host (typically an ISA, MicroChannel®, or '386 and '486/VESA VL local bus) can access CL-GD542X registers by setting up 16- or 24-bit addresses and generating I/O control signals to read or write 8- or 16-bit data. Other activities, such as DRAM refresh, screen refresh, and delayed CPU writes to display memory can take place concurrently with accesses to registers.

The registers are listed in Chapter 3, "Data Book", and described in Chapters 4–9. These registers include all the standard VGA registers, and are host-readable to allow BIOS and driver software to determine the state of the graphics adapter.

# 2.2.2 Host Access to Display Memory

The CL-GD542X handles the host access to display memory. The host effects memory accesses in the VGA address range to transfer data to or from one or more of the four display memory Planes. All of the required video handshake interface signals are internally generated by the CL-GD542X with no requirement for external logic decoding.

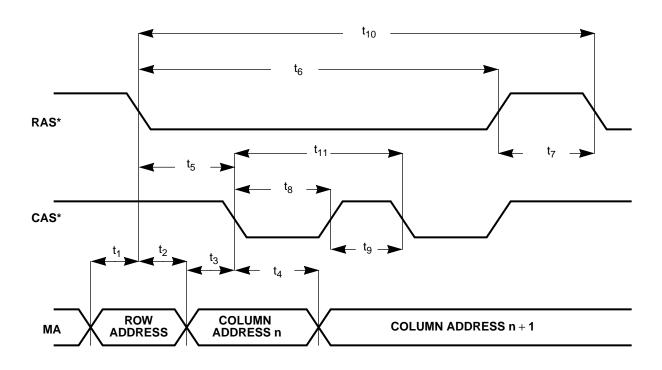

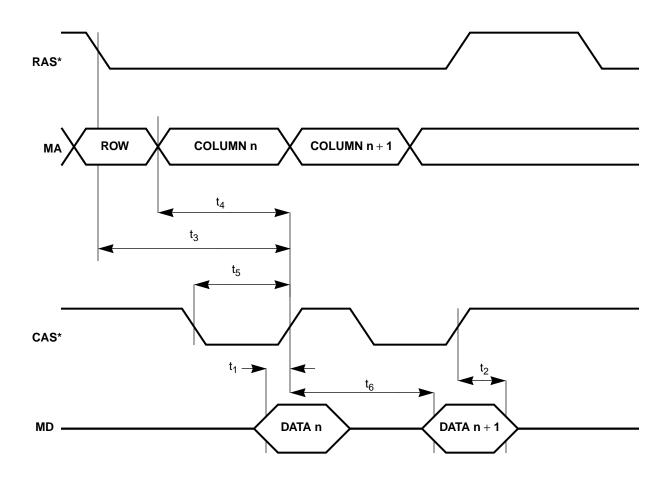

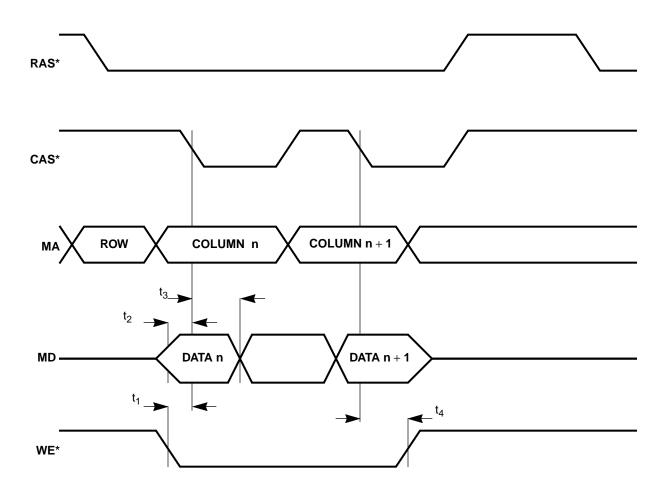

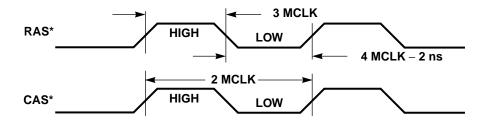

The CL-GD542X takes 24-bit addresses from the host, and transforms them according to the selected addressing mode and address space mappings, finally issuing multiplexed addresses to the planes via the MA[9:0] Address bus. RAS\*, CAS\*, OE\*, and WE[3:0]\* provide timing and control to the display memories. When interfacing to DRAMs that have dual-CAS\* signals, the CAS\* pin becomes WE\*, and the WE[3:0]\* pins become CAS[3:0]\*.

A Write Buffer is logically located at the CPU interface to isolate the CPU from the display memory. The CPU Write accesses to display memory take place immediately until the Write Buffer is full. The address and data are written into the cache, and the actual write into display memory occurs later. If the Write Buffer is full, wait states will be inserted until there is space.

# 2.2.3 Display Access to Display Memory

The CL-GD542X also contains an intelligent Address Sequencer that allocates display memory cycles not only to the host, but also to the display CRT Controller for screen refresh.

A FIFO logically between the Memory Sequencer and the Attribute Controller decouples the memory speed from the display speed, allowing the execution of Fast-page-mode accesses for screen refresh. This minimizes the memory bandwidth required.

The display is blanked during horizontal and vertical retrace intervals, freeing additional memory bandwidth for host access. The CL-GD542X improves on the performance of the IBM VGA implementation, especially for lower-resolution displays.

# 2.2.4 Display Memory Refresh

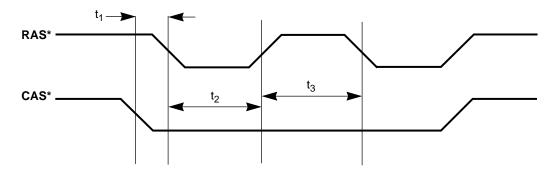

The CL-GD542X handles the refresh of the dynamic RAMs used for the display memory. During each horizontal blanking period, a selectable number of CAS\*-before-RAS\* refresh cycles are executed.

# 2.3 Major Components

The CL-GD542X incorporates all the major subsections of the IBM VGA/EGA into a single integrated circuit:

- Sequencer

- CRT Controller

- · Graphics Controller

- Attribute Controller

- Programmable Dual-Frequency Synthesizer

- Palette DAC

In describing the CL-GD542X family of VGA controllers, it is useful to retain the identity of the original major subsections found in the IBM EGA and VGA controllers. The architectures of these major subsections are described on the following pages.

# 2.3.1 Sequencer

The Sequencer controls access to the display memory. It ensures that the necessary screen refresh and dynamic memory refresh cycles are executed, and that the remaining memory cycles are made available for CPU and BLT read/write operations.

The Sequencer consists of a memory arbitrator and a memory controller. It accepts requests from memory address counters associated with the CRTC, and address transformation logic associated with the Graphics Controller. It uses the Video FIFO to deliver data to the Attribute Controller, and the Write Buffer to transfer data to the Graphics Controller.

The Memory Sequencer registers are described in Chapter 5.

The memory controller is driven by a memory clock (MCLK) optimized for the speed of the DRAM used, independent of the video clock. It generates the signals and addresses necessary for accessing the display memory. The memory arbitrator is also driven by the memory clock. It implements a policy that selects requests from either the CPU or the CRT on a dynamic priority.

# 2.3.2 CRT Controller

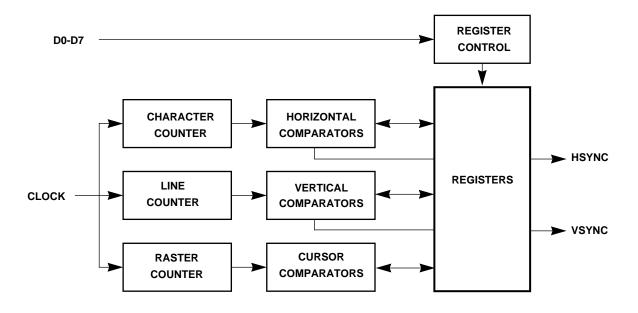

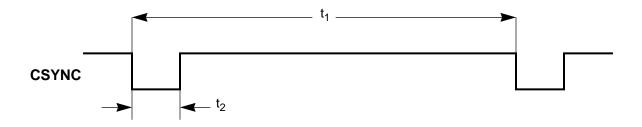

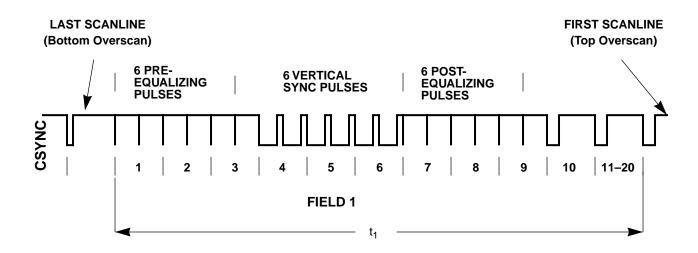

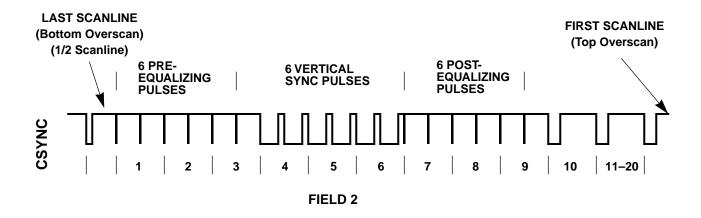

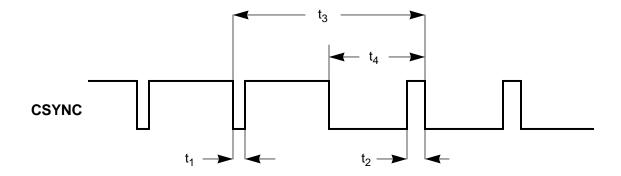

The CRT Controller generates the horizontal and vertical synchronization signals for the CRT display. It includes various registers that allow flexible configuration options. These options include user-configurable horizontal and vertical timing and polarity, cursor position, horizontal scanlines, and other display-related characteristics. The CRT Controller registers are described in Chapter 6.

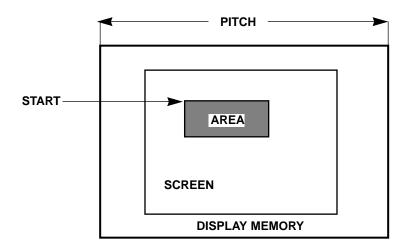

The CRT Controller is equivalent to the IBM CRTC as implemented in the IBM VGA hardware. The CRT Controller also provides split screen capability and smooth scrolling. A simplified block diagram of the CRT Controller is shown in Figure 2-1.

Figure 2-1. CRT Controller Functional Block Diagram

# 2.3.3 Graphics Controller

The Graphics Controller operates in either text or graphics modes and has the following major functions:

- · Provides the host CPU a read/write access path to display memory

- · Controls all four memory planes

- Allows data to be manipulated prior to being written to display RAM

- Formats data for use in various backward compatibility modes

- Provides color comparators for use in color painting modes

- Reads/writes 32-bit words through the 32-bit display memory interface

- Combines display RAM data and attribute data for output to the Pixel bus

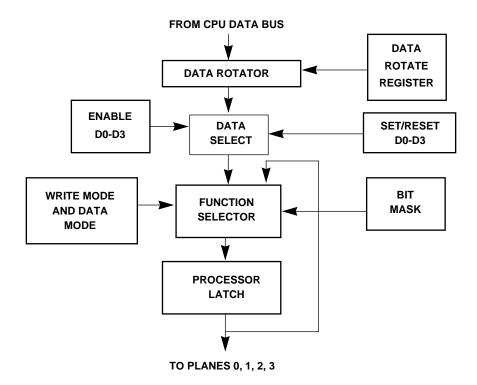

The Graphics Controller directs data from the display memory to the Attribute Controller and to the CPU. Figure 2-2 and Figure 2-3 illustrate typical write and read operations, respectively.

For a write operation, the data from the CPU bus are combined with the data from the Set/Reset Logic, depending on the Write mode. In addition, the data may be combined with the contents of the read latches, and some bits or planes may be masked (prevented from being changed). See the descriptions of the Graphics Controller registers in Chapter 7 for more information.

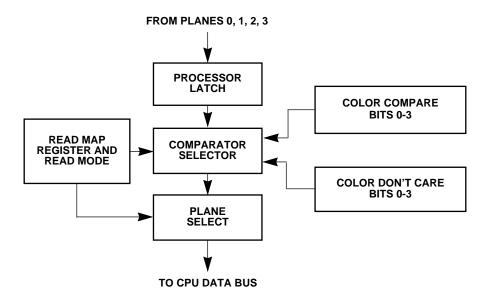

Figure 2-2. Graphics Controller Write Operation

The Graphics Controller is also involved when the CPU is reading data from display memory. Depending on the Read mode, the data returned may be the actual contents of the display memory, or it may reflect the outcome of comparisons with the color value in one of the Graphics Controller registers. See the descriptions of the Graphics Controller registers in Chapter 7 for more information.

Figure 2-3. Graphics Controller Read Operation

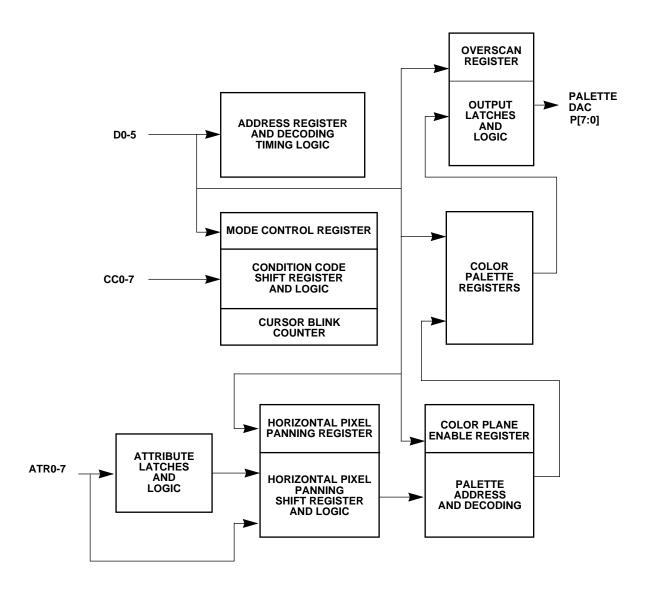

# 2.3.4 Attribute Controller

The Attribute Controller controls blinking and underline operations in alphanumeric modes. It also provides the horizontal pixel panning capability in both alphanumeric and graphics modes. The Attribute Controller registers are described in Chapter 8. Figure 2-4 depicts the functional block diagram of the Attribute Controller.

Figure 2-4. Attribute Controller Functional Block Diagram

# 2.3.5 **Dual-Frequency Synthesizer**

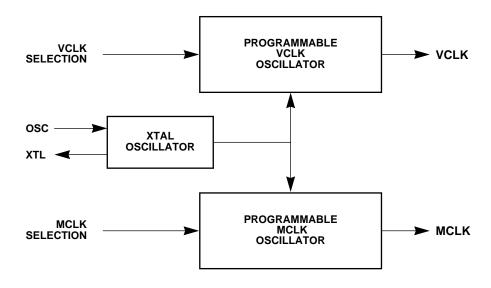

The CL-GD542X includes an integrated dual-frequency synthesizer that can be programmed to generate the VCLK for many standard screen formats, and the MCLK used by the Sequencer. The synthesizer requires a single-reference frequency of 14.31818 MHz that can be supplied by the on-chip oscillator, or can be injected from an external source.

Figure 2-5. Programmable Dual-Frequency Synthesizer Functional Diagram

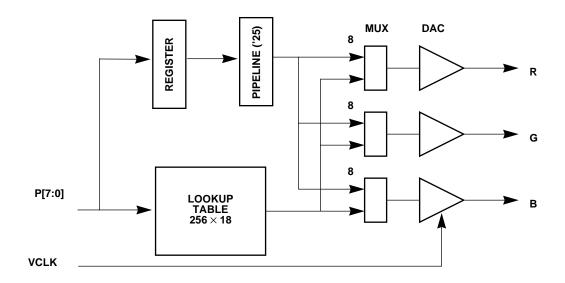

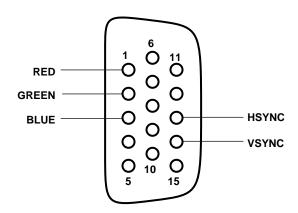

# 2.3.6 Palette DAC

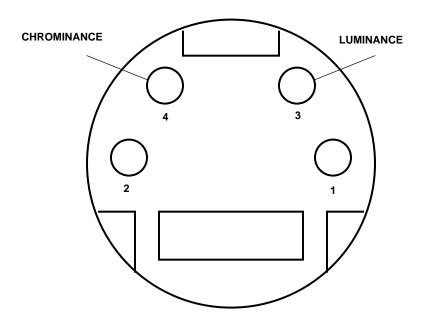

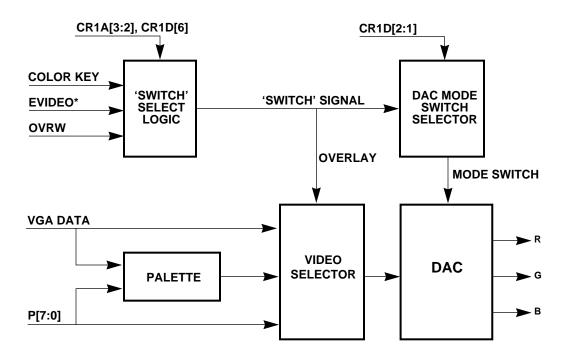

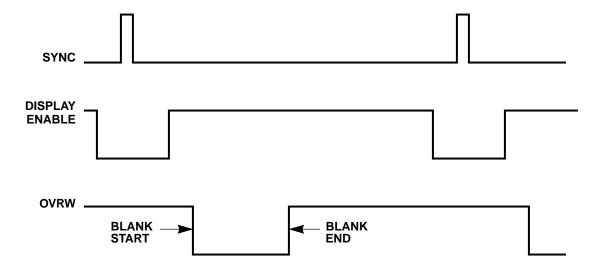

The CL-GD542X includes an integrated palette DAC that can interface directly to the monitor connector via appropriate RFI filters. The palette DAC can be programmed for 256 simultaneous colors from a palette of 256K, Direct-color mode, or YCrCb (CL-GD5425 only). In Direct-color mode, two or three contiguous bytes from the display memory are combined for each pixel. This allows 32K, 64K, or 16.8 million simultaneous colors on the screen. The CL-GD5425 can be programmed for YCrCb (16 bpp) or AccuPak™, a proprietary compression method. In addition, the CL-GD5425 can be configured for a 7.5 IRE offset black level. Figure 2-6 is a functional block diagram of the palette DAC.

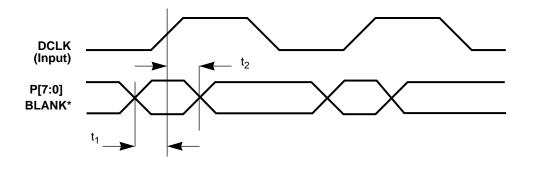

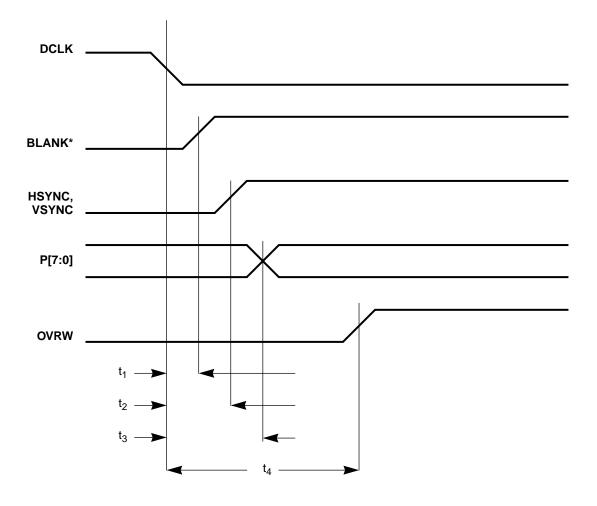

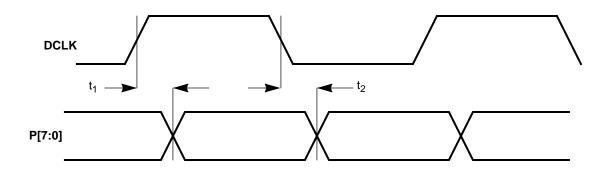

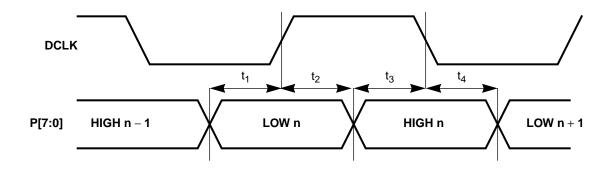

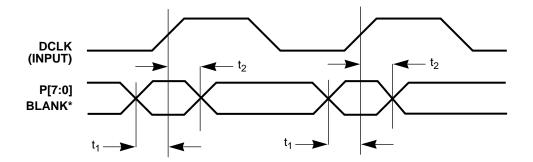

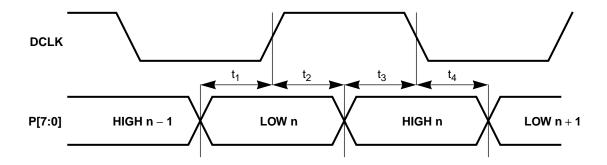

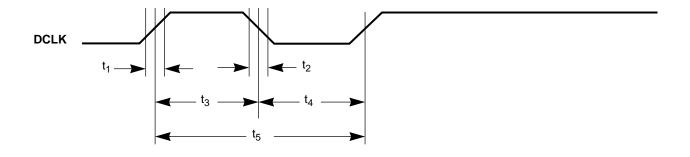

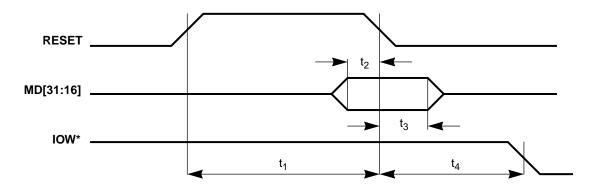

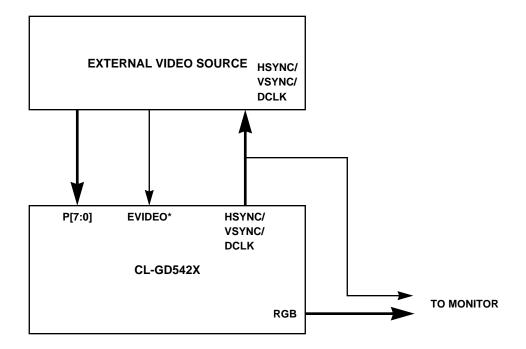

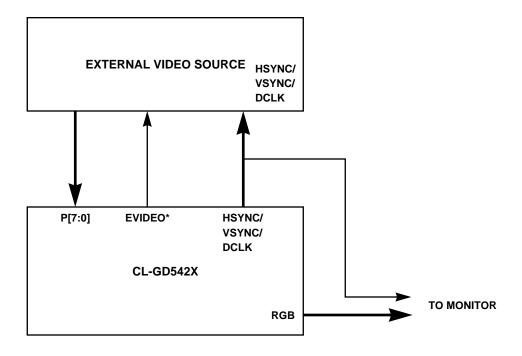

The pixel bus, DCLK, and BLANK\* can be driven into the CL-GD542X. This allows it to operate in the VESA-standard VGA passthrough connector mode. Fifteen- or sixteen-bit data can also be inserted from an external source through the P[7:0] pins. In addition to the VESA standard, the EVIDEO input is capable of switching at the pixel rate.

Figure 2-6. Palette DAC

# 2.4 Hardware/Software Compatibility

The CL-GD542X includes all registers and data paths required for VGA controllers. Enhancements include  $1024 \times 768$ , 8-bit Pixel mode, an internal color palette, eight simultaneously loadable text fonts, Write mode 3, and readable registers.

Extended-resolution display modes are made possible by the high video clock rates and high display memory bandwidth.

Extended text and graphics resolutions beyond the  $640 \times 350$  IBM EGA and  $640 \times 480$  VGA standards are also supported by the Cirrus Logic BIOS on both fixed-frequency, PS/2<sup>TM</sup>-compatible monitors as well as multiple-frequency monitors such as the NEC<sup>®</sup> MultiSync<sup>TM</sup>. These include 132-column and 60-line text modes,  $640 \times 480$  and  $800 \times 600$  32,768 and 65,536-color graphics modes,  $800 \times 600$  16-color VESA mode, and  $640 \times 480$  16.8-million True Color mode. The extended-resolution capabilities of the CL-GD542X are listed in the Chapter 3, "Data Book", along with the listing of the standard screen formats.

# 2.5 Video Subsystem Architecture

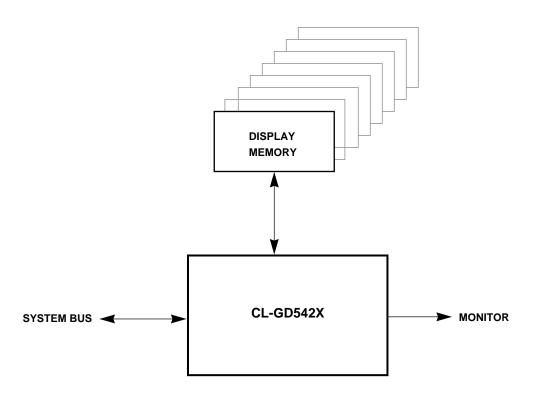

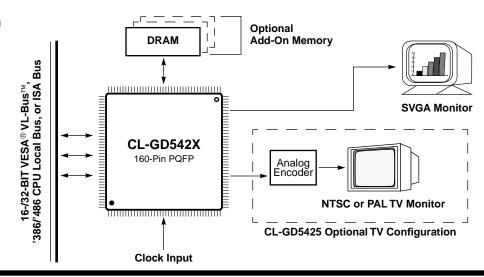

The following diagram shows the main components needed to implement a functional VGA subsystem using the CL-GD542X. The interfaces that must be implemented are the host CPU interface, the BIOS interface (for adapter board implementation only), the display memory interface, and the CRT interface.

Figure 2-7. Video Subsystem Architecture

# **FEATURES**

# ■ 32-bit GUI acceleration (CL-GD5426/'28/'29)

- BitBLT (Bit block transfer) engine

- Color expansion for 8- or 16-bit pixels

#### ■ 16/32-bit CPU interface

- VESA® VL-Bus™ (up to 50 MHz)

- ISA bus (12.5 MHz)

- Zero-wait-state write cycles

# ■ Resolutions up to 1280 × 1024